# Wide Input Voltage, 2.4 MHz, 3.0 Amp Asynchronous Buck Regulator With Low-I<sub>Q</sub> Standby, Sleep Mode, External Synchronization, and NPOR Output

#### **FEATURES AND BENEFITS**

- · Automotive AEC-Q100 qualified

- Withstands surge voltages up to 40 V

- Operates as low as 3.4 V<sub>IN</sub> (typ) with V<sub>IN</sub> decreasing

- Uses pulse frequency modulation (PFM) to draw only tens of microamperes from  $V_{IN}$  while maintaining keepalive  $V_{OUT}$

- PWM/PFM mode control input pin

- Delivers up to 3.0 A of output current with integrated 110 mΩ high voltage MOSFET

- SLEEP input pin commands ultra-low current shutdown mode

- Adjustable output voltage with ±1.0% accuracy from 0°C to 85°C, ±1.5% from -40°C to 150°C

- Programmable switching frequency: 250 kHz to 2.4 MHz

- Synchronization capability: applying a clock input to PWM/PFM input pin will increase PWM frequency

- · Active low, power-on reset (NPOR) open-drain output

Continued on next page...

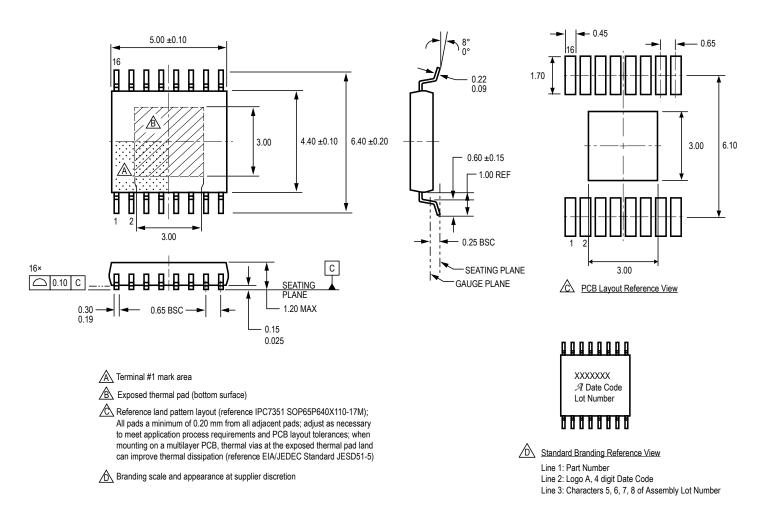

## Package: 16-Pin TSSOP with Exposed Themal Pad (suffix LP)

#### DESCRIPTION

Designed to provide the power supply requirements of next-generation car audio and infotainment systems, the A8590 provides all the control and protection circuitry to produce a high-current regulator with  $\pm 1.0\%$  output voltage accuracy. The A8590 employs pulse frequency modulation (PFM) to draw less than 50  $\mu A$  from 12  $V_{IN}$  while supplying 3.3 V / 40  $\mu A$ . After startup, the A8590 operates down to at least 3.6  $V_{IN}$  ( $V_{IN}$  falling).

Features of the A8590 include a PWM/ $\overline{PFM}$  mode control input to enable PWM (logic high) or PFM (logic low). If the PWM/ $\overline{PFM}$  input is driven by an external clock signal higher than the base frequency ( $f_{OSC}$ ), the PWM frequency synchronizes to the incoming clock frequency. The  $\overline{SLEEP}$  input pin commands an ultra-low current shutdown mode requiring less than 5  $\mu$ A for internal circuitry and 10  $\mu$ A (max) for MOSFET leakage at 16  $V_{IN}$ , 85°C. The A8590 has external compensation to accommodate a wide range of frequencies and external components, and provides a power-on reset (NPOR) signal validated by the output voltage. The A8590 uses Enhanced Continued on next page...

#### **APPLICATIONS**

- Automotive:

- □ Instrument clusters

- □ Audio systems

- Home audio

- □ Navigation□ HVAC

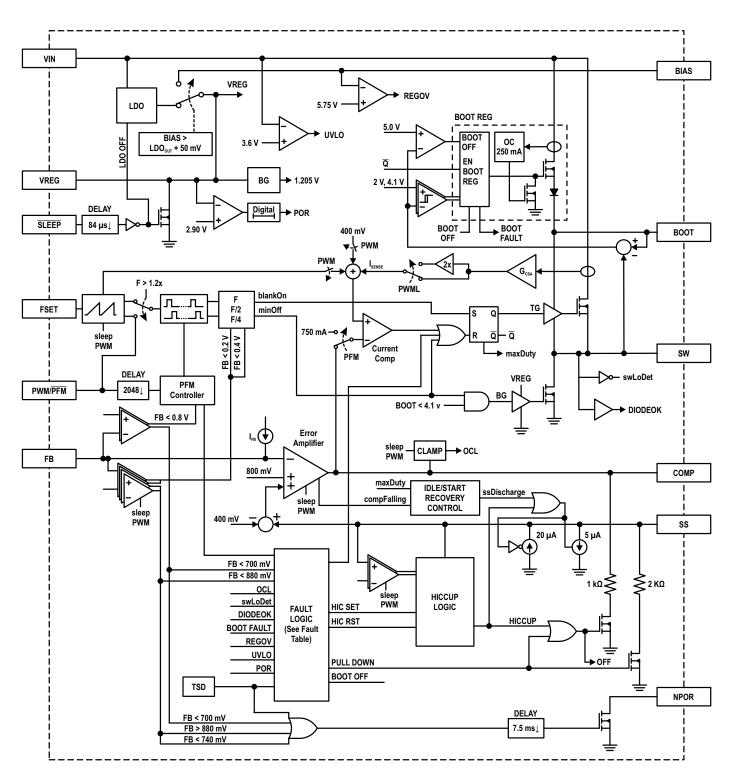

**Typical Application Diagram**

## Wide Input Voltage, 2.4 MHz, 3.0 Amp Asynchronous Buck Regulator With Low-I<sub>O</sub> Standby, Sleep Mode, External Synchronization, and NPOR Output

#### FEATURES AND BENEFITS (continued)

- Maximized duty cycle for low dropout

Enhanced recovery Idle-Stop Transients

- Pre-bias startup capable, V<sub>OUT</sub> will not cause a reset

- · External compensation for maximum flexibility

- Stable with ceramic or electrolytic output capacitors

- Excellent set of protection features to satisfy the most demanding applications

- Overvoltage, pulse-by-pulse current limit, hiccup mode short circuit, and thermal protection

- Robust FMEA, with pin open/short and component faults

- · Thermally enhanced surface-mount package

#### **DESCRIPTION** (continued)

Idle/Stop-Start Recovery technique to reduce or eliminate output overshoot when  $V_{IN}$  recovers from levels below  $V_{IN}$  minimum (i.e.,  $V_{OUT}$  drops out of regulation).

Extensive protection features of the A8590 include pulse-by-pulse current limit, hiccup mode short circuit protection, open/short asynchronous diode protection, BOOT open/short voltage protection,  $V_{\rm IN}$  undervoltage lockout,  $V_{\rm OUT}$  overvoltage protection and thermal shutdown.

The A8590 is supplied in a low profile 16-pin TSSOP package with exposed power pad (suffix LP). It is lead (Pb) free, with 100% matte-tin leadframe plating.

#### **SELECTION GUIDE**

| Part Number  | Operating Ambient Temperature<br>Range T <sub>A</sub> , (°C) | Packing                     |  |  |

|--------------|--------------------------------------------------------------|-----------------------------|--|--|

| A8590KLPTR-T | -40 to 125                                                   | 4000 pieces per 13-in. reel |  |  |

#### Table of Contents

| Specifications                                           |    |

|----------------------------------------------------------|----|

| Absolute Maximum Ratings                                 | 3  |

| Thermal Characteristics                                  |    |

| Functional Block Diagram                                 | 4  |

| Pin-out Diagram and Terminal List Table                  | 5  |

| Electrical Characteristics                               |    |

| Characteristic Performance                               | 10 |

| Functional Description                                   | 12 |

| Overview                                                 | 12 |

| Reference Voltage                                        | 12 |

| PWM Switching Frequency                                  | 12 |

| SLEEP Input                                              |    |

| PWM/PFM Input and PWM Synchronization                    |    |

| BIAS Input Functionality, Ratings, and Connections       | 13 |

| Transconductance Error Amplifier                         |    |

| Slope Compensation                                       |    |

| Current Sense Amplifier                                  |    |

| Power MOSFETs                                            | 14 |

| BOOT Regulator                                           |    |

| Pulse Width Modulation (PWM) Mode                        |    |

| Maximized Duty Cycle Control                             |    |

| Low-I <sub>Q</sub> Pulse Frequency Modulation (PWM) Mode |    |

| Reduced Current (Low-IP) PWM Mode                        |    |

| Soft-Start (Startup) and Inrush Current Control          |    |

| Pre-Biased Startup                                       |    |

| Not Power-On Reset (NPOR) Output                         | 18 |

| Protection Features                                                  | 19 |

|----------------------------------------------------------------------|----|

| Undervoltage Lockout (UVLO)                                          |    |

| Pulse-by-Pulse Overcurrent Protection (OCP)                          | 19 |

| OCP and Hiccup Mode                                                  | 20 |

| BOOT Capacitor Protection                                            | 20 |

| Asynchronous Diode Protection                                        | 20 |

| Output Overvoltage Protection (OVP)                                  | 21 |

| Pin-to-Ground and Pin-to-Pin Short Protections                       |    |

| Thermal Shutdown (TSD)                                               | 21 |

| Application Information                                              |    |

| Design and Component Selection                                       |    |

| Setting the Output Voltage (V <sub>OUT</sub> )                       | 25 |

| PWM Base Switching Frequency (f <sub>OSC</sub> , R <sub>FSET</sub> ) | 26 |

| Output Inductor (L <sub>O</sub> )                                    |    |

| Output Capacitors                                                    |    |

| Low-IQ PFM Output Voltage Ripple Calculation                         | 28 |

| Input Capacitors                                                     |    |

| Asynchronous Diode (D1)                                              |    |

| Bootstrap Capacitor                                                  |    |

| Soft-Start and Hiccup Mode Timing (C <sub>SS</sub> )                 | 29 |

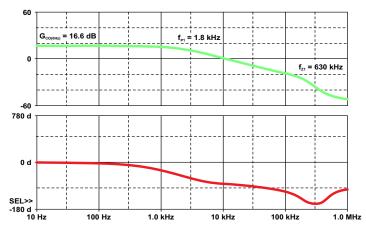

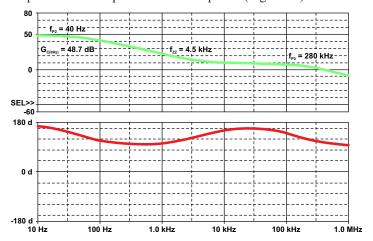

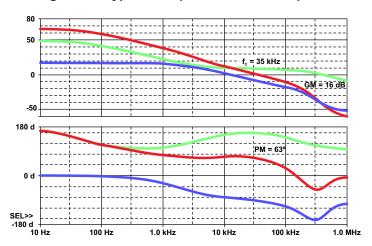

| Compensation Components (RZ, CZ, and CP)                             | 30 |

| A Generalized Tuning Procedure                                       | 32 |

| Power Dissipation and Thermal Calculations                           | 34 |

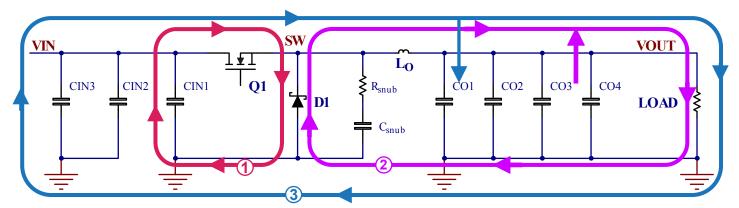

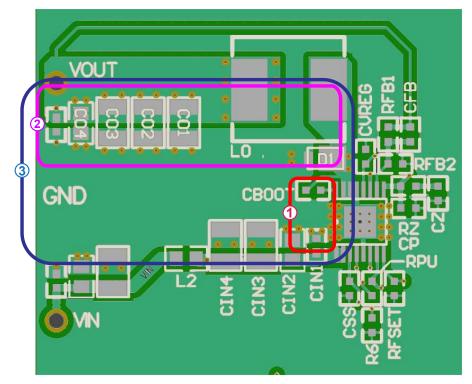

| PCB Component Placement and Routing                                  | 35 |

| Package Outline Drawing                                              | 37 |

#### **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Characteristic                | Symbol              | Notes                                                   | Rating                                  | Unit |

|-------------------------------|---------------------|---------------------------------------------------------|-----------------------------------------|------|

| VIN, SLEEP, SS Pin Voltage    |                     |                                                         | -0.3 to 40                              | V    |

| SW Pin Voltage                | V                   | Continuous (minimum limit is a function of temperature) | -0.3 to V <sub>IN</sub> + 0.3           | V    |

|                               | $V_{SW}$            | t < 50 ns                                               | -1.0 to V <sub>IN</sub> + 0.3           | V    |

| BOOT Pin Voltage              |                     | Continuous                                              | $V_{SW} - 0.3 \text{ to } V_{SW} + 5.5$ | V    |

|                               | V <sub>BOOT</sub>   | BOOT OV Fault Condition                                 | $V_{SW} - 0.3$ to $V_{SW} + 7.0$        | V    |

| BIAS Pin Voltage              | V <sub>BIAS</sub>   | Continuous                                              | –0.3 to 5.5                             | V    |

| BIAS FIII Voltage             |                     | BIAS OV Fault Condition                                 | –0.3 to 6                               | V    |

| All Other Pin Voltages        |                     |                                                         | –0.3 to 5.5                             | V    |

| Operating Ambient Temperature | T <sub>A</sub>      | K temperature range                                     | -40 to 125                              | °C   |

| Maximum Junction Temperature  | T <sub>J(max)</sub> |                                                         | 150                                     | °C   |

| Storage Temperature           | T <sub>stg</sub>    |                                                         | -55 to 150                              | °C   |

<sup>\*</sup> Operation at levels beyond the ratings listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to Absolute Maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions*                       | Value | Unit |

|----------------------------|-----------------|----------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | On 4-layer PCB based on JEDEC standard | 34    | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website.

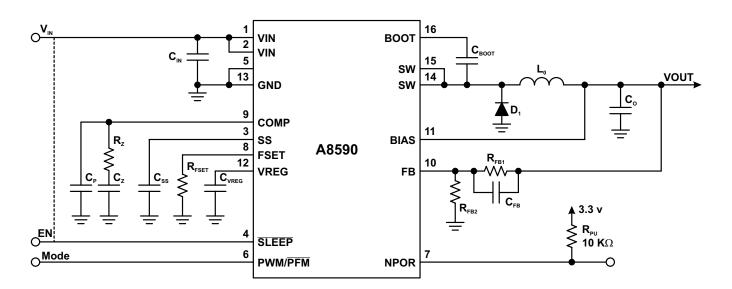

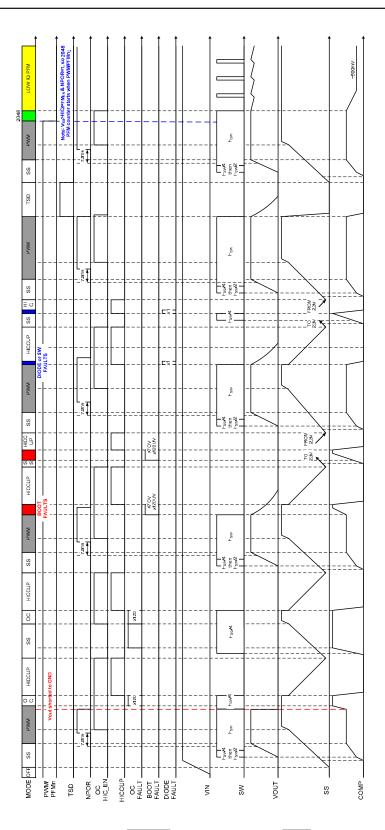

**Functional Block Diagram**

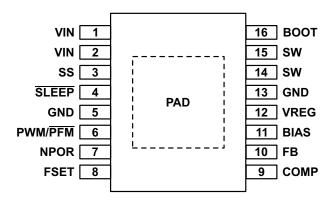

#### PINOUT DIAGRAM AND TERMINAL LIST TABLE

Package LP, 16-Pin TSSOP Pinout Diagram

#### **Terminal List Table**

| Name    | Number | Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIAS    | 11     | Bias input, supplies internal circuitry.                                                                                                                                                                                                                                                                                                                                                                      |

| воот    | 16     | High-side gate drive boost input. This pin supplies the drive for the high-side N-channel MOSFET. Connect a 47 nF ceramic capacitor from BOOT to SW.                                                                                                                                                                                                                                                          |

| COMP    | 9      | Output of the error amplifier and compensation node for the current mode control loop. Connect a series RC network from this pin to GND for loop compensation. See the Design and Component Selection section of this datasheet for further details.                                                                                                                                                          |

| FB      | 10     | Feedback (negative) input to the error amplifier. Connect a resistor divider from the regulator output, VOUT, to this pin to program the output voltage.                                                                                                                                                                                                                                                      |

| FSET    | 8      | Frequency setting pin. A resistor, R <sub>FSET</sub> , from this pin to GND sets the base PWM switching frequency (f <sub>OSC</sub> ). See the Design and Component Selection section for information on determining the value of R <sub>FSET</sub> .                                                                                                                                                         |

| GND     | 5, 13  | Ground pins.                                                                                                                                                                                                                                                                                                                                                                                                  |

| NPOR    | 7      | Active low, power-on reset output signal. This pin is an open drain output that transitions from low to high impedance after the output has maintained regulation for t <sub>D(NPOR)</sub> ).                                                                                                                                                                                                                 |

| PAD     | -      | Exposed pad of the package providing enhanced thermal dissipation. This pad must be connected to the ground plane(s) of the PCB with at least 6 vias, directly in the pad land.                                                                                                                                                                                                                               |

| PWM/PFM | 6      | Sets operating output mode ( $f_{SW}$ ). Setting this pin low forces Low- $I_Q$ PFM mode ( $f_{SW}$ set by load). Setting this pin high forces PWM mode switching at the base frequency ( $f_{OSC}$ ), set by $R_{FSET}$ . Applying an external clock input to this pin forces synchronization of PWM to the clock input rate ( $f_{SYNC}$ ), at a rate higher than $f_{OSC}$ . SLEEP low overrides this pin. |

| SLEEP   | 4      | Setting this pin low forces sleep mode (very low current shutdown mode: V <sub>OUT</sub> = 0 V). This pin must be set high to enable the A8590. If the application does not require a sleep mode, then this pin can be tied directly to VIN. Do not float this pin                                                                                                                                            |

| SS      | 3      | Soft-start and hiccup pin. Connect a capacitor, $C_{SS}$ , from this pin to GND to set soft-start mode duration. The capacitor also determines the hiccup period during overcurrent.                                                                                                                                                                                                                          |

| SW      | 14, 15 | The source of the high-side N-channel MOSFET. The external free-wheeling diode (D1) and output inductor ( $L_O$ ) should be connected to this pin. Both D1 and $L_O$ should be placed close to this pin and connected with relatively wide traces.                                                                                                                                                            |

| VIN     | 1, 2   | Power input for the control circuits and the drain of the high-side N-channel MOSFET. Connect this pin to a power supply providing from 4.0 to 35 V. A high quality ceramic capacitor should be placed and grounded very close to this pin.                                                                                                                                                                   |

| VREG    | 12     | Internal voltage regulator bypass capacitor pin. Connect a 1 µF ceramic capacitor from this pin to ground and place it very close to the A8590.                                                                                                                                                                                                                                                               |

#### ELECTRICAL CHARACTERISTICS: Valid at 4.0 V $\leq$ V<sub>IN</sub> $\leq$ 35 V, $-40^{\circ}$ C $\leq$ T<sub>A</sub> = T<sub>J</sub> $\leq$ 150°C,unless otherwise specified

| Characteristics                                                    | Symbol                                | Test Conditions                                                                                                                                                    | Min. | Тур.  | Max. | Unit               |

|--------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|--------------------|

| INPUT VOLTAGE                                                      |                                       |                                                                                                                                                                    |      | •     |      |                    |

| Input Voltage Range [1]                                            | V <sub>IN</sub>                       |                                                                                                                                                                    | 4.0  | _     | 35   | V                  |

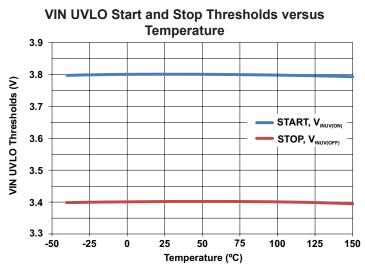

| VIN UVLO Start                                                     | V <sub>INUV(ON)</sub>                 | V <sub>IN</sub> rising                                                                                                                                             | 3.6  | 3.8   | 4.0  | V                  |

| VIN UVLO Stop                                                      | V <sub>INUV(OFF)</sub>                | V <sub>IN</sub> falling                                                                                                                                            | 3.2  | 3.4   | 3.6  | V                  |

| VIN UVLO Hysteresis                                                | V <sub>INUV(HYS)</sub>                |                                                                                                                                                                    | _    | 400   | _    | mV                 |

| INPUT SUPPLY CURRENT                                               | · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                    |      |       |      |                    |

| OL M - I - I + O I - O + [2][5]                                    |                                       | V <sub>SLEEP</sub> ≤ 0.5 V, T <sub>J</sub> = 85°C, V <sub>IN</sub> = 16 V                                                                                          | _    | 5     | 15   | μA                 |

| Sleep Mode Input Supply Current [2][5]                             | IN(SLEEP)                             | V <sub>SLEEP</sub> ≤ 0.5 V, T <sub>J</sub> = 85°C, V <sub>IN</sub> = 35 V                                                                                          | _    | 7     | 25   | μA                 |

| PWM Mode Input Supply Current [2]                                  | I <sub>IN(PWM)</sub>                  | V <sub>BIAS</sub> > 3.2 V, I <sub>OUT</sub> = 0 mA                                                                                                                 | _    | 2.5   | 5.0  | mA                 |

|                                                                    |                                       | $V_{\text{IN}}$ = 12 V, $V_{\text{OUT}}$ = 3.3 V, $V_{\text{PWM/PFM}} \le$ 0.8 V, $I_{\text{OUT}}$ = 40 μA, $T_{\text{A}}$ = 25°C, components selected per Table 3 | -    | _     | 50   | μА                 |

| Low-I <sub>Q</sub> PFM Input Supply Current [2][3]                 | I <sub>LO_IQ(1)</sub>                 | $V_{\text{IN}}$ = 12 V, $V_{\text{OUT}}$ = 5.0 V, $V_{\text{PWM/PFM}}$ ≤ 0.8 V, $I_{\text{OUT}}$ = 200 μA, $T_{\text{A}}$ = 25°C, components selected per Table 3  | -    | -     | 250  | μА                 |

|                                                                    |                                       | $V_{\rm IN}$ = 12 V, $V_{\rm OUT}$ = 6.5 V, $V_{\rm PWM/PFM}$ ≤ 0.8 V, $I_{\rm OUT}$ = 1 mA, $T_{\rm A}$ = 25°C, components selected per Table 3                   | -    | _     | 750  | μА                 |

| VOLTAGE REGULATION                                                 | `                                     | •                                                                                                                                                                  |      |       |      |                    |

| Foodback Valtage Assurably [4]                                     | V <sub>FB</sub>                       | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}, \text{V}_{\text{IN}} \ge 4.1 \text{ V}, \text{V}_{\text{FB}} = \text{V}_{\text{COMP}}$              | 792  | 800   | 808  | mV                 |

| Feedback Voltage Accuracy [4]                                      |                                       | $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \text{V}_{\text{IN}} \ge 4.1 \text{ V}, \text{V}_{\text{FB}} = \text{V}_{\text{COMP}}$           | 788  | 800   | 812  | mV                 |

| Low-I <sub>Q</sub> PFM Mode Output Voltage<br>Setting Range [1][3] | V <sub>OUT(LO_IQ)</sub>               | $3.0~{ m V} < { m V}_{ m BIAS} < 5.5~{ m V}$ and ${ m I}_{ m LO\_IQ}$ specifications satisfied                                                                     | 3.3  | _     | 6.5  | V                  |

| PWM Output Voltage Setting Range [3]                               | V <sub>OUT</sub>                      | V <sub>BIAS</sub> = GND, PWM only, no PFM mode                                                                                                                     | 8.0  | _     | 10   | V                  |

|                                                                    |                                       | $T_A$ = 85°C, DCR <sub>LO</sub> $\leq$ 75 m $\Omega$ , $V_{IN}$ = 3.6 V, $I_{OUT}$ = 1 A, $f_{SW}$ = 425 kHz                                                       | 3.27 | 3.295 | _    | V                  |

| Outrot Drawaut Valtage [2]                                         | .,                                    | $T_A$ = 85°C, DCR <sub>LO</sub> $\leq$ 75 m $\Omega$ , V <sub>IN</sub> = 5.3 V, I <sub>OUT</sub> = 1 A, f <sub>SW</sub> = 425 kHz                                  | 4.95 | 5.0   | -    | V                  |

| Output Dropout Voltage [3]                                         | V <sub>OUT(SAT)</sub>                 | $T_A$ = 85°C, DCR <sub>LO</sub> $\leq$ 50 m $\Omega$ , V <sub>IN</sub> = 3.75 V, I <sub>OUT</sub> = 1 A, f <sub>SW</sub> = 2 MHz                                   | 3.25 | 3.3   | _    | ٧                  |

|                                                                    |                                       | $T_A$ = 85°C, DCR <sub>LO</sub> $\leq$ 50 m $\Omega$ , $V_{IN}$ = 5.5 V, $I_{OUT}$ = 1 A, $f_{SW}$ = 2 MHz                                                         | 4.89 | 5.0   | -    | V                  |

| Low-I <sub>Q</sub> PFM Mode Ripple Voltage [3]                     | $\Delta V_{OUT(LO\_IQ)}$              | 8 V < V <sub>IN</sub> < 12 V, components selected per Table 3                                                                                                      | _    | 30    | 65   | mV <sub>PP</sub>   |

| Low-I <sub>Q</sub> PFM Mode Peak Current                           | 1                                     | f <sub>SW</sub> < 750 kHz                                                                                                                                          | _    | 750   | _    | mA <sub>PEAK</sub> |

| Threshold                                                          | I <sub>PEAK(LO_IQ)</sub>              | f <sub>SW</sub> > 750 kHz                                                                                                                                          | _    | 850   | _    | mA <sub>PEAK</sub> |

| Low-I <sub>Q</sub> PFM Mode DC Load Current [3]                    | I <sub>OUT(LO_IQ)</sub>               | Maximum load to maintain $\Delta V_{OUT(LO\_IQ)}$ , components selected per Table 3                                                                                | 400  | 550   | 700  | mA                 |

Continued on next page...

<sup>[1]</sup> Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>[2]</sup> Negative current is defined as coming out of the node or pin, positive current is defined as going into the node or pin.

<sup>[3]</sup> Ensured by design and characterization, not production tested.

<sup>[4]</sup> Performance at the 0°C and 85°C ranges ensured by design and characterization, not production tested.

<sup>[5]</sup> Performance at 85°C ensured by design and characterization, not production tested.

## Wide Input Voltage, 2.4 MHz, 3.0 Amp Asynchronous Buck Regulator With Low-I<sub>Q</sub> Standby, Sleep Mode, External Synchronization, and NPOR Output

#### ELECTRICAL CHARACTERISTICS (continued): Valid at $4.0 \text{ V} \le V_{\text{IN}} \le 35 \text{ V}$ , $-40^{\circ}\text{C} \le T_{\text{A}} = T_{\text{J}} \le 150^{\circ}\text{C}$ , unless otherwise specified

| Characteristics Symbol Test Condition |                          | Test Conditions                                                                                                   | Min.                            | Тур. | Max.                         | Unit |

|---------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------------------------------|------|

| ERROR AMPLIFIER                       | *                        |                                                                                                                   |                                 |      | •                            |      |

| Feedback Input Bias Current [7]       | I <sub>FB</sub>          |                                                                                                                   | -38                             | _    | -16                          | nA   |

| Open Loop Voltage Gain                | A <sub>VOL</sub>         | V <sub>COMP</sub> = 1.2 V                                                                                         | _                               | 65   | _                            | dB   |

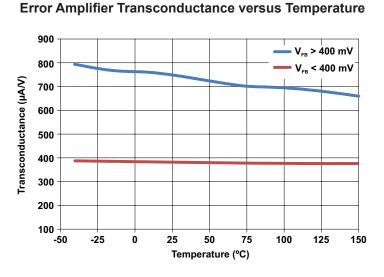

| Tononomedicatorio                     | _                        | 400 mV < V <sub>FB</sub>                                                                                          | 500                             | 750  | 950                          | μA/V |

| Transconductance                      | g <sub>m</sub>           | 0 V < V <sub>FB</sub> < 400 mV                                                                                    | 275                             | 375  | 475                          | μA/V |

| Output Current                        | I <sub>EA</sub>          | V <sub>COMP</sub> = 1.2 V                                                                                         | _                               | ±75  | _                            | μΑ   |

| COMP Pull-Down Resistance             | R <sub>COMP</sub>        | FAULT = 1 or HICCUP = 1                                                                                           | _                               | 1    | _                            | kΩ   |

| PULSE WIDTH MODULATION (PWM           |                          |                                                                                                                   |                                 |      | •                            |      |

| PWM Ramp Offset                       | V <sub>PWMOFFS</sub>     | V <sub>COMP</sub> level required for 0% duty cycle                                                                | _                               | 400  | _                            | mV   |

| Minimum Controllable PWM On-Time      | t <sub>ON(MIN)</sub> PWM | 12 V < V <sub>IN</sub> < 16 V, I <sub>OUT</sub> = 1 A, V <sub>BOOT</sub> - V <sub>SW</sub> = 4.5 V                | -                               | 95   | 135                          | ns   |

| Minimum Switch Off-Time               | t <sub>OFF(MIN)PWM</sub> |                                                                                                                   | _                               | 95   | 130                          | ns   |

| COMP to SW Current Gain               | 9 <sub>mPOWER</sub>      |                                                                                                                   | _                               | 4.0  | _                            | A/V  |

|                                       |                          | f <sub>OSC</sub> = 2.44 MHz                                                                                       | 2.31                            | 3.30 | 4.30                         | A/µs |

| Slope Compensation [8]                | S <sub>E</sub>           | f <sub>OSC</sub> = 1.00 MHz                                                                                       | 0.66                            | 1.00 | 1.32                         | A/µs |

|                                       |                          | f <sub>OSC</sub> = 252 kHz                                                                                        | 0.15                            | 0.22 | 0.29                         | A/µs |

| MOSFET PARAMETERS [6]                 |                          |                                                                                                                   |                                 |      |                              |      |

| High-Side MOSFET On-Resistance [9]    | R <sub>DS(on)HS</sub>    | $T_J = 25^{\circ}C$ , $V_{BOOT} - V_{SW} = 4.5 \text{ V}$ , $I_{DS} = 0.4 \text{ A}$                              | -                               | 110  | 125                          | mΩ   |

| High-Side MOSFET On-Resistance        |                          | $T_J = 150$ °C, $V_{BOOT} - V_{SW} = 4.5$ V, $I_{DS} = 0.4$ A                                                     | _                               | 190  | 215                          | mΩ   |

| High-Side MOSFET Leakage [7][10]      | I <sub>Ikg(HS)</sub>     | $T_J < 85^{\circ}C$ , $V_{\overline{SLEEP}} \le 0.5 \text{ V}$ , $V_{SW} = 0 \text{ V}$ , $V_{IN} = 16 \text{ V}$ | _                               | -    | 10                           | μA   |

| Tilgii-Side WOSFET Leakage Fixes      |                          | $T_J \le 150$ °C, $V_{\overline{SLEEP}} \le 0.5 \text{ V}$ , $V_{SW} = 0 \text{ V}$ , $V_{IN} = 16 \text{ V}$     | _                               | 60   | 150                          | μΑ   |

| SW Node Slew Rate [8]                 | SR <sub>SW</sub>         | 12 V < V <sub>IN</sub> < 16 V                                                                                     | _                               | 0.72 | _                            | V/ns |

| Low-Side MOSFET On-Resistance [9]     | R <sub>DS(on)LS</sub>    | $T_J = 25^{\circ}C, V_{IN} \ge 6 \text{ V}, I_{DS} = 0.1 \text{ A}$                                               | _                               | _    | 10                           | Ω    |

| PWM SWITCHING FREQUENCY               |                          |                                                                                                                   |                                 |      |                              |      |

|                                       |                          | $R_{FSET} = 8.06 \text{ k}\Omega, V_{PWM/\overline{PFM}} = \text{high}$                                           | 2.20                            | 2.44 | 2.70                         | MHz  |

| Base PWM Switching Frequency          | fosc                     | $R_{FSET} = 23.7 \text{ k}\Omega, V_{PWM/\overline{PFM}} = \text{high}$                                           | 0.90                            | 1.00 | 1.10                         | MHz  |

|                                       |                          | $R_{FSET} = 102 \text{ k}\Omega, V_{PWM/\overline{PFM}} = \text{high}$                                            | _                               | 252  | _                            | kHz  |

| PWM SYNCHRONIZATION TIMING            |                          |                                                                                                                   |                                 |      |                              |      |

| Synchronization Frequency Range       | f <sub>SYNC(MULT)</sub>  |                                                                                                                   | 1.2 ×<br>f <sub>OSC</sub> (typ) | _    | 1.5 × f <sub>OSC</sub> (typ) | _    |

| Synchronized PWM Frequency            | f <sub>SYNC(PWM)</sub>   |                                                                                                                   | _                               | _    | 2.9                          | MHz  |

| Synchronization Input Duty Cycle      | D <sub>SYNC</sub>        |                                                                                                                   | _                               |      | 80                           | %    |

| Synchronization Input Pulse Width     | t <sub>wSYNC</sub>       |                                                                                                                   | 200                             | _    | _                            | ns   |

| Synchronization Input Rise Time [8]   | t <sub>rSYNC</sub>       |                                                                                                                   | _                               | 10   | 15                           | ns   |

| Synchronization Input Fall Time [8]   | t <sub>fSYNC</sub>       |                                                                                                                   | _                               | 10   | 15                           | ns   |

Continued on next page...

<sup>[6]</sup> Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>[7]</sup> Negative current is defined as coming out of the node or pin, positive current is defined as going into the node or pin.

<sup>[8]</sup> Ensured by design and characterization, not production tested.

<sup>[9]</sup> Performance at 25°C ensured by design and characterization, not production tested.

<sup>[10]</sup> Performance at 85°C ensured by design and characterization, not production tested.

# Wide Input Voltage, 2.4 MHz, 3.0 Amp Asynchronous Buck Regulator With Low-I<sub>Q</sub> Standby, Sleep Mode, External Synchronization, and NPOR Output

### ELECTRICAL CHARACTERISTICS (continued): Valid at 4.0 V $\leq$ V<sub>IN</sub> $\leq$ 35 V, $-40^{\circ}$ C $\leq$ T<sub>A</sub> = T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics                                      | Symbol                      | Test Conditions                                                                                                                                           | Min. | Тур.              | Max. | Unit   |

|------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|------|--------|

| PWM/PFM PIN INPUT THRESHOLD                          | S                           |                                                                                                                                                           |      |                   |      |        |

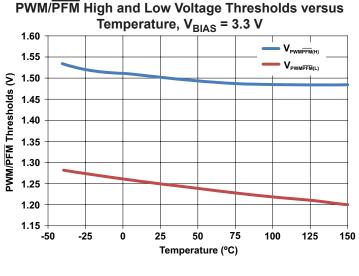

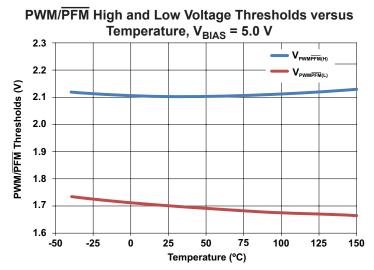

| PWM/PFM High Threshold                               | \ \                         | 3.0 V < V <sub>BIAS</sub> < 3.6 V, V <sub>PWM/PFM</sub> rising                                                                                            | _    | _                 | 2.0  | V      |

| PWW/PFW High Threshold                               | $V_{PWM/\overline{PFM}(H)}$ | 4.5 V < V <sub>BIAS</sub> < 5.5 V, V <sub>PWM/PFM</sub> rising                                                                                            | _    | _                 | 2.6  | V      |

| PWM/PFM Low Threshold                                |                             | 3.0 V < V <sub>BIAS</sub> < 3.6 V, V <sub>PWM/PFM</sub> falling                                                                                           | 0.8  | _                 | _    | V      |

| PWM/PFM Low Inreshold                                | $V_{PWM/\overline{PFM}(L)}$ | 4.5 V < V <sub>BIAS</sub> < 5.5 V, V <sub>PWM/PFM</sub> falling                                                                                           | 1.2  | -                 | _    | V      |

| PWM/PFM Hysteresis                                   |                             | $3.0 \text{ V} < \text{V}_{\text{BIAS}} < 3.6 \text{ V}, \text{V}_{\text{PWM/}\overline{\text{PFM}}(H)} - \text{V}_{\text{PWM/}\overline{\text{PFM}}(L)}$ | _    | 200               | _    | mV     |

| FWW/FFW Hysteresis                                   | V <sub>PWM/PFMhys</sub>     | $4.5 \text{ V} < \text{V}_{\text{BIAS}} < 5.5 \text{ V}, \text{V}_{\text{PWM/}\overline{\text{PFM}}(H)} - \text{V}_{\text{PWM/}\overline{\text{PFM}}(L)}$ | _    | 400               | _    | mV     |

| PWM/PFM Input Resistance                             | R <sub>PWM/PFM</sub>        |                                                                                                                                                           | 120  | 200               | 280  | kΩ     |

| Low-I <sub>Q</sub> PFM Transition Delay              | t <sub>D(LO_IQ)</sub>       | PWM/PFM = low, V <sub>SS</sub> > V <sub>HIC/PFM(EN)</sub> ,<br>NPOR = high                                                                                | -    | 2048              | _    | counts |

| PFM MODE TIMING                                      |                             |                                                                                                                                                           |      |                   |      |        |

| Constant PFM Off-Time                                |                             | f <sub>OSC</sub> < 1.5 MHz                                                                                                                                | _    | 435               | _    | ns     |

| Constant Privi On-Time                               | t <sub>OFF(PFM)</sub>       | f <sub>OSC</sub> > 1.5 MHz                                                                                                                                | _    | 275               | _    | ns     |

| Maximum PFM On-Time                                  | t <sub>ON(PFM)MAX</sub>     |                                                                                                                                                           | _    | 4.1               | _    | μs     |

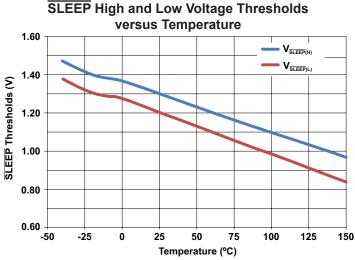

| SLEEP PIN INPUT THRESHOLDS                           |                             |                                                                                                                                                           |      |                   |      |        |

| SLEEP High Threshold                                 | V <sub>SLEEP(H)</sub>       | V <sub>SLEEP</sub> rising                                                                                                                                 | _    | 1.3               | 2.1  | V      |

| SLEEP Low Threshold                                  | V <sub>SLEEP(L)</sub>       | V <sub>SLEEP</sub> falling                                                                                                                                | 0.5  | 1.2               | _    | V      |

| SLEEP Delay                                          | t <sub>D(SLEEP)</sub>       | V <sub>SLEEP</sub> transitioning low                                                                                                                      | 55   | 103               | 150  | μs     |

| SLEEP Input Bias Current                             | I <sub>SLEEPBIAS</sub>      | V <sub>SLEEP</sub> = 5 V                                                                                                                                  | -    | 500               | _    | nA     |

| VREG PIN OUTPUT                                      |                             |                                                                                                                                                           |      |                   |      |        |

| VREG Output Voltage                                  | $V_{VREG}$                  | V <sub>BIAS</sub> = 0 V                                                                                                                                   | -    | 3.05              | _    | V      |

| BIAS Input Voltage Range                             | V <sub>BIAS</sub>           |                                                                                                                                                           | 3.2  | _                 | 5.5  | V      |

| BOOT REGULATOR                                       |                             |                                                                                                                                                           |      |                   |      |        |

| BOOT Voltage Enable Threshold                        | V <sub>BOOT(EN)</sub>       | V <sub>BOOT</sub> rising                                                                                                                                  | 1.7  | 2.0               | 2.2  | V      |

| BOOT Voltage Enable Hysteresis                       | V <sub>BOOT(HYS)</sub>      |                                                                                                                                                           | _    | 200               | _    | mV     |

| BOOT Voltage Low-Side Switch Disable Threshold       | V <sub>BOOTLS(DIS)</sub>    | V <sub>BOOT</sub> rising                                                                                                                                  | _    | 4.1               | _    | V      |

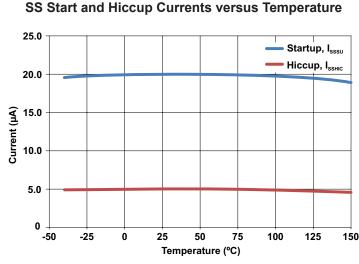

| SOFT-START PIN                                       |                             |                                                                                                                                                           |      |                   |      |        |

| FAULT, HICCUP Reset Voltage                          | V <sub>SSRST</sub>          | V <sub>SS</sub> falling due to RSS(FLT)                                                                                                                   | _    | 200               | 275  | mV     |

| Hiccup OCP (and Low IQ PFM Counter Enable) Threshold | V <sub>HIC/PFM(EN)</sub>    | V <sub>SS</sub> rising                                                                                                                                    | -    | 2.3               | _    | V      |

| Maximum Charge Voltage                               | V <sub>SS(MAX)</sub>        |                                                                                                                                                           | _    | V <sub>VREG</sub> | _    | _      |

| Startup (Source) Current                             | I <sub>SSSU</sub>           | HICCUP = FAULT = 0                                                                                                                                        | -30  | -20               | -10  | μA     |

| Hiccup (Sink) Current                                | I <sub>SSHIC</sub>          | HICCUP = 1                                                                                                                                                | 2.4  | 5                 | 10   | μA     |

| Pull-Down Resistance                                 | R <sub>SS(FLT)</sub>        | FAULT = 1 or V <sub>SLEEP</sub> = low                                                                                                                     | _    | 2                 | _    | kΩ     |

Continued on next page...

## Wide Input Voltage, 2.4 MHz, 3.0 Amp Asynchronous Buck Regulator With Low-I<sub>Q</sub> Standby, Sleep Mode, External Synchronization, and NPOR Output

### ELECTRICAL CHARACTERISTICS (continued): Valid at $4.0 \text{ V} \le \text{V}_{\text{IN}} \le 35 \text{ V}, -40 ^{\circ}\text{C} \le \text{T}_{\text{A}} = \text{T}_{\text{J}} \le 150 ^{\circ}\text{C}, \text{ unless otherwise specified}$

| Characteristics                                   | Symbol                   | Symbol Test Conditions                                           |     | Тур.                | Max. | Unit   |

|---------------------------------------------------|--------------------------|------------------------------------------------------------------|-----|---------------------|------|--------|

| SOFT-START PIN (continued)                        |                          |                                                                  |     |                     |      |        |

|                                                   |                          | 0 V < V <sub>FB</sub> < 200 mV                                   | _   | f <sub>OCS</sub> /4 | -    | _      |

| Soft-Start Frequency Foldback                     | f <sub>SW(SS)</sub>      | 200 mV < V <sub>FB</sub> < 400 mV                                | _   | f <sub>OCS</sub> /2 | _    | _      |

|                                                   |                          | 400 mV < V <sub>FB</sub>                                         | _   | focs                | _    | _      |

| Soft-Start Delay Time [12]                        | t <sub>D(SS)</sub>       | C <sub>SS</sub> = 22 nF                                          | _   | 440                 | _    | μs     |

| Soft-Start Output Ramp Time [12]                  | t <sub>SS</sub>          | C <sub>SS</sub> = 22 nF                                          | _   | 880                 | -    | μs     |

| HICCUP MODES                                      |                          |                                                                  |     |                     |      |        |

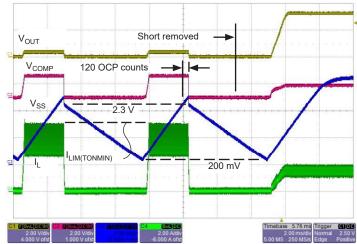

| Hiccup, OCP Count                                 | OCP <sub>LIM</sub>       | V <sub>SS</sub> > 2.3 V and OCL = 1                              | _   | 120                 | _    | counts |

| Hiccup, BOOT Undervoltage (Shorted) Count         | BOOT <sub>UV</sub>       |                                                                  | _   | 120                 | _    | counts |

| Hiccup, BOOT Overvoltage (Open) Count             | BOOT <sub>OV</sub>       |                                                                  | _   | 7                   | _    | counts |

| Overcurrent Protection (OCP)                      |                          |                                                                  |     |                     |      |        |

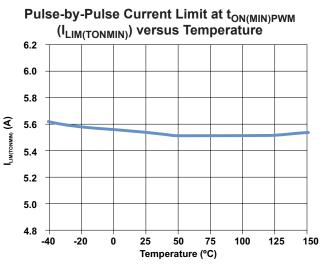

|                                                   | I <sub>LIM(TONMIN)</sub> | $t_{ON} = t_{ON(MIN)PWM}$                                        | 4.8 | 5.5                 | 6.1  | А      |

| PWM Pulse-by-Pulse Limit                          | I <sub>LIM(TONMAX)</sub> | $t_{ON} = (1/f_{SW}) - t_{OFF(MIN)PWM}$ , no PWM synchronization | 3.0 | 4.1                 | 5.1  | А      |

| OUTPUT VOLTAGE PROTECTION (                       | OVP)                     |                                                                  |     |                     |      |        |

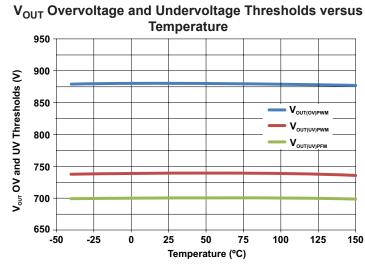

| VOUT Overvoltage PWM Threshold                    | V <sub>OUT(OV)PWM</sub>  | V <sub>FB</sub> rising, PWM mode                                 | 860 | 880                 | 902  | mV     |

| VOUT Overvoltage Hysteresis                       | V <sub>OUT(OV)HYS</sub>  | V <sub>FB</sub> falling, relative to V <sub>OUT(OV)PWM</sub>     | _   | -10                 | _    | mV     |

| VOUT Undervoltage PWM Threshold                   | V <sub>OUT(UV)PWM</sub>  | V <sub>FB</sub> falling, PWM mode                                | 715 | 740                 | 765  | mV     |

| VOUT Undervoltage Hysteresis                      | V <sub>OUT(UV)HYS</sub>  | V <sub>FB</sub> rising, relative to V <sub>OUT(UV)PWM</sub>      | _   | 10                  | 1    | mV     |

| VOUT Undervoltage PFM Threshold                   | V <sub>OUT(UV)PFM</sub>  | V <sub>FB</sub> falling, Low-IQ PFM mode                         | 665 | 700                 | 735  | mV     |

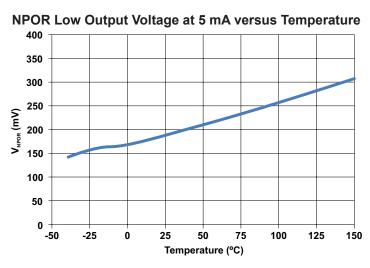

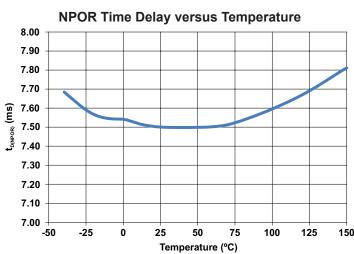

| POWER-ON RESET (NPOR) OUTPU                       | IT                       |                                                                  |     |                     |      |        |

| NPOR Rising Delay                                 | t <sub>D(NPOR)</sub>     | V <sub>FB</sub> rising only                                      | 5   | 7.5                 | 10   | ms     |

| NPOR Low Output Voltage                           | V <sub>NPOR(L)</sub>     | I <sub>NPOR</sub> = 5 mA                                         | _   | 185                 | 400  | mV     |

| NPOR Leakage Current [11]                         | I <sub>NPOR(LKG)</sub>   | V <sub>NPOR</sub> = 5.5 V                                        | -1  | _                   | 1    | μΑ     |

| THERMAL PROTECTION                                |                          |                                                                  |     |                     |      |        |

| Thermal Shutdown Rising Threshold <sup>[12]</sup> | T <sub>SD</sub>          | PWM stops immediately and COMP and SS are pulled low             | 155 | 170                 | 185  | °C     |

| Thermal Shutdown Hysteresis [12]                  | T <sub>SDHYS</sub>       |                                                                  | _   | 20                  | _    | °C     |

<sup>[11]</sup> Negative current is defined as coming out of the node or pin, positive current is defined as going into the node or pin. [12] Ensured by design and characterization, not production tested.

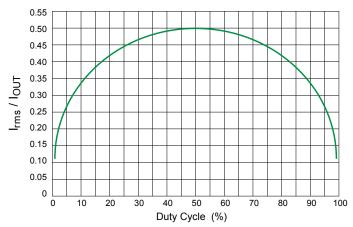

#### **CHARACTERISTIC PERFORMANCE**

#### FUNCTIONAL DESCRIPTION

#### Overview

The A8590 is an asynchronous current-mode buck regulator that incorporates all the control and protection circuitry necessary to provide the power supply requirements of car audio and infotainment systems.

The A8590 has three modes of operation. First, the A8590 can deliver up to 3.0 A in pulse width modulation (PWM) mode. Second, in Low- $I_Q$  pulse frequency modulation (PFM) mode, the A8590 will draw only tens of microamperes from  $V_{IN}$  while maintaining  $V_{OUT}$  (at no load). Under most conditions, Low- $I_Q$  PFM mode is typically capable of supporting up to 550 mA. Third, with the  $\overline{SLEEP}$  pin low, the A8590 will enter an ultra-low current shutdown (sleep) mode where  $V_{OUT}=0$  V and the total current drawn from  $V_{IN}$  will typically be less than 10  $\mu A$ .

The PWM/ $\overline{PFM}$  input pin is used to select either PWM or Low-IQ PFM mode. In PFM mode, the A8590 is able to supply a relatively high amount of current (typically 550 mA). This allows enough current for a microcontroller or DSP to fully power-up. After power-up, to obtain the full current capability of the A8590, the microcontroller or DSP must change the PWM/ $\overline{PFM}$  input from a logic low to a logic high to force PWM mode. This will provide full current to the remainder of the system.

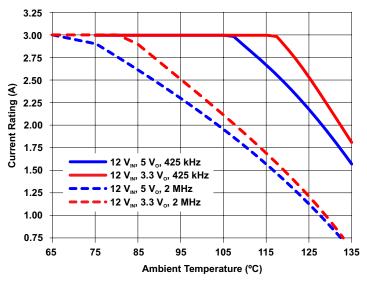

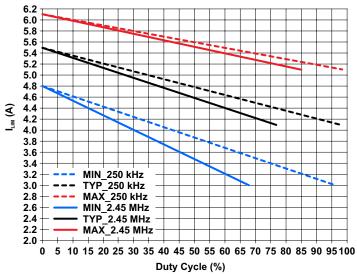

The A8590 was designed to support up to 3.0 A. However, the exact amount of current it will supply, before possible thermal shutdown, depends heavily on: duty cycle, ambient temperature,

Figure 1: A8590 Typical Current Derating

airflow, PCB layout, and PCB construction. Figure 1 shows calculated current ratings versus ambient temperature for  $V_{IN} = 12$  V, and  $V_{OUT} = 3.3$  V and 5.0 V, at both  $f_{SW} = 425$  kHz and  $f_{SW} = 2$  MHz. This analysis assumed a 4-layer PCB constructed according to the JEDEC standard (yielding a thermal resistance of 34°C/W), with no nearby heat sources, and no airflow.

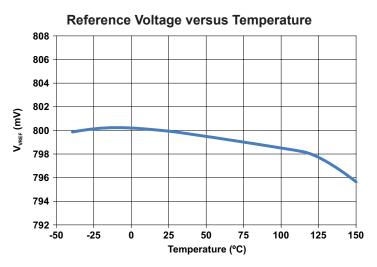

#### Reference Voltage

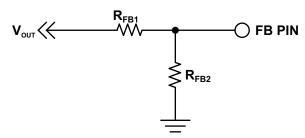

The A8590 incorporates an internal reference that allows output voltages ( $V_{OUT}$ ) as low as 0.8 V. The accuracy of the internal reference is  $\pm 1.0\%$  from 0°C to 85°C and  $\pm 1.5\%$  from -40°C to 150°C. The output voltage is programmed by connecting a resistor divider from VOUT to the FB pin of the A8590, as shown in the Typical Applications schematics.

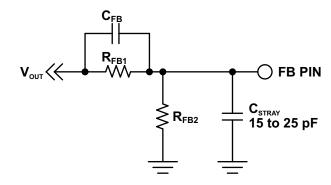

#### PWM Switching Frequency

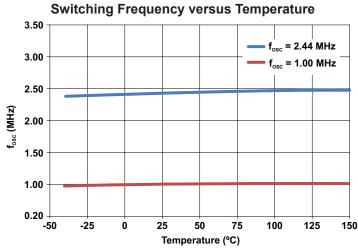

The PWM switching frequency of the A8590 is adjustable from 250 kHz to 2.4 MHz and has an accuracy of about  $\pm 10\%$  across the operating temperature range.

During startup, the PWM switching frequency changes from 25% to 50% and finally to 100% of  $f_{OSC}$ , as  $V_{OUT}$  rises from 0 V to the regulation voltage. The startup switching frequency is discussed in more detail in the section describing soft-start, below.

If the regulator output is shorted to ground,  $V_{FB} \approx 0$  V, the PWM frequency will be 25% of  $f_{OSC}.$  In this case, the extra-low switching frequency allows extra off-time between SW pulses. The extra off-time allows the output inductor current to decay back to 0 A before the next SW pulse occurs. This prevents the inductor current from climbing to a value that could damage the A8590 or the output inductor.

### **SLEEP** Input

The A8590 has a SLEEP logic level input pin. To get the A8590 to operate, the SLEEP pin must be a logic high (>2.1 V). The SLEEP pin is rated to 40 V, allowing the SLEEP pin to be connected directly to VIN if there is no suitable logic signal available to wake up the A8590.

When SLEEP transitions low, the A8590 waits approximately 103 µs before shutting down. This delay provides plenty of filtering to prevent the A8590 from prematurely entering sleep mode because of any small glitch coupling onto the PCB trace or SLEEP pin.

### PWM/PFM Input and PWM Synchronization

The PWM/PFM pin provides two major functions: a control input that sets the operating mode and an optional clock input for setting PWM frequency.

If PWM/ $\overline{PFM}$  is a logic high, the A8590 operates in PWM mode. If PWM/ $\overline{PFM}$  is a logic low, the A8590 operates in Low-I<sub>Q</sub> PFM (keep alive) mode. When PWM/ $\overline{PFM}$  transitions from logic high to logic low, the A8590 checks for V<sub>SS</sub> >2.3 V and NPOR at logic high. If these two conditions are satisfied, then the A8590 will wait 2048 internal clock cycles and then enter Low-I<sub>Q</sub> PFM mode. This delay provides plenty of filtering to prevent the regulator from prematurely entering PFM mode because of any small glitch coupling onto the PCB trace or PWM/ $\overline{PFM}$  pin.

Also, note that the  $\overline{\text{SLEEP}}$  pin must be a logic high or the PWM/ $\overline{\text{PFM}}$  input has no effect. The interaction between the  $\overline{\text{SLEEP}}$  pin and PWM/ $\overline{\text{PFM}}$  pin is summarized in Table 1.

Table 1: A8590 Modes of Operation

| Pin II | nputs      | Operating Mode |                                                    |                                                                    |  |

|--------|------------|----------------|----------------------------------------------------|--------------------------------------------------------------------|--|

| SLEEP  | PWM/PFM    | Name           | Description                                        |                                                                    |  |

| Low    | Don't Care | Sleep          | V <sub>OUT</sub>                                   | = 0 V                                                              |  |

| High   | High       |                | $f_{SW} = f_{OSC}$                                 |                                                                    |  |

| High   |            | PWM            | f <sub>SW_</sub> =<br>PWM/PFM<br>clock in          | V <sub>OUT</sub> = OK<br>and<br>I <sub>OUT</sub> ≤ 3.0 A           |  |

| High   |            |                | ow-I <sub>Q</sub> PFM after 2<br>2.3 V (typ) and N |                                                                    |  |

| High   | Low        | Low-IQ<br>PFM  | f <sub>SW</sub> is VOUT<br>dependent               | V <sub>OUT</sub> = OK<br>and<br>I <sub>OUT</sub> ≤ 550 mA<br>(typ) |  |

| High   | :ow        | Low-IP<br>PWM  | Fault, I <sub>LIM</sub> at 50%                     |                                                                    |  |

If an external clock is applied to the PWM/ $\overline{PFM}$  pin, the A8590 synchronizes its PWM frequency to the external clock. The external clock may be used to increase the A8590 base PWM frequency (f<sub>OSC</sub>) set by R<sub>FSET</sub>. Synchronization operates from 1.2 × f<sub>OSC</sub>(typ) to 1.5 × f<sub>OSC</sub>(typ) . The external clock pulses must satisfy the pulse width, duty cycle, and rise/fall time requirements shown in the Electrical Characteristics table in this datasheet.

### BIAS Input Functionality, Ratings, and Connections

When the A8590 is powering up, it operates from an internal LDO regulator, directly from VIN. However,  $V_{\rm IN}$  can be a relatively high voltage and an LDO is very inefficient and generates extra heat. To improve efficiency, especially in Low-I<sub>Q</sub> PFM mode, a BIAS pin is used. For most applications, the BIAS pin should be connected directly to the output of the regulator,  $V_{\rm OUT}$ . When  $V_{\rm OUT}$  rises to an adequate level (approximately 3.1 V), the A8590 will shut down the inefficient LDO and begin running its control circuitry directly from the output of the regulator. This makes the A8590 much more efficient and cooler.

The BIAS pin is designed to operate in the range from 3.2 to 5.5 V. If the output of the regulator is in this range, then  $V_{OUT}$  should be routed directly to the BIAS pin. However, if the output of the regulator is above 5.6 V then a very small LDO, capable of at least 5 mA, must be used to reduce the voltage to either 3.3 V or 5.0 V before routing it to the BIAS pin. Operating with an external LDO will reduce the efficiency in Low-I $_{\rm O}$  PFM mode.

The BIAS pin may be driven by an external power supply. For startup, there are no sequencing requirements between VIN and BIAS. However, for shutdown, VIN should be removed before BIAS. If BIAS is removed before VIN, it will cause the A8590 to reset. The reset will cause the A8590 to terminate PWM switching and  $V_{OUT}$  will decay. Also, NPOR,  $V_{SS}$ , and  $V_{COMP}$  will be pulled low. Ideally, the  $\overline{SLEEP}$  pin should be used to set the mode of the A8590 before VIN and/or BIAS are turned on or off.

If the BIAS pin is grounded, the A8590 will simply operate continuously from VIN. However, during PFM mode, the input current will increase, and the PFM efficiency will be significantly reduced.

#### **Transconductance Error Amplifier**

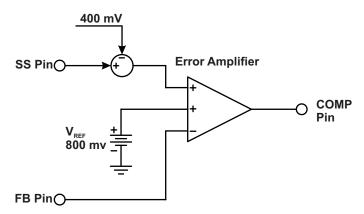

The transconductance error amplifier primary function is to control the regulator output voltage. The error amplifier is shown in Figure 2. Here, it is shown as a three-terminal input device with two positive and one negative input. The negative input is simply connected to the FB pin and is used to sense the feedback voltage for regulation. The two positive inputs are used for soft-start and steady-state regulation. The error amplifier performs an analog OR selection between its two positive inputs. The error amplifier regulates to either the soft-start pin voltage (minus 400 mV) or the A8590 internal reference,  $V_{\rm REF}$ , whichever is lower.

Figure 2: A8590 Error Amplifier

To stabilize the regulator, a series RC compensation network (R<sub>7</sub> and C<sub>7</sub>) must be connected from the error amplifier output (the COMP pin) to GND, as shown in the Typical Applications schematics. In most instances an additional, relatively low value, capacitor (C<sub>p</sub>) should be connected in parallel with the R<sub>Z</sub>-C<sub>Z</sub> components to reduce the loop gain at very high frequencies. However, if the C<sub>p</sub> capacitor is too large, the phase margin of the regulator may be reduced. Calculating  $R_Z$ ,  $C_Z$ , and  $C_P$  is covered in detail in the Component Selection section of this datasheet.

If a fault occurs or the regulator is disabled ( $\overline{\text{SLEEP}} = \text{low}$ ), the COMP pin is pulled to GND via approximately 1 k $\Omega$  and PWM switching is inhibited.

#### Slope Compensation

The A8590 incorporates internal slope compensation ( $S_E$ ) to allow PWM duty cycles above 50% for a wide range of input/output voltages and inductor values. The slope compensation signal is added to the sum of the current sense amplifier output and the PWM ramp offset. As shown in the Electrical Characteristics table, the amount of slope compensation scales with the base switching frequency set by R<sub>FSET</sub> (f<sub>OSC</sub>). The amount of slope compensation does not change when the regulator is synchronized to an external clock.

The value of the output inductor should be chosen such that S<sub>E</sub> is from  $0.5 \times$  to  $1 \times$  the falling slope of the inductor current (S<sub>E</sub>).

#### **Current Sense Amplifier**

The A8590 incorporates a high-bandwidth current sense amplifier to monitor the current in the high-side MOSFET. This current signal is used by both the PWM and PFM control circuitry to regulate the peak current. The current signal is also used by the protection circuitry to prevent damage to the A8590.

#### **Power MOSFETs**

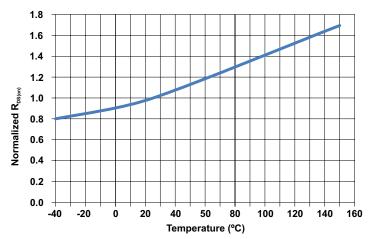

The A8590 includes a 40 V, 110 mΩ high-side N-channel MOSFET, capable of delivering at least 3.0 A. The A8590 also includes a 10  $\Omega$ , low-side MOSFET to help ensure the BOOT capacitor is always charged. The typical R<sub>DS(on)</sub> increase versus temperature is shown in Figure 3.

Figure 3: Typical MOSFET R<sub>DS(on)</sub> versus Temperature

#### **BOOT Regulator**

The A8590 contains a regulator to charge the boot capacitor. The voltage across the BOOT capacitor is typically 5.0 V. If the BOOT capacitor is missing, the A8590 detects a boot overvoltage. Similarly, if the BOOT capacitor is shorted the A8590 detects a boot undervoltage. Also, the BOOT regulator has a current limit to protect itself during a short-circuit condition. The details of how each type of boot fault is handled by the A8590 are shown in Figures 13 and 14 and summarized in Table 2.

#### Pulse Width Modulation (PWM) Mode

The A8590 uses fixed-frequency, peak current-mode control to provide excellent load and line regulation, fast transient response, and ease of compensation. A high-speed comparator and control logic, capable of typical pulse widths of 95 ns, are included in the A8590. The inverting input of the PWM comparator is connected to the output of the error amplifier. The non-inverting input is connected to the sum of the current sense signal, the slope compensation, and a DC offset voltage (V<sub>PWMOFFS</sub>, 400 mV (typ)). At the beginning of each PWM cycle, the CLK signal sets the PWM flip flop and the high-side MOSFET is turned on. When the summation of the DC offset, slope compensation, and current sense signal rises above the error amplifier voltage, the PWM flip-flop is reset and the high-side MOSFET is turned off.

The PWM flip-flop is reset-dominant, so the error amplifier may override the CLK signal in certain situations. For example, at very light loads or extremely high input voltages the error amplifier reduces (temporarily) output voltage below the 400 mV DC offset and the PWM flip-flop will ignore one or more of the incoming CLK pulses. The high-side MOSFET will not turn on, and the regulator will skip pulses to maintain output voltage regulation.

In PWM mode, all of the A8590 fault detection circuits are active. See Figure 13 for a timing diagram showing how faults are han-dled when in PWM mode. Also, the Protection Features section of this datasheet provides a detailed description of each fault and Table 2 presents a summary.

#### **Maximized Duty Cycle Control**

Most fixed frequency PWM controllers have limited maximum duty cycle. This is due to the off-time required to keep the charge pump capacitor charged in order to drive the high-side N-channel MOSFET. This limitation becomes significant in high-frequency, low-input regulators. It may cause the output to drop out of regulation during stop/start profiles in automotive designs.

The A8590 employs a technique that helps extend the maximum duty cycle. Without this technique the typical maximum duty cycle would be 74% at 2 MHz switching frequency. Using the extend duty cycle technique, the A8590 can achieve typical duty cycles of greater than 95% in 2 MHz designs.

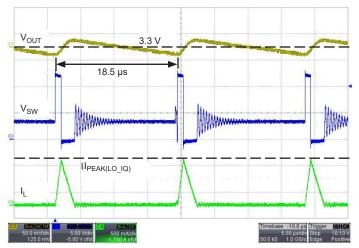

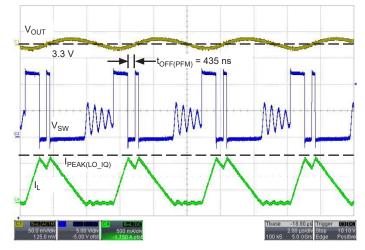

Figure 4: Low-I<sub>Q</sub> PFM Mode Operation at  $V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V, and  $I_{OUT}$  = 66 mA.

SW turns on only once every 18.5 µs to regulate V<sub>OUT</sub>

### Low-I<sub>Q</sub> Pulse Frequency Modulation (PFM) Mode

The A8590 enters Low-I $_Q$  PFM mode after 2048 internal clock cycles, if  $\overline{\text{SLEEP}}$  is high,  $V_{SS} > V_{HIC/PFM(EN)}$  (2.3 V (typ)), and NPOR is high. In Low-I $_Q$  PFM mode, the regulator operates with a switching frequency,  $f_{SW}$ , that depends on the load condition.

In Low-I $_Q$  PFM mode, a comparator monitors the voltage at the FB pin. If  $V_{FB}$  is above about 800 mV, the A8590 remains in coast mode and draws extremely low current from the input supply.

If the voltage at the FB pin drops below about 800 mV, the A8590 will fully power-up, delay approximately 2.5  $\mu s$  while it wakes up, and then turn on the high-side MOSFET.  $V_{OUT}$  will rise at a rate dependent on the input voltage, inductor value, output capacitance, and load. The high-side MOSFET will be turned off when either:

- current in the high-side MOSFET reaches I<sub>PEAK(LO IO)</sub>, or

- the high-side MOSFET has been on for t<sub>ON(PFM)MAX</sub>.

After the high-side MOSFET is turned off, the A8590 will again delay approximately  $t_{OFF(PFM)}$  and either:

- turn on the MOSFET again, if  $V_{FB} \le 800$  mV, or

- return to the Low-I<sub>O</sub> PFM mode

Figures 4 and 5 demonstrate Low-I<sub>Q</sub> PFM mode operation for a light load (66 mA) and a heavy load (330 mA), respectively.

In Low- $I_Q$  PFM mode the average current drawn from the input supply depends primarily on both the load, and how often the A8590 must fully power-up to maintain regulation. In Low- $I_Q$

Figure 5: Low- $I_Q$  PFM Mode Operation at  $V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V, and  $I_{OUT}$  = 330 mA.

SW turns on only twice every 5  $\mu$ s to regulate  $V_{OUT}$

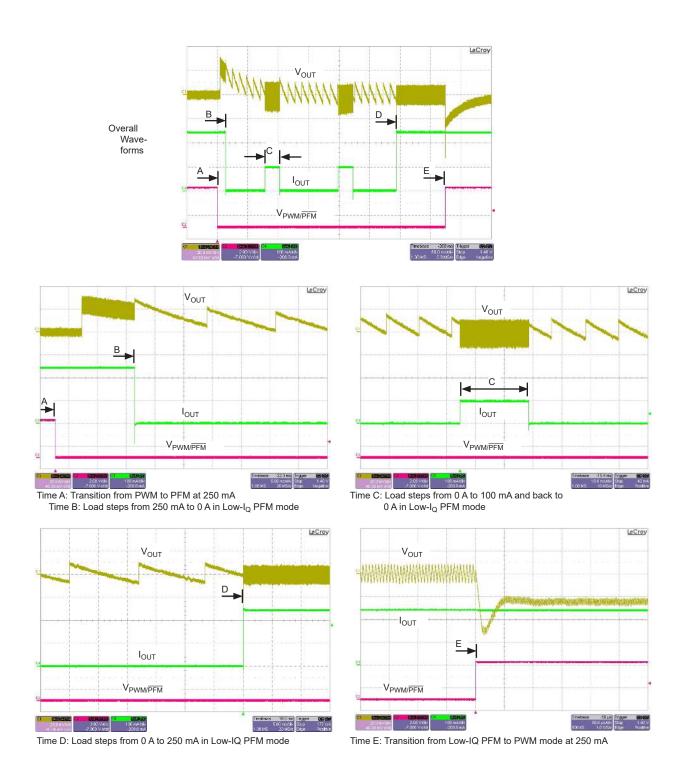

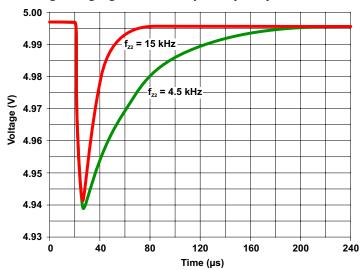

Figure 6: Transitions between PWM Mode and Low- $I_Q$  PFM Mode, and Load Transient Responses

Using circuit in typical application schematic ( $V_{IN}$  = 12 V,  $V_{OUT}$  = 5 V,  $f_{SW}$  = 425 kHz)

## Wide Input Voltage, 2.4 MHz, 3.0 Amp Asynchronous Buck Regulator With Low-I<sub>O</sub> Standby, Sleep Mode, External Synchronization, and NPOR Output

PFM mode the following faults are detected: a missing asynchronous diode, an open or shorted boot capacitor, VOUT shorted to ground, and SW shorted to ground. As described in the next section, if any of these faults occur the A8590 will transition from Low-I $_{\rm Q}$  PFM mode to Low-I $_{\rm P}$  PWM mode, with operation at 50% of the current limit of the PWM switching mode. See figure 14 for a timing diagram showing operation of the A8590 in Low-I $_{\rm Q}$  PFM mode.

In Low-I<sub>Q</sub> PFM mode the A8590 dissipates very little power, so the thermal monitoring circuit (TSD) is not needed and is disabled to minimize the quiescent current and improve efficiency.

Figure 6 shows PWM to Low- $I_Q$  PFM transitions for a typical microcontroller or DSP system. The system starts in PWM mode at  $I_{OUT} = 250$  mA and then transitions to Low- $I_Q$  PFM mode, also at  $I_{OUT} = 250$  mA (time A). While in Low- $I_Q$  PFM mode the current drops from 250 mA to 0 A (time B) and also cycles from no load to 100 mA (time C). In Low- $I_Q$  PFM mode the load steps from  $I_{OUT} = 0$  A to 250 mA (time D) and then the A8590 transitions back to PWM mode (time E). For this example, the output ripple voltage is always less than 30 mV<sub>PP</sub> and the transient deflection between modes is always less than 50 mV<sub>PEAK</sub>.

#### Reduced Current (Low-I<sub>P</sub>) PWM Mode

The A8590 supports two different levels of current limiting in PWM modes:

- 100% current, which is during normal PWM, and

- Low-I<sub>p</sub>, in which the current is limited to about 50% of the typical current limit

The Low-I<sub>P</sub> PWM mode is invoked when the A8590 is supposed to be in PFM mode but a fault occurs. The purpose of the Low-I<sub>P</sub> PWM mode is to give priority to maintaining reliable regulation of  $V_{OUT}$  while enabling all the protection circuits inside the A8590 that are normally debiased during Low-I<sub>Q</sub> PFM mode (high precision comparators, timers, and counters).

There are several faults that cause a transition from Low- $I_Q$  PFM to Low- $I_P$  PWM mode: a missing asynchronous diode, an open or shorted boot capacitor, VOUT shorted to ground, or SW shorted to ground. See figure 14 for a timing diagram showing operation when the A8590 transitions from Low- $I_Q$  PFM mode to Low- $I_P$  PWM mode.

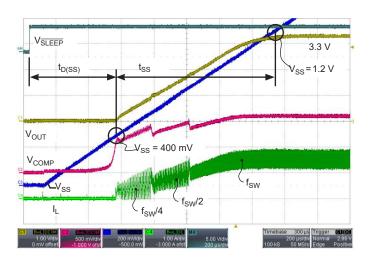

#### Soft-Start (Startup) and Inrush Current Control

Inrush current is controlled by a soft-start function. When the A8590 is enabled and all faults are cleared, the soft-start pin will source  $I_{SSSU}$  and the voltage on the soft-start capacitor,  $C_{SS}$ , will

ramp upward from 0 V. When the voltage at the soft-start pin exceeds approximately 400 mV, the error amplifier will slew its output voltage above the PWM Ramp Offset ( $V_{PWMOFFS}$ ). At that instant, the high-side and low-side MOSFETs will begin switching. As shown in Figure 7, there is a small delay ( $t_{D(SS)}$ ) between when the enable pin transitions high, and when both the soft-start voltage exceeds 400 mV and the error amplifier slews its output high enough to initiate PWM switching.

After the A8590 begins switching, the error amplifier will regulate the voltage at the FB pin to the soft-start pin voltage minus approximately 400 mV. During the active portion of soft-start, the voltage at the soft-start pin rises from 400 mV to 1.2 V (a difference of 800 mV), the voltage at the FB pin rises from 0 V to 800 mV, and the regulator output voltage rises from 0 V to the targeted setpoint, which is determined by the feedback resistor divider on the FB pin.

During startup, the PWM switching frequency is reduced to 25% of  $f_{OSC}$  while  $V_{FB}$  is below 200 mV. If  $V_{FB}$  is above 200 mV but below 400 mV, the switching frequency is reduced to 50% of  $f_{OSC}$ . Also, if  $V_{FB}$  is below 400 mV, the  $g_m$  of the error amplifier is reduced to  $g_m/2$ . When  $V_{FB}$  is above 400 mV the switching frequency will be  $f_{OSC}$  and the error amplifier gain will be  $g_m$ . The reduced switching frequencies and error amplifier gain are necessary to help improve output regulation and stability when VOUT is at a very low voltage. When  $V_{OUT}$  is very low, the PWM control loop requires on-times near the minimum controllable on-time, as well as extra-low duty cycles that are not possible at the base operating switching frequencies.

When the voltage at the soft-start pin reaches approximately 1.2 V, the error amplifier will change mode and begin regulating the voltage at the FB pin to the A8590 internal reference, 800 mV. The voltage at the soft-start pin will continue to rise to approximately  $V_{REG}$ . Complete soft-start operation from  $V_{OUT} = 0$  V is shown in Figure 7.

If the A8590 is disabled or a fault occurs, the internal fault latch will be set and the capacitor on the soft-start pin will be discharged to ground very quickly by an internal 2 k $\Omega$  pull-down resistor. The A8590 will clear the internal fault latch when the voltage at the soft-start pin decays to approximately 200 mV (V\_{SRST}). Conversely, if the A8590 enters hiccup mode, the capacitor on the soft-start pin is slowly discharged by a current sink, I\_{SSHIC}. Therefore, the soft-start capacitor (C\_{SS}) not only controls the startup time but also the time between soft-start attempts in hiccup mode. Hiccup mode operation is discussed in more detail in the Protection Features section of this datasheet.

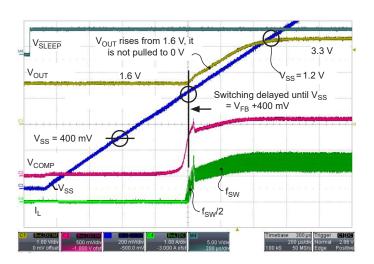

#### **Pre-Biased Startup**

If the output of the regulator ( $V_{OUT}$ ) is pre-biased to some voltage, the A8590 will modify the normal startup routine to prevent discharging the output capacitors. As described previously, the error amplifier usually becomes active when the voltage at the soft-start pin exceeds 400 mV. If the output is pre-biased, the FB pin will be at some non-zero voltage. The A8590 will not start switching until the voltage at the soft-start pin increases to approximately  $V_{FB} \pm 400$  mV. When the soft-start pin voltage exceeds this value: the error amplifier becomes active, the voltage at the COMP pin rises, PWM switching starts, and  $V_{OUT}$  ramps upward from the pre-bias level. Figure 8 shows startup when the output voltage is pre-biased to 1.6 V.

Figure 7: Normal Startup to  $V_{OUT}$  = 3.3 V and  $I_{OUT}$  = 1.6 A; PWM/PFM Pin = high, SLEEP Pin Transitions from Low to High

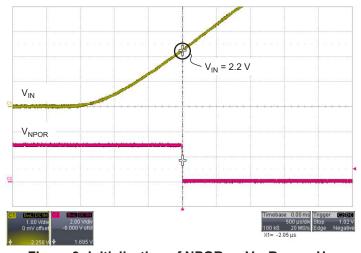

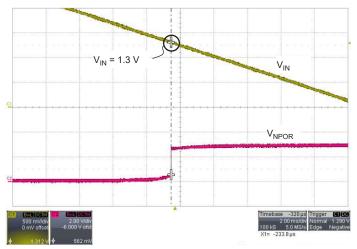

#### Not Power-On Reset (NPOR) Output

The A8590 has an inverted power-on reset output (NPOR) with a fixed delay of its rising edge ( $t_{D(NPOR)}$ ). The NPOR output is an open drain output so an external pull-up resistor must be used, as shown in the Typical Applications schematics. NPOR transitions high when the output voltage ( $V_{OUT}$ ), sensed at the FB pin, is within regulation. In PWM mode, NPOR is high when the output voltage is typically within 92.5% to 110% of the target value. In PFM mode, NPOR is high when the output voltage is typically above 87.5% of the target value. The NPOR overvoltage and undervoltage comparators incorporate a small amount of hysteresis (10 mV typically) and filtering (5  $\mu s$  typically) to help reduce chattering due to voltage ripple at the FB pin.