#### **Features**

- → Compliant with HDMI 1.4a specification up to 3.4 Gbps

- → Low Intra-pair and Inter-pair skews

- → Single 3.3 V Power Supply

- → -40°C to 85°C Operating Temperature Range

- → Integrated DP++ passive level shifter (48pin version only)

- → HPD Detection

- TMDS path auto-turn-off when HPD is not present

- → Supports DC and AC Coupled inputs (48-contact TQFN version only)

- → Integrated ESD protection to +/-4KV Contact on all I/O pins per IEC61000-4-2 standard

- → Package (Pb-free and Green available)

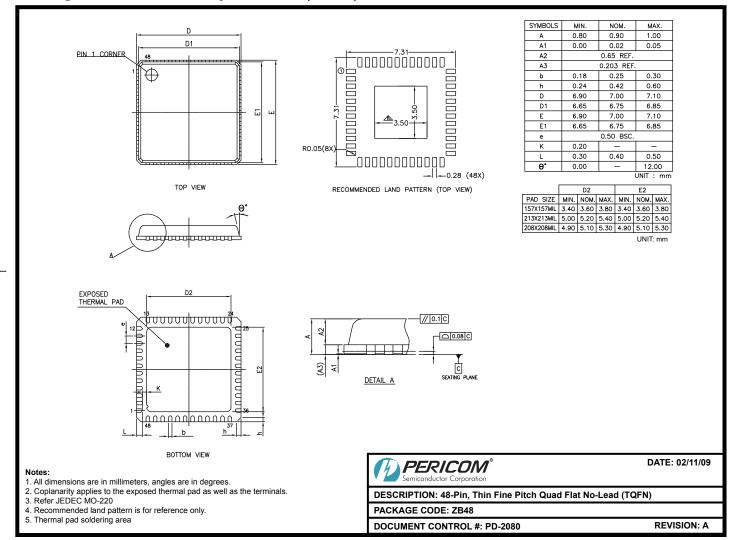

- 48-contact TQFN, 7mm x 7mm (ZBE)

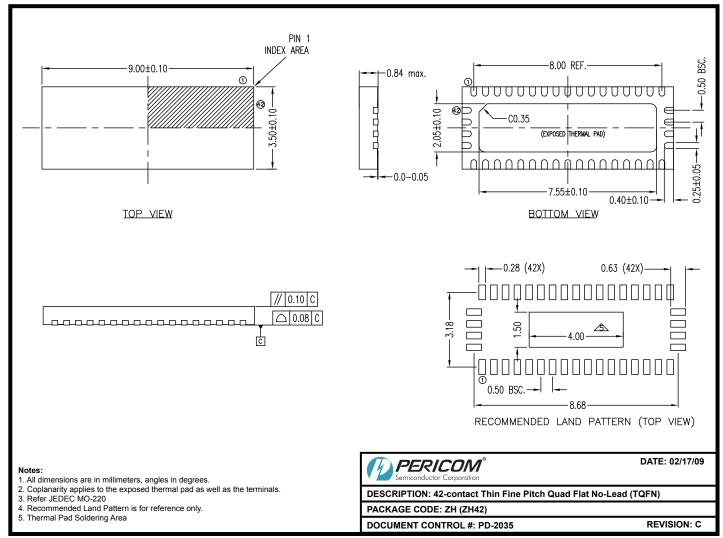

- 42-contact TQFN, 9mm x 3.5mm (ZHE)

#### **Applications**

- → HDMI Sink (monitor or DTV)

- → PC Motherboard / Graphics Card

- → Digital Set-Top-Box

- → 1-to-2 DP & HDMI/DVI Switch Box

- → DVD player

- → HDMI/DVI monitor or TV

#### **Description**

PI3HDMI1421 is industries lowest power HDMI mux/demux supporting up to 3.4Gbps signal throughput per channel. the PI-3HDMI1421 supports switching all TMDS channels, HPD channel, and the DDC channels. The part can behave as 1:2 demux or a 2:1 mux, since all signal paths are passive and therefore can support bi-directional data-traffic.

With integrated ESD protection up to +/-4kV contact per IEC61000-4-2, the PI3HDMI1421 is ideal for consumer applications.

12-0209 1 www.pericom.com P-0.1 07/20/12

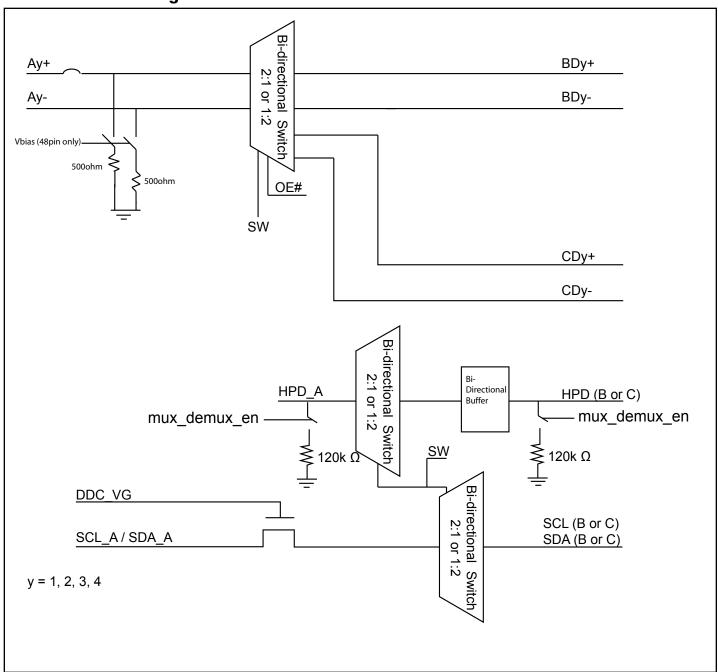

### **Functional Block Diagram**

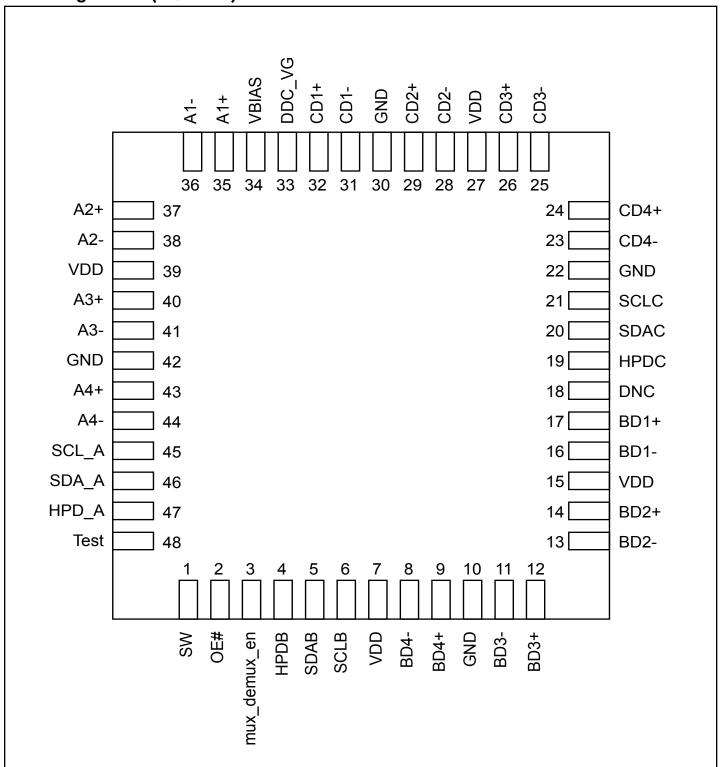

### **Pin Configuration (TQFN-48)**

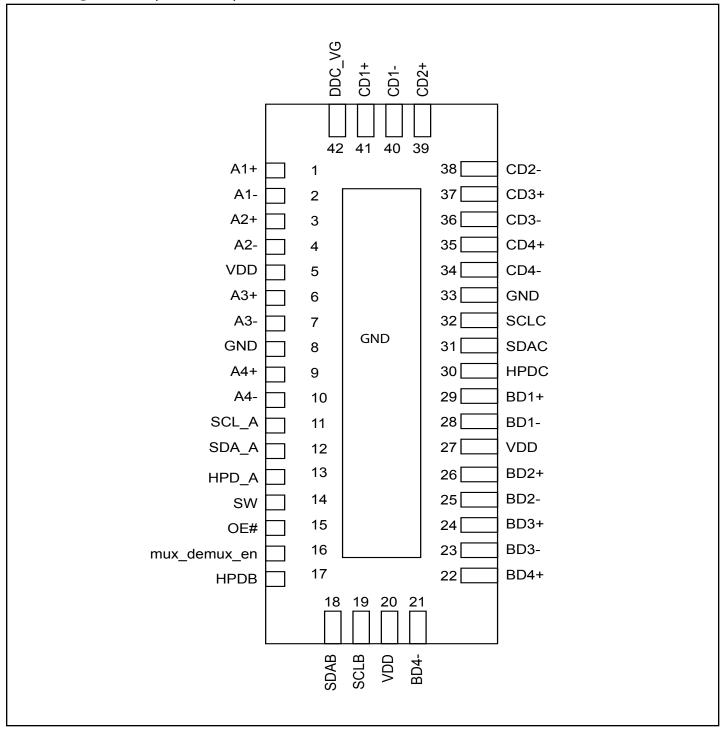

## **Pin Configuration (TQFN-42)**

## **Pin Description**

| Name                       | I/O                                                                           | Description                                                                                   |                                |                        |        |  |

|----------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------|------------------------|--------|--|

| mux_demux_en               | I                                                                             | H=1:2 demux; L=2:1 mux                                                                        |                                |                        |        |  |

| DNC                        | -                                                                             | Leave pin no connect (do not tie to GND or VDD)                                               |                                |                        |        |  |

| Ay+                        | I/O                                                                           | y = 1, 2, 3, 4, for positive differential data or clock inputs.                               |                                |                        |        |  |

| Ay-                        | I/O                                                                           | y = 1, 2, 3, 4, for ne                                                                        | gative differential data or cl | ock inputs.            |        |  |

| xDy+                       | I/O                                                                           | x = B,C; y = 1, 2, 3,                                                                         | 4 for positive differential or | utputs.                |        |  |

| xDy-                       | I/O                                                                           | x = B,C; y = 1, 2, 3,                                                                         | 4 for negative differential o  | utputs.                |        |  |

| HPDx                       | I/O                                                                           | When mux_demux<br>HPDx is 5V tolerar                                                          | x_en=High, internal pull-dent. | own at ~120Kohm is ena | abled. |  |

| LIDD. A                    | 1/0                                                                           | When mux_demux                                                                                | x_en=Low, internal pull-do     | wn at ~120Kohm is enal | bled.  |  |

| HPD_A                      | I/O                                                                           | HPD_A is 5V toler                                                                             | ent.                           |                        |        |  |

| SDA A SCI A                | I/O                                                                           | DDC channel pins                                                                              | to SOURCE                      |                        |        |  |

| SDA_A, SCL_A               | 1/0                                                                           | These pins are 5 V                                                                            | tolerant and should be con     | nected to Source side. |        |  |

| SDAx, SCLx                 | I/O                                                                           | x = B, C. These pins are DDC channel pins SDAx/SCLx.                                          |                                |                        |        |  |

| SDAX, SCLX                 | 1/0                                                                           | These pins are 5V tolerant and should be connected to Sink side.                              |                                |                        |        |  |

| Test                       | I                                                                             | For normal operation, please tie to GND                                                       |                                |                        |        |  |

|                            |                                                                               | Output Port control                                                                           |                                |                        |        |  |

|                            |                                                                               | SW                                                                                            | Port A connects to B           | Port A connects to C   | HPD_A  |  |

| SW                         | I                                                                             | 0                                                                                             | Enable                         | Hi-Z                   | HPDB   |  |

|                            |                                                                               | 1                                                                                             | Hi-Z                           | Enable                 | HPDC   |  |

|                            |                                                                               | OE# = HIGH, the o                                                                             | chip is in power down mode     | 2.                     |        |  |

| OE#                        | I                                                                             | OE# = HIGH, the chip is in power down mode.  OE# = LOW, the chip is in normal operation mode. |                                |                        |        |  |

|                            |                                                                               | For HDMI/DVI source demultiplexer: Connect to VDD or do not connect.                          |                                |                        |        |  |

| VBIAS (48pin package only) | I                                                                             | For dual mode DP source demultiplexer: Connect to GND.                                        |                                |                        |        |  |

| age only)                  | High speed channel Ax with 500ohm pulled to ground when Vbias is connected to |                                                                                               |                                | connected to GND       |        |  |

| GND                        |                                                                               | Ground connection                                                                             |                                |                        |        |  |

| VDD                        | Pwr                                                                           | Power supply at 3.3V                                                                          |                                |                        |        |  |

| DDC_VG                     | I                                                                             | GATE voltage for I                                                                            | DDC FETs (connect to volta     | ge from 2.5V to 3.6V)  |        |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameters                       | Comments                              | Unit        |

|----------------------------------|---------------------------------------|-------------|

| Supply Voltage Range             |                                       | -0.5V to 4V |

| Normal I/O Voltage Range         |                                       | -0.5V to 4V |

| 5V Safe I/O Voltage Range        | SCL_A, SDA_A, SCLx, SDAx, HPD_A, HPDx | -0.5V to 6V |

| ECD Bins Assil and Import        | Contact per IEC-61000-4-2             | ±4kV        |

| ESD Pins Ax+/- and xDx+/-        | HBM per JESD22                        | ±4kV        |

| Pins SCL/SDA_A, HPD_A, SCL/SDAx, | Contact per IEC-61000-4-2 HBM per     | ±4kV        |

| HPDx                             | JESD22                                | ±4kV        |

## **Normal Operating Conditions**

| Parameter                                                        | Min | Тур | Max | Unit |

|------------------------------------------------------------------|-----|-----|-----|------|

| Supply Voltage, VDD                                              | 3.0 | 3.3 | 3.6 | V    |

| Ambient Temperature                                              | -40 |     | +85 | °C   |

| Supply Current, I <sub>CC</sub> (When HPDx = high and OE# = low) |     |     | 150 | uA   |

| Supply Current, I <sub>CC</sub> (When HPDx = low and OE# = low)  |     |     | 10  | uA   |

| Power down Supply Current, (When OE# = high)                     |     |     | 10  | uA   |

12-0209 6 www.pericom.com P-0.1 07/20/12

## **Electrical Characteristics Over Recommended Operating Conditions** (unless otherwise noted)

| Symbol             | Parameter                                                  | <b>Test Conditions</b>           | Min | Тур  | Max | Unit  |

|--------------------|------------------------------------------------------------|----------------------------------|-----|------|-----|-------|

| TMDS di            | TMDS differential pins                                     |                                  |     |      |     |       |

| -3dB BW            | -3dB bandwidth                                             | See fig 5                        |     | 3.7  |     | GHz   |

| Dam                | Resistance through switch path when                        | All $Ax = 2.7V$ to $3.6V$        |     | 8.5  |     | ah ma |

| Ron                | ON (A to B or A to C)                                      | $V_{IN} = 3.0V, I = 20mA$        |     | 8.5  |     | ohm   |

| Con                | Capacitance through switch path when ON (A to B or A to C) | All $Ax = 2.7V \text{ to } 3.6V$ |     | 3.5  |     | pF    |

|                    | 1                                                          | @ 2.25Gbps, see fig 5            |     | -1.5 |     | 10    |

| IN                 | insertion loss                                             | @ 3.4Gbps, see fig 5             |     | -1.8 |     | dB    |

| Xtalk              | Crosstalk                                                  | @ 3.4Gbps. see fig 3             |     | -38  |     | dB    |

| Iso <sub>off</sub> | Off Isolation                                              | @ 3.4Gbps. see fig 4             |     | -29  |     | dB    |

| $T_{SK}$           | Inter-pair Skew                                            |                                  |     | 20   |     | ps    |

| T <sub>SK</sub>    | Intra-pair Skew                                            |                                  |     | 10   |     | ps    |

| I <sub>OFF</sub>   | Off Leakage Current                                        |                                  |     | 12   | 20  | μΑ    |

#### **Control Pins**

| Symbol            | Parameter                           | <b>Test Conditions</b>          | Min | Тур  | Max | Unit |

|-------------------|-------------------------------------|---------------------------------|-----|------|-----|------|

| $I_{IH}$          | High level digital input current(1) | $V_{IH} = 2V$ or $V_{DD}$       | -10 |      | 10  | 4    |

| $I_{\mathrm{IL}}$ | Low level digital input current(1)  | $V_{IL} = GND \text{ or } 0.8V$ | -10 |      | 10  | μΑ   |

| V <sub>IH</sub>   | Input High Voltage                  |                                 | 2.4 |      |     |      |

| $V_{\rm IL}$      | Input Low Voltage                   |                                 |     |      | 0.8 | V    |

| $V_{IK}$          | Input Clamp Voltage                 |                                 |     | -1.2 |     |      |

12-0209 7 www.pericom.com P-0.1 07/20/12

#### **DDC I/O Pins**

| Symbol           | Parameter                             | <b>Test Conditions</b>                                    | Min | Тур | Max | Unit |

|------------------|---------------------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| $I_{LK}$         | Input leakage current                 | $V_{I}$ = 0.1 $V_{DD}$ to $V_{DD}$ to isolated DDC inputs | -20 |     | 20  | μΑ   |

| C <sub>IO</sub>  | Input/Output capacitance              | V <sub>I</sub> peak-peak = 1V, 100 KHz                    |     |     | 5   | pF   |

| R <sub>ON</sub>  | Switch resistance                     | $I_O = 3mA$ , $V_O = 0.4V$ , DDC                          |     | 12  | 15  | Ω    |

| $V_{IH}$         | Single-ended high level input voltage |                                                           | 2.4 |     |     | V    |

| $V_{IL}$         | Single-ended low level input voltage  |                                                           | GND |     | 0.8 | V    |

| I <sub>OFF</sub> | Off Leakage Current                   |                                                           |     | 20  |     | μΑ   |

#### **HPD**x

| Symbol            | Parameter                              | Test Conditions                  | Min | Тур | Max | Unit |

|-------------------|----------------------------------------|----------------------------------|-----|-----|-----|------|

| I <sub>IH</sub>   | High level digital input current       | $V_{IH} = 2V \text{ or } V_{DD}$ | +20 |     | +40 | 4    |

| $I_{\mathrm{IL}}$ | Low level digital input current        | $V_{IL} = GND \text{ or } 0.8V$  | -20 |     | 20  | μΑ   |

| V <sub>OL</sub>   | Single-ended low level output voltage  | $I_{OL} = +4mA$                  | GND |     | 0.4 | V    |

| V <sub>OH</sub>   | Single-ended high level output voltage | $I_{OH} = -4mA$                  | 2.4 |     |     | V    |

| V <sub>IH</sub>   | Single-ended high level input voltage  |                                  | 2.4 |     |     | V    |

| V <sub>IL</sub>   | Single-ended low level input voltage   |                                  | GND |     | 0.8 | V    |

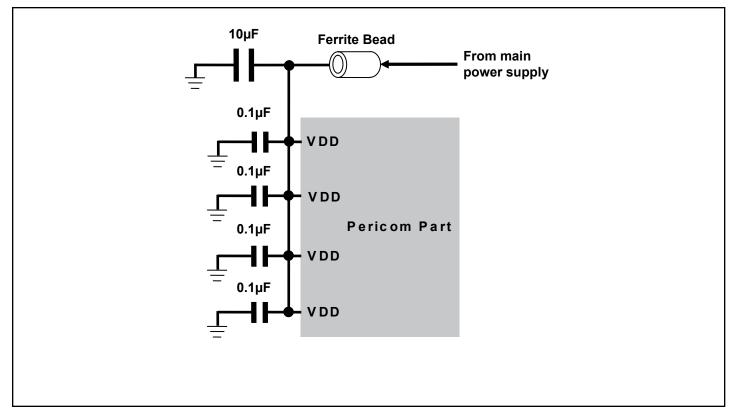

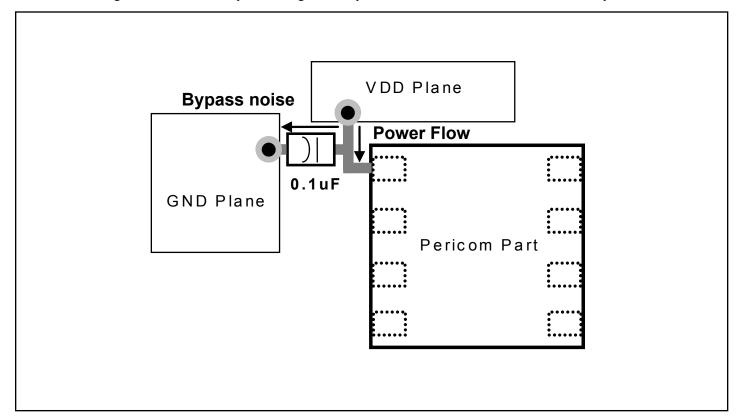

#### **Recommended Power Supply Decoupling Circuit**

Figure 1 is the recommended power supply decoupling circuit configuration. It is recommended to put  $0.1\mu F$  decoupling capacitor on each  $V_{DD}$  pin of our part. Four  $0.1\mu F$  decoupling capacitors are put in Figure 1 with an assumption of only four  $V_{DD}$  pins on our part. If there is more or less  $V_{DD}$  pins on our part, the number of  $0.1\mu F$  decoupling capacitors should be adjusted according to the actual number of  $V_{DD}$  pins. On top of  $0.1\mu F$  decoupling capacitor on each  $V_{DD}$  pin, it is recommended to put a  $10\mu F$  decoupling capacitor near our part's  $V_{DD}$ , it is for stabilizing the power supply for our part. Ferrite bead is also recommended for isolating the power supply for our part and other power supplies in other parts of the circuit. But, it is optional and depends on the power supply conditions of other circuits.

Figure 1: Recommended Power Supply Decoupling Circuit Diagram

12-0209 9 www.pericom.com P-0.1 07/20/12

#### **Requirements on the Decoupling Capacitors**

- i. There is no special requirement on the material of the capacitors. Ceramic capacitors are generally being used with typically materials of X5R or X7R.

- ii. 0.1uF decoupling capacitor in 0402 package is recommended.

#### **Layout and Decoupling Capacitor Placement Consideration**

- i. Each  $0.1\mu F$  decoupling capacitor should be placed as close as possible to each  $V_{DD}$  pin.

- ii. V<sub>DD</sub> and GND planes should be used to provide a low impedance path for power and ground.

- iii. Via holes should be placed to connect to V<sub>DD</sub> and GND planes directly.

- iv. Trace should be as wide as possible.

- v. Trace should be as short as possible.

- vi. The placement of decoupling capacitor and the way of routing trace should consider the power flowing criteria.

- vii. 10μF capacitor should also be placed close to our part and should be placed in the middle location of 0.1μF capacitors.

- viii. Avoid the large current circuit placed close to our part; especially when it is shared the same  $V_{DD}$  and GND planes, since large current flowing on our  $V_{DD}$  or GND planes will generate a potential variation on the  $V_{DD}$  or GND of our part.

Figure 2: Layout and Decoupling Capacitor Placement Diagram

12-0209 10 www.pericom.com P-0.1 07/20/12

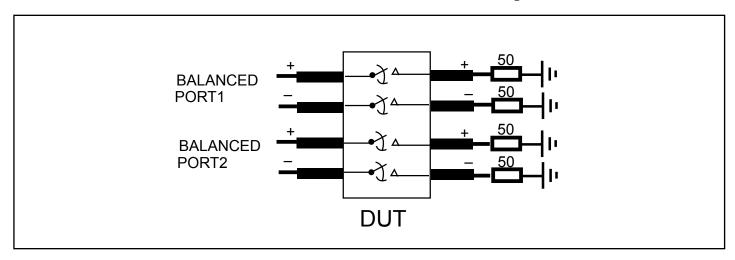

Fig 3: Crosstalk Setup

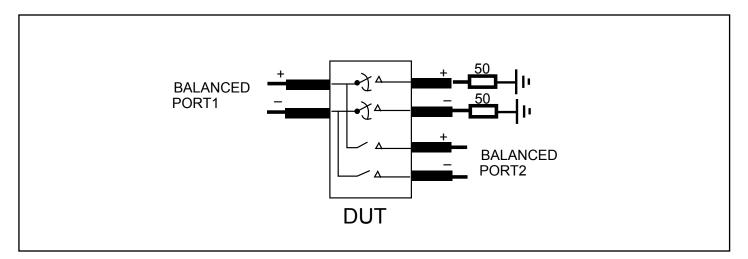

Fig 4: Off-isolation setup

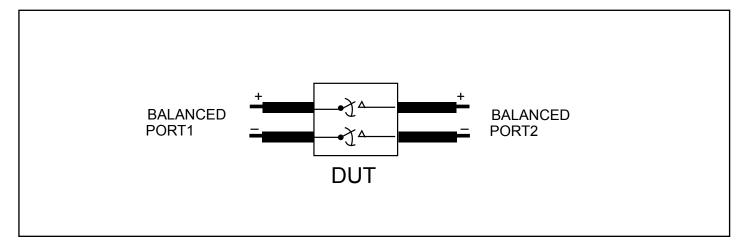

Fig 5: Differential Insertion Loss and -3dB Test Setup

12-0209 11 www.pericom.com P-0.1 07/20/12

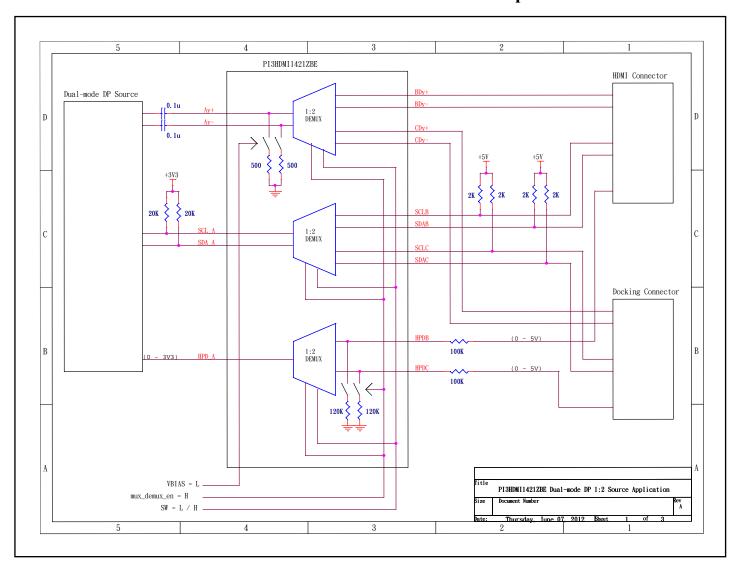

Fig 6: Dual-mode DP 1:2 Source Application Diagram

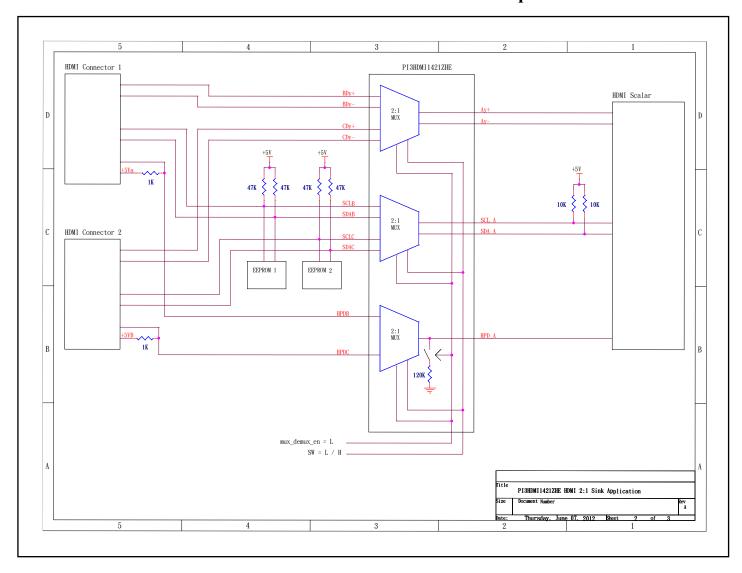

Fig 7: HDMI 2:1 Sink Application Diagram

### Package Mechanical: 48-pin, TQFN (ZB48)

09-0091

## Package Mechanical: 42-pin, TQFN (ZH42)

09-0116

#### **Ordering Information**

| Ordering Code  | Package Code | Package Description          |

|----------------|--------------|------------------------------|

| PI3HDMI1421ZBE | ZB           | 48-pin, Pb-free & Green TQFN |

| PI3HDMI1421ZHE | ZH           | 42-pin, Pb-free & Green TQFN |

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding an X Suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com