# RoboClock<sup>®</sup>, CY7B9950

# 2.5/3.3V, 200 MHz High-Speed Multi-Phase PLL Clock Buffer

## Features

- 2.5V or 3.3V operation

- Split output bank power supplies

- Output frequency range: 6 MHz to 200 MHz

- 50 ps typical matched-pair Output-output skew

- 50 ps typical Cycle-cycle jitter

- 49.5/50.5% typical output duty cycle

- Selectable output drive strength

- Selectable positive or negative edge synchronization

- Eight LVTTL outputs driving 50 Ω terminated lines

- LVCMOS/LVTTL over-voltage-tolerant reference input

- Phase adjustments in 625-/1250-ps steps up to ±7.5 ns

- 2x, 4x multiply and (1/2)x, (1/4)x divide ratios

- Spread-Spectrum compatible

- Industrial temp. range: -40°C to +85°C

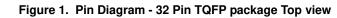

- 32-pin TQFP package

# Description

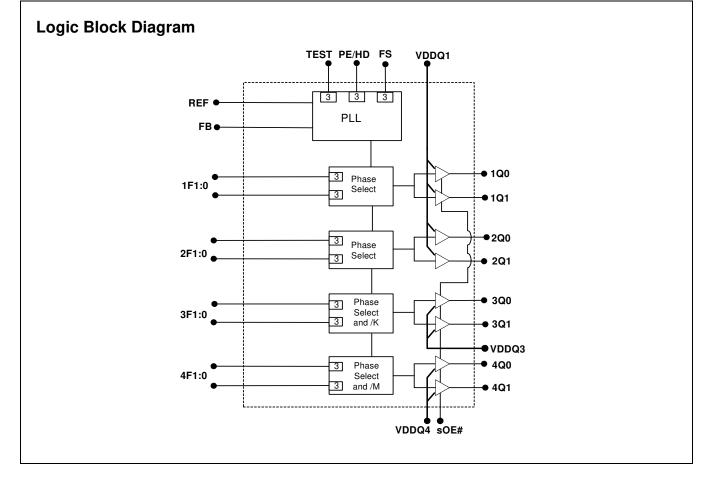

The CY7B9950 RoboClock<sup>®</sup> is a low voltage, low power, eight-output, 200 MHz clock driver. It features output phase programmability which is necessary to optimize the timing of high performance computer and communication systems.

The user can program the phase of the output banks through nF[0:1] pins. The adjustable phase feature allows the user to skew the outputs to lead or lag the reference clock. Any one of the outputs can be connected to the feedback input to achieve different reference frequency multiplications, and divide ratios and zero input-output delay.

The device also features split output bank power supplies, which enable the user to run two banks (1Qn and 2Qn) at a power supply level different from that of the other two banks (3Qn and 4Qn). Additionally, the three-level PE/HD pin controls the synchronization of the output signals to either the rising, or the falling edge of the reference clock and selects the drive strength of the output buffers. The high drive option (PE/HD = MID) increases the output current from ± 12 mA to ± 24 mA(3.3V).

Cypress Semiconductor Corporation • Document #: 38-07338 Rev. \*D

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised September 27, 2007

### Table 1. Pin Definitions

| Pin                                | Name                           | <b>IO</b> <sup>[1]</sup> | Туре         | Description                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------|--------------------------------|--------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 29                                 | REF                            | I                        | LVTTL/LVCMOS | Reference Clock Input.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 13                                 | FB                             | Ι                        | LVTTL        | Feedback Input.                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 27                                 | TEST                           | I                        | Three-level  | When MID or HIGH, disables Phase-locked Loop (PLL) <sup>[3]</sup> . REF goes to outputs of Bank 1 and Bank 2. REF also goes to outputs of Bank 3 and Bank 4 through output dividers K and M. Set LOW for normal operation.                                                                                                                                             |  |  |

| 22                                 | sOE#                           | I, PD                    | Two-level    | <b>nchronous Output Enable</b> . When HIGH, it stops clock outputs (except 2Q0 d 2Q1) in a LOW state (for PE = H or M) – 2Q0, and 2Q1 may be used as a feedback signal to maintain phase lock. When TEST is held at MID level d sOE# is HIGH, the nF[1:0] pins act as output disable controls for individual nks when nF[1:0] = LL. Set sOE# LOW for normal operation. |  |  |

| 4                                  | PE/HD                          | I, PU                    | Three-level  | elects Positive or Negative Edge Control and High or Low Output Drive<br>trength. When LOW/HIGH the outputs are synchronized with the<br>egative/positive edge of the reference clock, respectively. When at MID level,<br>e output drive strength is increased and the outputs synchronize with the<br>positive edge of the reference clock (see Table 7 on page 4).  |  |  |

| 24, 23, 26,<br>25, 1, 32, 3,<br>2  | nF[1:0]                        | I                        | Three-level  | Select Frequency and Phase of the Outputs (see Table 2, Table 3, Table 4 on page 4, Table 5 on page 4, and Table 6 on page 4).                                                                                                                                                                                                                                         |  |  |

| 31                                 | FS                             | Ι                        | Three-level  | Selects VCO Operating Frequency Range (see Table 5 on page 4)                                                                                                                                                                                                                                                                                                          |  |  |

| 19, 20, 15,<br>16, 10, 11, 6,<br>7 | nQ[1:0]                        | 0                        | LVTTL        | Four Banks of Two Outputs (see Table 2, Table 3, and Table 4 on page 4)                                                                                                                                                                                                                                                                                                |  |  |

| 21                                 | V <sub>DDQ1</sub> [2]          | PWR                      | Power        | <b>Power Supply for Bank 1 and Bank 2 Output Buffers</b> (see Table 8 on page 4 for supply level constraints).                                                                                                                                                                                                                                                         |  |  |

| 12                                 | V <sub>DDQ3</sub> [2]          | PWR                      | Power        | <b>Power Supply for Bank 3 Output Buffers</b> (see Table 8 on page 4 for supply evel constraints).                                                                                                                                                                                                                                                                     |  |  |

| 5                                  | V <sub>DDQ4</sub> [2]          | PWR                      | Power        | <b>Power Supply for Bank 4 Output Buffers</b> (see Table 8 on page 4 for supply level constraints).                                                                                                                                                                                                                                                                    |  |  |

| 14,30                              | V <sub>DD</sub> <sup>[2]</sup> | PWR                      | Power        | <b>Power Supply for Internal Circuitry</b> (see Table 8 on page 4 for supply level constraints).                                                                                                                                                                                                                                                                       |  |  |

| 8,9,17,18,28                       | V <sub>SS</sub>                | PWR                      | Power        | Ground                                                                                                                                                                                                                                                                                                                                                                 |  |  |

### **Device Configuration**

The outputs of the CY7B9950 can be configured to run at frequencies ranging from 6 to 200 MHz. Banks 3 and 4 output dividers are controlled by 3F[1:0] and 4F[1:0] as indicated in Table 2 and Table 3, respectively.

#### Table 2. Output Divider Settings — Bank 3

| 3F[1:0]              | K — Bank3 Output Divider |

|----------------------|--------------------------|

| LL                   | 2                        |

| HH                   | 4                        |

| Other <sup>[4]</sup> | 1                        |

### Table 3. Output Divider Settings — Bank 4

| 4F[1:0]              | M — Bank4 Output Divider |

|----------------------|--------------------------|

| LL                   | 2                        |

| Other <sup>[4]</sup> | 1                        |

The three-level FS control pin setting determines the nominal operating frequency range of the divide-by-one outputs of the device. The CY7B9950 PLL operating frequency range that corresponds to each FS level is given in Table 4 on page 4.

#### Notes

4. These states are used to program the phase of the respective banks (see Table 6 on page 4).

<sup>1. &</sup>quot;PD" indicates an internal pull-down and "PU" indicates an internal pull-up. "3" indicates a three-level input buffer

A bypass capacitor (0.1μF) must be placed as close as possible to each positive power pin (< 0.2"). If these bypass capacitors are not close to the pins their high-frequency filtering characteristic are cancelled by the lead inductance of the traces.</li>

<sup>3.</sup> When TEST = MID and sOE# = HIGH, PLL remains active with nF[1:0] = LL functioning as an output disable control for individual output banks. Skew selections remain in effect unless nF[1:0] = LL.

#### Table 4. Frequency Range Select

| FS | PLL Frequency Range |

|----|---------------------|

| L  | 24 to 50 MHz        |

| М  | 48 to 100 MHz       |

| Н  | 96 to 200 MHz       |

The selectable output skew is in discrete increments of time units  $(t_{U}). The value of <math display="inline">t_{U}$  is determined by the FS setting and the maximum nominal frequency. The equation used to determine

#### Table 6. Output Skew Settings

the t<sub>U</sub> value is:  $t_U = 1 / (f_{NOM} \times MF)$ , where MF is a multiplication factor, which is determined by the FS setting as indicated in Table 5.

#### Table 5. MF Calculation

| FS | MF | f <sub>NOM</sub> at which t <sub>U</sub> is 1.0 ns(MHz) |

|----|----|---------------------------------------------------------|

| L  | 32 | 31.25                                                   |

| М  | 16 | 62.5                                                    |

| Н  | 8  | 125                                                     |

| nF[1:0]           | Skew (1Q[0:1],2Q[0:1]) | Skew (3Q[0:1])   | Skew (4Q[0:1])          |

|-------------------|------------------------|------------------|-------------------------|

| LL <sup>[5]</sup> | -4t <sub>U</sub>       | Divide By 2      | Divide By 2             |

| LM                | –3t <sub>U</sub>       | –6t <sub>U</sub> | v6t <sub>U</sub>        |

| LH                | -2t <sub>U</sub>       | -4t <sub>U</sub> | -4t <sub>U</sub>        |

| ML                | –1t <sub>U</sub>       | –2t <sub>U</sub> | v2t <sub>U</sub>        |

| MM                | Zero Skew              | Zero Skew        | Zero Skew               |

| MH                | +1t <sub>U</sub>       | +2t <sub>U</sub> | +2t <sub>U</sub>        |

| HL                | +2tU                   | +4t <sub>U</sub> | +4t <sub>U</sub>        |

| HM                | +3t <sub>U</sub>       | +6t <sub>U</sub> | +6t <sub>U</sub>        |

| HH                | +4t <sub>U</sub>       | Divide By 4      | Inverted <sup>[6]</sup> |

In addition to determining whether the outputs synchronize to the rising or the falling edge of the reference signal, the 3-level PE/HD pin controls the output buffer drive strength as indicated in Table 7.

The CY7B9950 features split power supply buses for Banks 1 and 2, Bank 3 and Bank 4, which enables the user to obtain both 3.3V and 2.5V output signals from one device. The core power supply (VDD) must be set a level that is equal or higher than on any one of the output power supplies.

#### Table 7. PE/HD Settings

| PE/HD | Synchronization | Output Drive Strength <sup>[7]</sup> |  |  |

|-------|-----------------|--------------------------------------|--|--|

| L     | Negative        | Low Drive                            |  |  |

| М     | Positive        | High Drive                           |  |  |

| Н     | Positive        | Low Drive                            |  |  |

#### Table 8. Power Supply Constraints

| V <sub>DD</sub> | V <sub>DDQ1</sub> <sup>[8]</sup> | V <sub>DDQ3</sub> <sup>[8]</sup> | V <sub>DDQ4</sub> <sup>[8]</sup> |

|-----------------|----------------------------------|----------------------------------|----------------------------------|

| 3.3V            | 3.3V or 2.5V                     | 3.3V or 2.5V                     | 3.3V or 2.5V                     |

| 2.5V            | 2.5V                             | 2.5V                             | 2.5V                             |

### **Governing Agencies**

The following agencies provide specifications that apply to the CY7B9950. The agency name and relevant specification is listed below.

#### **Table 9. Governing Agencies and Specifications**

| Agency Name | Specification                                |

|-------------|----------------------------------------------|

| JEDEC       | JESD 51 (Theta JA)<br>JESD 65 (Skew, Jitter) |

| IEEE        | 1596.3 (Jitter Specs)                        |

| UL-194_V0   | 94 (Moisture Grading)                        |

| MIL         | 883E Method 1012.1 (Therma Theta JC)         |

#### Notes:

- 5. LL disables outputs if TEST = MID and sOE# = HIGH.

- 6. When 4Q[0:1] are set to run inverted (HH mode), sOE# disables these outputs HIGH when PE/HD = HIGH or MID and sOE# disables them LOW when PE/HD = LOW.

- When Y=QU, 1 are set to full inverted (nn inode), s∪E# disables these outputs HIGH when PE/HD = HIGH or MID and sOE# disables them LOW when PE/HD = LOW.

Please refer to "DC Parameters" section for I<sub>OH</sub>/I<sub>OL</sub> specifications.

V<sub>DDQ1/3/4</sub> must not be set at a level higher than that of V<sub>DD</sub>. They can be set at different levels from each other, e.g., V<sub>DD</sub> = 3.3V, V<sub>DDQ1</sub> = 3.3V, V<sub>DDQ3</sub> = 2.5V and V<sub>DDQ4</sub> = 2.5V.

### **Absolute Maximum Conditions**

| Parameter            | Description                       | Condition                   | Min                | Max                   | Unit |

|----------------------|-----------------------------------|-----------------------------|--------------------|-----------------------|------|

| V <sub>DD</sub>      | Operating Voltage                 | Functional @ 2.5V ± 5%      | 2.375              | 2.625                 | V    |

| V <sub>DD</sub>      | Operating Voltage                 | Functional @ 3.3V ± 10%     | 2.97               | 3.63                  | V    |

| V <sub>IN(MIN)</sub> | Input Voltage                     | Relative to V <sub>SS</sub> | $V_{\rm SS} - 0.3$ | -                     | V    |

| V <sub>IN(MAX)</sub> | Input Voltage                     | Relative to V <sub>DD</sub> | _                  | V <sub>DD</sub> + 0.3 | V    |

| Τ <sub>S</sub>       | Temperature, Storage              | Non-functional              | -65                | +150                  | °C   |

| T <sub>A</sub>       | Temperature, Operating Ambient    | Functional                  | -40                | +85                   | °C   |

| TJ                   | Temperature, Junction             | Functional                  | _                  | 155                   | °C   |

| Ø <sub>JC</sub>      | Dissipation, Junction to Case     | Mil-Spec 883E Method 1012.1 | _                  | 42                    | °C/W |

| Ø <sub>JA</sub>      | Dissipation, Junction to Ambient  | JEDEC (JESD 51)             | _                  | 105                   | °C/W |

| ESD <sub>HBM</sub>   | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000               | -                     | V    |

| UL-94                | Flammability Rating               | At 1/8 in.                  | V-                 | -0                    |      |

| MSL                  | Moisture Sensitivity Level        |                             |                    | 1                     |      |

| F <sub>IT</sub>      | Failure in Time                   | Manufacturing Testing       | 1                  | 0                     | ppm  |

### **DC Electrical Specifications at 2.5V**

| Parameter                       | Description              | Condition                                                                                            | Min                   | Max              | Unit |

|---------------------------------|--------------------------|------------------------------------------------------------------------------------------------------|-----------------------|------------------|------|

| V <sub>DD</sub>                 | 2.5 Operating Voltage    | 2.5V ± 5%                                                                                            | 2.375                 | 2.625            | V    |

| V <sub>IL</sub>                 | Input LOW Voltage        | REF, FB and sOE# Inputs                                                                              | -                     | 0.7              | V    |

| V <sub>IH</sub>                 | Input HIGH Voltage       |                                                                                                      | 1.7                   | -                | V    |

| V <sub>IHH</sub> <sup>[9]</sup> | Input HIGH Voltage       | 3-Level Inputs                                                                                       | V <sub>DD</sub> - 0.4 | -                | V    |

| V <sub>IMM</sub> [9]            | Input MID Voltage        | (TEST, FS, nF[1:0], PE/HD) (These pins<br>are normally wired to V <sub>DD</sub> , GND or uncon-      | $V_{DD}/2 - 0.2$      | $V_{DD}/2 + 0.2$ | V    |

| V <sub>ILL</sub> [9]            | Input LOW Voltage        | nected.)                                                                                             | _                     | 0.4              | V    |

| IIL                             | Input Leakage Current    | $V_{IN} = V_{DD}/G_{ND},$<br>$V_{DD} = max.$ (REF and FB inputs)                                     | -5                    | 5                | μA   |

| l <sub>3</sub>                  | 3-Level Input DC Current | HIGH, V <sub>IN</sub> = V <sub>DD</sub> 3-Level Inputs                                               | -                     | 200              | μA   |

|                                 |                          | $\frac{\text{MID, V}_{\text{IN}} = \text{V}_{\text{DD}}/2}{\text{DS}[1:0], \text{PD}\#/\text{DIV},}$ | -50                   | 50               | μA   |

|                                 |                          | LOW, $V_{IN} = V_{SS}$ PE/HD)                                                                        | -200                  | -                | μA   |

| I <sub>PU</sub>                 | Input Pull-up Current    | $V_{IN} = V_{SS}, V_{DD} = max.$                                                                     | -25                   | -                | μA   |

| I <sub>PD</sub>                 | Input Pull-down Current  | $V_{IN} = V_{DD}, V_{DD} = max., (sOE#)$                                                             | -                     | 100              | μA   |

| V <sub>OL</sub>                 | Output LOW Voltage       | I <sub>OL</sub> = 12 mA (PE/HD = L/H), (nQ[0:1])                                                     | -                     | 0.4              | V    |

|                                 |                          | I <sub>OL</sub> = 20 mA (PE/HD = MID), (nQ[0:1])                                                     | -                     | 0.4              | V    |

| V <sub>OH</sub>                 | Output HIGH Voltage      | I <sub>OH</sub> = -12 mA (PE/HD = L/H), (nQ[0:1])                                                    | 2.0                   | -                | V    |

|                                 |                          | I <sub>OH</sub> = -20 mA (PE/HD = MID), (nQ[0:1])                                                    | 2.0                   | -                | V    |

| I <sub>DDQ</sub>                | Quiescent Supply Current | V <sub>DD</sub> = max., TEST = MID, REF = LOW,<br>sOE# = LOW, outputs not loaded                     | -                     | 2                | mA   |

| I <sub>DD</sub>                 | Dynamic Supply Current   | At 100 MHz                                                                                           | At 100 MHz 150        |                  | mA   |

| C <sub>IN</sub>                 | Input Pin Capacitance    |                                                                                                      | 4                     |                  | pF   |

Note 9. These inputs are normally wired to  $V_{DD}$ , GND or unconnected. Internal termination resistors bias unconnected inputs to  $V_{DD}/2$ .

# DC Specifications at 3.3V

| Parameter                       | Description              | Con                                         | dition                                                                                                                    | Min  | Max                      | Unit |   |    |

|---------------------------------|--------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|--------------------------|------|---|----|

| V <sub>DD</sub>                 | 3.3 Operating Voltage    | 3.3V ± 10%                                  | 3.3V ± 10%                                                                                                                |      | 3.63                     | V    |   |    |

| V <sub>IL</sub>                 | Input LOW Voltage        | REF, FB and sOE#                            | Inputs                                                                                                                    | -    | 0.8                      | V    |   |    |

| V <sub>IH</sub>                 | Input HIGH Voltage       |                                             |                                                                                                                           | 2.0  | _                        | V    |   |    |

| V <sub>IHH</sub> <sup>[9]</sup> | Input HIGH Voltage       | 3-Level Inputs                              | 3-Level Inputs<br>(TEST, FS, nF[1:0], PE/HD) (These pins<br>are normally wired to V <sub>DD</sub> ,GND or<br>unconected.) |      | _                        | V    |   |    |

| V <sub>IMM</sub> <sup>[9]</sup> | Input MID Voltage        | are normally wired t                        |                                                                                                                           |      | V <sub>DD</sub> /2 + 0.3 | V    |   |    |

| V <sub>ILL</sub> [9]            | Input LOW Voltage        |                                             |                                                                                                                           | -    | 0.6                      | V    |   |    |

| IIL                             | Input Leakage Current    | $V_{IN} = V_{DD}/G_{ND}, V_{DD}$<br>inputs) | $V_{IN} = V_{DD}/G_{ND}, V_{DD} = max.$ (REF and FB inputs)                                                               |      | 5                        | μA   |   |    |

| l <sub>3</sub>                  | 3-Level Input DC Current | HIGH, V <sub>IN</sub> = V <sub>DD</sub>     | 3-Level Inputs                                                                                                            | -    | 200                      | μA   |   |    |

|                                 |                          | MID, $V_{IN} = V_{DD}/2$                    | (TEST, FS, nF[1:0],<br>DS[1:0], PD#/DIV,                                                                                  | -50  | 50                       | μA   |   |    |

|                                 |                          | LOW, $V_{IN} = V_{SS}$                      | PE/HD)                                                                                                                    | -200 | _                        | μA   |   |    |

| I <sub>PU</sub>                 | Input Pull-up Current    | $V_{IN} = V_{SS}, V_{DD} = ma$              | $V_{IN} = V_{SS}, V_{DD} = max.$                                                                                          |      | _                        | μA   |   |    |

| I <sub>PD</sub>                 | Input Pull-down Current  | $V_{IN} = V_{DD}, V_{DD} = m$               | $V_{IN} = V_{DD}, V_{DD} = max., (sOE#)$                                                                                  |      | 100                      | μA   |   |    |

| V <sub>OL</sub>                 | Output LOW Voltage       | I <sub>OL</sub> = 12 mA (PE/HE              | I <sub>OL</sub> = 12 mA (PE/HD = L/H), (nQ[0:1])                                                                          |      | 0.4                      | V    |   |    |

|                                 |                          | $I_{OL} = 24 \text{ mA} (\text{PE/HE})$     | $I_{OL} = 24 \text{ mA} (PE/HD = MID), (nQ[0:1])$                                                                         |      | 0.4                      | V    |   |    |

| V <sub>OH</sub>                 | Output HIGH Voltage      | I <sub>OH</sub> = -12 mA (PE/H              | HD = L/H), (nQ[0:1])                                                                                                      | 2.4  | _                        | V    |   |    |

|                                 |                          | $I_{OH} = -24 \text{ mA} (PE/H)$            | HD = MID), (nQ[0:1])                                                                                                      | 2.4  | _                        | V    |   |    |

| I <sub>DDQ</sub>                | Quiescent Supply Current |                                             | V <sub>DD</sub> = max., TEST = MID, REF = LOW,<br>sOE# = LOW, outputs not loaded                                          |      | 2                        | mA   |   |    |

| I <sub>DD</sub>                 | Dynamic Supply Current   | At 100 MHz                                  | At 100 MHz                                                                                                                |      | At 100 MHz 23            |      | 0 | mA |

| C <sub>IN</sub>                 | Input Pin Capacitance    |                                             |                                                                                                                           | 4    |                          | pF   |   |    |

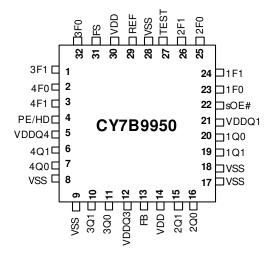

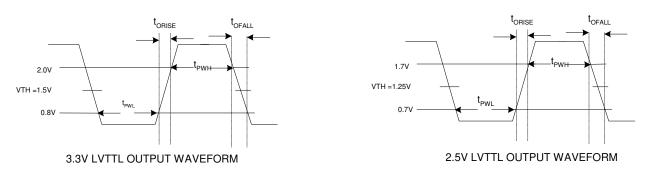

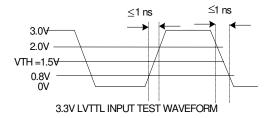

## AC Test Loads and Waveforms

# **AC Input Specifications**

| Parameter                      | Description          | Condition   | Min | Max | Unit |

|--------------------------------|----------------------|-------------|-----|-----|------|

| T <sub>R</sub> ,T <sub>F</sub> | Input Rise/Fall Time | 0.8V – 2.0V | -   | 10  | ns/V |

| T <sub>PWC</sub>               | Input Clock Pulse    | HIGH or LOW | 2   | -   | ns   |

| T <sub>DCIN</sub>              | Input Duty Cycle     |             | 10  | 90  | %    |

| F <sub>REF</sub>               | Froquoney            | FS = LOW    | 6   | 50  |      |

|                                |                      | FS = MID    | 12  | 100 | MHz  |

|                                |                      | FS = HIGH   | 24  | 200 |      |

# **Switching Characteristics**

| Parameter Description          |                                          | Condition                                                                                                                                                 |      | Тур           | Max  | Unit |

|--------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|------|

| F <sub>OR</sub>                | Output Frequency<br>Range                |                                                                                                                                                           |      | -             | 200  | MHz  |

| VCO <sub>LR</sub>              | VCO Lock Range                           |                                                                                                                                                           |      | _             | 400  | MHz  |

| VCO <sub>LBW</sub>             | VCO Loop Bandwidth                       |                                                                                                                                                           | 0.25 | -             | 3.5  | MHz  |

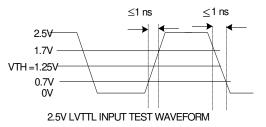

| t <sub>SKEWPR</sub>            | Matched-Pair Skew <sup>[10]</sup>        | Skew between the earliest and the latest output transi-<br>tions within the same bank.                                                                    | _    | 50            | 100  | ps   |

| t <sub>SKEW0</sub>             | Output-Output Skew <sup>[10]</sup>       | Skew between the earliest and the latest output transitions among all outputs at $0t_{\text{U}}.$                                                         | _    | 100           | 200  | ps   |

| t <sub>SKEW1</sub>             |                                          | Skew between the earliest and the latest output transi-<br>tions among all outputs for which the same phase delay<br>has been selected.                   | _    | 100           | 200  | ps   |

| t <sub>SKEW2</sub>             |                                          | Skew between the nominal output rising edge to the inverted output falling edge.                                                                          | -    | -             | 500  | ps   |

| t <sub>SKEW3</sub>             | Output-Output Skew <sup>[10]</sup>       | Skew between non-inverted outputs running at different frequencies.                                                                                       | -    | -             | 500  | ps   |

| t <sub>SKEW4</sub>             |                                          | Skew between nominal to inverted outputs running at different frequencies.                                                                                | -    | -             | 500  | ps   |

| t <sub>SKEW5</sub>             |                                          | Skew between nominal outputs at different power supply levels.                                                                                            | -    | -             | 650  | ps   |

| t <sub>PART</sub>              | Part-Part Skew                           | Skew between the outputs of any two devices under identical settings and conditions (V <sub>DDQ</sub> ,V <sub>DD</sub> ,temp, air flow, frequency, etc.). |      | _             | 750  | ps   |

| t <sub>PD0</sub>               | Ref-FB Propagation Delay <sup>[11]</sup> |                                                                                                                                                           |      | -             | +250 | ps   |

| t <sub>ODCV</sub>              | Output Duty Cycle                        | Fout < 100 MHz, measured at V <sub>DD</sub> /2                                                                                                            | 48   | 49.5/<br>50.5 | 52   | %    |

|                                |                                          | Fout > 100 MHz, measured at V <sub>DD</sub> /2                                                                                                            | 45   | 48/<br>52     | 55   |      |

| t <sub>PWH</sub>               | Output High Time<br>Deviation from 50%   | Measured at 2.0V for V <sub>DD</sub> = 3.3V and at 1.7V for V <sub>DD</sub> = 2.5V.                                                                       |      | -             | 1.5  | ns   |

| t <sub>PWL</sub>               | Output Low Time<br>Deviation from 50%    | Measured at 0.8V for $V_{DD}$ = 3.3V and at 0.7V for $V_{DD}$ = 2.5V.                                                                                     |      | -             | 2.0  | ns   |

| t <sub>R</sub> /t <sub>F</sub> | Output Rise/Fall Time                    | Measured at 0.8V – 2.0V for V <sub>DD</sub> = 3.3V and 0.7V–1.7V for V <sub>DD</sub> = 2.5V.                                                              |      | -             | 1.5  | ns   |

| t <sub>LOCK</sub>              | PLL lock time <sup>[12,13]</sup>         |                                                                                                                                                           | _    | -             | 0.5  | ms   |

| t <sub>CCJ</sub>               | Cycle-Cycle Jitter                       | Divide by one output frequency, $FS = L$ , $FB = divide by 1, 2, 4$ .                                                                                     | _    | 50            | 100  | ps   |

|                                |                                          | Divide by one output frequency, $FS = M/H$ , $FB = divide$ by 1, 2, 4.                                                                                    | -    | 70            | 150  | ps   |

- Note 10. Test load = 20 pF, terminated to  $V_{CC}/2$ . All outputs are equally loaded. 11.  $t_{PD}$  is measured at 1.5V for  $V_{DD}$  = 3.3V and at 1.25V for  $V_{DD}$  = 2.5V with REF rise/fall times of 0.5 ns between 0.8V 2.0V. 12.  $t_{LOCK}$  is the time that is required before outputs synchronize to REF. This specification is valid with stable power supplies which are within normal operating limits. 13. Lock detector circuit may be unreliable for input frequencies lower than 4 MHz, or for input signals which contain significant jitter.

# **AC Timing Definitions**

# **Ordering Information**

| Part Number    | Package Type            | Product Flow             | Status             |  |  |

|----------------|-------------------------|--------------------------|--------------------|--|--|

| CY7B9950AC     | 32 TQFP                 | Commercial, 0° to 70°C   | Not for new design |  |  |

| CY7B9950ACT    | 32 TQFP – Tape and Reel | Commercial, 0° to 70°C   | Not for new design |  |  |

| CY7B9950AI     | 32 TQFP                 | Industrial, -40° to 85°C | Not for new design |  |  |

| CY7B9950AIT    | 32 TQFP – Tape and Reel | Industrial, -40° to 85°C | Not for new design |  |  |

| Pb-free        |                         |                          |                    |  |  |

| CY7B9950AXC    | 32 TQFP                 | Commercial, 0° to 70°C   | Active             |  |  |

| CY7B9950V-5AXC | 32 TQFP                 | Commercial, 0° to 70°C   | Active             |  |  |

| CY7B9950AXCT   | 32 TQFP – Tape and Reel | Commercial, 0° to 70°C   | Active             |  |  |

| CY7B9950AXI    | 32 TQFP                 | Industrial, -40° to 85°C | Active             |  |  |

| CY7B9950AXIT   | 32 TQFP – Tape and Reel | Industrial, –40° to 85°C | Active             |  |  |

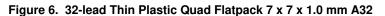

### **Package Drawing and Dimension**

### **Document History Page**

|      | Document Title: RoboClock <sup>®</sup> CY7B9950 2.5/3.3V, 200 MHz High-Speed Multi-Phase PLL Clock Buffer<br>Document Number: 38-07338 |            |                    |                                                                                                                                                                                                                                                                                 |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev. | ECN No.                                                                                                                                | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                           |  |  |

| **   | 121663                                                                                                                                 | 11/25/02   | RGL                | New Data Sheet                                                                                                                                                                                                                                                                  |  |  |

| *A   | 122548                                                                                                                                 | 12/12/02   | RGL                | Removed the PD#/DIV and DS[1:0] pins in $V_{IHH}, V_{IMM}$ and $V_{ILL}$ for both 2.5V and 3.3V DC Electrical Specs tables                                                                                                                                                      |  |  |

| *В   | 124646                                                                                                                                 | 03/05/03   | RGL                | Corrected the description of Pin 27(TEST) in the Pin Description table Corrected the description of Pin 12 ( $V_{DDQ}$ ) in the Pin Description table Corrected the Min and Max values of $V_{DD}$ from 2.25/2.75 to 2.375/2.625 Volts in the Absolute Maximum Conditions table |  |  |

| *C   | 433662                                                                                                                                 | See ECN    | RGL                | Added Lead-free devices<br>Added Jitter typical values                                                                                                                                                                                                                          |  |  |

| *D   | 1562063                                                                                                                                | See ECN    | PYG/AESA           | Added Lead-free CY7B9940V-5AXC to Ordering Information<br>Added Status column to Ordering Information table                                                                                                                                                                     |  |  |

© Cypress Semiconductor Corporation, 2002-2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 38-07338 Rev. \*D

#### Revised September 27, 2007

Page 12 of 12

RoboClock is a registered trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders. All products and company names mentioned in this document may be the trademarks of their respective holders.