# **Battery cell controller IC**

The 33772 is a SMARTMOS lithium ion Battery Cell Controller IC designed for automotive applications, such as hybrid electric (HEV) and electric vehicles (EV) along with industrial applications, such as energy storage systems (ESS), and uninterruptible power supply (UPS) systems. The device performs ADC conversions of the differential cell voltages and current, as well as battery Coulomb counting and battery temperature measurements. The information is digitally transmitted through SPI or transformer isolation to a microcontroller for processing.

### **Features**

- 5.0 V ≤ V<sub>PWR</sub> ≤ 30 V operation, 40 V transient

- 3 to 6 cells management

- · Isolated 2.0 Mbps differential communication or 4.0 Mbps SPI

- · Addressable on initialization

- · Synchronized cell voltage/current measurement with Coulomb count

- · Total stack voltage measurement

- Seven GPIO/temperature sensor inputs

- 5.0 V at 5.0 mA reference supply output

- Automatic over/undervoltage & temperature detection routable to fault pin

- Integrated Sleep mode over/undervoltage & temperature monitoring

- Onboard 300 mA passive cell balancing with diagnostics

- Hot plug capable

- Detection of internal and external faults, as open lines, shorts, and leakages

- · Single chip ASIL C capable

- Fully compatible with the MC33771 for max 14 cells

## 33772

#### **BATTERY CELL CONTROLLER IC**

AE SUFFIX (PB-FREE) 98ASA00173D 48-PIN LQFP-EP

### **Applications**

- · Automotive: 12 V and high-voltage battery packs

- · E-bikes, e-scooters

- Energy storage systems

- · Uninterruptible power supply (UPS)

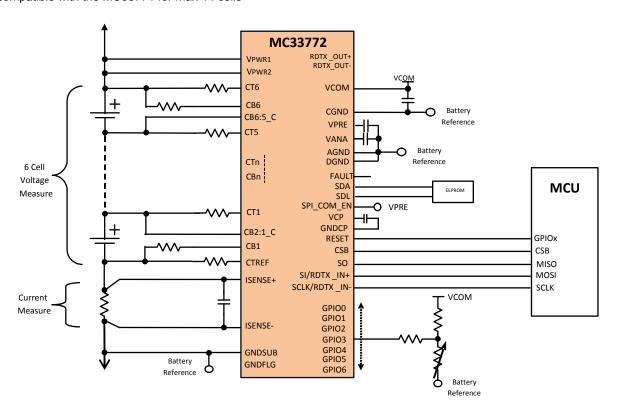

Figure 1. Simplified application diagram of SPI communication context

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

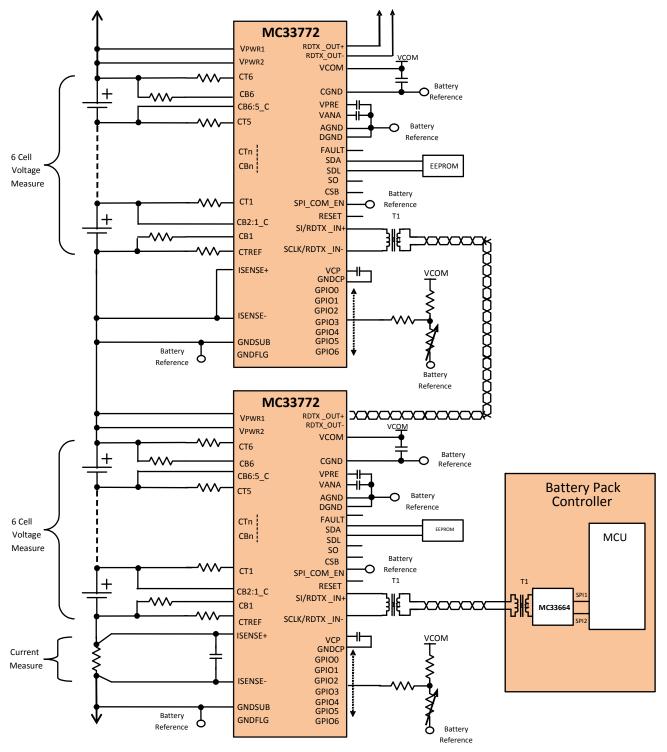

Figure 2. Simplified application diagram of twisted pair line communication with isolation transformers

Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Communication type | Calibration type | Temperature      | Number of cells    | Package         |

|----------------------------|--------------------|------------------|------------------|--------------------|-----------------|

| PC33772ASP1                | SPI version        | Type N           |                  |                    |                 |

| PC33772ATP1                | TPL version        | туре п           |                  |                    |                 |

| PC33772ASP3                | SPI version        | Type F           | -40 °C to 125 °C | Three to six cells | 48 Pin LQFP-EP  |

| PC33772ATP3                | TPL version        | Type F           | -40 C to 125 C   | Three to six cens  | 40 FIII LQFF-EF |

| PC33772ASP5                | SPI version        | Type T           |                  |                    |                 |

| PC33772ATP5                | TPL version        | турет            |                  |                    |                 |

#### Notes

1. To order parts in Tape & Reel, add the R2 suffix to the part number.

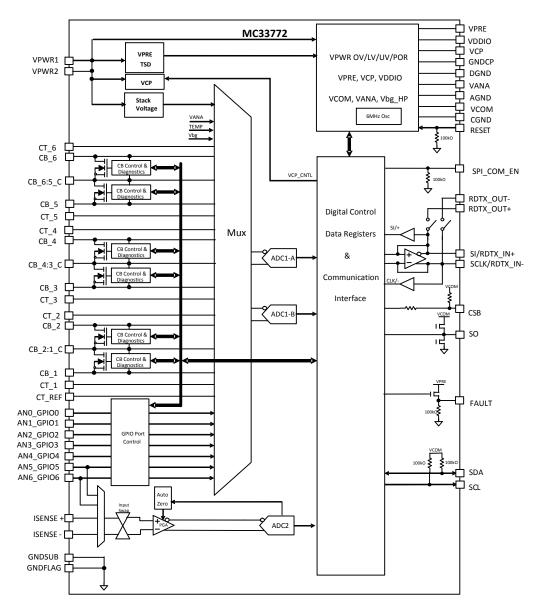

Figure 3. Simplified internal block diagram

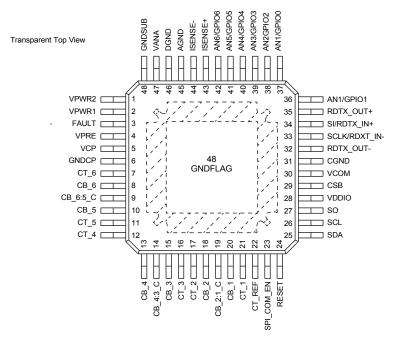

Figure 4. 33772 pinout diagram

Table 2. 33772 pin definitions

| Pin number | Pin name | Definition                                                                                             |

|------------|----------|--------------------------------------------------------------------------------------------------------|

| 1          | VPWR2    | Power input to the 33772                                                                               |

| 2          | VPWR1    | Power input to the 33772                                                                               |

| 3          | FAULT    | Fault output dependent on user defined internal or external faults. If not used, it must be left open. |

| 4          | VPRE     | Pre-regulator voltage. Connect to a 470 nF capacitor                                                   |

| 5          | VCP      | Charge pump capacitor. Connect to a 10 nF                                                              |

| 6          | GNDCP    | Charge pump capacitor ground                                                                           |

| 7          | CT_6     | Cell pin 6 input. Terminate to LPF resistor                                                            |

| 8          | CB_6     | Cell balance driver. Terminate to cell 6 cell balance load resistor                                    |

| 9          | CB_6:5_C | Cell balance 6:5 common. Terminate to cell 6 & 5 common pin                                            |

| 10         | CB_5     | Cell balance driver. Terminate to cell 5 cell balance load resistor                                    |

| 11         | CT_5     | Cell pin 5 input. Terminate to LPF resistor                                                            |

| 12         | CT_4     | Cell pin 4 input. Terminate to LPF resistor                                                            |

| 13         | CB_4     | Cell balance driver. Terminate to cell 4 cell balance load resistor                                    |

| 14         | CB_4:3_C | Cell balance 4:3 common. Terminate to cell 4 & 3 common pin                                            |

| 15         | CB_3     | Cell balance driver. Terminate to cell 3 cell balance load resistor                                    |

| 16         | CT_3     | Cell pin 3 input. Terminate to LPF resistor                                                            |

| Pin number | Pin name   | Definition                                                                                                       |

|------------|------------|------------------------------------------------------------------------------------------------------------------|

| 17         | CT_2       | Cell pin 2 input. Terminate to LPF resistor                                                                      |

| 18         | CB_2       | Cell balance driver. Terminate to cell 2 cell balance load resistor                                              |

| 19         | CB_2:1_C   | Cell Balance 2:1 common. Terminate to cell 2 & 1 common pin                                                      |

| 20         | CB_1       | Cell balance driver. Terminate to cell 1 cell balance load resistor                                              |

| 21         | CT_1       | Cell pin 1 input. Terminate to LPF resistor                                                                      |

| 22         | CT_REF     | Cell pin REF input. Terminate to LPF resistor                                                                    |

| 23         | SPI_COM_EN | SPI communication enable, pin must be high for SPI to be active.                                                 |

| 24         | RESET      | RESET is an active high input. RESET has an internal pull-down. If not used, it can be tied to GND.              |

| 25         | SDA        | I <sup>2</sup> C data                                                                                            |

| 26         | SCL        | I <sup>2</sup> C clock                                                                                           |

| 27         | SO         | SPI serial output                                                                                                |

| 28         | VDDIO      | IO voltage for I <sup>2</sup> C and SPI interfaces. Voltage level corresponding to Logic 1 are the same as VDDIO |

| 29         | CSB        | SPI chip select                                                                                                  |

| 30         | VCOM       | Communication regulator output, decouple with 2.2 $\mu\text{F}$ ceramic                                          |

| 31         | CGND       | Communication decoupling ground, terminate to GNDSUB                                                             |

| 32         | RDTX_OUT-  | Receive/transmit output negative                                                                                 |

#### 33772

Table 2. 33772 pin definitions (continued)

| Pin number | Pin name      | Definition                                           |

|------------|---------------|------------------------------------------------------|

| 33         | SCLK/RDTX_IN- | SPI clock or receive/transmit input negative         |

| 34         | SI/RDTX_IN+   | SPI serial input or receiver/transmit input positive |

| 35         | RDTX_OUT+     | Receive/transmit output positive                     |

| 36         | AN0/GPIO0     | General purpose analog input or GPIO                 |

| 37         | AN1/GPIO1     | General purpose analog input or GPIO                 |

| 38         | AN2/GPIO2     | General purpose analog input or GPIO                 |

| 39         | AN3/GPIO3     | General purpose analog input or GPIO                 |

| 40         | AN4/GPIO4     | General purpose analog input or GPIO                 |

| 41         | AN5/GPIO5     | General purpose analog input or GPIO                 |

| Pin number | Pin name  | Definition                                                                                              |

|------------|-----------|---------------------------------------------------------------------------------------------------------|

| 42         | AN6/GPIO6 | General purpose analog input or GPIO                                                                    |

| 43         | ISENSE+   | Current measurement input+                                                                              |

| 44         | ISENSE-   | Current measurement input-                                                                              |

| 45         | AGND      | Analog ground, terminate to GNDSUB                                                                      |

| 46         | DGND      | Digital ground, terminate to GNDSUB                                                                     |

| 47         | VANA      | Precision ADC analog supply. Decouple with ceramic 47 nF ceramic capacitor to AGND                      |

| 48         | GNDSUB    | Ground reference for device, terminate to reference of battery cluster. Note: GNDREF is an alias of it. |

| 49         | GNDFLAG   | Device flag, terminate to lowest potential of battery cluster                                           |

### Table 3. Key parameters

Characteristics noted under SPI mode conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, TPL mode: 7.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 24 V, T<sub>A</sub> = 25 °C, unless otherwise noted. Before starting any development, it is recommended to request a copy of the full 33772 data sheet.

| Symbol                       | Characteristic                                                                                                               |             | Unit | Notes |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|

| Power manageme               | nt                                                                                                                           |             |      |       |

| I <sub>VPWR</sub>            | Supply Current (base value)  • Normal mode, Cell Balance OFF, ADC Inactive, Communication Inactive, I <sub>VCOM</sub> = 0 mA | 5.8         | mA   |       |

| I <sub>VPWR(CBON)</sub>      | Supply Current adder to set all 6 Cell Balance switches ON                                                                   | 0.97        | mA   |       |

| I <sub>VPWR(ADC)</sub>       | Delta Supply Current to perform ADC conversions (addend)  • ADC1-A,B continuously converting  • ADC2 continuously converting | 2.9<br>1.17 | mA   |       |

| I <sub>VPWR(SS)</sub>        | Supply Current in Sleep mode, Communication Inactive, Cell Balance OFF, Oscillator Monitor ON  • SPI mode  • TPL mode        | 32<br>50    | μА   |       |

| t <sub>VPWR(FILTER)</sub>    | V <sub>PWR</sub> OV, LV, UV Filter                                                                                           | 50          | μs   |       |

| VPRE power supp              | lly                                                                                                                          |             |      | -     |

| V <sub>VPRE(UV_TH)</sub>     | Undervoltage Threshold for V <sub>CP</sub> minus V <sub>PRE</sub>                                                            | 4.25        | V    |       |

| /CP power supply             | /                                                                                                                            |             |      |       |

| V <sub>CP(UV_TH)</sub>       | Undervoltage Threshold for V <sub>CP</sub> minus V <sub>PRE</sub>                                                            | 1.5         | V    |       |

| /COM power sup               | ply                                                                                                                          |             |      |       |

| V <sub>COM</sub>             | VCOM Output Voltage                                                                                                          | 5.0         | V    |       |

| V <sub>COM(UV)</sub>         | VCOM Undervoltage Fault Threshold                                                                                            | 4.5         | V    |       |

| V <sub>COM_HYS</sub>         | VCOM Undervoltage Hysteresis                                                                                                 | 100         | mV   |       |

| VDDIO power sup              | ply                                                                                                                          |             |      |       |

| t <sub>VCOM(FLT_TIMER)</sub> | VCOM Undervoltage Fault Timer                                                                                                | 10          | μs   |       |

| t <sub>VCOM(RETRY)</sub>     | VCOM Fault Retry Timer                                                                                                       | 10          | ms   |       |

| R <sub>VCOM(SS)</sub>        | VCOM Sleep Mode Pull-down Resistor                                                                                           | 2.0         | kΩ   |       |

Characteristics noted under SPI mode conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, TPL mode: 7.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 24 V, T<sub>A</sub> = 25 °C, unless otherwise noted. Before starting any development, it is recommended to request a copy of the full 33772 data sheet.

| Symbol                       | Characteristic                                                 | Тур.     | Unit   | Notes    |

|------------------------------|----------------------------------------------------------------|----------|--------|----------|

| VANA power supp              | bly                                                            | <u> </u> | I      | <u> </u> |

|                              | VANA Output Voltage (NOT USED BY EXTERNAL CIRCUITS)            | 2.05     | V      |          |

| $V_{ANA}$                    | Decouple with 47 nF X7R 0603 or 0402                           | 2.65     | V      |          |

| $V_{ANA(UV)}$                | VANA Undervoltage Fault Threshold                              | 2.4      | V      |          |

| V <sub>ANA_HYS</sub>         | VANA Undervoltage Hysteresis                                   | 50       | mV     |          |

| t <sub>VANA(FLT_TIMER)</sub> | VANA Undervoltage Fault Timer                                  | 11       | μs     |          |

| V <sub>ANA (OV)</sub>        | VANA Overvoltage Fault Threshold                               | 2.8      | V      |          |

| t <sub>VANA(RETRY)</sub>     | VANA Fault Retry Timer                                         | 10       | ms     |          |

| R <sub>VANA_RPD</sub>        | VANA Sleep Mode Pull-down Resistor                             | 1.0      | kΩ     |          |

| DC1-A, ADC1-B                | ,                                                              | <b>'</b> |        |          |

| CTn <sub>(LEAKAGE)</sub>     | Cell Terminal Input Leakage Current                            | 10       | nA     |          |

| CTn <sub>(FV)</sub>          | Cell Terminal Input Current - Functional Verification          | 1.0      | mA     |          |

| CT <sub>N</sub>              | Cell Terminal Input Current During Conversion                  | 100      | nA     |          |

| R <sub>PD</sub>              | Cell Terminal Open Load Detection Pull-down Resistor           | 950      | Ω      |          |

| V <sub>VPWR_RES</sub>        | VPWR Terminal Measurement Resolution                           | 2.4415   | mV/LSB |          |

| V <sub>CT_ANx_RES</sub>      | Cell Voltage and ANx Resolution in 15-bits MEAS_xxxx registers | 152.5925 | μV/LSB |          |

|                              | Single Channel Net Conversion Time                             |          |        |          |

| t <sub>VCONV</sub>           | 16-Bit Resolution                                              | 25.36    | μs     |          |

| V <sub>V_NOISE</sub>         | • 16-Bit Resolution 400 μVrms                                  |          | μVrms  |          |

| DC2/current sen              | se module                                                      | -        |        |          |

| I <sub>ISENSE_OL</sub>       | ISENSE Open Load injected current                              | 130      | μΑ     |          |

| V <sub>ISENSE_OL</sub>       | ISENSE Open Load detection threshold                           | 460      | mV     |          |

| V <sub>2RES</sub>            | ADC Resolution                                                 | 0.6      | μV/LSB |          |

|                              | PGA saturation half-range                                      |          |        |          |

|                              | • Gain = 256                                                   | 4.9      |        |          |

| $V_{PGA\_SAT}$               | • Gain = 64                                                    | 19.5     | mV     |          |

|                              | • Gain = 16<br>• Gain = 4                                      | 78.1     |        |          |

|                              |                                                                | 150.0    |        |          |

|                              | Voltage threshold for PGA gain increase • Gain = 256           | _        |        |          |

| $V_{PGA\_ITH}$               | • Gain = 64                                                    | 2.344    | mV     |          |

| PGA_IIII                     | • Gain = 16                                                    | 9.375    |        |          |

|                              | • Gain = 4                                                     | 37.50    |        |          |

|                              | Voltage threshold for PGA gain decrease                        |          |        |          |

|                              | • Gain = 256                                                   | 4.298    |        |          |

| $V_{PGA\_DTH}$               | • Gain = 64                                                    | 17.188   | mV     |          |

| -                            | • Gain = 16                                                    | 68.750   |        |          |

|                              | • Gain = 4                                                     | -        |        |          |

| t <sub>PGA_SETTLE</sub>      | PGA settling time after a chopper event                        | 14.0     | μs     |          |

| t <sub>ICONV</sub>           | ADC Conversion Time including PGA settling time                |          | μs     |          |

|                              | 16-Bit Resolution                                              | 37.67    |        |          |

| $V_{I\_NOISE}$               | Noise at 16-bit Conversion                                     | 3.01     | μVrms  |          |

#### 33772

Characteristics noted under SPI mode conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, TPL mode: 7.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 24 V, T<sub>A</sub> = 25 °C, unless otherwise noted. Before starting any development, it is recommended to request a copy of the full 33772 data sheet.

| Symbol                     | Characteristic                                                                                                                                 | Тур.            | Unit  | Notes |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-------|

| ADC2/current sens          | se module (continued)                                                                                                                          |                 | I.    |       |

| V <sub>I_NOISE</sub>       | Noise Error at 13-bit Conversion                                                                                                               | 8.33            | μVrms |       |

| ADC <sub>CLK</sub>         | ADC2 and ADC1-A,B Clocking Frequency                                                                                                           | 6.0             | MHz   |       |

| Cell balance drive         | rs                                                                                                                                             |                 | 1     | 1     |

| V <sub>DS(CLAMP)</sub>     | Cell Balance Driver VDS Active Clamp Voltage  • Clamp Energy tbd                                                                               | 11              | V     |       |

| V <sub>OUT(FLT_TH)</sub>   | Output Fault Detection Voltage Threshold  • Balance OFF (Open Load)  • Balance ON (Shorted Load)                                               | 0.55            | V     |       |

| R <sub>PD_CB</sub>         | Output OFF Open Load Detection Pull-down Resistor  • Balance OFF, Open Load Detect Disabled                                                    | 2.0             | kΩ    |       |

| R <sub>DS(on)</sub>        | Drain-to-Source ON Resistance  • $I_{OUT}$ = 300 mA, $T_J$ = 105 °C  • $I_{OUT}$ = 300 mA, $T_J$ = 25 °C  • $I_{OUT}$ = 300 mA, $T_J$ = -40 °C | _<br>0.5<br>0.4 | Ω     |       |

| t <sub>ON</sub>            | Cell Balance Driver Turn On<br>• $R_L = 15 \Omega$                                                                                             | 350             | μs    |       |

| t <sub>OFF</sub>           | Cell Balance Driver Turn Off<br>• $R_L = 15 \Omega$                                                                                            | 200             | μs    |       |

| t <sub>BAL_DEGLICTH</sub>  | Short/Open Detect Filter Time                                                                                                                  | 20              | μs    |       |

| nternal temperatu          | re measurement                                                                                                                                 |                 | •     |       |

| IC_TEMP1_RES               | IC Temperature Resolution                                                                                                                      | 0.032           | K/LSB |       |

| T <sub>SD_TH</sub>         | Thermal Shutdown                                                                                                                               | 170             | °C    |       |

| T <sub>SD_HYS</sub>        | Thermal Shutdown Hysteresis                                                                                                                    | 10              | °C    |       |

| General purpose i          | nput/output GPIOx                                                                                                                              | <b>'</b>        |       | 1     |

| V <sub>OL(TH)</sub>        | Analog Input Open Pin Detect Threshold                                                                                                         | 0.15            | V     |       |

| R <sub>OPENPU</sub>        | Internal Open detection Pull-down Resistor                                                                                                     | 5.0             | kΩ    |       |

|                            | GPIO0 WU De-glitch Filter                                                                                                                      | 50              | μs    |       |

|                            | GPIO0 Daisy Chain De-glitch Filter both edges                                                                                                  | 20              | μs    |       |

|                            | GPIO2 Convert Trigger De-glitch Filter                                                                                                         | 2.0             | μs    |       |

| Reset input                |                                                                                                                                                | <u> </u>        | l     | 1     |

| t <sub>RESETFLT</sub>      | RESET De-glitch Filter                                                                                                                         | 100             | μs    |       |

| R <sub>RESET_PD</sub>      | Input Logic Pull-down (RESET)                                                                                                                  | 100             | kΩ    |       |

| SPI_COM_EN inpu            | ıt                                                                                                                                             | 1               | 1     | 1     |

| V <sub>HYS</sub>           | Input Hysteresis                                                                                                                               | 125             | mV    |       |

| R <sub>SPI_COM_EN_PD</sub> | Input Pull-down Resistor (SPI_COM_EN)                                                                                                          | 100             | kΩ    |       |

| Bus switch for TP          | L communication                                                                                                                                | 1               | 1     | 1     |

| RX <sub>TERM</sub>         | Bus Termination Resistor (open resistor when bus switch is closed)                                                                             | 300             | Ω     | 1     |

Remark: if the bus switch is closed, the termination resistor is open, else the termination resistor is connected. At the end of the daisy chain the switch must be open, so the transmission line is properly terminated.

Characteristics noted under SPI mode conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, TPL mode: 7.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 24 V, T<sub>A</sub> = 25 °C, unless otherwise noted. Before starting any development, it is recommended to request a copy of the full 33772 data sheet.

| Symbol                    | Characteristic                                                                                                                                                                                                    |       | Unit | Notes |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|

| Digital interface         |                                                                                                                                                                                                                   |       |      |       |

|                           | FAULT Output (High Active, I <sub>OH</sub> = 1.0 mA)                                                                                                                                                              | 4.9   | V    |       |

|                           | FAULT Output Pull-down Resistance                                                                                                                                                                                 | 100   | kΩ   |       |

| V <sub>HYS</sub>          | Input Hysteresis SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL                                                                                                                                                        | 80    | mV   |       |

| R <sub>SCLK_PD</sub>      | Input Logic Pull-down Resistance (SCLK/RDTX_IN-, SI/RDTX+)                                                                                                                                                        | 20    | kΩ   |       |

| R_ <sub>PU</sub>          | Input Logic Pull-up Resistance to V <sub>COM</sub> (CSB, SDA, SCL)                                                                                                                                                | 100   | kΩ   |       |

| CSB <sub>WU_FLT</sub>     | CSB Wake-up De-glitch Filter, Low to High Transition                                                                                                                                                              | 50    | μs   |       |

| System timing             | -                                                                                                                                                                                                                 |       | l .  | 1     |

| t <sub>CELL_CONV</sub>    | Time needed to acquire all 6 cell voltages and the current after an on demand conversion  • 16-Bit Resolution                                                                                                     | 208   | μs   |       |

| t <sub>SYNC</sub>         | V/I time synchronization • ADC1-A,B at 16-Bit, ADC2 at 16-Bit                                                                                                                                                     | 113   | μs   |       |

| twake_delay               | Time between wake pulses                                                                                                                                                                                          | 600   | μs   |       |

| t <sub>IDLE</sub>         | Idle time out after POR                                                                                                                                                                                           | 60    | S    |       |

| t <sub>WAKE_INIT</sub>    | Wake-up signaling time out after POR                                                                                                                                                                              | 0.75  | S    |       |

| t <sub>DIAG</sub>         | Diagnostic Mode Time-out                                                                                                                                                                                          | 1.0   | S    |       |

| t <sub>EOC</sub>          | SOC to Data Ready (includes post processing of data)  • 16-Bit Resolution                                                                                                                                         |       | μs   |       |

| t <sub>SETTLE</sub>       | Time after SOC to begin converting with ADC1-A,b                                                                                                                                                                  | 12.28 | μs   |       |

| t <sub>CLST_TPL</sub>     | Time needed to send a SOC command and read back 6 cell voltages, 7 temperatures, 1 current, 1 Coulomb counter with TPL communication working at 2.0 Mbps and ADC1-A,B configured as follows:  • 16-Bit Resolution |       | ms   |       |

| t <sub>CLST_SPI</sub>     | Time needed to send a SOC command and read back 6 cell voltages, 7 temperatures, 1 current, 1 Coulomb counter with SPI communication working at 4.0 Mbps and ADC1-A,B configured as follows:  • 16-Bit Resolution | 0.86  | ms   |       |

| t <sub>I2C_ACCESS</sub>   | EEPROM Access Time, EEPROM Write (depends on device selection)                                                                                                                                                    | 5.0   | ms   |       |

| t <sub>WAVE_DC_BITx</sub> | Daisy Chain Duty Cycle OFF Time  • t <sub>WAVE_DC_BITx</sub> = 00                                                                                                                                                 | 500   | μs   |       |

| t <sub>WAVE_DC_BITx</sub> | Daisy Chain Duty Cycle OFF Time  • twave_DC_Bitx = 01                                                                                                                                                             | 1.0   | ms   |       |

| t <sub>WAVE_DC_BITx</sub> | Daisy Chain Duty Cycle OFF Time  • twave_dc_Bitx = 10                                                                                                                                                             |       | ms   |       |

| t <sub>WAVE_DC_BITx</sub> | Daisy Chain Duty Cycle OFF Time  • twave_dc_Bitx = 11                                                                                                                                                             | 100   | ms   |       |

| t <sub>WAVE_DC_ON</sub>   | Daisy Chain Duty Cycle ON Time                                                                                                                                                                                    | 500   | μs   |       |

| t <sub>SLEEP</sub>        | Time out to enter Sleep Mode in the absence of TPL communication                                                                                                                                                  | 1024  | ms   |       |

Characteristics noted under SPI mode conditions 5.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, TPL mode: 7.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  30 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 24 V, T<sub>A</sub> = 25 °C, unless otherwise noted. Before starting any development, it is recommended to request a copy of the full 33772 data sheet.

| Symbol                     | Characteristic                               | Тур.  | Unit | Notes |  |  |

|----------------------------|----------------------------------------------|-------|------|-------|--|--|

| Transformer inter          | ransformer interface                         |       |      |       |  |  |

| t <sub>RES</sub>           | Slave Response After Write Command (echo)    | 2.35  | μs   |       |  |  |

|                            | Time Between Slave Response Messages (Q)     | 1.5   | μs   |       |  |  |

|                            | Start of Message (S)                         | 500   | ns   |       |  |  |

|                            | Start of Message Delay (T)                   | 250   | ns   |       |  |  |

|                            | Bit Time (U)                                 | 250   | ns   |       |  |  |

|                            | Bit Delay (V)                                |       | ns   |       |  |  |

|                            | Message Duration (R)                         | 21.25 | μs   |       |  |  |

| VRDTX <sub>INTH</sub>      | Differential Receiver Threshold              | 0.74  | V    |       |  |  |

| VRDTX <sub>INHYS</sub>     | Differential Receiver Threshold Hysteresis   | 130   | mV   |       |  |  |

| V <sub>RDTX(PK_DIFF)</sub> | Amplifier Differential Output Voltage        | 2.5   | V    |       |  |  |

| V <sub>RDTX_BIAS</sub>     | Transformer Bias Voltage  • Driver tri-state | 2.5   | V    |       |  |  |

| Revision | Date   | Description of changes        |

|----------|--------|-------------------------------|

| 2.0      | 8/2016 | Added revision history table. |

#### How to Reach Us:

Home Page: NXP.com

Web Support:

http://www.nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no expressed or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation, consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by the customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address:

http://www.nxp.com/terms-of-use.html.

NXP, the NXP logo, Freescale, the Freescale logo and SMARTMOS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. All rights reserved.

© 2016 NXP B.V.

Document Number: MC33772SM

Rev. 2.0 8/2016