# CMX608/CMX618/ CMX638 RALCWI Vocoders

D/608\_18\_38/11 September 2014

Provisional Issue

#### **Features**

- Near Toll Quality RALCWI Coding Algorithm

- Multiple Bit Rate Modes:

- 2400 or 2750 bps

- 3600 bps with FEC Enabled

- 4-bit Viterbi Soft Decision Decoding

- Integrated Audio CODEC (CMX618/CMX638 only)

- Integrated Input and Output Channel Filters

- 20ms, 40ms, 60ms and 80ms Packet Lengths

- No Licensing or Royalty Payments

- Ancillary Audio Functions:

- Voice Activity Detector

- Comfort Noise Generator

- DTMF and Single Tone Regeneration

- 1.8V Low Power Operation, 3.3V Tolerant I/O

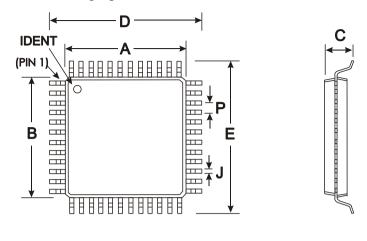

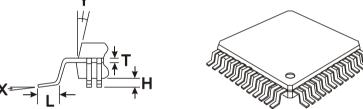

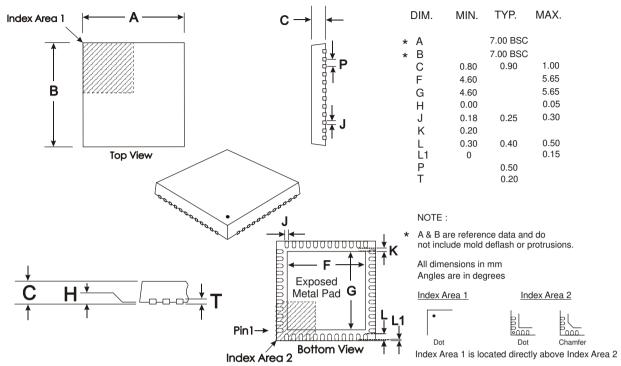

- Small 48-pin LQFP and VQFN Packages

## **Applications**

- Digital PMR, LMR, Voice Radio

- · Digital Trunking

- DMR TDMA

- DMR FDMA, dPMR

- Digital Voice Scrambling and Encryption

- Digital WLL

- Voice Storage and Playback Systems

- Regenerative Digital Voice Repeaters

- · Messaging Systems

- VoIP Systems

- Voice Pagers

- Half-Duplex Vocoding (CMX608/CMX618)

- Full-Duplex Vocoding (CMX638 only)

## 1. Brief Description

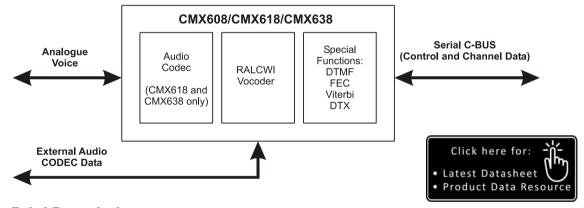

The CMX608/CMX618/CMX638 are flexible, high integration, high performance, RALCWI (Robust Advanced Low Complexity Waveform Interpolation) Vocoders, offering near toll quality voice at very low bit rates. A Forward Error Correction (FEC) engine provides optimum performance in real life applications. The RALCWI Vocoder comprises four independent functions which are selectable by the host: Voice Encoder, FEC Encoder, Voice Decoder and FEC Decoder. The CMX608 and CMX618 are half-duplex Vocoders and the CMX638 is a full-duplex Vocoder with integrated voice CODEC. The CMX618 includes an integrated voice CODEC, offering a complete analogue voice to low bit rate vocoded data function, with integrated channel filters removing the need for external components, whereas the CMX608 requires an external voice CODEC.

CMX608/CMX618/CMX638 operate from a dual power supply (1.8V and 3.3V) and are available in both 48-pin LQFP (L4) and 48-pin VQFN (Q3) packages.

\*\*Continued overleaf .....

In encode mode, the voice encoder uses a 20ms voice frame size with two programmable bit rates: 2400bps or 2750bps. The optional FEC encoder performs channel coding of the encoded voice (2400bps or 2750bps, depending on the selected mode) and forms an encoded, interleaved bit-stream of 3600bps (216 bits per 60ms packet or 288 bits per 80ms packet). The FEC operation utilises a packet of either 3 or 4 x 20ms Vocoder frames to provide optimum error correction performance.

In decode mode, the optional FEC decoder performs de-interleaving and channel decoding of the coded bit-stream (216 bits per 60ms packet or 288 bits per 80ms packet) and forms an error-corrected bit-stream of encoded voice at 2400bps or 2750bps rate, depending on the selected mode. The FEC decoder can optionally use "soft decision" metrics to improve its decoding ability. The voice decoder then converts the error-corrected bit-stream back into a digitised voice signal.

Soft Decision Decoding (SDD), Discontinuous Transmission detection (DTX), Voice Activity Detection (VAD) and Comfort Noise Generation (CNG) functions are also included, to further enhance the overall performance. Single (STD) and Dual (DTMF) Tones can be detected and sent separately in the coded bit-stream, then regenerated at the far end.

New features and enhancements to existing functions may be provided from time to time, expanding the capabilities of the Vocoder. These are provided as Function Images™, a hex format file that can be loaded via the C-BUS at run-time. Function Images™ can be downloaded from the CML Portal, a secure area of the CML website. Details of currently available Function Images™ can be found in the CMX608/CMX618/CMX638 Product page on the CML website.

## **CONTENTS**

| Secti | <u>ion</u>                                                            | <u>Page</u> |

|-------|-----------------------------------------------------------------------|-------------|

| 1.    | Brief Description                                                     | 1           |

| 2.    | Block Diagram                                                         | 5           |

| 3.    | Signal List                                                           | 6           |

| 4.    |                                                                       |             |

| 4.    | 4.1. PCB Layout Guidelines and Power Supply Decoupling                |             |

|       | 4.2. Audio CODEC External Components (CMX618/CMX638 only)             | 11          |

| _     |                                                                       |             |

| 5.    | 5.1. Initialisation                                                   |             |

|       | 5.2. Encoder                                                          |             |

|       | 5.2.1. Single Frame Packet, without FEC, STD or DTMF                  |             |

|       | 5.2.2. Multiple Frame Packet with FEC, but without STD or DTMF        | 16          |

|       | 5.3. Decoder                                                          | 16          |

|       | 5.3.1. Single Frame Packet, without FEC, STD or DTMF                  |             |

|       | 5.3.2. Multiple Frame Packet with FEC, but without STD or DTMF        |             |

|       | 5.4. Overall Signal Latency                                           |             |

|       | 5.5.1. Packets of Raw Vocoder Frames                                  |             |

|       | 5.5.2. Packets of FEC Protected Frames                                |             |

|       | 5.6. External CODEC Support                                           |             |

|       | 5.7. Operation with DTMF (Dual Tone Multi-Frequency)                  |             |

|       | 5.7.1. DTMF Transmit                                                  |             |

|       | 5.7.2. DTMF Receive                                                   |             |

|       | 5.7.3. DTMF Format                                                    |             |

|       | 5.9. C-BUS Interface                                                  |             |

|       | 5.10. C-BUS Registers                                                 |             |

|       | 5.10.1. Command Registers                                             |             |

|       | 5.10.2. 8 Bit Write-Only Registers                                    |             |

|       | 5.10.3. 8 Bit Read-Only Registers                                     |             |

|       | 5.10.4. 16-bit Write-Only Registers                                   |             |

|       | 5.10.5. 16-bit Read-Only Registers                                    |             |

| 6.    | Application Notes                                                     |             |

|       | 6.1. Basic Operation of the Vocoder                                   |             |

|       | 6.2. FEC and LLR Decoding                                             |             |

|       | 6.3. DTX and SID Functions                                            |             |

|       | 6.5. Slip Management                                                  |             |

|       | 6.6. Setting the Watermarks for the Vocoder Data Input (Output) FIFOs |             |

|       | 6.7. Download Protocol for Function Images™                           |             |

|       | 6.8. Using the PLEVEL register to set the Input Gain                  |             |

| 7.    | Performance Specification                                             | 61          |

|       | 7.1. Electrical Performance                                           | 61          |

|       | 7.1.1. Absolute Maximum Ratings                                       |             |

|       | 7.1.2. Operating Limits                                               |             |

|       | 7.1.3. Operating Characteristics                                      |             |

|       | // I GUNGUIIU                                                         | no          |

| <u>Table</u>                                                            | <u>Page</u> |

|-------------------------------------------------------------------------|-------------|

| Table 1 Clock/Crystal Selection                                         | 10          |

| Table 2 DTMF - Format 1                                                 | 27          |

| Table 3 Standard DTMF Keypad Layout                                     | 28          |

| Table 4 DTMF - Format 2                                                 |             |

| Table 5 C-BUS Register Addresses                                        |             |

| Table 6 Decoder Packet Description                                      | 43          |

| Table 7 Encoder Packet Description                                      | 45          |

| Figure                                                                  | <u>Page</u> |

| Figure 1 Block Diagram                                                  |             |

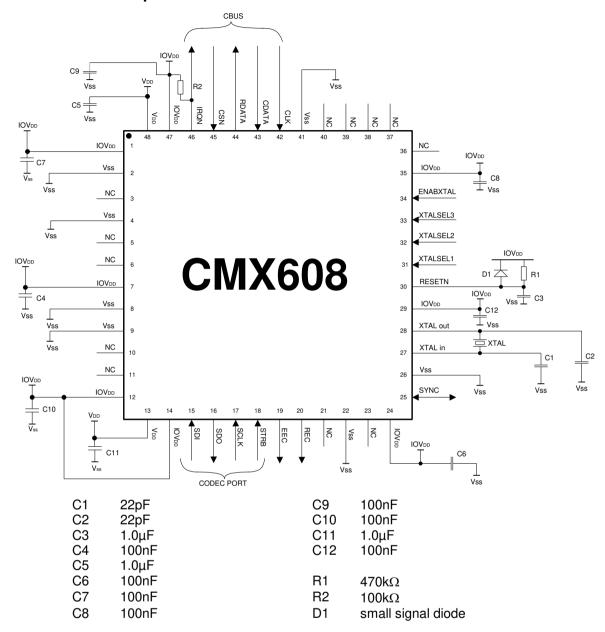

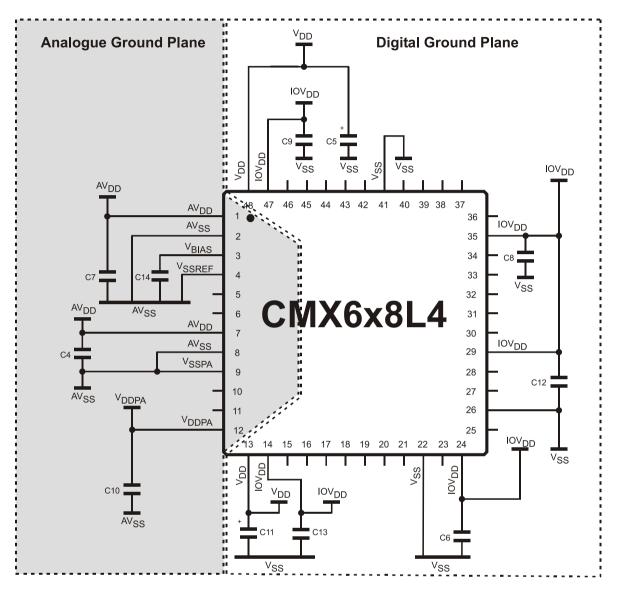

| Figure 2 CMX608 Recommended External Components                         | 9           |

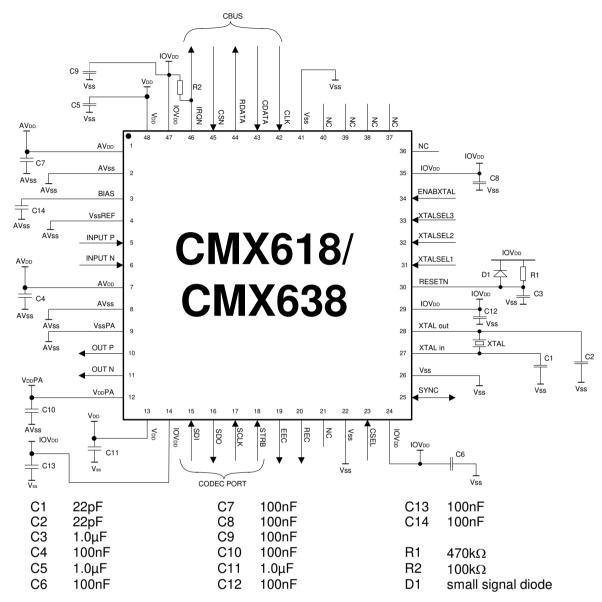

| Figure 3 CMX618/CMX638 Recommended External Components                  |             |

| Figure 4 CMX618/CMX638 Power Supply and De-coupling                     | 11          |

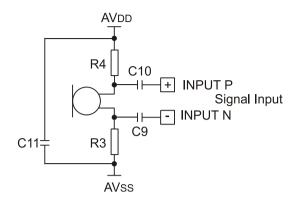

| Figure 5 Recommended External Components – Differential CODEC Inputs    | 12          |

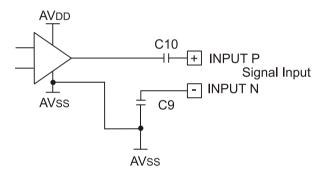

| Figure 6 Recommended External Components – Single-ended CODEC Inputs    |             |

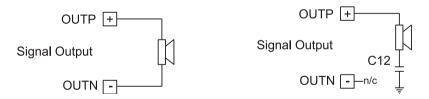

| Figure 7 Recommended External Components – CODEC Output                 |             |

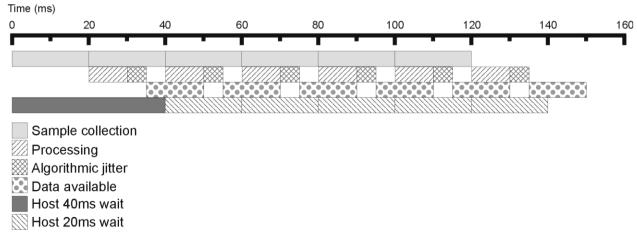

| Figure 8 Single Frame Packet Encoding                                   |             |

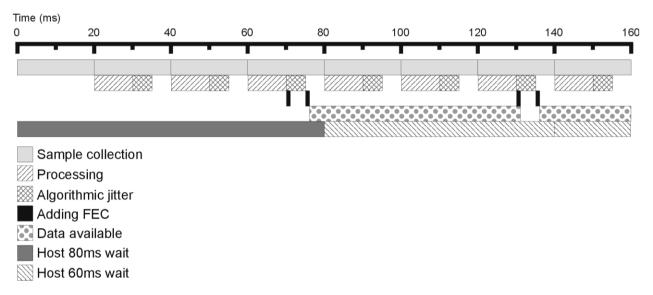

| Figure 9 Multiple Frame Packet Encoding                                 |             |

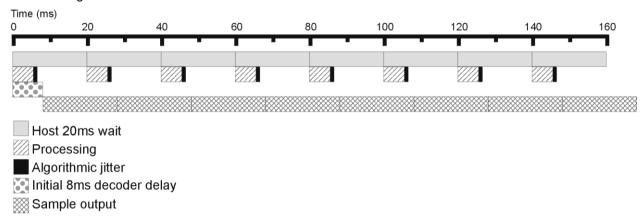

| Figure 10 Single Frame Packet Decoding                                  |             |

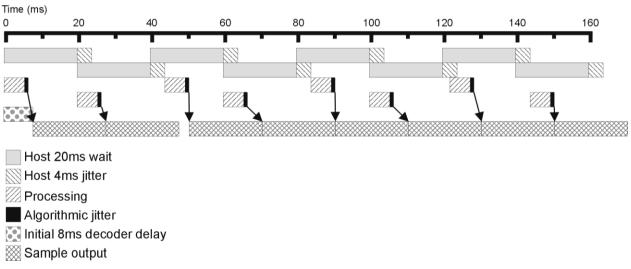

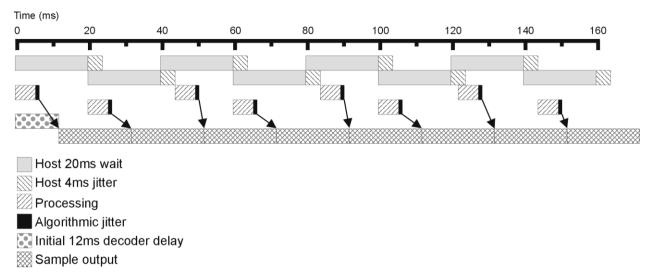

| Figure 11 Single Frame Packet Decoding with Host Jitter                 |             |

| Figure 12 Single Frame Packet Decoding with Host Jitter (Increased IDD) | 19          |

| Figure 13 Multiple Frame Packet Decoding                                |             |

| Figure 14 Overall Signal Latency                                        |             |

| Figure 15 PCM3500 Interface                                             |             |

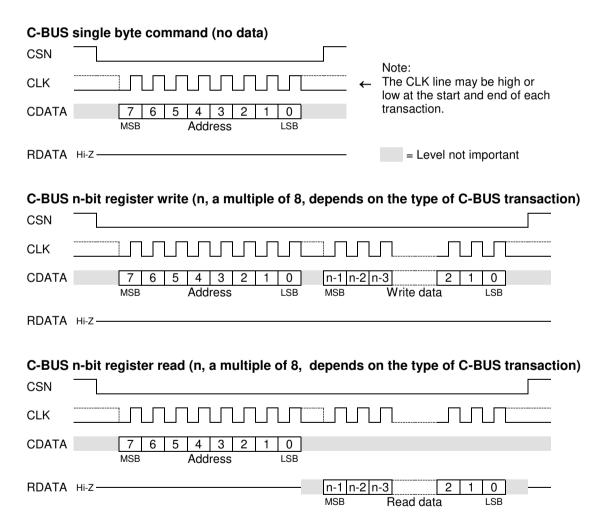

| Figure 16 Basic C-BUS Transactions                                      |             |

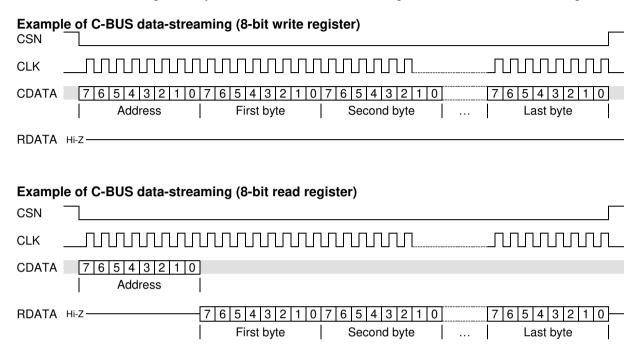

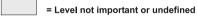

| Figure 17 C-BUS Data-Streaming Operation                                |             |

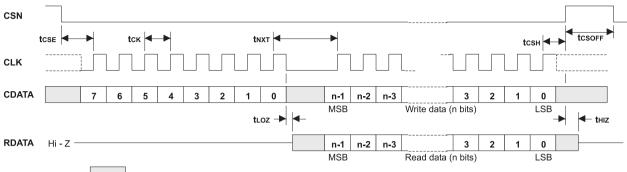

| Figure 18 C-BUS Timing                                                  |             |

| Figure 19 CODEC (SSP) Port Timing (Slave Mode)                          |             |

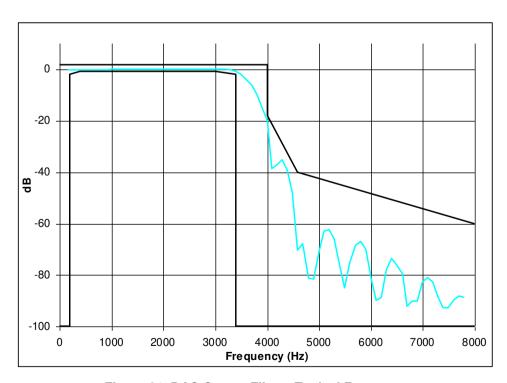

| Figure 20 ADC Input Filter - Typical Response                           |             |

| Figure 21 DAC Output Filter - Typical Response                          |             |

| Figure 22 48-pin LQFP Mechanical Outline (L4)                           |             |

| Figure 23 48-pin VQFN Mechanical Outline (Q3)                           | 69          |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [http://www.cmlmicro.com/].

## **History**

| Version | Changes                                                                                            | Date     |

|---------|----------------------------------------------------------------------------------------------------|----------|

| 11      | Editorial improvements                                                                             | 19.09.14 |

| 10      | Corrected the lack of termination of the SYNC pin (pin 25)                                         | 31.07.12 |

| 9       | • Corrected minor rerrors and the table definition of bits 2, 3 in section 5.10.1.                 | 19.05.09 |

| 8       | • Clarified the function of the ENABXTAL and RESETN/General Reset functions.                       | 12.12.08 |

|         | Added power supply ground plane layout drawing.                                                    |          |

| 7       | Clarification of when to write packets in full duplex mode                                         | 18.07.08 |

|         | <ul> <li>Information added about loading Function Images™ into the device</li> </ul>               |          |

|         | Clarification on choice of Xtal and Clock speed                                                    |          |

|         | <ul> <li>Clarification on use of the CLOCK and DTMFATTEN registers</li> </ul>                      |          |

|         | <ul> <li>Information added about use of the PLEVEL (peak level) register</li> </ul>                |          |

|         | <ul> <li>Corrections to "Basic Operation of the Vocoder" (section 6.1) and to "Download</li> </ul> |          |

|         | Protocol for Function Updates" (section 6.7)                                                       |          |

|         | Typical I <sub>DD</sub> Digital current consumption figure amended for full duplex mode            |          |

|         | <ul> <li>Correction to the description of dPMR frames in section 5.4.2</li> </ul>                  |          |

| 6       | First Release of document with CMX638 (full-duplex device) included                                | 19.03.08 |

## 2. Block Diagram

Figure 1 Block Diagram

## 3. Signal List

| CMX608/<br>CMX618/<br>CMX638<br>L4/Q3 | Signal                   |                   | Description                                                |  |  |  |  |

|---------------------------------------|--------------------------|-------------------|------------------------------------------------------------|--|--|--|--|

| Pin No.                               | Name                     | Туре              |                                                            |  |  |  |  |

| 1                                     | $AV_DD$                  | Power             | CMX618/CMX638: Analogue Positive Power Supply 3.3V         |  |  |  |  |

| ı                                     | A V DD                   | i owei            | CMX608: Not used (connect to IOV <sub>DD</sub> )           |  |  |  |  |

| 2                                     | $AV_{SS}$                | Power             | CMX618/CMX638: Analogue Negative Power Supply 0V           |  |  |  |  |

| 2                                     | AVSS                     | rowei             | CMX608: Not used (connect to V <sub>SS</sub> )             |  |  |  |  |

| 3                                     | BIAS                     | Analogue          | CMX618/CMX638: Analogue Bias (approximately 1.65 Volts)    |  |  |  |  |

| 3                                     | DIAG                     | Output            | CMX608: Not used (leave unconnected)                       |  |  |  |  |

| 4                                     | V <sub>SS</sub> REF      | Power             | CMX618/CMX638: Analogue Negative Reference                 |  |  |  |  |

| 4                                     | V <sub>SS</sub> I 1∟1    | i owei            | CMX608: Not used (connect to V <sub>SS</sub> )             |  |  |  |  |

| 5                                     | INPUT P                  | Analogue          | CMX618/CMX638: Audio CODEC Positive Input (self biased)    |  |  |  |  |

| J                                     | INI OTT                  | Input             | CMX608: Not used (leave unconnected)                       |  |  |  |  |

| 6                                     | INPUT N                  | Analogue          | CMX618/CMX638: Audio CODEC Negative Input (self biased)    |  |  |  |  |

| 0                                     | 1101 01 10               | Input             | CMX608: Not used (leave unconnected)                       |  |  |  |  |

| 7                                     | 7 AV <sub>DD</sub> Power |                   | CMX618/CMX638: Analogue Positive Power Supply 3.3V         |  |  |  |  |

| ,                                     | A V DD                   | 1 OWEI            | CMX608: Not used (connect to IOV <sub>DD</sub> )           |  |  |  |  |

| 8                                     | $AV_SS$                  | Power             | CMX618/CMX638: Analogue Negative Power Supply 0V           |  |  |  |  |

| 0                                     | AVSS                     | 1 OWEI            | CMX608: Not used (connect to V <sub>SS</sub> )             |  |  |  |  |

| 9                                     | $V_{\rm SS}$ PA          | Power             | CMX618/CMX638: Output Amplifier Negative Power Supply 0V   |  |  |  |  |

| 3                                     | VSSIA                    | 1 OWC1            | CMX608: Not used (connect to V <sub>SS</sub> )             |  |  |  |  |

| 10                                    | OUT P                    | Analogue          | CMX618/CMX638: Audio CODEC – Amplifier Positive Output     |  |  |  |  |

| 10                                    | 0011                     | Output            | CMX608: Not used (leave unconnected)                       |  |  |  |  |

| 11                                    | OUT N                    | Analogue          | CMX618/CMX638: Audio CODEC – Amplifier Negative Output     |  |  |  |  |

| 11                                    | 00110                    | Output            | CMX608: Not used (leave unconnected)                       |  |  |  |  |

| 12                                    | $V_{DD}PA$               | Power             | CMX618/CMX638: Output Amplifier Positive Power Supply 3.3V |  |  |  |  |

| 12                                    | V DDI A                  | i owei            | CMX608: Not used (connect to IOV <sub>DD</sub> )           |  |  |  |  |

| 13                                    | $V_{DD}$                 | Power             | Digital Positive Power Supply 1.8V                         |  |  |  |  |

| 14                                    | $IOV_{DD}$               | Power             | Digital I/O Positive Power Supply 3.3V                     |  |  |  |  |

| 15                                    | SDI                      | Digital Input     | SSP port serial data input                                 |  |  |  |  |

| 16                                    | SDO                      | Digital<br>Output | SSP port serial data output CODEC PORT                     |  |  |  |  |

| 17                                    | SCLK                     | Digital Input     | ut SSP port serial clock input                             |  |  |  |  |

| 18                                    | STRB                     | Digital Input     | out SSP port serial strobe input                           |  |  |  |  |

| CMX608/<br>CMX618/<br>CMX638<br>L4/Q3 | MX618/<br>CMX638 Signal |                                 | Description                                                                                                                                       |  |  |  |  |

|---------------------------------------|-------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No.                               | Name                    | Туре                            |                                                                                                                                                   |  |  |  |  |

| 19                                    | EEC                     | Digital<br>Output               | Enable external CODEC, controlled by the C-BUS                                                                                                    |  |  |  |  |

| 20                                    | REC                     | Digital<br>Output               | Reset external CODEC, controlled by the C-BUS                                                                                                     |  |  |  |  |

| 21                                    | NC                      |                                 | Reserved for future use. Do not connect to this pin.                                                                                              |  |  |  |  |

| 22                                    | V <sub>SS</sub>         | Power                           | Negative Power Supply 0V                                                                                                                          |  |  |  |  |

|                                       | NC                      |                                 | CMX608: Reserved for future use. Do not connect to this pin.                                                                                      |  |  |  |  |

| 23                                    | CSEL                    | Digital Input                   | CMX618/CMX638: CODEC Select (Internal if '1', External if '0') This pin must be connected to either IOV <sub>DD</sub> or V <sub>SS</sub> .        |  |  |  |  |

| 24                                    | IOV <sub>DD</sub>       | Power                           | Digital I/O Positive Power Supply 3.3V                                                                                                            |  |  |  |  |

| 25                                    | SYNC                    | Digital<br>Input/Output         | Synchronisation Input/Output. By default, this pin is an input and must be connected by the user to either IOV <sub>DD</sub> or V <sub>SS</sub> . |  |  |  |  |

| 26                                    | V <sub>SS</sub>         | Power                           | Negative Power Supply 0V                                                                                                                          |  |  |  |  |

| 27                                    | XTALin                  | Input                           | Crystal Input                                                                                                                                     |  |  |  |  |

| 28                                    | XTALout                 | Output                          | Crystal Output                                                                                                                                    |  |  |  |  |

| 29                                    | $IOV_{DD}$              | Power                           | Digital I/O Positive Power Supply 3.3V                                                                                                            |  |  |  |  |

| 30                                    | RESETN                  | Digital Input                   | General Reset (active low)                                                                                                                        |  |  |  |  |

| 31                                    | XTALSEL1                | Digital Input                   |                                                                                                                                                   |  |  |  |  |

| 32                                    | XTALSEL2                | Digital Input                   | These bits select the crystal/clock frequency, according to Table 1.                                                                              |  |  |  |  |

| 33                                    | XTALSEL3                | Digital Input                   | according to Table 1.                                                                                                                             |  |  |  |  |

| 34                                    | ENABXTAL                | Digital Input                   | Enable Crystal Oscillator/External Clock Input                                                                                                    |  |  |  |  |

| 35                                    | $IOV_{DD}$              | Power                           | Digital I/O Positive Power Supply 3.3V                                                                                                            |  |  |  |  |

| 36                                    | NC                      |                                 | Reserved for future use. Do not connect to this pin.                                                                                              |  |  |  |  |

| 37                                    | NC                      |                                 | Reserved for future use. Do not connect to this pin.                                                                                              |  |  |  |  |

| 38                                    | NC                      |                                 | Reserved for future use. Do not connect to this pin.                                                                                              |  |  |  |  |

| 39                                    | NC                      |                                 | Reserved for future use. Do not connect to this pin.                                                                                              |  |  |  |  |

| 40                                    | NC                      |                                 | Reserved for future use. Do not connect to this pin.                                                                                              |  |  |  |  |

| 41                                    | $V_{SS}$                | Power                           | Negative Power Supply 0V                                                                                                                          |  |  |  |  |

| 42                                    | CLK                     | Digital Input                   | C-BUS Serial Clock                                                                                                                                |  |  |  |  |

| 43                                    | CDATA                   | Digital Input                   | ut C-BUS Command Data                                                                                                                             |  |  |  |  |

| 44                                    | RDATA                   | Tri-state<br>Output             | C-BUS Reply Data                                                                                                                                  |  |  |  |  |

| 45                                    | CSN                     | Digital Input                   | C-BUS Chip Select (bar)                                                                                                                           |  |  |  |  |

| 46                                    | IRQN                    | Open Drain<br>Digital<br>Output | C-BUS Interrupt Request (bar)                                                                                                                     |  |  |  |  |

| CMX608/<br>CMX618/<br>CMX638<br>L4/Q3 | Signal                  |    | Description                                                                                                                                                 |  |  |

|---------------------------------------|-------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No.                               | Name Type               |    |                                                                                                                                                             |  |  |

| 47                                    | IOV <sub>DD</sub> Power |    | Digital I/O Positive Power Supply 3.3V                                                                                                                      |  |  |

| 48                                    | V <sub>DD</sub> Power   |    | Digital Positive Power Supply 1.8V                                                                                                                          |  |  |

| EXPOSED  METAL SUB NC  PAD            |                         | NC | On the Q3 package only, the central metal pad may be connected to Analogue Ground (Avss) or left unconnected.  No other electrical connection is permitted. |  |  |

## 4. External Components

Notes: 1. On CMX608/CMX618/CMX638 devices, the crystal selection pins (XTALSEL1, XTALSEL2 and XTALSEL3) must be permanently tied to either IOVDD or Vss and not driven from a logic level output of the host μController (see Table 1 for a list of crystal frequencies). For 9.6MHz and 12.0MHz operation, either a crystal or a clock can be used. For all other frequencies, a clock must be injected into the XTALIN pin and the XTALOUT pin must be left unconnected.

- 2. To use the CMX608/CMX618/CMX638, tie the ENABXTAL pin to IOV<sub>DD</sub>. If the ENABXTAL pin is connected to Vss it will force the device into a deep powersave mode, where the C-BUS interface and clock input (XTALIN) are disabled and the crystal oscillator is powered down.

- 3. A single  $10\mu\text{F}$  electrolytic capacitor may be fitted in place of C5 and C11, providing the two  $V_{DD}$  pins are connected together on the pcb with an adequate width power supply trace.

Figure 2 CMX608 Recommended External Components

9

Figure 3 CMX618/CMX638 Recommended External Components

| Crystal Selec | t Input Pins: |          | Clock/Crystal |                      |  |

|---------------|---------------|----------|---------------|----------------------|--|

| XTALSEL3      | XTALSEL2      | XTALSEL1 | Frequency     | Clock/Crystal Choice |  |

| 0             | 0             | 1        | 9.6MHz        | crystal or clock     |  |

| 0             | 1             | 0        | 12.0MHz       | crystal or clock     |  |

| 0             | 1             | 1        | 14.4MHz       | external clock only  |  |

| 1             | 0             | 0        | 16.8MHz       | external clock only  |  |

| 1             | 0             | 1        | 19.2MHz       | external clock only  |  |

| 1             | 1             | 0        | 21.6MHz       | external clock only  |  |

| 1             | 1             | 1        | 24.0MHz       | external clock only  |  |

Table 1 Clock/Crystal Selection

## 4.1. PCB Layout Guidelines and Power Supply Decoupling

Figure 4 CMX618/CMX638 Power Supply and De-coupling

Component Values as per Figure 3.

#### Notes:

It is important to protect the analogue pins from extraneous inband noise and to minimise the impedance between the CMX618/CMX638 and the power supply and bias de-coupling capacitors. The de-coupling capacitors C4, C6, C7, C8, C9, C10, C12, C13 and C14 should be as close as possible to the CMX618/CMX638. It is therefore recommended that the printed circuit board is laid out with separate ground planes for the AV $_{\rm SS}$  and (digital) V $_{\rm SS}$  supplies in the area of the CMX618/CMX638, with provision to make links between them close to the CMX618/CMX638. The use of a multi-layer printed circuit board will facilitate the provision of ground planes on separate layers. The layout of a CMX608 printed circuit board should make use of a single ground plane covering the whole chip area shown above.

On CMX618/CMX638,  $V_{BIAS}$  is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled, to ensure its integrity, so apart from the decoupling capacitor shown, no other loads should be connected. If  $V_{BIAS}$  needs to be used to set an external midpoint reference, it must be buffered with a high input impedance buffer.

## 4.2. Audio CODEC External Components (CMX618/CMX638 only)

Figure 5 Recommended External Components - Differential CODEC Inputs

Figure 6 Recommended External Components – Single-ended CODEC Inputs

Note: Care should be taken to avoid shorting OUTP and OUTN together, or shorting either OUTP or OUTN to Vss or Vdd.

An external RC filter could be added across the OUTP and OUTN pins if clock noise needs further reduction.

| C9  | 470nF |

|-----|-------|

| C10 | 470nF |

| C11 | 1.0μF |

| C12 | 100μF |

| R3  | 1.0kΩ |

| R4  | 1.0kΩ |

Figure 7 Recommended External Components - CODEC Output

## 5. General Description

The CMX608/CMX618/CMX638 are a pin-compatible family of near toll quality voice encoders/decoders (Vocoders). The voice encoding/decoding is performed by a new, low data rate algorithm which is based on Robust Advanced Low Complexity Waveform Interpolation (RALCWI) technology. The data rate is selectable between 2400bps or 2750bps (all without FEC) or 3600bps (with FEC). The frame length is selectable from 20ms, 40ms, 60ms or 80ms (all without FEC) or from 60ms or 80ms (with FEC). The integral Viterbi FEC decoder can optionally use "soft decision" metrics to improve its decoding ability if the signal can be applied in a 4-bit digital representation of the received/demodulated analogue signal. The FEC can also be used on its own, so that data can be decoded/error-corrected then re-encoded and forwarded on. This allows use in a digital voice repeater.

RALCWI technology uses unique proprietary signal decomposition and parameter encoding methods, ensuring high voice quality at high compression ratios. The voice quality of RALCWI-class Vocoders, as estimated by independent listeners, is similar to that provided by standard Vocoders running at bit rates above 4000 bps. The Mean Opinion Score (MOS) of voice quality for this Vocoder is about 3.5-3.6. This value was determined by a paired comparison method, performing listening tests of developed and standard voice Vocoders.

The RALCWI Vocoder operates on a "frame-by-frame" basis. The 20ms source voice frame consists of 160 samples of linear 16-bit PCM sampled at 8kHz. The Voice Encoder performs voice analysis at the high time resolution (8 times per frame) and forms a set of estimated parameters for each voice segment. All of the estimated parameters are quantized to produce 48- or 55-bit frames, using Vector Quantization (VQ) of different types. All of the vector quantizers were trained on a mixed multi-language voice base, which contains voice samples in both Eastern and Western languages.

Voice parameters are coded by the Voice Encoder with high efficiency. Sensitivity to errors is estimated for each output bit and a bit frame is split into two parts: "more sensitive to errors" and "less sensitive to errors". To protect the voice parameters against channel errors without reducing voice quality, the "more sensitive" bits are protected. Such protection is provided by the FEC Encoder/Decoder mechanism. The Voice Decoder de-guantizes the parameters and re-synthesizes the voice.

Control of the CMX608/CMX618/CMX638 is over a C-BUS serial port from the host  $\mu$ C. On the CMX618/CMX638 only, the CSEL pin allows the selection of an internal or external CODEC, by connecting the CSEL pin to either IOV<sub>DD</sub> or V<sub>SS</sub> respectively. If the internal CODEC is selected, the SDI, STRB and SCLK pins should be connected to Vss. Synchronisation to the host  $\mu$ C is by use of either the (rising-edge active) SYNC input or by writing to the SYNC register (\$02). All major data paths are buffered in each direction with FIFO registers. The SSP port, which is used for the external ADC serial input and DAC serial output, is buffered in this way, as is the data to and from the CODEC (CMX618/CMX638 only) and also the vocoded data which is streamed into and out of the C-BUS interface. The management of these FIFOs is handled automatically and does not require any user intervention, other than the supply or consumption of data at the appropriate rate.

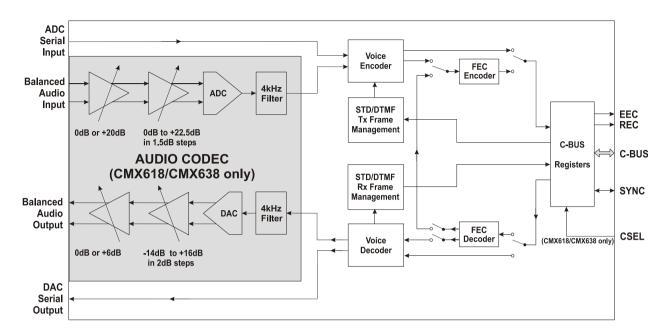

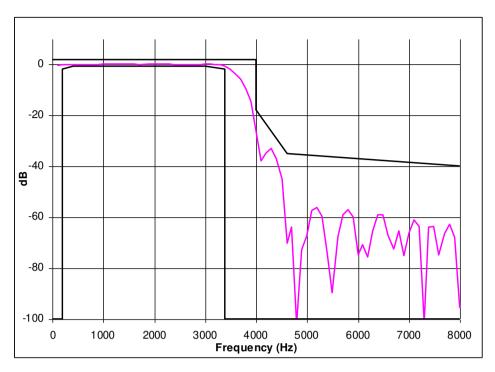

On the CMX618/CMX638 only, a voice CODEC is included, consisting of a microphone input to an ADC and a DAC with an earpiece output. A variable gain stage is associated with each converter. The differential input stage includes 20dB of switchable gain, for use as a microphone pre-amplifier. The input gain blocks are provided to allow for inputs from different microphone or other audio devices. At the very highest gain combinations, the input noise may start to be significant. In this case, users may wish to consider an external low-noise preamplifier prior to the differential input stage. For most applications this will not be necessary. The differential output stage includes 6dB of switchable gain. By using the output stage in a differential configuration, a further 6dB of gain can be achieved. Both input and output stages include a high-order digital channel filter, to constrain the input and output signals to an audio bandwidth of 4kHz. See Figure 20 and Figure 21 for further details. This avoids the necessity of adding external third (or higher) order filters, thus saving external components. A small number of external components, as shown in Figure 5, Figure 6 and Figure 7 is all that is required to implement the analogue interfaces to the CMX618/CMX638 voice CODEC.

The CMX608 (and the CMX618/CMX638, if the internal CODEC is not selected) provides a synchronous serial port (SSP), enabling a wide range of external CODECs to be used with this device. Two digital outputs, EEC and REC, can be used to enable and reset the external CODEC. They are controlled by bit 0 (EEC) and bit 1 (REC) of the EXCODECCONT register (\$0B). On the CMX618/CMX638 only, when the internal CODEC is selected, these pins are available as uncommitted digital outputs instead.

In CMX608/CMX618/CMX638, DTMF and single tones (STD) can be sent and received reliably over a noisy channel by using the special control codes, see section 5.7. Both devices feature a DTX (Discontinuous Transmission) mode, where an integral Voice Activity Detector in the encoder will send SID (Silence Insertion Description) data to the decoder, which will perform Comfort Noise Generation.

The CMX608 and CMX618 devices can operate in a mode that reduces the current consumption when the device is not actively being used, at the expense of a small reduction in maximum C-BUS SCLK frequency and an increase in the difference between the peaks and troughs of current consumption when running.

This mode is known as 'clock-throttling', where the vocoder's internal clock rate is automatically set to a quarter of its normal value when the device is waiting for samples or packets, i.e. not actively engaged in encoding or decoding. Clock throttling is not available on the CMX638.

This mode is enabled by setting bit 4 of the POWERSAVE register (\$09) to '1' after the device has been reset. The typical overall current consumption with "clock throttling" enabled can be calculated from the following figures:

```

(3.3V) I_{DD} Total = I_{DD} IODigital + I_{DD} Analogue + I_{DD} Analogue PA = 7.8 mA when encoding (3.3V) I_{DD} Total = I_{DD} IODigital + I_{DD} Analogue + I_{DD} Analogue PA = 4.1 mA when decoding. (1.8V) I_{DD} Total = I_{DD} Digital = 33.0 mA when encoding and = 20.0 mA when decoding

```

For the CMX638, clock throttling is not possible, so the typical Full-duplex current consumption figures are:

```

(3.3V) I_{DD} Total = I_{DD} IODigital + I_{DD} Analogue + I_{DD} Analogue PA = 11.3 mA (1.8V) I_{DD} Total = I_{DD} Digital = 49.0 mA

```

#### 5.1. Initialisation

On first applying power, three actions have to be performed: the crystal oscillator has to start up (if used), the bias chain has to be powered up (CMX618/CMX638 only), so that the decoupling capacitor (C14) has charged to  $AV_{DD}$  / 2, and on-chip digital circuits have to be reset into a known state. The crystal oscillator typically takes much less than 20ms to start up, but the actual time will depend on the ESR of the crystal used. With the components shown in Figure 3, the BIAS pin will take 100ms typically to reach its steady-state value of  $AV_{DD}$  / 2. There are two sources of reset:

- o pulling the RESETN signal (pin 30) to '0' for at least 200ns, then returning it to '1' (the pin does not have an internal pullup resistor). Note that the device does not have an automatic power-up reset.

- o writing to the C-BUS RESET register (\$01). This is a 1-byte command which has no data.

A hard reset (taking RESETN low) will also force the ENABXTAL signal low, which disables the clock and powersaves the crystal oscillator. On first applying power, the RESETN pin should be held low until all the power supplies have stabilised, to ensure correct operation of the device. When coming out of a hard reset, the device needs the crystal oscillator to be working, then counts 65,536 clock cycles (= 5.4ms delay with a 12.0MHz clock), then automatically performs a soft reset by writing to the C-BUS RESET register.

A soft reset (writing to the RESET register) will clear all registers to '0', unless noted otherwise – in which case the default settings are restored. The device will be ready to accept C-BUS commands approximately 1.5ms after completion of the soft reset action and will indicate that it is ready by setting bit 15 of the STATUS register (\$40) to '1' and also by indicating a C-BUS interrupt request by pulling the IRQN pin low. Note that on reset, the IRQENAB register (\$1F) bit 15 will automatically be set to '1', thus enabling the RDY interrupt to activate the IRQN pin. Refer also to section 6.1 for a description of the start-up sequence.

Connecting the ENABXTAL pin to Vss when the device is operational will force the device into a power-save mode where the C-BUS interface and clock input (XTALIN) are disabled and the crystal oscillator is powered down. However, the BIAS pin and C-BUS registers are not disturbed, so normal operation can be resumed by re-connecting the ENABXTAL pin to IOV<sub>DD</sub> and waiting for the crystal oscillator to re-start.

#### 5.2. Encoder

The encoder deals with a basic frame size of 20ms, 160 samples, of audio. 1, 2, 3, or 4 frames may be collected together and supplied to the host as a single packet. In the case of the 3 and 4 frame packets, error protection may also be added with the FEC option. The encoder can also detect single tones (STD) and/or DTMF in the audio stream. If detected, special frames are produced which the decoder will recognise and deal with accordingly.

The exact rate at which packets are produced is dependant on the accuracy of the CODEC's sample rate. The nominal rate is every 20ms, or a multiple thereof, depending on the number of frames that make up the packet. For instance, a packet of 3 frames with FEC will be produced every 60ms. The algorithm used to encode voice has algorithmic jitter, i.e. it does not take the same amount of time to encode each frame. Some frames will take longer than others, consequently, the exact time that a packet will be available is not predictable. The encoder will notify the host as soon as a packet becomes available. Over a period of time the average rate will be every 20ms (or a multiple thereof) according to the CODEC's sample rate.

Once a packet of data becomes available, the host may read it straight away, or it can wait for a period of time. The packet will remain available until the next one is produced.

## 5.2.1. Single Frame Packet, without FEC, STD or DTMF

This is the simplest and most basic configuration. The encoder will produce a one-frame raw Vocoder packet every 20ms. Once the encode instruction is given, the device will collect 20ms (160 samples) worth of audio. These 160 samples will be given to the encoder to process. The processing of these samples will take no more than 15ms, therefore the first packet of data will be available no later than 35ms after the device was instructed to encode.

There are two basic strategies that can be adopted for servicing the encoder:

#### Event-driven

The host may use the C-BUS interrupt, IRQN, or poll the STATUS register, then read the Vocoder packet as soon as it becomes available. This is signified by bit 0 (VDA) of the STATUS register being set to '1'. The host may then choose to hold the packet in a buffer until the correct time to process it arrives. In the case of a voice recorder, the packet could be put into a storage device immediately. In the case of some sort of transmission (radio or network), the packet may be held until the correct time-slot arrives.

### Timed

Assuming the host has an accurate 20ms timer derived from the same master clock as that supplied to the audio CODEC (this could be the Vocoder device, or an external CODEC), wait for a timer event and then instruct the device to encode. Wait for two more timer events, then read the first Vocoder packet. For every subsequent timer event, read another Vocoder packet. Figure 8 shows the sequence of events.

Figure 8 Single Frame Packet Encoding

This timed method may also be used where the host clock and CODEC clock are unrelated, in which case the host must supply a synchronising signal. Further details of slip management are given in section 6.5.

#### 5.2.2. Multiple Frame Packet with FEC, but without STD or DTMF

This is the most suitable configuration for use in a wireless system where the channel is prone to bit errors. Two modes are available:

- 3 frame packet, which represents 60ms of voice. This mode is most suitable for TDMA/DMR.

- 4 frame packet, which represents 80ms of voice. This mode is most suitable for FDMA/DMR.

Figure 9 shows the 3 frame mode, but the principal applies equally to the 4 frame mode. There are two basic strategies that can be adopted for servicing the encoder:

#### Event-driven

This is exactly the same as for the single frame example. Bit 0 (VDA) in the STATUS (\$40) register will be set to '1' when an FEC protected frame becomes available. If interrupts are enabled then IRQN will also be pulled low.

#### Timed

It is assumed that the host has an accurate method of timing, as discussed in the single frame example. Instruct the device to encode. Wait for 80ms, then read the first Vocoder packet. Wait for 60ms before reading the next and subsequent packets.

Figure 9 Multiple Frame Packet Encoding

Figure 9 shows the sequence of events. Adding the FEC is shown twice, though it is only executed once. This is to show that it will start immediately after the 3<sup>rd</sup> vocoded frame is available - which depends on the algorithmic jitter for that frame.

In the case of 4 frame packets, the initial wait should be 100ms and the subsequent waits should be 80ms.

#### 5.3. Decoder

Like the encoder, the decoder deals with a basic frame size of 20ms, 160 samples, of audio. 1, 2, 3, or 4 frames may be collected together and supplied to the decoder as a single packet. In the case of the 3 and 4 frame packets, error protection may also be included with the FEC option. FEC protected packets may contain either soft bits or hard bits. A soft-bit packet is 4 times the size of a hard-bit packet, as each soft-bit is represented by a nibble. The decoder can also detect special STD and DTMF frames and reproduce these as tones in the audio stream.

The exact rate at which packets must be presented is dependant on the accuracy of the CODEC's sample rate. The nominal rate is every 20ms, or a multiple thereof, depending on the number of frames that make up the packet. For instance, a packet of 3 frames with FEC will be produced every 60ms. The algorithm used to decode the encoded voice has algorithmic jitter, i.e. it does not take the same amount of time to decode each frame. Some frames will take longer than others. An initial delay in sending samples to the CODEC, coupled with an output buffer, will ensure that the CODEC is not starved of samples. It is also possible for the decoder to indicate that a new packet should be presented for decoding, based upon the number of samples left in the output buffer.

## 5.3.1. Single Frame Packet, without FEC, STD or DTMF

This is the simplest and most basic configuration. The decoder will produce 20ms of audio for each single-frame raw Vocoder packet.

Once the decode instruction is given, the device will wait for single-frame raw Vocoder packets to arrive every 20ms. Once the first packet is received, the initial decoder delay timer will be started, the frame will be decoded into 20ms of audio samples and the resulting samples placed in the output buffer. After the samples have been placed in this buffer, the device will wait for the initial decoder delay (IDD) timer to expire before sending the first sample to the CODEC. After this initial delay, further samples are given to the CODEC at its sample rate. The initial delay is set to be greater than the maximum time it takes to decode a frame. This ensures that the CODEC will not be starved of samples if the subsequent frame takes longer to decode than the first frame. The default initial decoder delay is set to 64 samples (8ms), which is more than sufficient to cover the internal algorithmic jitter. If the host, either through its internal scheduling or as a result of any algorithmic jitter in any processing that has to occur (e.g. demodulation), cannot supply the packets at exactly the right time (even though the average interval is correct), this initial delay should be increased to cover the additional jitter. The IDD (\$0C) register has been provided in order to facilitate the adjustment of this delay.

The CMX608 and CMX618 can be configured to set the STATUS (\$40) register bit 8 (VDW *Vocoder Data Wanted*) to '1' whenever there are fewer than a certain number of samples left in the output buffer. This is controlled by the low and high watermarks, which are set by using the VDWHLWM (\$1E) register. When the number of samples left in the output buffer is less than or equal to the low watermark, VDW will be set to '1' (and a C-BUS interrupt will occur, if enabled). Once indicated, the VDW bit cannot be set again until the output buffer has had at least 'high watermark' samples in it. This hysteresis prevents constant indication or interrupts when the number of samples in the buffer is still less than the low watermark.

There are three basic strategies that can be adopted for driving the decoder:

#### Event driven / Method 1

The host may use the C-BUS interrupt, IRQN, or poll the STATUS register, then supply a Vocoder packet as soon as the VDW bit is set. For this method the low and high watermarks must be set to suitable values. As an example, given that the decoder algorithm will take no more than 8ms to process a frame, and that the host can respond to the STATUS register having its VDW bit set within 1 ms, the low watermark should be set for a time period of 9ms, where 9ms at 8000 samples per second equates to a period of 72 samples. The high watermark should be set to a few samples less than 160. This value is not critical, providing it is greater than the low watermark.

The host should send the first packet to the device, after which it should wait, either by polling or by making use of the C-BUS interrupt, for the VDW bit to be set to '1'. Once this bit is set, the next packet should be sent to the device. The process should be repeated for as long as there are packets to decode. This method is an ideal choice for a voice record/playback system.

## Event driven / Method 2

The device can be set up to produce a short pulse every 20ms on the SYNC pin (pin 25). This pulse can be used to signal an interrupt to the controlling host, which can then cause a packet of data to be sent to the Vocoder. The 20ms period is directly related to the sample rate of the internal CODEC. This will only work for a CMX618/CMX638 set up for using its internal CODEC. For the CMX608, or the

CMX618/CMX638 in external CODEC mode, the SYNC output is not available, so another method needs to be employed, e.g using a modulo 160 counter clocked by the CODEC frame sync.

#### Timed

It is assumed that the host has an accurate 20ms timer, derived from the master clock of the system, which may or may not be synchronous with the audio CODEC. Wait for a timer event, instruct the device to decode, and then supply a packet for decoding. For every subsequent timer event, supply another packet for decoding. This is essentially the same as the event driven / method 2 above, the difference being that if the timer is not synchronous with the CODEC then the device's slip management feature will have to be employed. Further details of slip management are given in section 6.5.

The following diagrams show various aspects of the timed delivery of single-frame raw Vocoder packets for decoding.

Figure 10 Single Frame Packet Decoding

Figure 10 shows the sequence of events including the initial decoder delay, which compensates for the decoder's algorithmic jitter.

Figure 11 Single Frame Packet Decoding with Host Jitter

Figure 11 shows the effect of 4ms of host jitter with a default value of 8ms for the initial decoder delay. After the second batch of samples there is a gap, where the worst case of early delivery followed by late delivery has caused the CODEC to be starved of samples. To avoid this situation, the IDD has to be increased.

Figure 12 Single Frame Packet Decoding with Host Jitter (Increased IDD)

Figure 12 is the same as the previous figure, but with an increased initial decoder delay. As can be seen, the CODEC is no longer starved of samples.

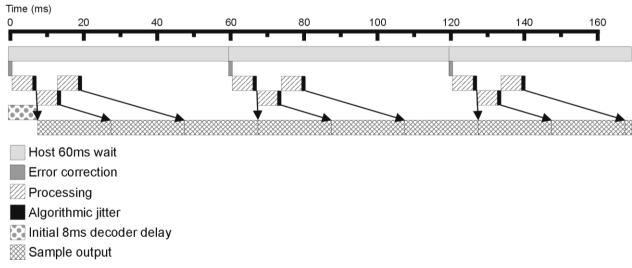

#### 5.3.2. Multiple Frame Packet with FEC, but without STD or DTMF

This is the most suitable configuration for use in a wireless system, where the channel is prone to bit errors. Two modes are available:

- 3 frame packet, which represents 60ms of voice. This mode is most suitable for TDMA/DMR.

- 4 frame packet, which represents 80ms of voice. This mode is most suitable for FDMA/DMR.

For each of these modes, the packets may contain either hard-bits or soft-bits.

Figure 13 shows a timed delivery method for the 3 frame mode, although the principal applies equally to the 4 frame mode. As in the above examples, if the host has some algorithmic jitter (which affects the exact time of packet delivery), then the IDD register should be used to increase the initial decoder delay.

Figure 13 Multiple Frame Packet Decoding

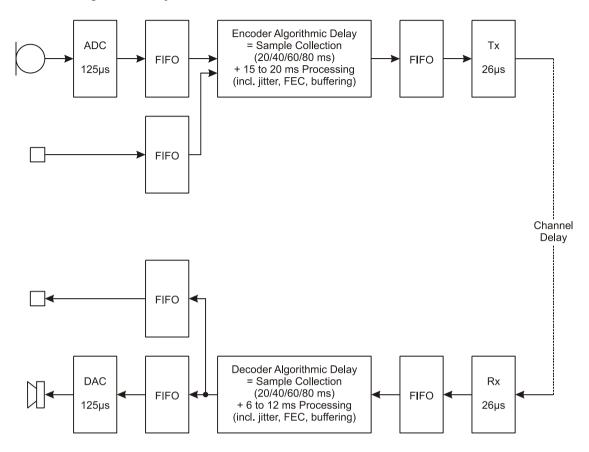

## 5.4. Overall Signal Latency

Figure 14 Overall Signal Latency

The overall latency of a signal through an encoder/decoder pair is shown diagrammatically in Figure 14.

## 5.5. Vocoder Data Format and Bit Order

Packets of both raw and FEC protected Vocoder data are transferred between the device and the host microprocessor over the byte-wide streaming C-BUS registers. The following sections describe how the data is organised for the various configurations.

## 5.5.1. Packets of Raw Vocoder Frames

The device can produce encoded voice at two different bit rates: 2400bps and 2750bps. The higher the bit rate, the more bits per 20ms are produced. These bits are packed into bytes for transfer over the C-BUS. For each bit rate, some of the bits produced are more sensitive to corruption and some are less sensitive. For applications where the in-built FEC protection is not going to be used, perhaps because the user already has an existing FEC system, the bits should be encapsulated in such a way that those which are more sensitive to corruption have the greatest protection. The bits in a frame are named B0, B1, B2 ... etc.

#### 2400bps

A 20ms Vocoder frame consists of 48 bits. 24 bits are more sensitive and 24 bits are less sensitive. A single frame is transferred between the device and the host as 6 bytes. The table below shows the bit positions in the transferred bytes. The more sensitive bits are shown white on black. The byte at the top is the first out of the C-BUS for the encoder and the first into the C-BUS for the decoder.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

| B15 | B14 | B13 | B12 | B11 | B10 | B9  | B8  |

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 |

| B31 | B30 | B29 | B28 | B27 | B26 | B25 | B24 |

| B39 | B38 | B37 | B36 | B35 | B34 | B33 | B32 |

| B47 | B46 | B45 | B44 | B43 | B42 | B41 | B40 |

There are no un-used bits in the packet. For multiple frame packets, each frame is 6 bytes and is read or written to the C-BUS in chronological order.

#### 2750bps

A 20ms Vocoder frame consists of 55 bits. 23 bits are more sensitive and 32 bits are less sensitive. A single frame is transferred between the device and the host as 7 bytes. The table below shows the bit positions in the transferred bytes. The more sensitive bits are shown white on black. The byte at the top is the first out of the C-BUS for the encoder and the first into the C-BUS for the decoder.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

| B15 | B14 | B13 | B12 | B11 | B10 | B9  | B8  |

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 |

| B31 | B30 | B29 | B28 | B27 | B26 | B25 | B24 |

| B39 | B38 | B37 | B36 | B35 | B34 | B33 | B32 |

| B47 | B46 | B45 | B44 | B43 | B42 | B41 | B40 |

| х   | B54 | B53 | B52 | B51 | B50 | B49 | B48 |

The most significant bit of the last byte is un-used. Its value is indeterminate. For multiple frame packets, each frame is 7 bytes (with 1 unused bit in the last byte) and is read or written to the C-BUS in chronological order.

#### 5.5.2. Packets of FEC Protected Frames

The device has a built-in FEC system to protect the Vocoder frames when transported over an error prone channel. The data interleaving has been organised to provide good performance over a channel with burst errors, typical in wireless applications. Only the bits that are more sensitive to corruption are protected

FEC can be applied over 3 or 4 frames resulting in a packet of 216 or 288 bits, regardless of the Vocoder bit rate. The bits in the packet are named D0 through D215 (or D287). The bits should be transmitted in order, starting with D0 and ending with D215 (or D287).

#### Hard-bits

Hard bits are represented by one bit per bit. These are packed into 27 bytes for 3-frame FEC and 36 bytes for 4-frame FEC. The following table shows how these bits are packed and transferred between the Vocoder and the host microprocessor. The byte at the top is the first out of the C-BUS for the encoder and the first into the C-BUS for the decoder.

| 7          | 6             | 5           | 4          | 3           | 2    | 1    | 0    |

|------------|---------------|-------------|------------|-------------|------|------|------|

| D0         | D1            | D2          | D3         | D4          | D5   | D6   | D7   |

| D8         | D9            | D10         | D11        | D12         | D13  | D14  | D15  |

| Intervenir | ng bits follo | ow the san  | ne pattern |             |      |      |      |

| D200       | D201          | D202        | D203       | D204        | D205 | D206 | D207 |

| D208       | D209          | D210        | D211       | D212        | D213 | D214 | D215 |

| For 4 fran | ne packet     | s, the sequ | uence con  | tinues thus | S    |      |      |

| D272       | D273          | D274        | D275       | D276        | D277 | D278 | D279 |

| D280       | D281          | D282        | D283       | D284        | D285 | D286 | D287 |

#### Soft-bits

Soft bits are represented by one nibble per bit. These should be packed into 108 bytes for a 3-frame FEC and 144 bytes for a 4-frame FEC. The following table shows how these bits should be packed and sent to the decoder over the C-BUS. The byte at the top should be the first one sent. The bits of a nibble are shown as n3 to n0, with n3 being the most significant and n0 being the least significant.

| 7                                                | 6            | 5          | 4          | 3    | 2  | 1  | 0  |  |  |

|--------------------------------------------------|--------------|------------|------------|------|----|----|----|--|--|

| n3                                               | n2           | n1         | n0         | n3   | n2 | n1 | n0 |  |  |

| D0                                               |              |            |            | D1   |    |    |    |  |  |

| D2                                               |              |            |            | D3   |    |    |    |  |  |

| Intervenir                                       | ng bits foll | ow the sar | ne pattern |      |    |    |    |  |  |

| D212                                             |              |            |            | D213 |    |    |    |  |  |

| D214                                             |              |            |            | D215 |    |    |    |  |  |

| For 4 frame packets, the sequence continues thus |              |            |            |      |    |    |    |  |  |

| D284                                             |              |            |            | D285 |    |    |    |  |  |

| D286                                             |              |            |            | D287 |    |    |    |  |  |

#### TDMA/DMR

The TDMA/DMR specification names the Vocoder socket bits VS0 to VS215 and states that bit VS215 is transmitted first. When using the RALCWI Vocoder in conjunction with TDMA/DMR, bit VS215 should be assigned Vocoder bit D0 and bit VS0 should be assigned Vocoder bit D215, with the intervening bits assigned in sequential order.

| Vocoder socket bit assignments |       |       |   |      |      |      |  |  |  |

|--------------------------------|-------|-------|---|------|------|------|--|--|--|

| VS215                          | VS214 | VS213 | > | VS2  | VS1  | VS0  |  |  |  |

| D0                             | D1    | D2    | > | D213 | D214 | D215 |  |  |  |

#### FDMA/DMR (dPMR)

In dPMR, each of the four frames constituting a super-frame (the basic element of data transfer) has a capacity of 36 bytes, suitable for transmission of an 80msec FEC-encoded Vocoder data packet. The frame data bits are always transmitted byte by byte with the MSB first, starting with either the FrameSync2 pattern, or the Colour Code (dependant on the frame number), followed by the control channel data and the payload data. In a Voice super-frame, the Vocoder data bits should be transmitted D0 first to D287 last within the payload data section of each of the four frames.

#### 5.6. External CODEC Support

The CODEC supplies samples of audio for vocoding. On the CMX608, use of the CODEC port is mandatory, as there is no internal CODEC. On the CMX618/CMX638, use of the CODEC port is optional and the selection of internal or external CODEC is made automatically by examination of CSEL (pin 23). If it is pulled low during power-up or reset, an external CODEC will be selected. This selection can then only be changed by performing a reset operation.

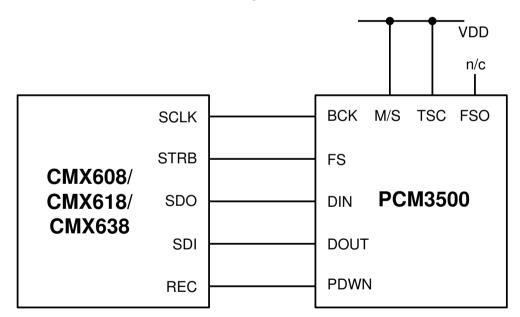

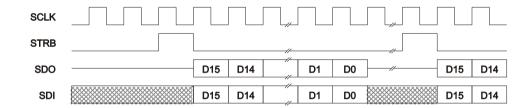

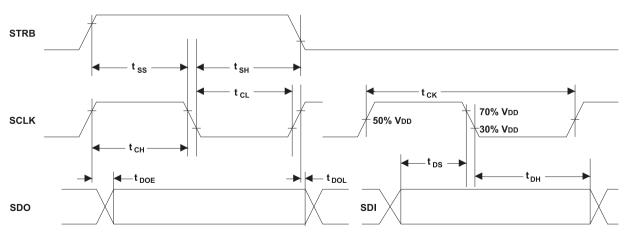

An external CODEC (such as the Burr Brown PCM3500) can be supported via the 4-wire CODEC interface known as the Synchronous Serial Port (SSP). The CMX608 SSP consists of the following signals: synchronising clock (SCLK, pin 17), start of frame indicator (STRB, pin 18), data-in (SDI, pin 15) and data-out (SDO, pin 16). Both data and control information are transferred in to and out of the CODEC/SSP port 16-bits at a time. The transfer of data is illustrated in Figure 19. Additionally the CODEC may have Enable and Reset pins that can be connected to the EEC (pin 19) and REC (pin 20) pins of the CMX608. The state of these outputs is controlled by writing to the EXCODECCONT register (\$0B). On power-up, or after a general reset, the state of these two control signals will be low.

The SSP interface is flexible enough to drive a wide range of CODEC devices meeting the following basic specifications:

- 8k samples per second, 16 bit, linear.

- The SCLK must run at a higher frequency than the bit rate (>128kHz). There must be at least one complete SCLK cycle between the last bit of a sample and the next start of frame.

- Meet the constraints of the CODEC (SSP) port timing diagram.

Two C-BUS registers are used for the control and set-up of external CODECs. The external CODEC control register (EXCODECCONT) is used for starting and stopping the SSP, defining the operating conditions and managing the command FIFO. The external CODEC command register (EXCODECCMD) enables up to 16 command words to be specified, which will be sent to a CODEC after the SSP is started. The CMX608/CMX618/CMX638 include pre-set configurations for a popular CODEC: the Burr-Brown (Texas Instruments) PCM3500, as well as for a general-purpose configuration.

#### PCM3500

This CODEC should be supplied with a 4096MHz clock, giving a sample rate of 8ksample/s. The connections for this device are shown below and in Figure 15:

| PCM | 3500  |                            | CMX608/CM | X618/CMX638 |

|-----|-------|----------------------------|-----------|-------------|

| Pin | Name  |                            | Pin       | Name        |

| 1   | Vcom  | Follow data sheet          |           |             |

| 2   | Vref1 | Follow data sheet          |           |             |

| 3   | Vref2 | Follow data sheet          |           |             |

| 4   | Vin   | Follow data sheet          |           |             |

| 5   | AGND  | Follow data sheet          |           |             |

| 6   | M/S   | Pull high - Master mode    |           |             |

| 7   | TSC   | Pull high - Time slot mode |           |             |

| 8   | BCK   | Connect to                 | 17        | SCLK        |

| 9   | FS    | Connect to                 | 18        | STRB        |

| 10  | DIN   | Connect to                 | 16        | SDO         |

| 11  | DOUT  | Connect to                 | 15        | SDI         |

| 12  | FSO   | Leave Unconnected          |           |             |

| 13  | Vdd   | Follow data sheet          |           |             |

| 14  | DGND  | Follow data sheet          |           |             |

| 15  | SCKIO | Follow data sheet          |           |             |

| 16  | XTO   | Follow data sheet          |           |             |

| 17  | XTI   | Follow data sheet          |           |             |

| 18  | HPFD  | Follow data sheet          |           |             |

| 19  | LOOP  | Follow data sheet          |           |             |

| 20  | PDWN  | Connect to                 | 20        | REC         |

| 21  | AGND  | Follow data sheet          |           |             |

| 22  | Vout  | Follow data sheet          |           |             |

| 23  | AGND  | Follow data sheet          |           |             |

| 24  | Vcc   | Follow data sheet          |           |             |

The PCM3500 is started using the following sequence of instructions:

- Select the external CODEC type PCM3500.

- Write \$45 (CODEC\_PCM3500) into the EXCODECCONT register (\$0B) and then wait for the RDY bit to be set in the STATUS register (\$40). If C-BUS interrupts are enabled for the RDY bit, then IRQN will go low as well this applies to the rest of the sequence.

- Ensure that the CODEC is in its power-save/reset mode, the CODEC port (SSP) is disabled and the CODEC command FIFO is empty.

Write \$86 (ECC\_CODEC\_RESET) into the EXCODECCONT register and then wait for the RDY bit to be set in the STATUS register.

Write \$82 (ECC\_SSP\_STOP) into the EXCODECCONT register and then wait for the RDY bit to be set in the STATUS register.

Write \$83 (ECC\_FIFO\_CLEAR) into the EXCODECCONT register and then wait for the RDY bit to be set in the STATUS register.

Start the CODEC port.

Write \$81 (ECC\_SSP\_START) into the EXCODECCONT register and then wait for the RDY bit to be set in the STATUS register.

Bring the CODEC out of power-save/reset

Write \$87 (ECC\_CODEC\_START) into the EXCODECCONT register and then wait for the RDY bit to be set in the STATUS register.

To stop the device, for power saving, the following sequence should be used:

Place the device into power-save.

Write \$88 (ECC\_CODEC\_PSAVE) into the EXCODECCONT register (\$0B) and then wait for the RDY bit to be set in the STATUS register (\$40)

To restart the device after power saving:

Restart the CODEC port.

Write \$87 (ECC\_CODEC\_START) into the EXCODECCONT register and then wait for the RDY bit to be set in the STATUS register.

Figure 15 PCM3500 Interface

#### Supporting other CODECs

CODECs other than the two detailed above can be used with this device, providing they meet the basic capabilities mentioned above.

There are three facts that must be established in order to successfully use a CODEC:

Is the data sampled on the positive or the negative edge of the SCLK?

If the data is sampled on the positive edge of SCLK, choose either CODEC\_GENERIC1 or CODEC\_GENERIC2 as the CODEC type. If the data is sampled on the negative edge of SCLK, then choose either CODEC\_GENERIC3 or CODEC\_GENERIC4 as the CODEC type.

Does the CODEC output 16 or more SCLKs before a frame sync?

If the CODEC outputs less than 16 SCLKs before the first frame sync, choose CODEC\_GENERIC2 or CODEC\_GENERIC4 as the CODEC type. If the CODEC outputs 16 SCLKs or more before the first frame sync, then choose CODEC\_GENERIC1 or CODEC\_GENERIC3 as the CODEC type.

The CODEC type to use is the choice that is common to both of the above.

Does the CODEC require data to be sent to it for configuration?

If the CODEC requires configuration words to be sent to it to set it up, these should be loaded into the CODEC command FIFO.

Hardware control of the CODEC can be done by using the EEC and REC output pins. Either use the direct control commands REC/EEC (0,1,2,3) or use the individual control commands ECC\_???\_LOW/ECC\_???\_HIGH (\$89-\$8C). Using the generic CODEC settings means that the ECC\_CODEC\_RESET/ECC\_CODEC\_START/ECC\_CODEC\_PSAVE commands do nothing and therefore should not be used.

## 5.7. Operation with DTMF (Dual Tone Multi-Frequency)

The CMX608, CMX618 and CMX638 (in half-duplex mode only) can be enabled to send or receive DTMF. This facility is not available when the CMX638 is used in full-duplex mode.

#### 5.7.1. DTMF Transmit

When the device is transmitting voice data (encoding), special DTMF data frames can replace the voice data frames. The DTMF data frames can be generated by one of two modes:

- Mode 1 DTMF (Tones) are detected and decoded to a 4-bit number. This 4-bit number is sent in the special DTMF data frames. In this mode, DTMF transmission is automated, i.e. if DTMF is detected then the DTMF data frame is sent, otherwise the voice data frames are sent. This mode is enabled by bit 11 (EDTMFD) in the VCTRL register (\$11).

- Mode 2 DTMF (Data) is entered directly as a 4-bit number in bits 0 to 3 of the SDTMF register (\$08). This 4-bit number is sent in the special DTMF data frames. In this mode, the duration of the DTMF data frames is specified (in terms of the number of frames) in bits 4 to 7 of the SDTMF register. Setting the duration to \$0 disables this feature. Setting the duration to \$F enables continuous DTMF.

If both modes are enabled then Mode 2 will take precedence.

## 5.7.2. DTMF Receive

When the device is receiving voice data (decoding), special DTMF data frames may replace the voice data frames. If DTMF is enabled in receive then DTMF data frames are automatically detected and can be used in one of two modes:

Mode 1 The DTMF 4-bit number is detected from the DTMF data frame. The 4-bit code is made available in the DFRAMEDATA register (\$37) and is also re-synthesized as a tone at the output. This mode is enabled by setting bits 5 and 6 in the VCTRL register (\$11) to '1'.

Mode 2 The DTMF 4-bit number is detected from the DTMF data frame. The 4-bit code is made available in the DFRAMEDATA register (\$37) and silence is output from the Codec. This mode is enabled by setting bit 5 in the VCTRL register (\$11) to '1' and by setting bit 6 in the VCTRL register to '0'.

The DTMF generators and detectors are provided so that commonly encountered tones can be reproduced naturally at the other end of a Vocoded link, rather than being interpreted as a form of speech. They should not be relied upon to provide an error free method of relaying tone signalling to other decoders, such as a telephone exchange DTMF detector, for example.

#### 5.7.3. DTMF Format

The DTMF format is selected by bit 7 in the (Vocoder Configuration) VCFG register (\$07), according to the following tables:

Format 1 This format is used when bit 7 of the VCFG register (\$07) is cleared to '0'.

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Symbol |

|-------|-------|-------|-------|--------|

| 0     | 0     | 0     | 0     | D      |

| 0     | 0     | 0     | 1     | 1      |

| 0     | 0     | 1     | 0     | 2      |

| 0     | 0     | 1     | 1     | 3      |

| 0     | 1     | 0     | 0     | 4      |

| 0     | 1     | 0     | 1     | 5      |

| 0     | 1     | 1     | 0     | 6      |

| 0     | 1     | 1     | 1     | 7      |

| 1     | 0     | 0     | 0     | 8      |

| 1     | 0     | 0     | 1     | 9      |

| 1     | 0     | 1     | 0     | 0      |

| 1     | 0     | 1     | 1     | *      |

| 1     | 1     | 0     | 0     | #      |

| 1     | 1     | 0     | 1     | Α      |

| 1     | 1     | 1     | 0     | В      |

| 1     | 1     | 1     | 1     | С      |

Table 2 DTMF - Format 1

**Format 2** This format corresponds with the row and column layout of a standard telephone keypad matrix. This format is used when bit 7 of the VCFG register (\$07) is set to '1'.

|                         | 1209Hz | 1336Hz | 1477Hz | 1633Hz | Row Index<br>Bit 3:2 |

|-------------------------|--------|--------|--------|--------|----------------------|

| 697Hz                   | 1      | 2      | 3      | Α      | 0                    |

| 770Hz                   | 4      | 5      | 6      | В      | 1                    |

| 852Hz                   | 7      | 8      | 9      | С      | 2                    |

| 941Hz                   | *      | 0      | #      | D      | 3                    |

| Column Index<br>Bit 1:0 | 0      | 1      | 2      | 3      |                      |

Table 3 Standard DTMF Keypad Layout

This results in the following table in ascending numerical order for the bit patterns.

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Symbol |

|-------|-------|-------|-------|--------|

| 0     | 0     | 0     | 0     | 1      |

| 0     | 0     | 0     | 1     | 2      |

| 0     | 0     | 1     | 0     | 3      |

| 0     | 0     | 1     | 1     | Α      |

| 0     | 1     | 0     | 0     | 4      |

| 0     | 1     | 0     | 1     | 5      |

| 0     | 1     | 1     | 0     | 6      |

| 0     | 1     | 1     | 1     | В      |

| 1     | 0     | 0     | 0     | 7      |

| 1     | 0     | 0     | 1     | 8      |

| 1     | 0     | 1     | 0     | 9      |

| 1     | 0     | 1     | 1     | С      |

| 1     | 1     | 0     | 0     | *      |

| 1     | 1     | 0     | 1     | 0      |

| 1     | 1     | 1     | 0     | #      |

| 1     | 1     | 1     | 1     | D      |

Table 4 DTMF - Format 2

## 5.8. Operation with STD (Single Tones)

The CMX608, CMX618 and CMX638 (in half-duplex mode only) can be enabled to send or receive single tones. This facility is not available when the CMX638 is used in full-duplex mode.

The STD generators and detectors are provided so that commonly encountered tones can be reproduced naturally at the other end of a Vocoded link, rather than being interpreted as a form of speech. They should not be relied upon to provide an error free method of relaying tone signalling to other decoders.

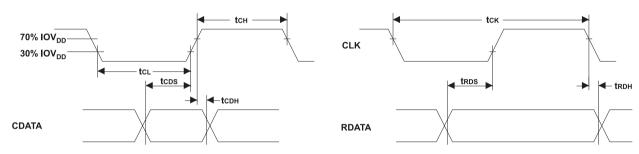

#### 5.9. C-BUS Interface

This block provides for the transfer of data and control or status information between the internal registers of the CMX608/CMX618/CMX638 and the host  $\mu$ C, by using the C-BUS serial bus. Each transaction consists of a single Register Address byte sent from the  $\mu$ C, which may be followed by a data word sent from the  $\mu$ C (written into one of the Write-Only Registers), or a data word sent to the  $\mu$ C (read out from one of the Read-Only Registers). All C-BUS data words are a multiple of 8 bits wide, the width depending on the source or destination register. Note that certain C-BUS transactions require only an address byte to be sent from the  $\mu$ C, no data transfer being required. The operation of the C-BUS is illustrated in Figure 16.