# Isolated RS-485 Full-Duplex Evaluation Module

This user's guide describes the evaluation module (EVM) for a RS-485 Full-duplex transceiver. This EVM helps designers evaluate the device performance for fast development and analysis of data transmission systems using any of the TI RS-485 Full-duplex devices in a 16-pin DW package.

#### **CAUTION**

Do not use this EVM for isolation voltage tests even though the Full-duplex device has galvanic isolation of up to 4000 V. This EVM is designed for the evaluation of device operating parameters only. If a high voltage (greater than 5.5 V) is applied anywhere in the circuit, the EVM could be damaged.

#### **Contents**

| 1 | Introduction                                                  |

|---|---------------------------------------------------------------|

| 2 | Functional Configurations of the Isolated RS-485 Transceivers |

| 3 | Isolated RS-485 EVM Schematic and Layout                      |

| 4 | Bill of Materials                                             |

| 5 | EVM Setup and Operation                                       |

| 6 | References                                                    |

|   | List of Figures                                               |

| 1 | ISO1412 Functional Block Diagram                              |

| 2 | ISO1412 DW Package 16-Pin SOIC Pin Configuration              |

| 3 | Board Layout                                                  |

| 4 | Top-Layer View Full Duplex Isolated RS-485 EVM                |

| 5 | ISO1412DWEVM Schematic                                        |

| 6 | Basic EVM Setup and Jumper Configurations                     |

| 7 | Example scope capture at 100-kHz and VCC1,2 at 3.3 V          |

|   | List of Tables                                                |

| 1 | Bill of Materials                                             |

| 2 | Jumper configuration                                          |

#### **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

The ISO141x family of devices is an isolated differential line transceiver for TIA/EIA 485/422 applications. The devices with the B suffix are  $5\text{-kV}_{\text{RMS}}$ , basic isolated transceivers. The basic isolation devices can be used for long transmission lines because the ground loop is broken. The broken ground loop lets a much larger range of common-mode voltage be used in the design.

The symmetrical isolation barrier of the device is tested to give 5000  $V_{RMS}$  of isolation for 60 s per UL 1577 between the bus-line transceiver and the logic-level interface. Any cabled I/O can have electrical noise transients from various sources. These noise transients can cause damage to the transceiver, nearby sensitive circuitry, or both if the transients are of sufficient magnitude and duration. These isolated devices can significantly increase protection and decrease the risk of damage to expensive control circuits. The bus pins can endure high levels of IEC ESD and EFT events. No additional components for system-level protection are needed because of this endurance.

This EVM can evaluate different system parameters of the devices. Test signals and sequences can be applied to the device and different performance characteristics such as propagation delay, power consumption, and different bus and driver conditions. Users can evaluate these parameters in their own lab environment.

The EVM has footprints named *DNI* for additional components that are not needed to test the standard functionality. Add components to these footprints for evaluation and to get specific system requirements. Refer to this users guide for the basic functionality that can be assessed with the EVM.

Go to the isolated RS-485 transceiver page on TI.com for data sheets and a detailed description of the ISO141x devices. Review the TI E2E<sup>TM</sup> Online Community for digital isolators to find technical support for this EVM and other isolated devices. This EVM is designed with the signal paths for the Full-duplex operation.

## 2 Functional Configurations of the Isolated RS-485 Transceivers

#### 2.1 Device Pin Functions and Configurations

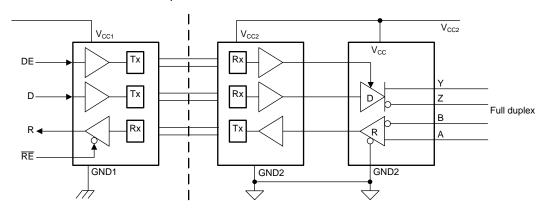

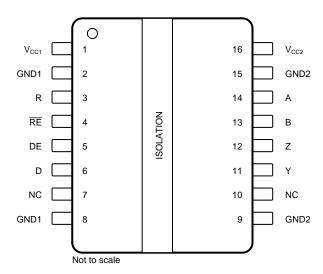

Figure 1 shows a functional diagram of an isolated Full-duplex RS485 transceiver. Figure 2 shows the pin configuration of the ISO1412 device in the DW package. The ISO1412DWEVM comes with the ISO1412DW device and all components installed for the basic tests.

Figure 1. ISO1412 Functional Block Diagram

Figure 2. ISO1412 DW Package 16-Pin SOIC Pin Configuration

## 3 Isolated RS-485 EVM Schematic and Layout

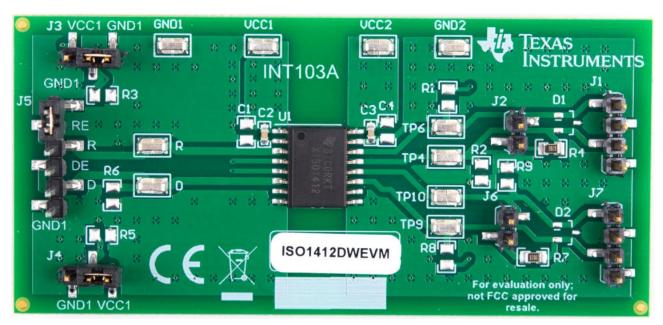

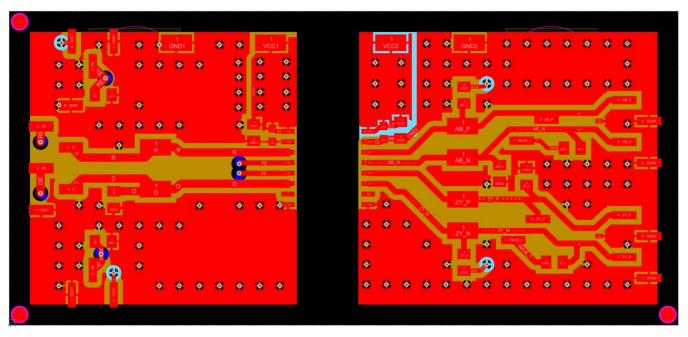

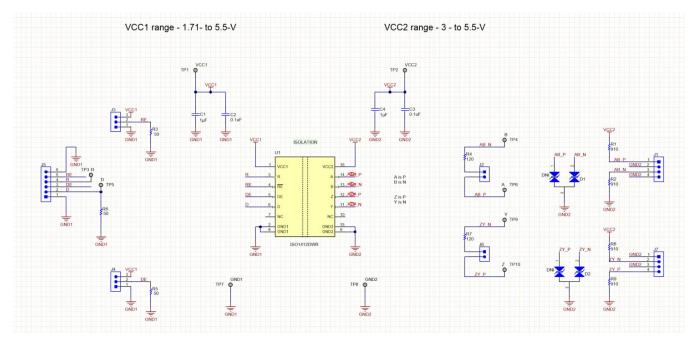

Figure 3 shows the board layout of the isolated full-duplex RS-485 EVM. Figure 4 shows the board layout of the full-duplex isolated RS-485 EVM. Figure 5 shows the schematic of the full-duplex isolated RS-485 EVM.

Figure 3. Board Layout

Figure 4. Top-Layer View Full Duplex Isolated RS-485 EVM

Figure 5. ISO1412DWEVM Schematic

www.ti.com Bill of Materials

#### 4 Bill of Materials

Table 1 shows the bill of materials for the EVM.

## Table 1. Bill of Materials

| Item | Quantity | Designator                                | Description                                                                                                                 | Manufacturer         | Part Number      |

|------|----------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|

| 1    | 2        | J1, J7                                    | Header, 2.54 mm, 4 x 1,<br>SMT                                                                                              | Wurth Elektronik     | 61000418221      |

| 2    | 2        | J2, J6                                    | Header, 2.54 mm, 2 x 1, SMT                                                                                                 | Wurth Elektronik     | 61000218321      |

| 3    | 2        | J3,J4                                     | Header, 2.54 mm, 3 x 1, SMT                                                                                                 | Wurth Elektronik     | 61000318221      |

| 4    | 1        | J5                                        | Header, 2.54 mm, 6 x 1,<br>SMT                                                                                              | Molex                | 87898-0657       |

| 5    | 2        | C2,C3                                     | CAP, CERM, 0.1 uF, 25 V,<br>+/- 5%, X7R, 0603                                                                               | AVX                  | 06033C104JAT2A   |

| 6    | 2        | C1, C4                                    | CAP, CERM, 1 uF, 25 V, +/-<br>10%, X7R, 0805                                                                                | Kemet                | C0805C105K3RACTU |

| 8    | 4        | R1,R2, R8, R9                             | RES, 910, 0.5%, 0.1 W, 0805                                                                                                 | Susumu Co Ltd        | RR1220P-911-D    |

| 9    | 3        | R3,R5,R6 <sup>(1)</sup>                   | RES, 49.9, 1%, 0.125 W,<br>AEC-Q200 Grade 0, 0805                                                                           | Vishay-Dale          | CRCW080549R9FKEA |

| 10   | 2        | R4, R7                                    | RES, 120, 1%, 0.4 W, 0805                                                                                                   | Rohm                 | ESR10EZPF1200    |

| 11   | 10       | A, B, Z, YD, GND1, GND2,<br>R, VCC1, VCC2 | Test Point, Miniature, SMT                                                                                                  | Keystone             | 5019             |

| 12   | 2        | D1, D2                                    | TVS Diode according to requirements                                                                                         | DNI                  | DNI              |

| 13   | 4        | H1, H2, H3, H4                            | Bumpon, Hemisphere, 0.44<br>X 0.20, Clear                                                                                   | ЗМ                   | SJ-5303 (CLEAR)  |

| 14   | 1        | U1                                        | 5-kV <sub>RMS</sub> Reinforced and<br>Basic Isolated RS-485/RS-<br>422 Transceiver With<br>Robust-EMC, DW0016B<br>(SOIC-16) | Texas<br>Instruments | ISO1412DW        |

The 50-Ω resistors R3, R5, and R6, have the index n.a., indicating that these components are not assembled. Because signal generators have a typical source impedance of 50 Ω, their output signal is twice the required signal voltage and assumes that the on board 50-Ω resistors divide this voltage down to the correct signal level. J3 and J4 can only be used when these resistors are not populated.

#### 5 EVM Setup and Operation

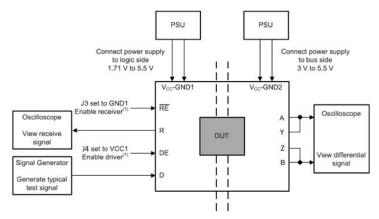

Figure 6 shows the basic setup of the EVM with two power supplies needed to evaluate isolator performance. Use voltages that are within the range given in the device data sheet. The typical voltages for the  $V_{\text{CC1}}$  and  $V_{\text{CC2}}$  supplies are 3.3 V and 5 V. Separate power supplies generate each supply voltage. The supply voltages do not need to have the same value. If both side are to be evaluated at the same supply voltage, only one power supply is required. This one power supply can power both sides of the EVM.

(1) Normal transceiver operation requires both the driver and the resections to be active. Set the enable pin (RE) to logic low and the driver enable pin (DE) to logic high.

Figure 6. Basic EVM Setup and Jumper Configurations

Table 2 shows the information on jumper configuration for basic tests.

Connection Label Description Connect this jumper to enable the 120- $\Omega$  termination resistor. Disconnect this jumper to J2 J2 disable the  $120-\dot{\Omega}$  termination resistor. The bus lines should be  $120-\Omega$  terminated (jumper connected) to assess full performance. Connect this jumper between the middle pin and GND1 to tie the  $\overline{\text{RE}}$  pin low. The receiver is enabled when the RE pin is low. Tie the RE pin to GND1 for full operation tests. J3 VCC1, GND1 Connect this jumper between the middle pin and VCC1 to tie the RE pin high. The receiver is disabled when the RE pin is high. Connect this jumper between the middle pin and GND1 to tie the DE pin low. The driver input is disabled when the DE pin is low. J4 VCC1, GND1 Connect this jumper between the middle pin and VCC1 to tie the DE pin high. The driver input is enabled when the DE pin is high. Tie the DE pin to VCC1 for full operation tests. J1, J7 J1, J7 Connect A to Y and B to Z to simulate half duplex operation.

**Table 2. Jumper configuration**

www.ti.com References

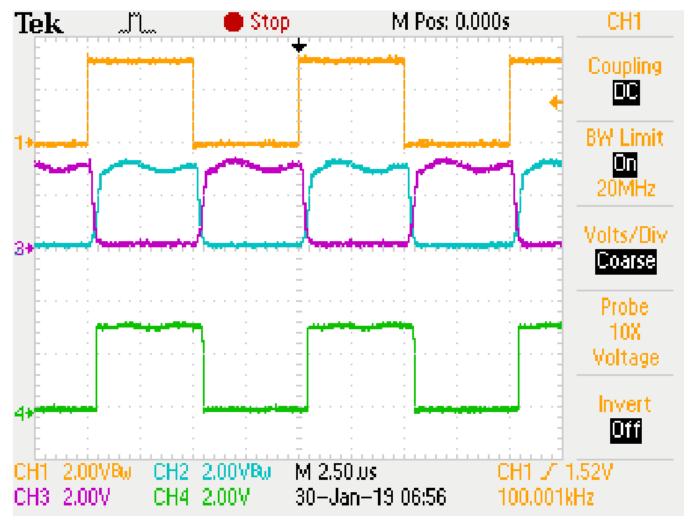

Figure 7. Example scope capture at 100-kHz and VCC1,2 at 3.3 V

#### 6 References

Refer to these references for more information:

- Texas Instruments, Digital Isolator Design Guide

- Texas Instruments, ISO141x 5-kV<sub>RMS</sub> Isolated RS-485/RS-422 Transceiver With Robust EMC data sheet

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated