# **CS4236B**

# CrystalClear<sup>TM</sup> Single Chip Audio System

- Compatible with Sound Blaster<sup>TM</sup>, Sound Blaster Pro<sup>1M</sup>, and Windows Sound System<sup>TM</sup>

- Advanced MPC3-Compliant Input and Output Mixer

- Enhanced Stereo Full Duplex Operation

- Dual Type-F DMA Support

- Industry Leading Delta-Sigma Data Converters

- Fully Plug-and-Play ISA Compatible

- 3.3 V or 5 V ISA Bus Operation

- **Programmable Power Management**

- Hardware Master Volume Control

- Joystick Port and MPU-401 Compatible MIDI Interface

- Optional Enhanced IDE CD-ROM Interface

- CS9236 Wavetable Digital Audio Interface

- 16-Bit Address Decode Support

- CS4236/CS4232/CS4231 Register Compatible

# **General Description**

The CS4236B is a single chip multimedia audio system that is a pin-compatible upgrade to the CS4236. The CS4236B adds an input mixer and a wavetable-synthesis interface to the industry standard CS4236. The CS4236B is compatible with the Microsoft Windows Sound System standard and will run software written to the Sound Blaster and Sound Blaster Pro interfaces. The CS4236B is fully compliant with Microsoft's PC '97 and WHQL audio requirements. In addition, the CS4236B includes hardware master volume control pins as well as extensive power management control over each internal logical section.

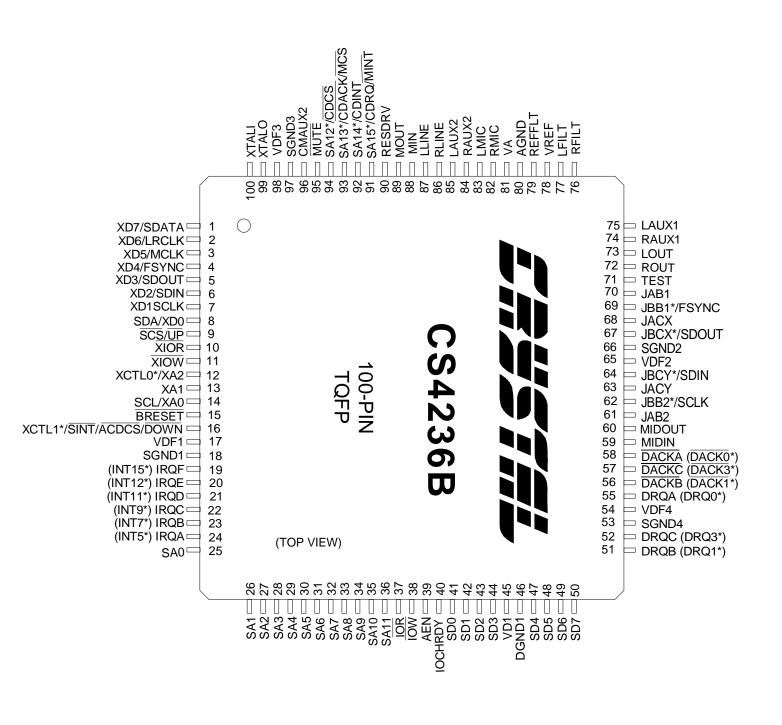

#### **ORDERING INFORMATION:** CS4236B-JQ 100 pin TQFP, 14x14x1.4mm

Advanced Product Information

This document contains information for a new product. Cirrus Logic, Inc. reserves the right to modify this product without notice.

# Cirrus Logic, Inc

P.O. Box 17847, Austin, TX 78760 (512) 445 7222 Fax: (512) 445 7581 http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 1997 (All Rights Reserved)

# TABLE OF CONTENTS

| GENERAL DESCRIPTION                               | 12              |

|---------------------------------------------------|-----------------|

| ISA Bus Interface                                 | 13              |

| I/O Cycles                                        |                 |

| I/O Address Decoding                              | 14              |

| DMA Cycles                                        |                 |

| Interrupts                                        | 15              |

| PLUG AND PLAY                                     | 15              |

| PnP Data                                          |                 |

| Loading Resource Data                             |                 |

| Loading Firmware Patch Data                       |                 |

| The Crystal Key                                   |                 |

| Bypassing Plug and Play                           | 10              |

| Hardware Configuration Data                       | 20              |

| Hostload Procedure                                | 20              |

| External E <sup>2</sup> PROM                      | 24              |

| WINDOWS SOUND SYSTEM CODEC                        | 24              |

| Enhanced Functions (MODEs)                        | <b>20</b><br>26 |

| FIFOs                                             |                 |

| WSS Codec PIO Register Interface                  | 21              |

| DMA Interface                                     | 21              |

| DMA Interface                                     |                 |

| Dual DMA Channel Mapping                          | 20              |

| Single DMA Channel (SDC) Made                     | 20              |

| Single DMA Channel (SDC) Mode                     | 28              |

| Sound System Codec Register Interface             | 29              |

| Direct Mapped Registers (R0-R3)                   | 29              |

| I/O Data Registers (R3)                           | 34              |

| Indirect Mapped Registers (I0-I31)                | 35              |

| WSS Extended Registers (X0-X25)                   | 48              |

| SOUND BLASTER INTERFACE                           |                 |

| Mode Switching                                    | 57              |

| Sound Blaster Register Interface                  |                 |

| Sound Blaster Mixer Registers                     | 59              |

| GAME PORT INTERFACE                               | 60              |

| CONTROL INTERFACE                                 |                 |

| Control Register Interface                        | 61              |

| Control Indirect Registers (C0-C8)                | 65              |

| MPU-401 INTERFACE                                 | 68              |

| MPU-401 Register Interface                        | 68              |

| MIDI UART                                         | 69              |

| MPU-401 "UART" Mode Operation                     | 69              |

| FM SYNTHESIZER (Internal)                         | 69              |

| EXTERNAL PERIPHERAL PORT                          | 70              |

| External Synthesizer Interface<br>CDROM Interface | 70              |

| CDROM Interface                                   | 71              |

| Modem Interface                                   | 72              |

| DSP SERIAL AUDIO DATA PORT                        | 72              |

| CS9236 WAVETABLE SERIAL DATA PORT            | .74  |

|----------------------------------------------|------|

| WSS CODEC SOFTWARE DESCRIPTION               | .75  |

| Calibration                                  | .75  |

| Changing Sampling Rate                       | .76  |

| Changing Audio Data Formats                  | .77  |

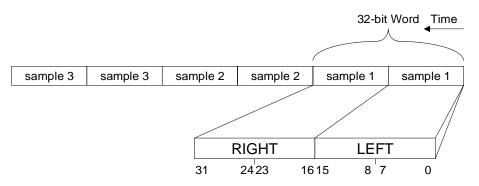

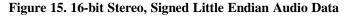

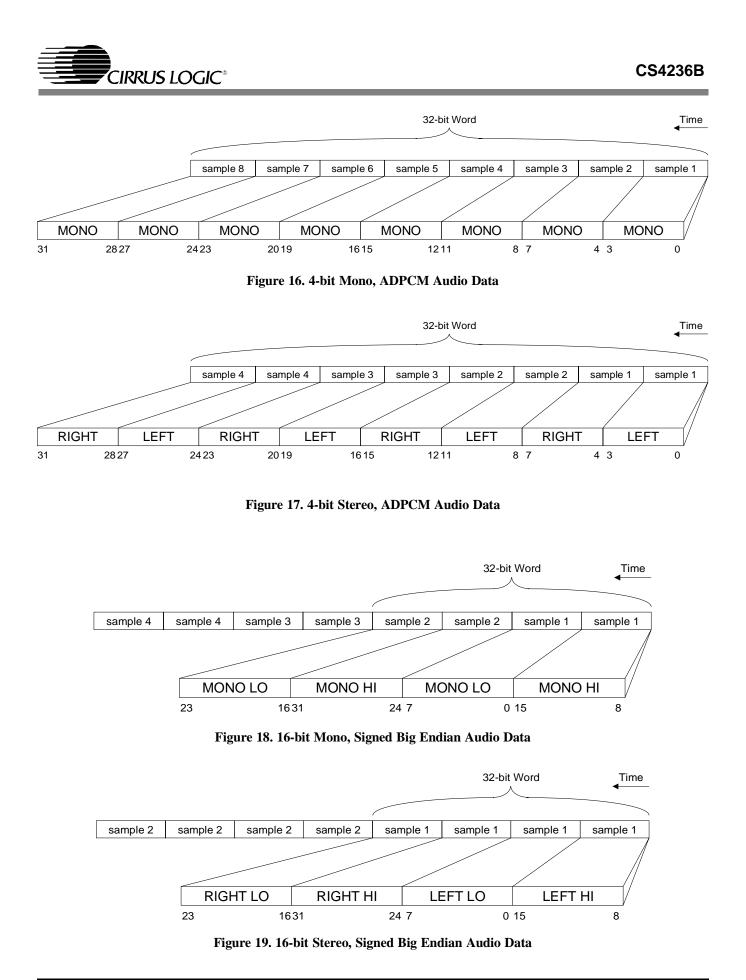

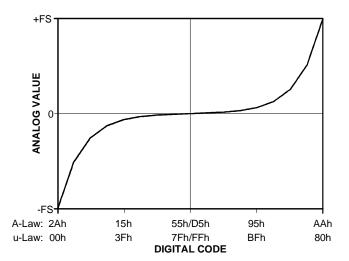

| Audio Data Formats                           | .77  |

| DMA Registers                                |      |

| Digital Loopback                             |      |

| Timer Registers                              | .82  |

| WSS Codec Interrupt                          |      |

| Error Conditions                             | .83  |

| DIGITAL HARDWARE DESCRIPTION                 |      |

| Bus Interface                                | .83  |

| Volume Control Interface                     | .83  |

| Crystal/Clock                                | .84  |

| General Purpose Output Pins                  | .84  |

| Reset and Power Down                         | .85  |

| Multiplexed Pin Configuration                | .85  |

| ANALOG HARDWARE DESCRIPTION                  | .86  |

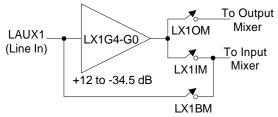

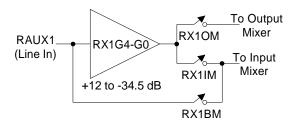

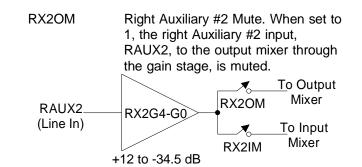

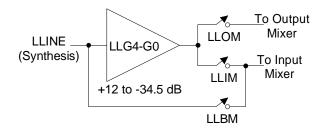

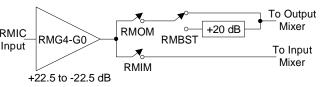

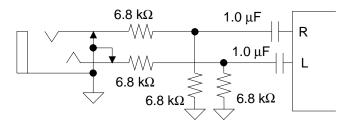

| Line-Level Inputs Plus MPC Mixer             | .86  |

| Microphone Level Inputs                      |      |

| Mono Input                                   |      |

| Line-Level Outputs                           |      |

| Mono Output with Mute Control                |      |

| Miscellaneous Analog Signals                 | .88  |

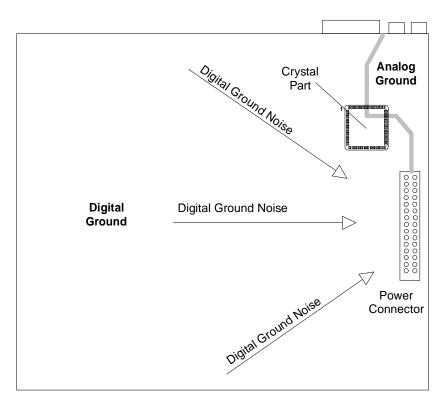

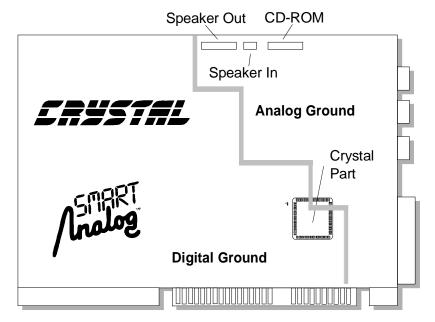

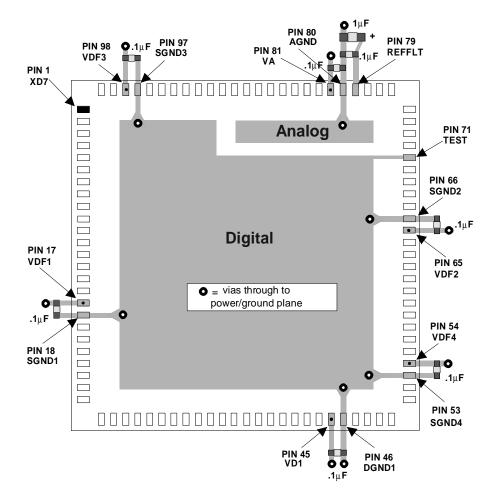

| GROUNDING AND LAYOUT                         | .88  |

| POWER SUPPLIES                               | .89  |

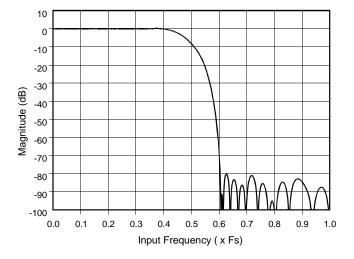

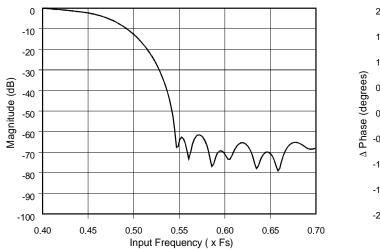

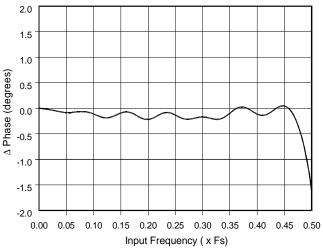

| ADC/DAC FILTER RESPONSE                      | .91  |

| PIN DESCRIPTIONS                             | .93  |

| ISA Bus Interface Pins                       |      |

| Analog Inputs                                | .95  |

| Analog Outputs                               |      |

| MIDI Interface                               | .97  |

| External FM Synthesizer Interface            | .97  |

| External Peripheral Port                     | .97  |

| Joystick/DSP Serial Port Interface           |      |

| CS9236 Wavetable Serial Port Interface       |      |

| CDROM and Modem Interface                    |      |

| Volume Control                               |      |

| Miscellaneous                                |      |

| Power Supplies                               | .103 |

| PARAMETER DEFINITIONS                        | .104 |

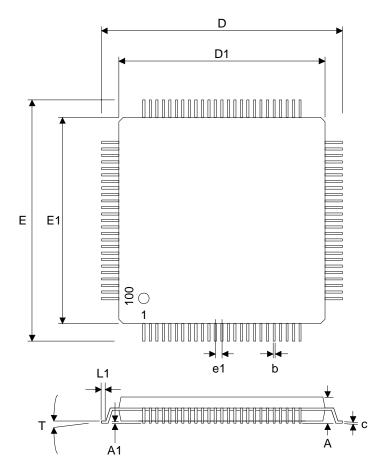

| PACKAGE PARAMETERS                           | .105 |

| APPENDIX A: E <sup>2</sup> PROM TYPICAL DATA | .106 |

| APPENDIX B: CS4236B DIFFERENCES              | .108 |

|                                              |      |

Windows and Windows Sound System are registered trademarks of Microsoft Corporation.

Sound Blaster and Sound Blaster Pro are registered trademarks of Creative Labs.

Adlib is a registered trademark of Adlib Corporation.

#

Measurement Bandwidth is 20 Hz to 20 kHz - unweighted, 16-bit linear coding.)

|                                                                                                 |               | C                  | S4236B-              | JQ           | CS                 | 64236B-              | KQ            |                                                       |

|-------------------------------------------------------------------------------------------------|---------------|--------------------|----------------------|--------------|--------------------|----------------------|---------------|-------------------------------------------------------|

| Parameter*                                                                                      | Symbol        | Min                | Тур                  | Max          | Min                | Тур                  | Max           | Units                                                 |

| Analog Input Characteristics - Minimum Ga                                                       | in Setting (0 | dB); un            | less oth             | erwise s     | pecified           | ł.                   |               |                                                       |

| ADC Resolution (Note                                                                            | I)            | 16                 | -                    | -            | 16                 | -                    | -             | Bits                                                  |

| ADC Differential Nonlinearity (Note                                                             | I)            | -                  | -                    | ±0.5         | -                  | -                    | ±0.5          | LSB                                                   |

| Instantaneous Dynamic Range Line Input<br>(Note 2) Mic Input                                    |               | -                  | 80<br>75             | -            | 80<br>72           | 85<br>79             | -             | dB<br>dB                                              |

| Total Harmonic Distortion Line Input<br>Mic Input                                               |               | -                  | 0.05<br>0.05         | -            | -                  | 0.006<br>0.01        | 0.02<br>0.025 | %<br>%                                                |

| Interchannel Isolation<br>Line to Line Input<br>Line-to-AUX<br>Line-to-AUX                      | ts<br>1       | -<br>-<br>-        | 80<br>80<br>90<br>90 | -<br>-<br>-  |                    | 80<br>80<br>90<br>90 | -<br>-<br>-   | dB<br>dB<br>dB<br>dB                                  |

| Interchannel Gain Mismatch Line Input<br>Mic Input                                              |               | -                  | -                    | ±0.5<br>±0.5 | -                  | -                    | ±0.5<br>±0.5  | dB<br>dB                                              |

| Programmable Input Gain Span Line Input                                                         | ts            | 21.5               | 22.5                 | -            | 21.5               | 22.5                 | -             | dB                                                    |

| Gain Step Size                                                                                  |               | 1.3                | 1.5                  | 1.7          | 1.3                | 1.5                  | 1.7           | dB                                                    |

| ADC Offset Error 0 dB Ga                                                                        | n             | -                  | -                    | -            | -                  | ±10                  | ±100          | LSB                                                   |

| Full Scale Input Voltage: (MGE=1) MIC Input<br>(MGE=0) MIC Input<br>LINE, AUX1, AUX2, MIN Input | ts            | 0.26<br>2.6<br>2.6 | 0.28<br>2.8<br>2.8   | -<br>-       | 0.26<br>2.6<br>2.6 | 0.28<br>2.8<br>2.8   | -             | V <sub>pp</sub><br>V <sub>pp</sub><br>V <sub>pp</sub> |

| Gain Drift                                                                                      |               | -                  | ±100                 | -            | -                  | ±100                 | -             | ppm/°C                                                |

| Input Resistance (Note 1) Mic Input<br>Other Input                                              |               | 8<br>20            | 11<br>23             | -            | 8<br>20            | 11<br>23             | -             | kΩ<br>kΩ                                              |

| Input Capacitance (Note                                                                         | 1)            | -                  | -                    | 15           | -                  | -                    | 15            | pF                                                    |

Notes: 1. This specification is guaranteed by characterization, no production testing. 2. MGE = 1 (see WSS Indirect Reg 10, 11).

\*Parameter definitions are given at the end of this data sheet.

Specifications are subject to change without notice.

# ANALOG CHARACTERISTICS (Continued)

|                                                                              |                    |            | CS4236B-JQ  |                        | CS          | 4236B-      | KQ                     |                        |                      |

|------------------------------------------------------------------------------|--------------------|------------|-------------|------------------------|-------------|-------------|------------------------|------------------------|----------------------|

| Parameter*                                                                   |                    | Symbol     | Min         | Тур                    | Max         | Min         | Тур                    | Max                    | Units                |

| Analog Output Characteristics - Minim                                        | num Atte           | nuation (C | )dB); ur    | nless oth              | erwise      | specifie    | d.                     |                        |                      |

| DAC Resolution (N                                                            | Note 1)            |            | 16          | -                      | -           | 16          | -                      | -                      | Bits                 |

| DAC Differential Nonlinearity (N                                             | Note 1)            |            | -           | -                      | ±0.5        | -           | -                      | ±0.5                   | LSB                  |

| Dynamic Range -Total All C<br>-Instantaneous                                 | Outputs            | TDR<br>IDR | -           | -<br>85                | -           | -<br>80     | 95<br>85               | -                      | dB                   |

| Total Harmonic Distortion (N                                                 | Note 3)            | THD        | -           | 0.01                   | -           | -           | 0.01                   | 0.02                   | %                    |

| Interchannel Isolation Line Out (N                                           | Note 3)            |            | -           | 95                     | -           | -           | 95                     | -                      | dB                   |

| Interchannel Gain Mismatch Lir                                               | ne Out             |            | -           | ±0.1                   | ±0.5        | -           | ±0.1                   | ±0.5                   | dB                   |

| Voltage Reference Output - VREF                                              |                    |            | 2.0         | 2.2                    | 2.5         | 2.0         | 2.2                    | 2.5                    | V                    |

| Voltage Reference Output Current - VRE<br>(Note                              | ∃F<br>es 1,4)      |            | -           | 100                    | 400         | -           | 100                    | 400                    | μA                   |

| DAC Programmable Attenuation Span                                            |                    |            | 100         | 106.5                  | -           | 100         | 106.5                  | -                      | dB                   |

| DAC Attenuation Step Size +12 dB to -<br>-82.5 dB to -9-                     |                    |            | 1.3<br>1.0  | 1.5<br>1.5             | 1.7<br>2    | 1.3<br>1.0  | 1.5<br>1.5             | 1.7<br>2               | dB<br>dB             |

| DAC Offset Voltage                                                           |                    |            | -           | -                      | -           | -           | ±1                     | ±10                    | mV                   |

| 1 0 /                                                                        | MOUT<br>Note 3)    |            | 2.6         | 2.8                    | 3.2         | 2.6         | 2.8                    | 3.2                    | Vpp                  |

| Gain Drift                                                                   |                    |            | -           | 100                    | -           | -           | 100                    | -                      | ppm/°C               |

|                                                                              | sband)<br>Note 1)  |            | -           | -                      | 1           | -           | -                      | 1                      | Degree               |

| External Load Impedance (N                                                   | Note 1)            |            | 10          | -                      | -           | 10          | -                      | -                      | kΩ                   |

| Mute Attenuation                                                             |                    |            | 80          | -                      | -           | 80          | -                      | -                      | dB                   |

| Total Out-of-Band Energy 0.6xFs to 10 (N                                     | 00 kHz<br>Note 1)  |            | -           | -                      | -           | -           | -                      | -45                    | dB                   |

| Audible Out-of-Band Energy 0.6xFs to 2<br>(Fs=8kHz) (N                       | 22 kHz<br>Note 1)  |            | -           | -                      | -           | -           | -                      | -70                    | dB                   |

| Power Supply                                                                 |                    |            |             |                        |             |             |                        |                        |                      |

| Power Supply Current Digital, Ope<br>Analog, Ope<br>Total Ope<br>Total Power | erating<br>erating |            | -<br>-<br>- | 80<br>25<br>105<br>100 | -<br>-<br>- | -<br>-<br>- | 80<br>25<br>105<br>100 | 91<br>31<br>122<br>400 | mA<br>mA<br>mA<br>μA |

|                                                                              | Note 1)            |            | 40          | _                      | -           | 40          | -                      | _                      | dB                   |

Notes: 3. 10 k $\Omega$ , 100 pF load.

4. DC current only. If dynamic loading exists, then the voltage reference output must be buffered or the performance of ADCs and DACs will be degraded.

#### CS4236B-JQ CS4236B-KQ Parameter\* Min Тур Max Min Max Units Typ Mixer Gain Range Span LINE, AUX1, AUX2 45 46.5 dB ---MIC, MIN -42 45 dB Hardware Master \_ \_ 44 48 dB (Digital) Wavetable, Monitor, PC Wave, DSP, FM 90 94.4 dB -\_ -MIC, LINE, AUX1, AUX2 Step Size -1.3 1.5 1.7 dB \_ MIN \_ 2.3 3.0 3.7 dB 2.0 2.4 Hardware Master 1.6 dB -(Digital) Wavetable, Monitor, PC Wave, DSP, FM 0.9 1.5 2.0 dB ---Dynamic Range -Total -94.5 dB ---\_ (Analog Mixers) -Instantaneous 91 88 dB ----**Total Harmonic Distortion** (Note 3) 0.005 0.002 dB --\_ \_ (Analog Mixers)

# **MIXERS** ( $T_A = 25 \text{ °C}$ ; VA, VD1, VDF1-VDF4 = +5V; Input Levels: Logic 0 = 0V, Logic 1 = VD1; 1 kHz Input Sine wave, Measurement Bandwidth is 20 Hz to 20 kHz - unweighted.)

# **ABSOLUTE MAXIMUM RATINGS** (AGND, DGND, SGND = 0V, all voltages with respect to 0V.)

| Pa                      | Symbol                                               | Min             | Max          | Units      |        |

|-------------------------|------------------------------------------------------|-----------------|--------------|------------|--------|

| Power Supplies:         | Digital                                              |                 | -0.3         | 6.0        | V      |

|                         | Analog                                               | VDF1-VDF4<br>VA | -0.3<br>-0.3 | 6.0<br>6.0 | V<br>V |

| Total Power Dissipation | (Supplies, Inputs, Outputs)                          |                 | -            | 1          | W      |

| Input Current per Pin   | (Except Supply Pins)                                 |                 | -10.0        | +10.0      | mA     |

| Output Current per Pin  | (Except Supply Pins)                                 |                 | -50          | +50        | mA     |

| Analog Input Voltage    |                                                      |                 | -0.3         | VA+0.3     | V      |

| Digital Input Voltage:  | SA<11:0>, IOR, IOW, AEN<br>SD<7:0>, DACK <a:c></a:c> |                 | -0.3         | VD1+0.3    | V      |

|                         | All other digital inputs                             |                 | -0.3         | VDF+0.3    | V      |

| Ambient Temperature     | (Power Applied)                                      |                 | -55          | +125       | °C     |

| Storage Temperature     |                                                      |                 | -65          | +150       | °C     |

Warning: Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# **RECOMMENDED OPERATING CONDITIONS** (AGND, DGND, SGND = 0V, of voltages with respect to 0V)

all voltages with respect to 0V.)

| Parameter                     |                  |                                         | Symbol    | Min  | Тур | Max  | Units |

|-------------------------------|------------------|-----------------------------------------|-----------|------|-----|------|-------|

| Power Supplies:               | Digital          |                                         | VD1       | 4.75 | 5.0 | 5.25 | V     |

|                               | Ū.               | (Note 5)                                |           | 3.0  | 3.3 | 3.6  | V     |

|                               | Digital Filtered | ( , , , , , , , , , , , , , , , , , , , | VDF1-VDF4 | 4.75 | 5.0 | 5.25 | V     |

|                               | Analog           |                                         | VA        | 4.75 | 5.0 | 5.25 | V     |

| Operating Ambient Temperature |                  |                                         | TA        | 0    | 25  | 70   | °C    |

Note 5. When VD1 is powered from 3.3 Volts, all ISA bus input pins, except DRQA, must also be 3.3 Volts. DRQA is internally powered from the VDF supply and must have a 5 Volt interface. To use DRQA in a 3.3 Volt application, a level translator is needed.

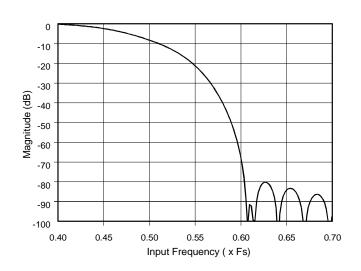

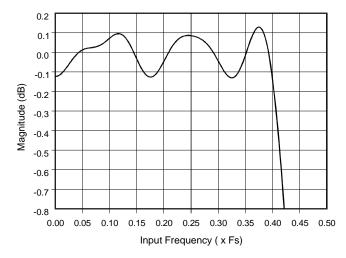

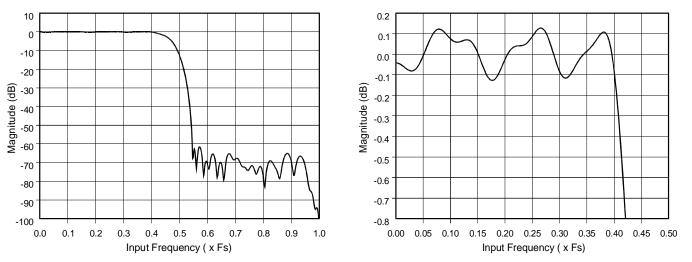

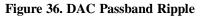

# DIGITAL FILTER CHARACTERISTICS (Note 1)

| Parameter                           |                                                                   | Symbol | Min     | Тур         | Max                     | Units       |

|-------------------------------------|-------------------------------------------------------------------|--------|---------|-------------|-------------------------|-------------|

| Passband                            |                                                                   |        | 0       | -           | 0.40xFs                 | Hz          |

| Frequency Response                  |                                                                   |        | -1.0    | -           | +0.5                    | dB          |

| Passband Ripple                     | (0-0.40xFs)                                                       |        | -       | -           | ±0.1                    | dB          |

| Transition Band                     |                                                                   |        | 0.40xFs | -           | 0.60xFs                 | Hz          |

| Stop Band                           |                                                                   |        | 0.60xFs | -           | -                       | Hz          |

| Stop Band Rejection                 |                                                                   |        | 74      | -           | -                       | dB          |

| Group Delay                         | 8- and 16-bit formats<br>Stereo ADPCM format<br>Mono ADPCM format |        | -<br>-  | -<br>-<br>- | 10/Fs<br>14/Fs<br>18/Fs | S<br>S<br>S |

| Group Delay Variation vs. Frequency | ADCs<br>DACs                                                      |        | -       | -           | 0.0<br>0.1/Fs           | μs<br>μs    |

# **DIGITAL CHARACTERISTICS** (T<sub>A</sub> = 25°C; VA, VDF1-VDF4 = 5V, VD1 = 5V/3V; AGND, DGND1, SGND1-SGND4 = 0V.)

| Parameter                                     |                                       |                                                                                                        |                          | Min              | Max                       | Units            |

|-----------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------|------------------|---------------------------|------------------|

| High-level Input Voltage                      |                                       | Digital Inputs<br>XTALI                                                                                | VIH                      | 2.0<br>VD-1.0    | -                         | V<br>V           |

| Low-level Input Voltage                       |                                       |                                                                                                        | VIL                      | -                | 0.8                       | V                |

| High-level Output Voltage:<br>ISA Bus Pins (e | Vон                                   | н 2.4<br>2.4<br>2.4<br>2.4<br>2.4                                                                      | VD1<br>VDF<br>VDF<br>VDF | V<br>V<br>V<br>V |                           |                  |

| Low-level Output Voltage:                     | ISA Bus Pins<br>IOCHRDY<br>All Others | $I_0 = 24.0 \text{ mA}$<br>$I_0 = 18.0 \text{ mA}$<br>$I_0 = 8.0 \text{ mA}$<br>$I_0 = 4.0 \text{ mA}$ | V <sub>OL</sub>          | -<br>-<br>-      | 0.55<br>0.4<br>0.4<br>0.4 | V<br>V<br>V<br>V |

| Input Leakage Current                         |                                       | (Digital Inputs)                                                                                       |                          | -10              | 10                        | μA               |

| Output Leakage Current                        | (High-Z                               | Digital Outputs)                                                                                       |                          | -10              | 10                        | μA               |

6. Open Collector pins. High level output voltage dependent on external pull up (required) used and Note number of peripherals (gates) attached.

# **TIMING PARAMETERS** ( $T_A = 25 \text{ °C}$ ; VA, VD1, VDF1-VDF4 = +5V; outputs loaded with 30pF Input Levels: Logic 0 = 0V, Logic 1 = VD1)

| Parameter                                                      | Symbol          | Min | Max | Units |

|----------------------------------------------------------------|-----------------|-----|-----|-------|

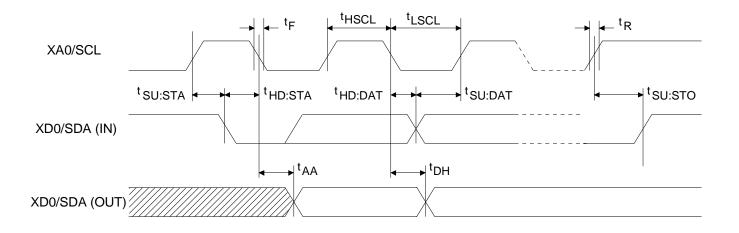

| E <sup>2</sup> PROM Timing (Note 1)                            | I I             |     |     | I     |

| SCL Low to SDA Data Out Valid                                  | t <sub>AA</sub> | 0   | 3.5 | μs    |

| Start Condition Hold Time                                      | thd:STA         | 4.0 | -   | μs    |

| Clock Low Period                                               | <b>t</b> LSCL   | 4.7 | -   | μs    |

| Clock High Period                                              | tHSCL           | 4.0 | -   | μs    |

| Start Condition Setup Time<br>(for a Repeated Start Condition) | ts∪:sta         | 4.7 | -   | μs    |

| Data In Hold Time                                              | thd:dat         | 0   | -   | μs    |

| Data In Setup Time                                             | tsu:dat         | 250 | -   | ns    |

| SDA and SCL Rise Time (Note 7)                                 | t <sub>R</sub>  | -   | 1   | μs    |

| SDA and SCL Fall Time                                          | tF              | -   | 300 | ns    |

| Stop Condition Setup Time                                      | tsu:sto         | 4.7 | -   | μs    |

| Data Out Hold Time                                             | tDH             | 0   | -   | ns    |

Notes 7. Rise time on SDA is determined by the capacitance of the SDA line with all connected gates and the external pullup resistor required.

**E<sup>2</sup>PROM 2-Wire Interface Timing**

# TIMING PARAMETERS (Continued)

| Parameter                                                                           |                                | Symbol                                   | Min      | Max     | Units    |

|-------------------------------------------------------------------------------------|--------------------------------|------------------------------------------|----------|---------|----------|

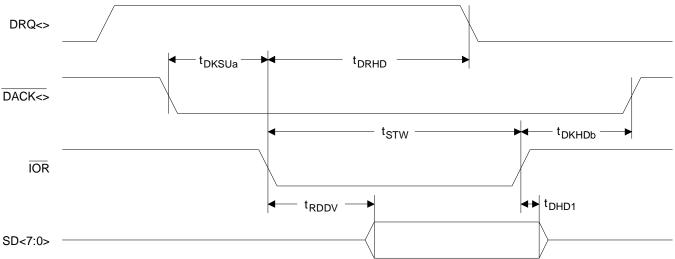

| Parallel Bus Timing                                                                 |                                |                                          |          |         |          |

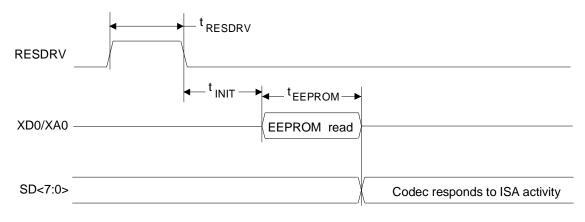

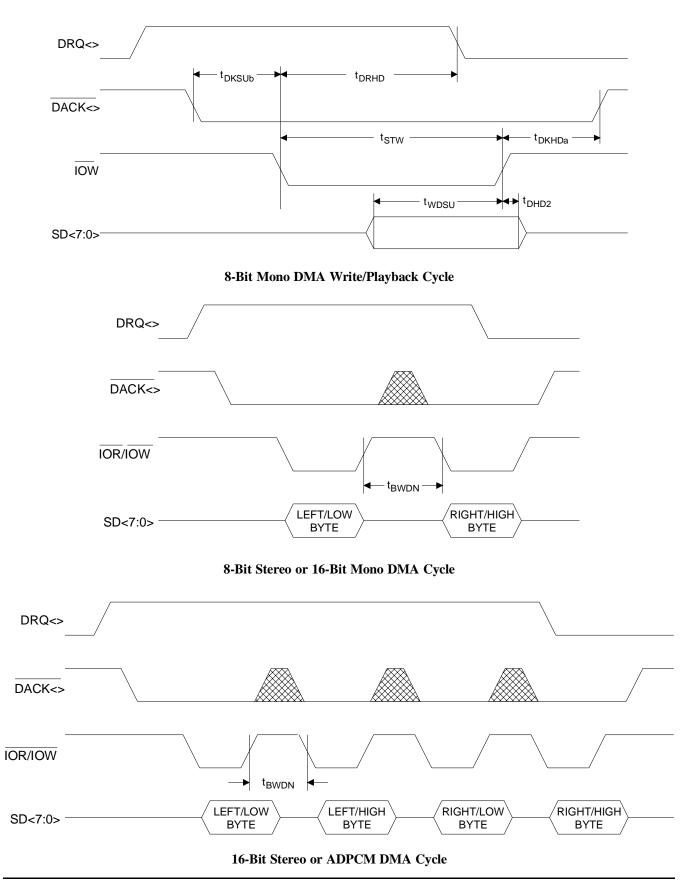

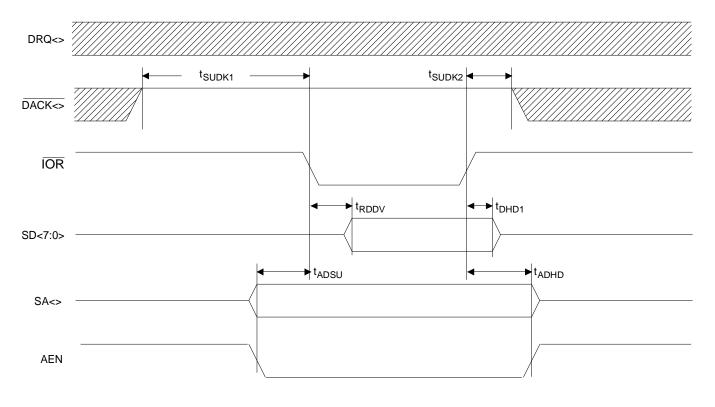

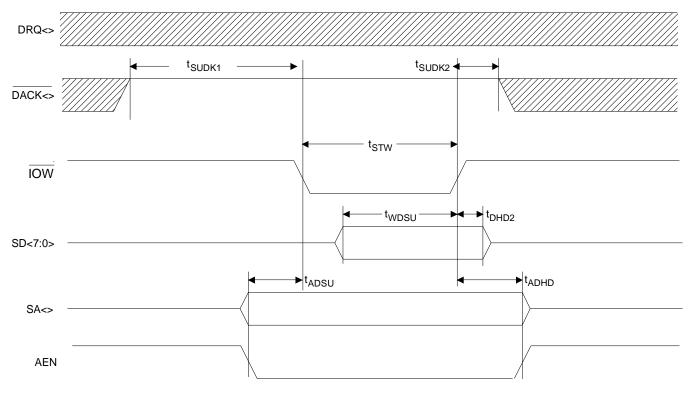

| IOW or IOR strobe width                                                             |                                | tstw                                     | 90       | -       | ns       |

| Data valid to IOW rising edge                                                       | (write cycle)                  | twdsu                                    | 22       | -       | ns       |

| IOR falling edge to data valid (read cycle)                                         |                                | tRDDV                                    | -        | 60      | ns       |

| SA <> and AEN setup to IOR or IOW falling                                           | ng edge                        | tadsu                                    | 22       | -       | ns       |

| SA <> and AEN hold from IOW or IOR ris                                              | ing edge                       | tadhd                                    | 10       | -       | ns       |

| DACK<> inactive to IOW or IOR falling ed<br>immediately followed by a non-DMA cycle | • • •                          | tSUDK1                                   | 60       | -       | ns       |

| DACK<> active from IOW or IOR rising ec<br>cycle completion followed by DMA cycle)  | lge (non-DMA<br>(Note 8)       | tSUDK2                                   | 0        | -       | ns       |

| DACK<> setup to IOR falling edge (DMA<br>DACK<> setup to IOW falling edge           | cycles)<br>(Note 8)            | tDKSUa<br>tDKSUb                         | 25<br>25 | -       | ns<br>ns |

| Data hold from IOW rising edge                                                      |                                | tDHD2                                    | 15       | -       | ns       |

| DRQ<> hold from IOW or IOR falling edge<br>(assumes no more DMA cycles needed)      | e DTM(I10) = 0<br>DTM(I10) = 1 | t <sub>DRHD</sub>                        | -<br>-25 | 45<br>- | ns       |

| Time between rising edge of IOW or IOR edge of IOW or IOR                           | to next falling                | tBWDN                                    | 80       | -       | ns       |

| Data hold from IOR rising edge                                                      |                                | tDHD1                                    | 0        | 25      | ns       |

| DACK<> hold from IOW rising edge<br>DACK<> hold from IOR rising edge                |                                | t <sub>DKHDa</sub><br>t <sub>DKHDb</sub> | 25<br>25 | -       | ns<br>ns |

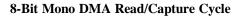

| RESDRV pulse width high                                                             | (Note 1)                       | tresdrv                                  | 1        | -       | ms       |

| Initialization Time                                                                 | (Note 1, 9)                    | t <sub>INIT</sub>                        | 130      | 1200    | ms       |

| EEPROM Read Time                                                                    | (Note 1, 10)                   | <b>t</b> EEPROM                          | 1        | 420     | ms       |

| XTAL, 16.9344 MHz, frequency                                                        | (Notes 1, 11)                  |                                          | 16.92    | 16.95   | MHz      |

| XTALI high time                                                                     | (Notes 1, 11)                  |                                          | 24       | -       | ns       |

| XTALI low time                                                                      | (Notes 1, 11)                  |                                          | 24       | -       | ns       |

| Sample Frequency                                                                    | (Note 1)                       | Fs                                       | 3.918    | 50      | kHz      |

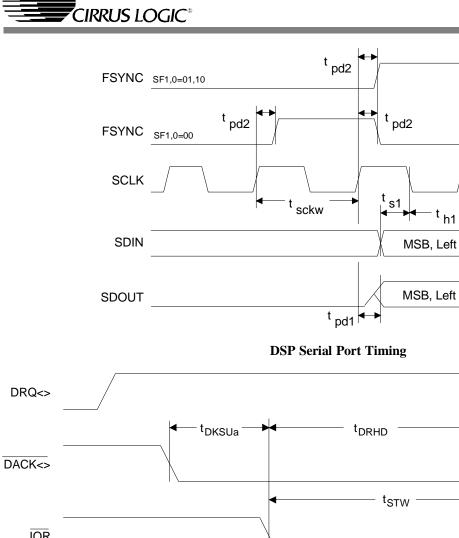

| Serial Port Timing                                                                  |                                | 1                                        |          |         |          |

| SCLK rising to SDOUT valid                                                          | (Note 1)                       | tPD1                                     | -        | 60      | ns       |

| SCLK rising to FSYNC transition                                                     | (Note 1)                       | tPD2                                     | -20      | 20      | ns       |

| SDIN valid to SCLK falling                                                          | (Note 1)                       | ts1                                      | 30       | -       | ns       |

| SDIN hold after SCLK falling                                                        | (Note 1)                       | tH1                                      | 30       | -       | ns       |

Notes: 8. AEN must be high during DMA cycles.

9. Initialization time depends on the power supply circuitry, as well as the the type of clock used. 10. EEPROM read time is dependent on amount of data in EEPROM. Minimum time relates to no

EEPROM present. Maximum time relates to EEPROM data size of 2k bytes.

11. The Sample frequency specification must not be exceeded.

<sup>- t</sup> h1

**Reset Timing**

CS4236B

I/O Read Cycle

I/O Write Cycle

# GENERAL DESCRIPTION

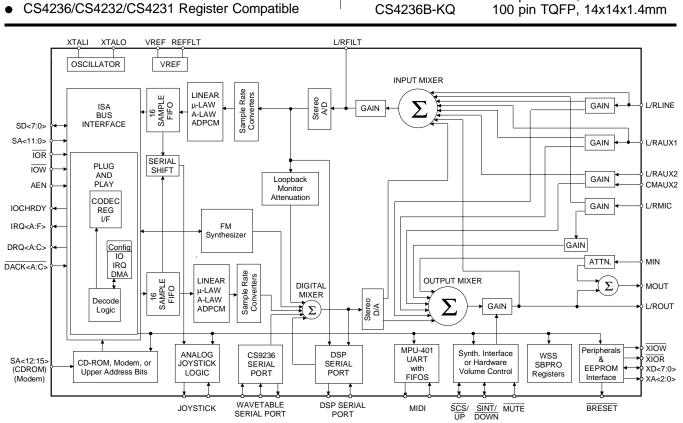

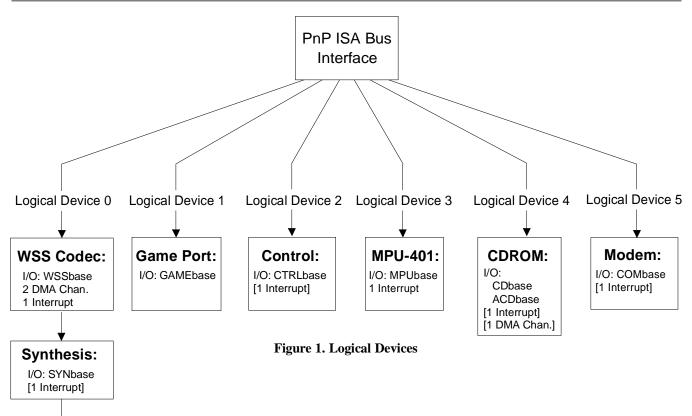

This device is comprised of six physical devices along with Plug-and-Play support for two additional external devices. The internal devices are:

Windows Sound System Codec Sound Blaster Pro Compatible Interface Game Port (Joystick) Control MPU-401 FM Synthesizer The two external devices are: IDE CDROM Modem

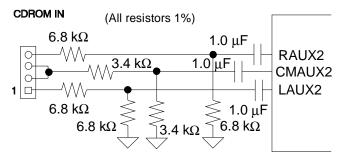

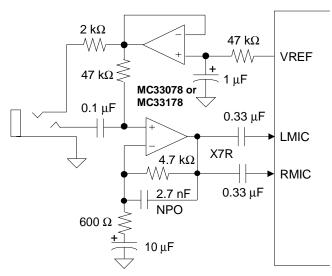

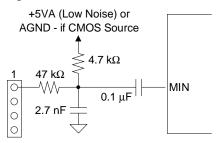

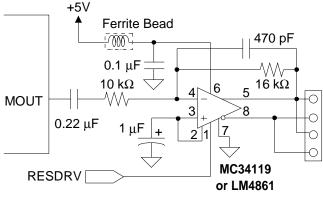

A full ISA interface with Plug and Play compatibility and an External Peripheral Port for interfacing to external devices (i.e. Wave-Table Synthesizer, CDROM, and Modem) is included. Since the Wave-Table Synthesizer and CDROM analog inputs are external, mapping as shown in Figure 5, on page 58, must be used to maintain Sound Blaster compatibility, i.e. CDROM analog must be connected to the AUX2 analog inputs of the mixer.

On power up, this part requires a RESDRV signal to initialize the internal configuration. When initially powered up, the part is isolated from the bus, and each device supported by the part must be activated via software. Once activated, each device responds to the resources given (Address, IRQ, and DMA channels). The eight devices listed above are grouped into six logical devices, as shown in Figure 1 (bracketed features are supported, but typically not used). The six logical devices are:

# LOGICAL DEVICE 0:

Windows Sound System Codec (WSS Codec) Adlib/Sound Blaster-compatible Synthesizer Sound Blaster Pro Compatible Interface

LOGICAL DEVICE 1: Game Port

LOGICAL DEVICE 2: Control

# LOGICAL DEVICE 3: MPU401

# LOGICAL DEVICE 4: CDROM

# LOGICAL DEVICE 5: Modem

Logical Device 0 consists of three physical devices. The WSS Codec and the Synthesizer are grouped together since the original Windows Sound System board expected an FM synthesizer if the codec was present. The Sound Blaster Pro Compatible interface, SBPro, is also grouped to allow the WSS Codec and the SBPro to share Interrupts and DMA channels. The Synthesizer device could be the internal FM synthesizer, or a synthesizer externally located on the Peripheral Port. The external synthesizer interface supports both FM and wavetable synthesizers such as the CS9233. The WSS Codec, FM synthesizer, and the SBPro compatible devices are internal to the part.

Logical Device 1 is the Game Port that supports up to two joystick devices.

Logical Device 2 is the Control device that supports global features of the part. This device uses I/O locations to control power management, joystick rate, and PnP resource data loading.

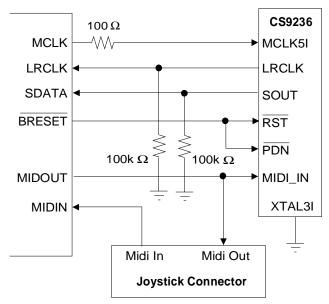

Logical Device 3 is the MPU-401 interface. The MPU-401 MIDI interface includes a 16-byte FIFO for data transmitted out the MIDOUT pin and a 16-byte FIFO for data received from the MIDIN pin.

Logical Device 4 supports an IDE CDROM connected to the peripheral port. This interface, on the external peripheral port, can support CDROMs with up to 8 I/O locations and supports both the base address and the alternate base address, an interrupt, and a DMA channel. Although this logical device is listed as a CDROM, any external device that fits within the resources listed above may be substituted.

Logical Device 5 supports a modem connected to the peripheral port. This interface, on the external peripheral port, supports modems with 2 to 256 I/O locations (only SA2-SA0 are buffered through the part) and supports a base address and an interrupt. Although this logical device is listed as a modem, any external device that fits within the resources listed above may be substituted.

# ISA Bus Interface

SBPro:

I/O: SBbase

(DMA shared) (Interrupt shared)

The 8-bit parallel I/O and 8-bit parallel DMA ports provide an interface which is compatible with the Industry Standard Architecture (ISA) bus. The ISA Interface enables the host to communicate with the various functional blocks within the part via two types of accesses: Programmed I/O (PIO) access, and DMA access.

A number of configuration registers must be programmed prior to any accesses by the host computer. The configuration registers are programmed via a Plug-and-Play configuration sequence or via configuration software provided by Crystal Semiconductor.

# I/O CYCLES

Every device that is enabled, requires I/O space. An I/O cycle begins when the part decodes a valid address on the bus while the DMA acknowledge signals are inactive and AEN is low. The  $\overline{IOR}$  and  $\overline{IOW}$  signals determine the direction of the data transfer. For read cycles, the part will drive data on the SD<7:0> lines while the host asserts the  $\overline{IOR}$  strobe. Write cycles require the host to assert data on the SD<7:0> lines and strobe the  $\overline{IOW}$  signal. Data is latched on the rising edge of the  $\overline{IOW}$  strobe.

# I/O ADDRESS DECODING

The logical devices use 10-bit or 12-bit address decoding. The Synthesizer, Sound Blaster, Game Port, MPU-401, CDROM, and Modem devices support 10-bit address decoding, while the Windows Sound System and Control devices support 12-bit address decoding. Devices that support 10-bit address decoding, require A10 and A11 be zero for proper decode; therefore, no aliasing occurs through the 12-bit address space.

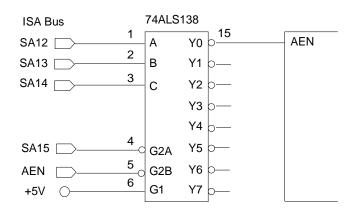

To prevent aliasing into the upper address space, a "16-bit decode" option may be used, where the upper address bits SA12 through SA15 are connected to the part. SA12-SA15 are then decoded to be 0,0,0,0 for all logical device address decoding. When the upper address bits are used, the CDROM and Modem interfaces are no longer available since the upper address pins are multiplexed with the CDROM and Modem interfaces (See Reset and Power Down section). If the CDROM or Modem is needed, the circuit shown in Figure 2 can replace the SA12 through SA15 pins and provide the same functionality. Four cascaded OR gates, using a 74ALS32, can replace the ALS138 in Figure 2, but causes a greater delay in address decoding.

Figure 2. 16-bit Decode Circuit

# DMA CYCLES

The part supports up to three 8-bit ISA-compatible DMA channels. The default hardware connections, which can be changed through the hardware configuration data, are:

DMA A = ISA DMA channel 0 DMA B = ISA DMA channel 1 DMA C = ISA DMA channel 3

The typical configuration would require two DMA channels. One for the WSS Codec and Sound Blaster playback, and the other for WSS Codec capture (to support full-duplex). The CDROM, if used, can also support a DMA channel, although this is not typical.

DMA cycles are distinguished from control register cycles by the generation of a DRQ (DMA Request). The host acknowledges the request by generating a DACK (DMA Acknowledge) signal. The transfer of audio data occurs during the DACK cycle. During the DACK cycle the address lines are ignored.

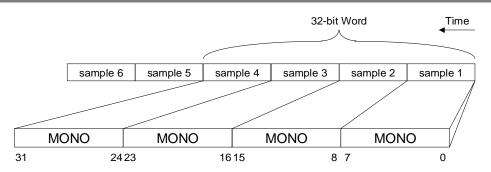

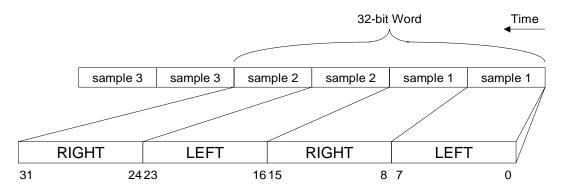

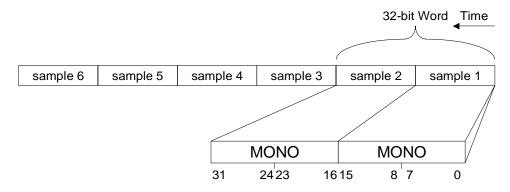

The digital audio data interface uses DMA request/grant pins to transfer the digital audio data between the part and the ISA bus. Upon receipt of a DMA request, the host processor responds with an acknowledge signal and a command strobe which transfers data to and from the part, eight bits at a time. The request pin stays active until the appropriate number of 8-bit cycles have occurred. The number of 8-bit transfers will vary depending on the digital audio data format, bit resolution, and operation mode.

The DMA request signal can be asserted at any time. Once asserted, the DMA request will remain asserted until a complete DMA cycle occurs. A complete DMA cycle consists of one or more bytes depending on which device internal to the part is generating the request.

# INTERRUPTS

For Plug-and-Play flexibility, six interrupt pins are supported, although only one or two are typically used. The default hardware connections, which can be modified through the hardware configuration data, are:

IRQ A = ISA Interrupt 5 IRQ B = ISA Interrupt 7 IRQ C = ISA Interrupt 9 IRQ D = ISA Interrupt 11 IRQ E = ISA Interrupt 12 IRQ F = ISA Interrupt 15

The typical configuration would support two interrupt sources: one shared between the WSS Codec and the Sound Blaster Pro compatible devices, and the other for the MPU401 device. Interrupts are also supported for the Synthesizer, Control, CDROM devices, but are typically not used. If the modem logical device (LD5) is used, it would typically support an interrupt.

# PLUG AND PLAY

The Plug-and-Play (PnP) interface logic is compatible with the Intel/Microsoft Plug-and-Play specification, version 1.0a, for an ISA-bus device. Since the part is an ISA-bus device, it only supports ISA-compatible IRQs and DMA channels. Plug and Play compatibility allows the PC to automatically configure the part into the system upon power up. Plug and Play capability optimally resolves conflicts between Plug and Play and non-Plug and Play devices within the system. Alternatively, the PnP feature can be bypassed. See the *Bypassing PnP* section for more information. For a detailed Plug-and-Play protocol description, please refer to the *Plug and Play ISA Specification*.

To support Plug-and-Play in ISA systems that do not have a PnP BIOS or a PnP-aware operating system, the Configuration Manager (CM) TSR and an ISA Configuration Utility (ICU) from Intel Corp. are used to provide these functions. The CM isolates the cards, assigns Card Select Numbers, reads PnP card resource requirements, and allocates resources to the cards based on system resource availability. The ICU is used to keep the BIOS and the CM informed of the current system configuration. It also aids users in determining configurations for non-PnP ISA cards. A more thorough discussion of the Configuration Manager and the ISA Configuration Utility can be found in the Product Development Information document of the Plug and Play Kit by Intel Corp. In a PnP BIOS system, the BIOS is responsible for configuring at least all system board PnP devices. Some systems require additional software to aid the BIOS in configuring PnP ISA cards. The PnP BIOS can execute all PnP functions independently of the type of operating system. However, if a PnP aware operating system is present, the PnP responsibilities are shared between the BIOS and the operating system. For more information regarding PnP BIOS, please refer to the latest revision of the Plug and Play BIOS Specification published by Compaq Computer, Phoenix Technologies, and Intel.

The Plug and Play configuration sequence maps the various functional blocks of the part (logical devices) into the host system address space and configures both the DMA and interrupt channels. The host has access to the part via three 8-bit auto-configuration ports: Address port (0279h), Write Data port (0A79h), and relocatable Read Data port (020Bh - 03FFh). The read data port is relocated automatically by PnP software when a conflict occurs.

The configuration sequence is as follows:

- 1. Host sends a software key which places all PnP cards in the sleep state (or Plug-and-Play mode).

- 2. The Crystal part is isolated from the system using an isolation sequence.

- 3. A unique identifier (handle) is assigned to the part and the resource data is read.

- 4. After all cards' resource requirements are determined, the host uses the handle to assign conflict-free resources

- 5. After the configuration registers have been programmed, each configured logical device is activated.

- 6. The part is then removed from Plug-and-Play mode.

Upon power-up, the chip is inactive and must be enabled via software. The Crystal part monitors writes to the PnP Auto-Configuration Address port (0279h). If the host sends a PnP initiation key, consisting of a series of 32 predefined byte writes, the hardware will detect the key and place the part into the Plug-and-Play (PnP) mode. Another method to program the part is to use a special Crystal initiation key which functions like the PnP initiation key, but can be invoked by the user at any time. However, the Crystal Key only supports one Crystal part per system. The Crystal key and special commands are detailed in the *Crystal Key* and *Bypassing PnP* sections.

The isolation sequence uses a unique 72-bit serial identifier. The host performs 72 pairs of I/O read accesses to the Read Data port. The identifier determines what data is put on the data bus in response to those read accesses. When the isolation sequence is complete, the CM assigns a Card Select Number (CSN) to the part. This number distinguishes the Crystal part from the other PnP devices in the system. The Configuration Manager (CM) then reads the resource data from the Crystal part. The 72-bit identifier and the resource data is either stored in an external user-programmable E<sup>2</sup>PROM, or loaded via a "hostload" procedure from BIOS before PnP software is initiated. The CM determines the necessary resource requirements for the system and then programs the part through the configuration registers. The configuration register data is written one logical device at a time. After all logical devices have been configured, CM activates each device individually. Each logical device is now available on the ISA bus and responds to the programmed address range, DMA channels, and interrupts that have been allocated to that logical device.

# PnP Data

Hardware Configuration and Plug-and-Play resource data must be loaded into the part's RAM. The data may be stored in an external  $E^2$ PROM or may be downloaded from the host.

To load the data, refer to the *Loading Resource Data* section. The following is the Plug-and-Play resource data:

The first nine bytes of the PnP resource data are the Plug-and-Play ID, which uniquely identifies the Crystal part from other PnP devices. The Crystal default is broken down as follows:

- 0Eh, 63h Crystal ID 'CSC' in compressed ASCII. (See the PnP Spec for more information)

- 42h Oem ID. A unique Oem ID must be obtained from Crystal for each unique Crystal product used.

- 35h Crystal product ID for the CS4236B

- FFh, FFh, FFh, FFh Serial number. This can be modified by each OEM to uniquely identify their card.

- ??h Checksum.

Of the 9-byte serial number listed above, Crystal software uses the first two bytes to indicate the presence of a Crystal part, and the fourth byte, 0x35, to indicate the CS4236B; therefore, these three bytes must not be altered.

The next 3 bytes are the PnP version number. The default is version 1.0a: 0Ah, 10h, 01h.

The next sequence of bytes are the ANSI identifier string. The default is: 82h, 0Eh, 00h, 'Crystal Codec', 00h.

The logical device data must be entered using the PnP ISA Specification format. Typical logical device values are found in Table 1. The  $E^2$ PROM version for this data is found in Appendix A.

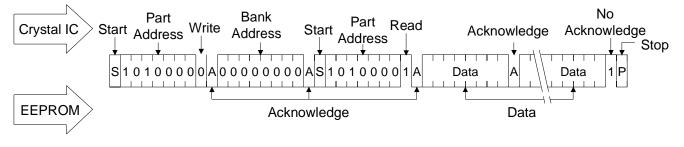

# Loading Resource Data

A serial E<sup>2</sup>PROM interface allows user-programmable serial number and resource data to be stored in an external  $E^2$ PROM. The interface is compatible with devices from a number of vendors and the size may vary according to specific customer requirements. The maximum size for resource data supported by the part's internal RAM is 384 bytes of combined Hardware Configuration and PnP resource data. With the addition of the 4-byte header, the maximum amount of  $E^2$ PROM space used would be 388 bytes. However, the part also supports firmware upgrades via the  $E^2$ PROM. The maximum size  $E^2$ PROM supported is 2k bytes. After power-up, the existence of an  $E^2$ PROM is checked by reading the first two bytes from the  $E^2$ PROM interface. If the data from the  $E^2PROM$  port reads 55h and BBh, then the rest of the  $E^2$ PROM data is loaded into the internal RAM. If the first two bytes aren't correct, the  $E^2$ PROM is assumed not to exist and a "hostload" procedure must be used to load the internal RAM. The Hostload procedure can be found in the Hostload section. For motherboard designs, an  $E^2$ PROM should still be included, to allow faster integrating of resource and firmware patch data. This allows updates without respiring BIOS code. If the part is installed on a plug-in card, then an external  $E^2$ PROM is required to ensure that the proper PnP resource data is loaded into the internal RAM prior to a PnP sequence. See the

*External*  $E^2 PROM$  section for more information on the serial  $E^2 PROM$  interface and  $E^2 PROM$  programming.

The format for the data stored in the  $E^2$ PROM is as follows:

- (Hardware Configuration Data:) 2 bytes E<sup>2</sup>PROM validation: 55h, BBh

- 2 bytes length of resource data in  $E^2$ PROM

- 19 bytes Hardware Configuration

- (Plug and Play Resource Data:) 9 bytes Plug and Play ID

- 3 bytes Plug and Play version number

- Variable number of bytes of user defined ASCII ID string

- Logical Device 0 (Windows Sound System, FM Synthesizer, Sound Blaster Pro) data

- Logical Device 1 (Game Port) data

- Logical Device 2 ( Control) data

- Logical Device 3 (MPU-401) data

Logical Device 4 ( CD-ROM) data

Logical Device 5 (Modem) data

End of Resource byte & checksum byte

Firmware patch code.

A typical  $E^2$ PROM data load, in assembly format, can be found in Appendix A.

# Loading Firmware Patch Data

An external  $E^2$ PROM is read during the powerup sequence that stores Hardware Configuration and PnP data, and firmware patch data. The part contains RAM and ROM to run the core proces-

sor. The RAM allows updates to the core processor functionality. Placing the firmware patches in  $E^2$ PROM, gives the maximum functionality at power-up without the need for a software driver.

The firmware patch data is typically included at the end of the PnP resource data. Crystal provides a utility that will read in patch data from a file, and append it to the PnP resource data. The patch file must be obtained from Crystal.

# The Crystal Key

NOTE: The Crystal Key cannot differentiate between multiple Crystal Codecs in a system; therefore, ONLY ONE Crystal part is allowed in systems using the Crystal Key. To allow multiple parts in a system, the Plug-and-Play isolation sequence must be used since it supports multiple parts via the serial identifier used in the isolation sequence.

| Physical Device              | Logical Device               | Best Choice      | Acceptable<br>Choice 1       | Sub optimal<br>Choice 1           | Sub optimal<br>Choice 2 |

|------------------------------|------------------------------|------------------|------------------------------|-----------------------------------|-------------------------|

| WSS                          | 0                            |                  |                              | ANSI ID =                         | WSS/SB                  |

| 16-bit address<br>decode     | WSSbase<br>Length/Alignment  | 534h-534h<br>4/4 | 534-608h<br>4/D4h            | 534-FFCh<br>4/4                   |                         |

| high true<br>edge sensitive  | IRQ                          | 5<br>(SB share)  | 5,7,9,11,12,15<br>(SB share) | 5, 7, 9, 11, 12, 15<br>(SB share) |                         |

| 8-bit, count by byte, type A | DMA                          | 1<br>(SB share)  | 0, 3<br>(SB share)           | 0, 1, 3<br>(SB share)             |                         |

| same                         | DMA                          | 0, 3             | 0, 1, 3                      |                                   |                         |

| Synthesis                    | 0                            |                  |                              |                                   |                         |

| 16-bit address decode        | SYNbase<br>Length/Alignment  | 388h<br>4/8      | 388h<br>4/8                  | 388-3F8h<br>4/8                   |                         |

|                              | IRQ                          |                  |                              |                                   |                         |

| SB Pro                       | 0                            |                  |                              |                                   |                         |

| 16-bit address<br>decode     | SBbase<br>Length/Alignment   | 220h<br>16/16    | 220-260h<br>16/32            | 220-300h<br>16/32                 |                         |

| Game Port                    | 1                            |                  |                              | ANSI ID =                         | = GAME                  |

| 16-bit address decode        | GAMEbase<br>Length/Alignment | 200h<br>8/8      | 208h<br>8/8                  |                                   |                         |

| Control                      | 2                            |                  |                              | ANSI ID                           | = CTRL                  |

| 16-bit address<br>decode     | CTRLbase<br>Length/Alignment | 120-3F8h<br>8/8  |                              |                                   |                         |

|                              | IRQ                          |                  |                              |                                   |                         |

| MPU401                       | 3                            |                  | 1                            | ANSI ID                           | = MPU                   |

| 16-bit address               | MPUbase                      | 330h             | 330-360h                     | 330-3E0h                          |                         |

| decode                       | Length/Alignment             | 2/8              | 2/8                          | 2/8                               |                         |

|                              | IRQ                          | 9                | 9,11,12,15                   |                                   |                         |

---- Feature not supported in the listed configuration, but is supported through customization.

### Table 1. Typical Motherboard Plug-and-Play Resource Data

The Crystal key places the part in the configuration mode. Once the Crystal key has been initiated, new PnP resource data can be downloaded by a hostload sequence, or an alternate method of programming the configuration registers may be used. This alternate method is referred to as the "SLAM" method. The SLAM method allows the user to directly access the configuration registers, configure, and activate the chip, and then, optionally, disable the PnP and/or Crystal key feature. The SLAM method uses commands that are similar to the PnP commands; however, they are different since the user has direct access to the configuration registers. To use the SLAM method, see the *Bypassing PnP* section.

The following 32 bytes, in hex, are the Crystal key:

96, 35, 9A, CD, E6, F3, 79, BC,

5E, AF, 57, 2B, 15, 8A, C5, E2

F1, F8, 7C, 3E, 9F, 4F, 27, 13,

09, 84, 42, A1, D0, 68, 34, 1A

# **Bypassing Plug and Play**

The SLAM method allows the user to bypass the Plug and Play features and, as an option, allows the part to act like a non-Plug and Play or legacy device; however, the SLAM method only supports one Crystal IC per system. The user directly programs the resources into the part, and then optionally disables the PnP and/or the Crystal Key, which forces the part to disregard any future PnP or Crystal initiation key sequences (All activated logical devices appear as legacy devices to PnP). The Crystal and PnP keys can also be disabled through the E<sup>2</sup>PROM.

To use the SLAM method, the following sequence must be followed:

- 1. Host sends 32-byte Crystal key to I/O 0279h, chip enters configuration mode.

- 2. Host programs CSN (Card Select Number) by writing a 06h and 00h to I/O 0279h.

- 3. Host programs the configuration registers of each logical device by writing to I/O 0279h. The following data is the maximum amount of information per device. All current devices only need a subset of this data:

Logical Device ID (15h, xxh) xxh is logical device number: 0-5

- I/O Port Base Address 0 (47h, xxh, xxh) high byte , low byte

- I/O Port Base Address 1 (48h, xxh, xxh) high byte , low byte

- I/O Port Base Address 2 (42h, xxh, xxh) high byte , low byte

- Interrupt Select 0 (22h, xxh)

Interrupt Select 1 (27h, xxh)

DMA Select 0 (2Ah, xxh)

DMA Select 1 (25h, xxh)

Activate Device (33h, 01h) (33h, 00h deactivates a device)

- 4. Repeat #3 for each logical device to be enabled. (Not all devices need be enabled.)

- 5. Host activates chip by writing a 79h to 279h.

- 6. (Optional) Host disables PnP Key by writing a 55h to CTRLbase+5. The part will not participate in any future PnP cycles. The Crystal Key can also be disabled by writing a 56h to CTRLbase+5.

NOTE: To enable the PnP/Crystal Keys after they have been disabled by the SLAM method, bring the RESDRV pin to a logic high or remove power from the device.

The following illustrates typical data sent using the SLAM method.

| 006h, 001h       | ; CSN=1                     |

|------------------|-----------------------------|

| 015h, 000h       | ; LOGICAL DEVICE 0          |

| 047h, 005h, 034h | ; WSSbase = 0x534           |

| 048h, 003h, 088h | ; SYNbase = 0x388           |

| 042h, 002h, 020h | ; SBbase = 0x220            |

| 022h, 005h       | ; WSS & SB IRQ = 5          |

| 02Ah, 001h       | ; WSS & SB DMA0 = 1         |

| 025h, 003h       | ; WSS capture DMA1 = 3      |

| 033h, 001h       | ; activate logical device 0 |

| 015h, 001h       | ; LOGICAL DEVICE 1          |

| 047h, 002h, 000h | ; GAMEbase = 0x200          |

| 033h, 001h       | ; activate logical device 1 |

| 015h, 002h       | ; LOGICAL DEVICE 2          |

| 047h, 001h, 020h | ; CTRLbase = 0x120          |

| 033h, 001h       | ; activate logical device 2 |

| 015h, 003h       | ; LOGICAL DEVICE 3          |

| 047h, 003h, 030h | ; MPUbase=0x330             |

| 022h, 009h       | ; MPU IRQ = 9               |

| 033h, 001h       | ; activate logical device 3 |

| 079h             | ; activate Crystal device   |

If all the above data is sent, after the Crystal key, all devices except the CDROM and Modem will respond to the appropriate resources given.

# Hardware Configuration Data

The Hardware Configuration data contains mapping information that links interrupt and DMA pins with actual interrupt numbers used by PnP and SLAM procedures. This data also controls the XCTL0/XA2 pin functionality. The Hardware Configuration data precedes the PnP Resource data.

The Hardware Configuration data is either 19 or 23 bytes long and contains the data necessary to configure the part. If an  $E^2PROM$  is not used (Hostload), the first four bytes are not needed, which means the configuration data is only 19 bytes long. The configuration data maps the many functions of the logical devices to the physical pins of the chip. Table 2 lists the Hardware Configuration bytes. The detailed bit descriptions for each byte follows below.

## HW Config. Byte 5: ACDbase Address Length

Mask, Default = 00000000

| wask                                                                                                                                                                       | , Deja | uu = 0 | 100000 | 100 |     |     |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-----|-----|-----|-----|

| D7                                                                                                                                                                         | D6     | D5     | D4     | D3  | D2  | D1  | D0  |

| res                                                                                                                                                                        | res    | res    | res    | res | CM2 | CM1 | CM0 |

| CM2-CM0 Address bit masks for the Alternate<br>CDROM address decode, ACDbase.<br>See the <i>CDROM Interface</i> section<br>for more details on ACDbase                     |        |        |        |     |     |     |     |

| 000 - <u>ACDCS</u> low for 1 byte<br>001 - <u>ACDCS</u> low for 2 bytes<br>011 - <u>ACDCS</u> low for 4 bytes<br>111 - ACDCS low for 8 bytes<br>xxx - all others, RESERVED |        |        |        |     |     |     |     |

| BYTE | Default | Description                                                                                                                                          |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 55h     | E <sup>2</sup> PROM validation byte 1.<br>The first two bytes tell the Crystal Codec that the E <sup>2</sup> PROM exists.                            |

| 2    | BBh     | E <sup>2</sup> PROM validation byte 2                                                                                                                |

| 3    | 00h     | High byte for length of resource data in E <sup>2</sup> PROM                                                                                         |

| 4    | DDh     | Low byte for length of resource data in E <sup>2</sup> PROM                                                                                          |

| 5    | 00h     | Alternate CDROM (Logical Device 4), ACDbase, Address length mask                                                                                     |

| 6    | 03h     | Modem (Logical Device 5), COMbase, Address length mask                                                                                               |

| 7    | 80h     | Misc. Configuration Bits: Interrupt Pin Polarities, Key Disables, VCEN, & LD4 features                                                               |

| 8    | 00h     | Global Configuration Bits: IFM, VCF1 and VCF0, WTEN, SPS                                                                                             |

| 9    | 0Bh     | Code Base Byte - Must be 0x0B                                                                                                                        |

| 10*  | 20h     | RESERVED - Must be 0x20                                                                                                                              |

| 11*  | 04h     | RESERVED - Must be 0x04                                                                                                                              |

| 12*  | 08h     | RESERVED - Must be 0x08                                                                                                                              |

| 13*  | 10h     | RESERVED - Must be 0x10                                                                                                                              |

| 14*  | 80h     | RESERVED - Must be 0x80                                                                                                                              |

| 15*  | 00h     | RESERVED - Must be 0x00                                                                                                                              |

| 16*  | 00h     | RESERVED - Must be 0x00                                                                                                                              |

| 17   | 00h     | External Peripheral Port I/O Decode Address Length 00 = 4 bytes, 08 = 8 bytes 08h causes XCTL0/XA2 pin to change to peripheral port address bit XA2. |

| 18*  | 48h     | RESERVED - Must be 0x48                                                                                                                              |

| 19   | 75h     | IRQ A/B Selection: Lower nibble = A, Upper nibble = B.<br>Along with next two bytes - specify hardware interrupts tied to IRQA-IRQF pins             |

| 20   | B9h     | IRQ C/D Selection: Lower nibble = C, Upper nibble = D.                                                                                               |

| 21   | FCh     | IRQ E/F Selection: Lower nibble = E, Upper nibble = F.                                                                                               |

| 22   | 10h     | DMA A/B Selection: Lower nibble = A, Upper nibble = B.<br>This byte and the next byte - specify hardware DRQ/DACKs tied to the DMAA-DMAC pins        |

| 23   | 03h     | DMA C Selection: Lower nibble = C, Upper nibble = reserved (must be $0$ ).                                                                           |

NOTE: The first four bytes are exclusive to the  $E^2$ PROM and are not used in the Hostload mode. \* Currently not supported. Must be set to default values given in the table.

Table 2. Hardware Configuration Data

| HW Config. | Byte | 6: | COMbase | Address | Length |

|------------|------|----|---------|---------|--------|

|            |      |    |         |         |        |

Mask, Default = 00000011

| -   |     | D5  |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|

| MM7 | MM6 | MM5 | MM4 | MM3 | MM2 | MM1 | MM0 |

- MM7-MM0 Address bit masks for Logical Device 5, typically a modem address, COMbase. See the *Modem Interface* Section for more details on COMbase.

- $\begin{array}{l} 00000000 \underline{MCS} \text{ low for 1 byte} \\ 00000001 \underline{MCS} \text{ low for 2 bytes} \\ 00000011 \underline{MCS} \text{ low for 4 bytes} \\ 00000111 \underline{MCS} \text{ low for 8 bytes} \\ 00001111 \underline{MCS} \text{ low for 16 bytes} \\ 00011111 \underline{MCS} \text{ low for 32 bytes} \\ 00111111 \underline{MCS} \text{ low for 64 bytes} \\ 01111111 \underline{MCS} \text{ low for 128 bytes} \\ 1111111 \underline{MCS} \text{ low for 256 bytes} \\ xxxxxxxx all others, RESERVED \\ \end{array}$

NOTE: The part only buffers the lower three address bits onto the peripheral port. When setting the address decode greater than 8 bytes, the upper address bits should be buffered externally. HW Config. Byte 7: Misc. Configuration Bits,

| Defai | Default = 10000000 |     |     |     |      |     |        |   |

|-------|--------------------|-----|-----|-----|------|-----|--------|---|

| D7    | D6                 | D5  | D4  | D3  | D2   | D1  | D0     |   |

| IHCD  | IHS                | PKD | CKD | IHM | VCEN | SDD | ACDB7D | 1 |

- ACDB7D Alternate CDROM, data Bit 7 Disable. When set, SD7 is held in a high impedance state when reading from ACDbase+1 (only this one address). This bit provides support for IDE alternate base address sharing with the floppy disk controller.

- SDD SD Disable. When set, SD<7:0> are high impedance on reads from any peripheral port address: External synthesis, CDROM or Modem devices. Allows external buffers to bypass the part while still allowing PnP address support. This bit is also internally forced on whenever WTEN or SPS in HW Config. byte 8, or C8, is set.

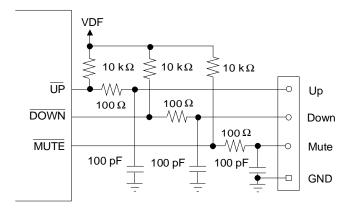

- VCEN Volume <u>Control</u> Enable. When set, the UP, DOWN, and MUTE pins become active and provide a hardware master volume control.

- IHM Interrupt High Modem (LD5). When set, MINT is active high. When clear, MINT is active low.

- CKD Crystal Key disable. When set, blocks the part from receiving the Crystal key. Note that if both CKD and PKD are set, software will be unable to reconfigure the part.

- PKD PnP Key disable. When set, blocks the part from receiving the Plug-and-Play key. Note that if both CKD and PKD are set, software will be unable to reconfigure the part.

- IHS Interrupt High Synthesizer. When set, SINT is active high. When clear, SINT is active low.

- IHCD Interrupt High CDROM. When set, CDINT is active high. When clear, CDINT is active low.

| HW Config. Byte 8: Global Configuration | n Bits, |

|-----------------------------------------|---------|

|-----------------------------------------|---------|

| Default = 00 |                                                                                                                                                 |                                                                                     |                                                                                 |                                                                                       |                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|

| D7 D6        | D5 D4                                                                                                                                           | D3                                                                                  | D2                                                                              | D1                                                                                    | D0                                              |

| IFM VCF1     | VCF0 SLAD                                                                                                                                       | WTEN                                                                                | SPS                                                                             | res                                                                                   | res                                             |

| res          | Must be se<br>ibility with                                                                                                                      |                                                                                     |                                                                                 |                                                                                       | mpat-                                           |

| SPS          | DSP Serial<br>set, switch<br>pins from t<br>XD4-XD1<br>I16 is set,<br>to the DSF<br>this bit is e<br>not be driv<br>to peripher<br>tion is also | es the<br>the sec<br>pins. Th<br>the XD<br>serial<br>enabled<br>ren whe<br>ral port | DSP s<br>ond joy<br>nen, wi<br>4-XD1<br>port pi<br>, the S<br>en acce<br>device | erial po<br>/stick to<br>hen SF<br>pins co<br>ns. On<br>D bus<br>esses co<br>es. This | o the<br>PE in<br>onvert<br>ce<br>will<br>occur |

| WTEN         | WaveTable<br>set, forces<br>to the CS9<br>table Musi<br>pins. Once<br>SD bus wi<br>cesses oco<br>devices. T<br>able in C8                       | XD7-X<br>236 Sin<br>c Synth<br>e this bi<br>ll not be<br>cur to p<br>his fund       | D5 pin<br>ngle-C<br>nesizer<br>t is ena<br>e drive<br>periphe                   | hip Wa<br>serial<br>abled, t<br>n wher<br>ral port                                    | onvert<br>ve-<br>port<br>the<br>a ac-           |

| SLAD         | Soundblas<br>When clea<br>Synthesize<br>the LINE A<br>When set,<br>changes d<br>ters.                                                           | ir, Sour<br>er Volur<br>Alternati<br>SB Syl                                         | nd Blas<br>ne cha<br>e (X0/)<br>nthesiz                                         | ter (SE<br>nges a<br>(1) volu<br>er Volu                                              | 3)<br>ffect<br>ume.<br>ume                      |

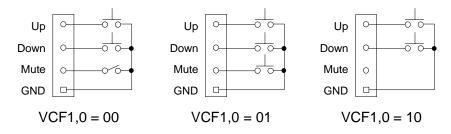

| VCF1,0       | Hardware<br>These bits<br><u>hardware</u><br>DOWN, ar<br>trol is enal<br>the previou<br>byte.                                                   | contro<br>vol <u>ume</u><br>nd MUT<br>pled by                                       | l the fo<br><u>c</u> ontro<br>E. The<br>setting                                 | ormat o<br>I pins l<br>volum<br>VCEN                                                  | <u>f th</u> e<br>JP,<br>ie con-<br>I in         |

|              |                                                                                                                                                 |                                                                                     |                                                                                 |                                                                                       |                                                 |

- MUTE is low, the volume is muted. 01 - MUTE is a momentary switch. MUTE toggles between mute and

- MUTE toggles between mute and un-mute. Pressing the up or down switch always un-mutes.

- 10 MUTE is not used. Two button volume control. Pressing the up and down buttons simultaneously causes the volume to mute. Pressing up or down un-mutes.

- 11 <u>- UP pin is not used. The</u> MUTE pin functions as the Up function. With this exception, this mode functions similarly to the pervious two-button mode. This mode provides backwards compatibility with the CS4236.