PREPARED BY: DATE

S. Sadamils .. Dec. 8. 2009

APPROVED BY: DATE

7 J. Mahmuchi Dec 8. 2009

CO

# SHARP

MOBILE LIQUID CRYSTAL

DISPLAY GROUP

SHARP CORPORATION

SPECIFICATION

| SPEC No. | LCY-09033B   |

|----------|--------------|

| FILE No. |              |

| ISSUE:   | Dec. 8. 2009 |

| PAGE:    | 44 pages     |

MOBILE LIQUID CRYSTAL DISPLAY DIVISION II

# DEVICE SPECIFICATION FOR

# Control IC of TFT-LCD

Type No. LQ0DZC2291

| CUSTOMER'S APPROVAL |                                                                                                                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATE                |                                                                                                                                                                                            |

| <u>BY</u>           | PRESENTED  BY TAKAAKI IEMOTO Department Assistant General manager Engineering Department 3 Mobile Liquid Crystal Display Division II Mobile Liquid Crystal Display Group SHARP CORPORATION |

# RECORDS OF REVISION

Type No: LQ0DZC2291

| SPEC No.   | Date        | NO. | PAGE | SUMMARY                                   | NOTE                  |

|------------|-------------|-----|------|-------------------------------------------|-----------------------|

| LCY-09033A | 2009. 06.05 |     | -    | -                                         | 1st Issue             |

| LCY09033B  | 2009.12.8   |     | 22   | Connection of terminal STHR/STHL and LCD. | 2 <sup>nd</sup> Issue |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

|            |             |     |      |                                           |                       |

Note: In this ASIC Specification, binary notation, decimal notation and hexadecimal notation are described according to the rules below.

Binary notation: Double quotation marks are used, e.g., "111000" or "1001". Otherwise, 'b' is appended, e.g., 111000b.

Hexadecimal notation: '0x' is used, e.g., 0x3F or 0x2D. Otherwise, 'H' is appended, e.g., 20H or 1000H. Decimal notation: Unless binary notation and hexadecimal notation are used, decimal notation is used.

#### - CONTENTS -

| <ol> <li>Over\</li> </ol> | view and Features of Product                                       | 3  |

|---------------------------|--------------------------------------------------------------------|----|

| 1.1.                      | Product Overview                                                   | 3  |

| 1.2.                      | Main Features                                                      | 3  |

| 1.3.                      | Block diagram                                                      | 3  |

| 2. Pin D                  | escription                                                         | 5  |

| 2.1.                      | Pin Layout                                                         | 5  |

| 2.2.                      | Pin Settings                                                       | 7  |

| 3. Absolute               | e Maximum Ratings                                                  | 8  |

| 4. Electrica              | al Specification                                                   | 8  |

| 4.1. Rec                  | ommended Operating Range                                           | 8  |

| 4.2. DC                   | Electrical Specification                                           | 9  |

| 4.3. AC I                 | Electrical Specification                                           | 9  |

|                           | - Map                                                              |    |

| 6. Cond                   | itions for Input Signal                                            | 11 |

| 6.1.                      | Conditions for Image Signal Input                                  |    |

| 6.2.                      | Horizontal timing 1 HENAB = Active input                           |    |

| 6.3.                      | Horizontal timing 2 HENAB = Fixed to Lo                            |    |

| 6.4.                      | Vertical timing 1 HENAB = Active input                             |    |

| 6.5.                      | Vertical timing 2 HENAB = Fixed to Lo                              |    |

| 6.6.                      | Horizontal/Vertical Data Capture Position                          |    |

| 7. Serial                 | I Input Conditions (I2C)                                           |    |

| 7.1.                      | Protocol                                                           |    |

| 7.2.                      | Serial Interface AC Characteristics                                | 16 |

| 7.3.                      | Instruction to Write/Read to/from ASIC                             |    |

| 8. Desci                  | ription of Function and Supported Register                         |    |

| 8.1.                      | Outline of Loading                                                 |    |

| 8.2.                      | Description of Register Regarding Loading                          |    |

| 9. Powe                   | r ON Sequence                                                      |    |

|                           | ormat                                                              |    |

|                           | Run Display                                                        |    |

| 11.1.                     | Overview of FreeRun Display                                        | 21 |

| 11.2.                     | Conditions for Transition to FreeRun                               |    |

| 11.3.                     | Conditions for Recovery from FreeRun                               |    |

| 12. Horiz                 | ontal/Vertical Reverse Display                                     |    |

|                           | Independent Gamma Correction                                       |    |

| 13.1.                     | Overview of RGB Independent Gamma Correction                       |    |

| 13.2.                     | Description of Register Regarding RGB Independent Gamma Correction |    |

| 13.3.                     | Flow of Use of Independent Gamma Function                          |    |

| 14. EEPF                  | ROM                                                                |    |

| 14.1.                     | EEPROM                                                             | 24 |

| 14.2.                     | Recommended EEPROM                                                 |    |

| 14.3.                     | Description of Register Regarding EEPROM                           |    |

| 14.4.                     | How to Write/Read to/from EEPROM                                   |    |

| 14.5.                     | ROM_Map of EEPROM                                                  |    |

|                           | rol of D/A Converter (hereinafter referred to as "DAC")            |    |

| 15.1.                     |                                                                    |    |

| 15.2.        | Recommended Component for DAC                                      | 26 |

|--------------|--------------------------------------------------------------------|----|

| 15.3.        | Description of Register Regarding DAC Control                      | 26 |

| 15.4.        | Actual Usage                                                       | 27 |

| 16. Contro   | ol of A/D Converter (hereinafter referred to as "ADC")             | 28 |

| 16.1.        | Overview of ADC Control                                            | 28 |

| 16.2.        | Recommended Component for ADC                                      | 28 |

| 17. Output   | t I/F to LCD                                                       | 29 |

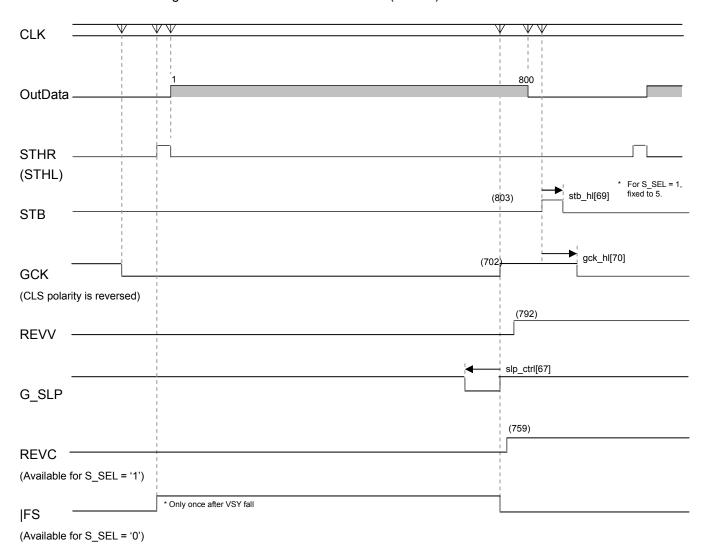

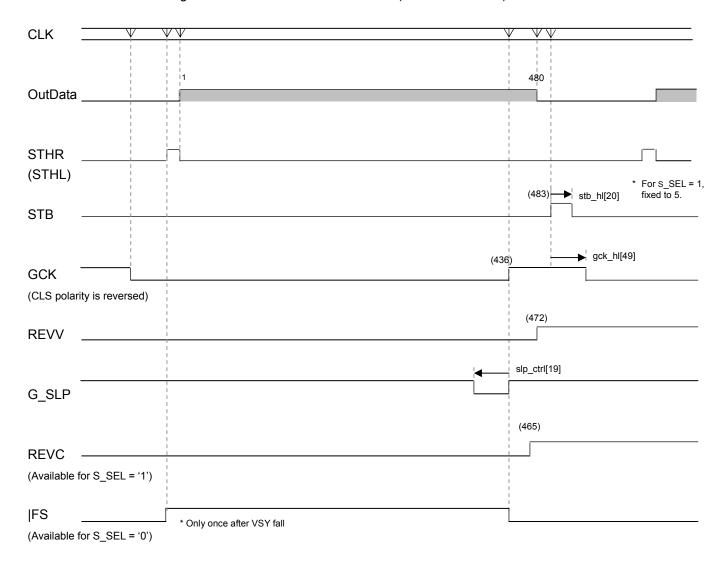

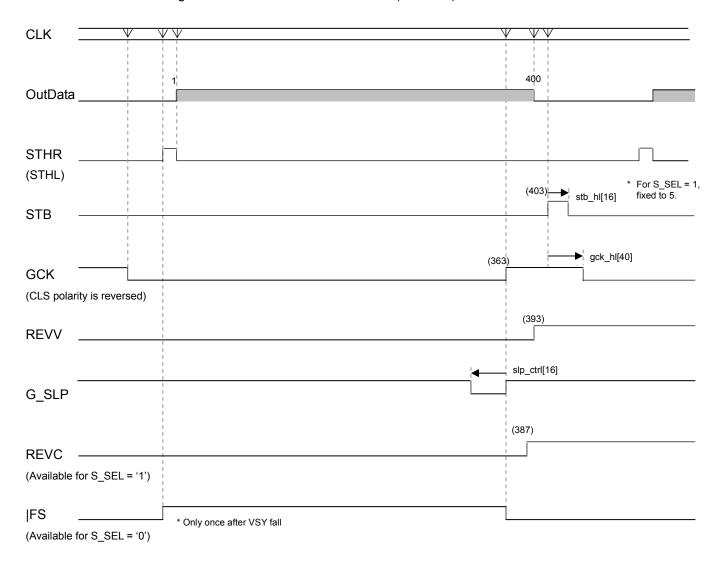

| 17.1.        | Example of Horizontal Timing                                       | 29 |

| 17.1.1.      | Horizontal Timing for Horizontal Resolution 800 Dots (WVGA)        | 29 |

| 17.1.2.      | Horizontal Timing for Horizontal Resolution 480 Dots (WEGA1/WEGA2) | 30 |

| 17.1.3.      | Horizontal Timing for Horizontal Resolution 400 Dots (WQVGA)       | 31 |

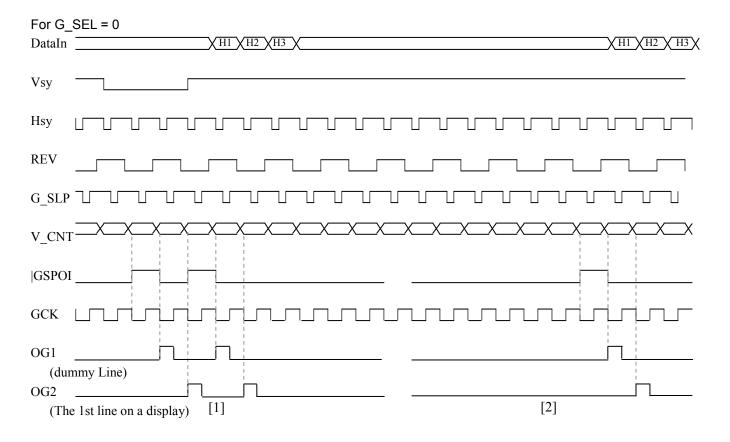

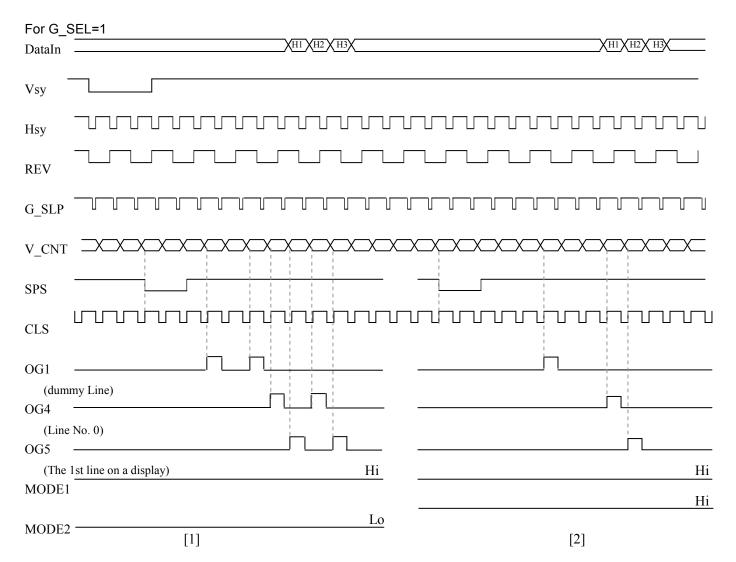

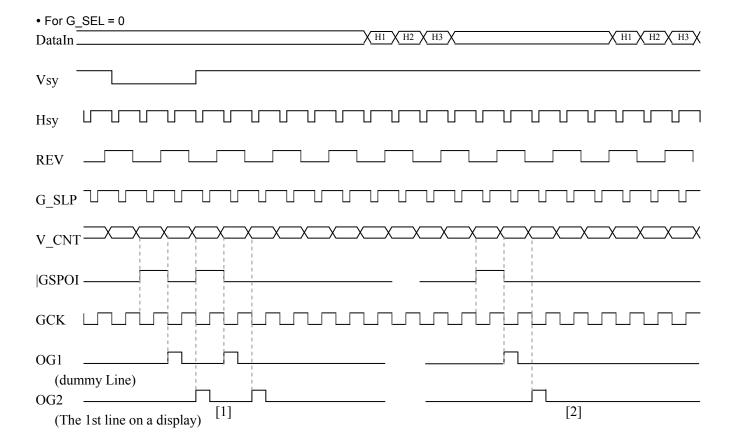

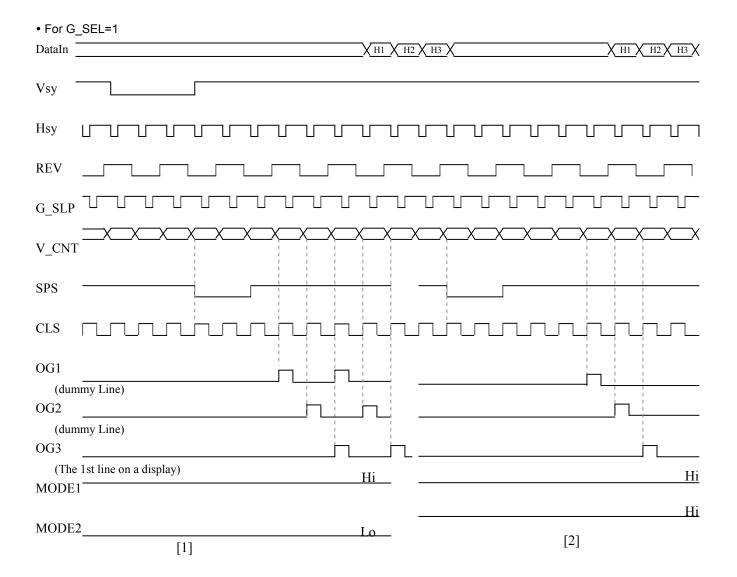

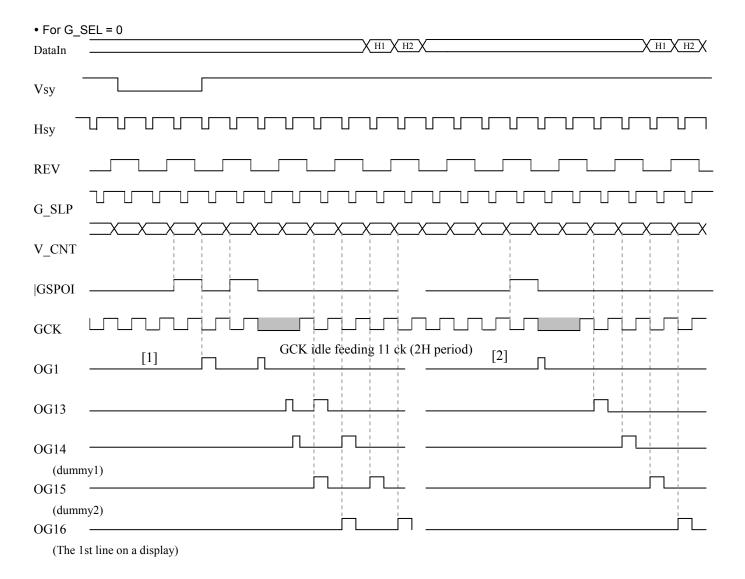

| 17.2.        | Example of Vertical Timing                                         | 32 |

| 17.2.1.      | Vertical Timing for Vertical Resolution 480 Lines (WVGA)           | 32 |

| 17.2.2.      | Vertical Timing for Vertical Resolution 240 Lines (WQVGA/WEGA2)    | 34 |

| 17.2.3.      | Vertical Timing for Vertical Resolution 272 Lines (WEGA1)          | 36 |

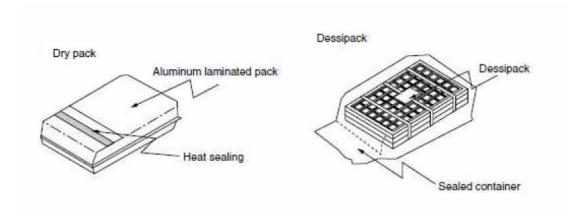

| 18. Cautions | s on storage                                                       | 37 |

| 18.1. Stor   | age environment                                                    | 37 |

| 18.2. Stor   | age methods                                                        | 37 |

| 18.3. Lon    | g-term storage                                                     | 37 |

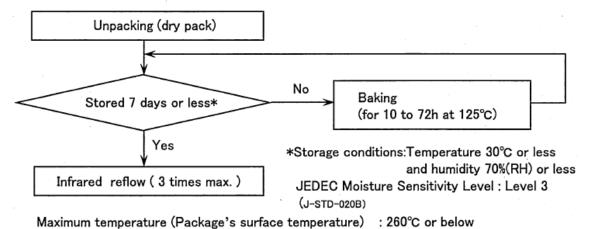

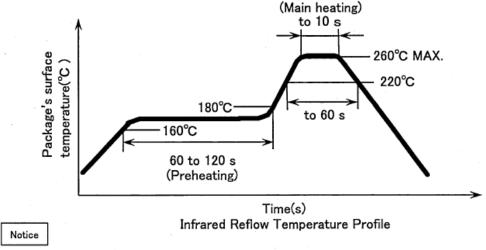

| 19. Recomn   | nended soldering condition of infrared reflow                      | 39 |

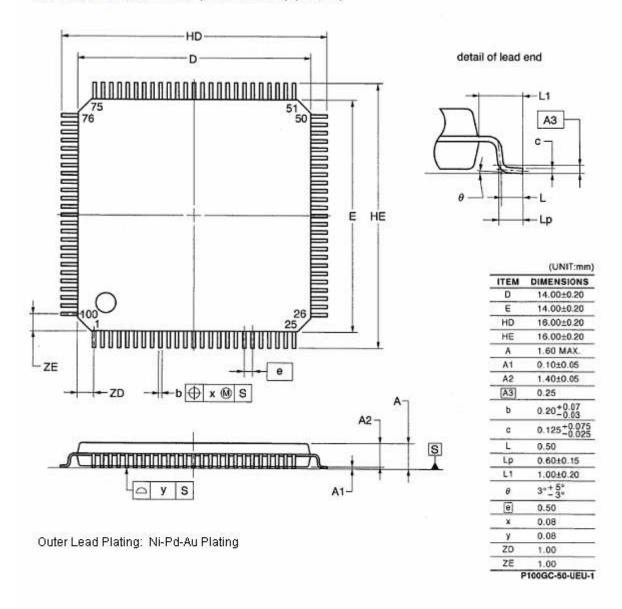

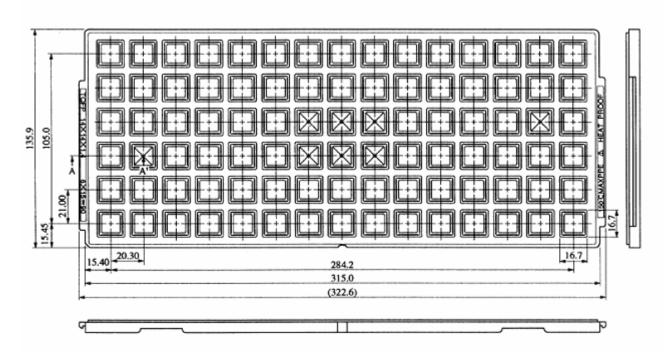

| 20. Outline  | drawings                                                           | 40 |

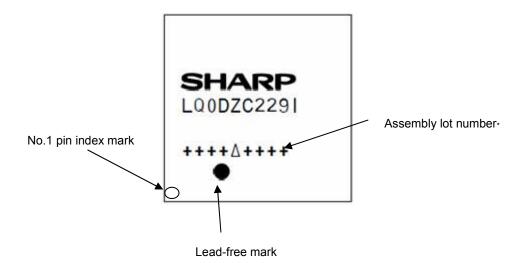

| 21. Marking  |                                                                    | 41 |

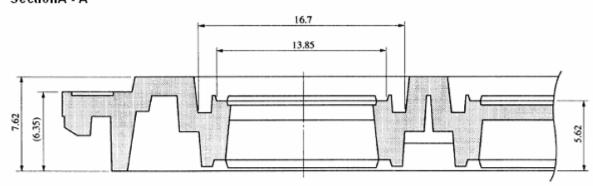

| 22. Tray cor | ntainer                                                            | 42 |

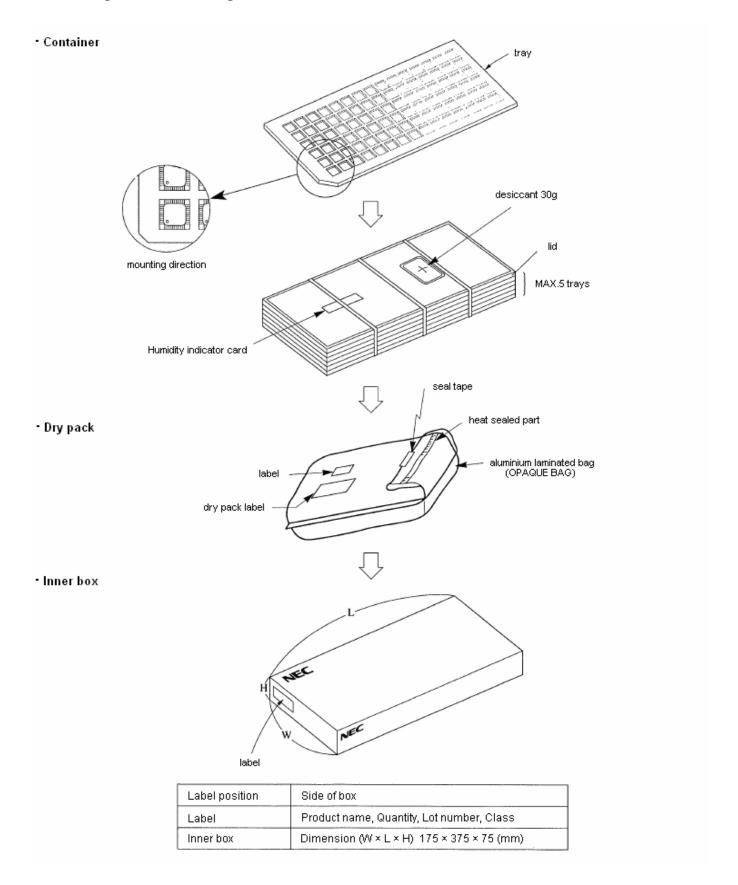

| 23.Packing   | outline drawing                                                    | 43 |

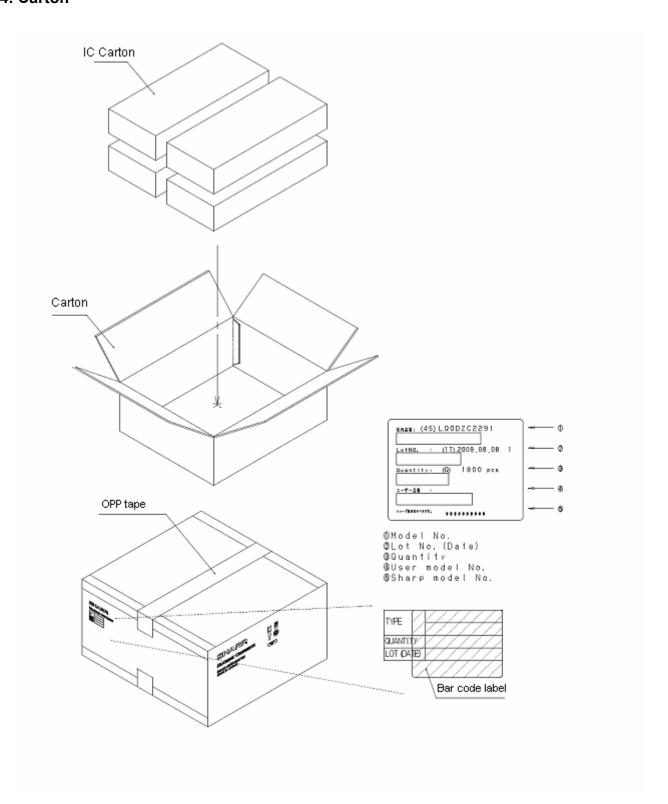

| 24 Carton    |                                                                    | 11 |

#### 1. Overview and Features of Product

#### 1.1. Product Overview

This product is a timing controller for liquid crystal module to display four kinds of resolutions, i.e., WVGA ( $800RGB[H] \times 480[V]$ , WQVGA ( $400RGB[H] \times 240[V]$ ), WEGA1 ( $480RGB[H] \times 272[V]$ ) and WEGA2 ( $480RGB[H] \times 240[V]$ ). Moreover, RGB independent gamma can be controlled by adding external EEPROM. This controller has an auto-loading function. After resetting, the controller reads the register set values/independent gamma parameters from the external EEPROM and works according to the set values.

#### 1.2. Main Features

- a) Timing controller (for WVGA, WQVGA, WEGA1 and WEGA2) contained

- b) ROMOFF setting (It can be specified whether external EEPROM should be disabled or enabled.)

- c) HSY/VSY input monitoring function. ("Free Run" is shown when HSY/VSY has not yet been input and when an error has been occurred in input.)

- d) Free Run Display (Blue background screen 1H = 1200 clk or more/1V = 700 Lines or more)

- e) Horizontal/vertical reverse display available.

- f) Independent gamma setting (supported only for ROMOFF = 0)

- g) External D/A Converter 8ch control output supported (only for ROMOFF = 0)

- h) External A/D Converter 2ch control output supported (only for ROMOFF = 0)

- i) Internal register control with I2C (only for ROMOFF = 0)

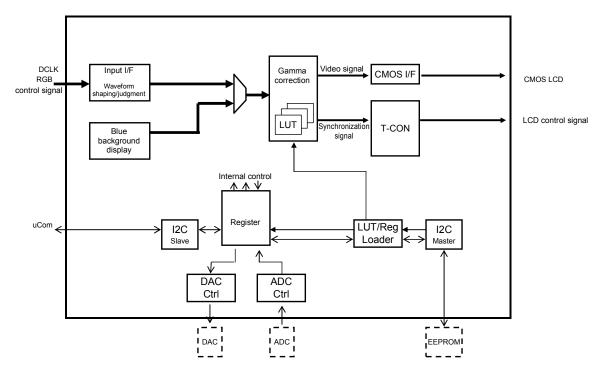

#### 1.3. Block diagram

Figure 1-1 shows a simplified block diagram of LQ0DZC2291.

Figure 1-1: Simplified Block Diagram of LQ0DZC2291

Overview of block diagram is described below.

#### (1) Input I/F

Receives 18-bit parallel data input externally and passes it to the image processing block stated below. Waveform shaping (Hsy/Vsy phase difference absorption), pulse noise elimination (pulse of 2 clk or less) from control signal and synchronization signal input judgment are performed here.

#### (2) Blue background display

A block to generate the blue background display when Input I/F of (1) has judged that there is no synchronization signal input.

#### (3) Gamma correction

The gamma correction function allows to process input video data per RGB data and adjust the gamma curve per R, G and B. (This is available only for ROMOFF = '0'.)

#### (4) T-CON

A block of timing controller to drive a panel of four kinds of resolutions, i.e., WVGA, WQVGA, WEGA1 and WEGA2.

#### (5) LUT/Reg\_Loader

A block to read a data from the external EEPROM, which is connected to have an initial value of an ASIC's internal register and internal LUT, and to update the data for the register and LUT.

#### (6) DAC Ctrl

External D/C converter can be connected and controlled to set up the liquid crystal display gradation and specify the COM signal. In this block, a control signal to DAC is generated to control DAC.

#### (7) ADC Ctrl

External A/D converter can be connected and controlled. This block receives a signal from ADC and stores a data in the internal register of ASIC. Thermistor and photo sensor can be connected and monitored, by way of example.

# 2. Pin Description

# 2.1. Pin Layout

Table 2-1 describes all the pins.

Table 2-1: Pin Description

| Table 2-1: Pin Description           |          |                                               |                             |                                                               |                                  |  |  |

|--------------------------------------|----------|-----------------------------------------------|-----------------------------|---------------------------------------------------------------|----------------------------------|--|--|

| PIN No. I/O Attribute Pin Name Power |          |                                               | _                           | Description of Function                                       | Operation when it is not be used |  |  |

| 1                                    | _        | VDD                                           |                             |                                                               |                                  |  |  |

| 2                                    | - 1      | IG0                                           |                             | Green data input pin (LSB)                                    |                                  |  |  |

| 3                                    | I        | IG1                                           |                             | Green data input pin                                          |                                  |  |  |

| 4                                    | I        | IG2                                           |                             | Green data input pin                                          |                                  |  |  |

| 5                                    | I        | IG3                                           |                             | Green data input pin                                          |                                  |  |  |

| 6                                    | I        | IG4                                           |                             | Green data input pin                                          |                                  |  |  |

| 7                                    | I        | IG5                                           |                             | Green data input pin (MSB)                                    |                                  |  |  |

| 8                                    | I        | IB0                                           |                             | Blue data input pin (LSB)                                     |                                  |  |  |

| 9                                    | I        | IB1                                           |                             | Blue data input pin                                           |                                  |  |  |

| 10                                   | _        | IB2                                           |                             | Blue data input pin                                           |                                  |  |  |

| 11                                   | _        | IB3                                           |                             | Blue data input pin                                           |                                  |  |  |

| 12                                   | _        | IB4                                           |                             | Blue data input pin                                           |                                  |  |  |

| 13                                   | _        | IB5                                           |                             | Blue data input pin (MSB)                                     |                                  |  |  |

| 14                                   | ld       | ROMOFF                                        |                             | Setting whether external EEPROM should be disabled or enabled |                                  |  |  |

| 15                                   | lu       | VRVC                                          |                             | Vertical scan reversal                                        |                                  |  |  |

| 16                                   | lu       | HRVC                                          |                             | Horizontal scan reversal                                      |                                  |  |  |

| 17                                   | ld       | SMC                                           |                             | ASIC test pin                                                 | OPEN/GND                         |  |  |

| 18                                   | ld       | GMDSEL                                        |                             | Gate start pulse output setting                               |                                  |  |  |

| 19                                   | 0        | SOUT                                          |                             | ASIC test pin                                                 | OPEN                             |  |  |

| 20                                   | 1        | TMC                                           |                             | ASIC test pin                                                 | OPEN/GND                         |  |  |

| 21                                   |          |                                               | OPEN/GND                    |                                                               |                                  |  |  |

| 22                                   | lu       | VSY Vertical synchronization signal input pin |                             |                                                               |                                  |  |  |

| 23                                   | ld       | HENAB                                         | , , , , , ,                 |                                                               |                                  |  |  |

| 24                                   | lu       | HSY                                           |                             | Horizontal synchronization signal input pin                   |                                  |  |  |

| 25                                   | _        | VDD                                           |                             |                                                               |                                  |  |  |

| 26                                   | _        | GND                                           |                             |                                                               |                                  |  |  |

| 27                                   | ı        | DCLK                                          |                             | Clock input pin                                               |                                  |  |  |

| 28                                   | _        | GND                                           |                             |                                                               |                                  |  |  |

| 29                                   | lsu      | FRESET                                        |                             | ASIC reset pin                                                |                                  |  |  |

| 30                                   | -        | VDD                                           |                             | , tere recet p                                                |                                  |  |  |

| 31                                   | ld       | S SEL                                         |                             | Source driver setting pin                                     |                                  |  |  |

| 32                                   | Id       | G SEL                                         |                             | Gate driver setting pin                                       |                                  |  |  |

| 33                                   | Id       | DSEL1                                         |                             | Resolution setting pin 1                                      |                                  |  |  |

| 34                                   | Id       | DSEL2                                         |                             | Resolution setting pin 2                                      |                                  |  |  |

| 35                                   | Id       | TEST1                                         |                             | ASIC test pin                                                 | GND                              |  |  |

| 36                                   | _        | GND                                           |                             |                                                               |                                  |  |  |

| 37                                   | lou      | SERDIO                                        | 3mA                         | Serial data I/O pin                                           | OPEN                             |  |  |

| 38                                   | lu       | SERCK                                         | J.11// 1                    | Serial clock input pin                                        | OPEN/VDD                         |  |  |

| 39                                   | 0        | ADCCK                                         | 3mA                         | ADC clock output pin                                          | OPEN                             |  |  |

| 40                                   | 0        | ADCCS                                         | 3mA                         | ADC chip select output pin                                    | OPEN                             |  |  |

| 41                                   |          |                                               | ADC control data output pin | OPEN                                                          |                                  |  |  |

| 42                                   | _        | · · ·                                         |                             | ADC data input pin                                            | OPEN/VDD                         |  |  |

| 43                                   | 0        | DACDI                                         | ···                         |                                                               | OPEN                             |  |  |

| 44                                   | <u> </u> |                                               | DAC load output pin         | OPEN                                                          |                                  |  |  |

| 45                                   | lOu      | DACCK                                         | 3mA                         | DAC clock output pin                                          | OPEN                             |  |  |

| 46                                   | -<br>-   | GND                                           | O111/ (                     | Dr. to diodit output pin                                      | OI LIT                           |  |  |

| 47                                   | 0        | ROMCK                                         | 3mA                         | EEPROM clock output pin                                       | OPEN                             |  |  |

| 48                                   | 0        | ROMWC                                         | 3mA                         | EEPROM write protect output pin                               | OPEN                             |  |  |

| 49                                   | lOu      | ROMDIO                                        | 3mA                         | EEPROM data I/O pin                                           | OPEN                             |  |  |

| 50                                   | -<br>-   | GND                                           | JIIIA                       | LEI ROM data 1/0 pin                                          | OI LIN                           |  |  |

| PIN No. | I/O<br>Attribute | Pin Name   | Drive<br>Power | Description of Function                               | Operation when it is not be used |

|---------|------------------|------------|----------------|-------------------------------------------------------|----------------------------------|

| 51      | - VDD            |            |                |                                                       |                                  |

| 52      | O OR0            |            | 6mA            | Red data output pin (LSB)                             |                                  |

| 53      | 0                | OR1        | 6mA            | Red data output pin                                   |                                  |

| 54      | 0                | OR2        | 6mA            | Red data output pin                                   |                                  |

| 55      | 0                | OR3        | 6mA            | Red data output pin                                   |                                  |

| 56      | 0                | OR4        | 6mA            | Red data output pin                                   |                                  |

| 57      | 0                | OR5        | 6mA            | Red data output pin (MSB)                             |                                  |

| 58      | _                | GND        |                |                                                       |                                  |

| 59      | 0                | OG0        | 6mA            | Green data output pin (LSB)                           |                                  |

| 60      | 0                | OG1        | 6mA            | Green data output pin                                 |                                  |

| 61      | 0                | OG2        | 6mA            | Green data output pin                                 |                                  |

| 62      | 0                | OG3        | 6mA            | Green data output pin                                 |                                  |

| 63      | 0                | OG4        | 6mA            | Green data output pin                                 |                                  |

| 64      | 0                | OG5        | 6mA            | Green data output pin (MSB)                           |                                  |

| 65      | _                | VDD        |                |                                                       |                                  |

| 66      | 0                | OB0        | 6mA            | Blue data output pin (LSB)                            |                                  |

| 67      | 0                | OB1        | 6mA            | Blue data output pin                                  |                                  |

| 68      | 0                | OB2        | 6mA            | Blue data output pin                                  |                                  |

| 69      | 0                | OB3        | 6mA            | Blue data output pin                                  |                                  |

| 70      | 0                | OB4        | 6mA            | Blue data output pin                                  |                                  |

| 71      | 0                | OB5        | 6mA            | Blue data output pin (MSB)                            |                                  |

| 72      | _                | GND        |                |                                                       |                                  |

| 73      | Ю                | STHR       | 6mA            | * <sup>1</sup> Start pulse I/O signal                 |                                  |

| 74      | Ю                | STHL       | 6mA            | * <sup>1</sup> Start pulse I/O signal                 |                                  |

| 75      | _                | VDD        |                |                                                       |                                  |

| 76      | _                | GND        |                |                                                       |                                  |

| 77      | 0                | CLK        | 12mA           | Source driver sampling clock                          |                                  |

| 78      | _                | GND        |                |                                                       |                                  |

| 79      | 0                | STB        | 6mA            | Source driver latch pulse output                      |                                  |

| 80      | 0                | REV        | 6mA            | Source driver polarity reversal control output        |                                  |

| 81      | 0                | FS REVO    | 6mA            | * Offset cancel / COM polarity reversal signal output |                                  |

| 82      | 0                | LBR        | 3mA            | Source driver horizontal reversal control output      |                                  |

| 83      | Ю                | GSPOI MODE | 2 3mA          | * Gate start pulse / Gate mode setting pin            |                                  |

| 84      | 0                | R/L        | 3mA            | Gate driver vertical reversal control output          |                                  |

| 85      | Ю                | GSPIO SPS  | 3mA            | * Gate start pulse                                    |                                  |

| 86      | 0                | GOE MODE   | 1 3mA          | * Gate driver control output                          |                                  |

| 87      | 0                | GCK CLS    | 3mA            | * Gate driver shift clock                             |                                  |

| 88      | I                | TEB        |                | ASIC test pin                                         | VDD                              |

| 89      | ld               | TEST2      |                | ASIC test pin                                         | GND                              |

| 90      |                  |            | 3mA            | Full gate output ON setting output                    | OPEN                             |

| 91      |                  |            | 3mA            | Power supply circuit control output                   |                                  |

| 92      | 92 O G_SLP       |            | 3mA            | Gate slope control pin                                | OPEN                             |

| 93      |                  |            |                |                                                       |                                  |

| 94      | 4 I IR0          |            |                | Red data input pin (LSB)                              |                                  |

| 95      | I                | I IR1      |                | Red data input pin                                    |                                  |

| 96      | I                | IR2        |                | Red data input pin                                    |                                  |

| 97      | I                | IR3        |                | Red data input pin                                    |                                  |

| 98      | ĺ                | IR4        |                | Red data input pin                                    |                                  |

| 99      | I                | IR5        |                | Red data input pin (MSB)                              |                                  |

| 100     | _                | GND        |                |                                                       |                                  |

I: Input pin O: Output pin IO: I/O pin d: Pull-down for input pin u: Pull-up for input pin su: Schmitt input pin

<sup>\* &</sup>lt;sup>1</sup> Table 12-3 on page 22.

<sup>\*2</sup> Refer to Table 2-2 on page 10.

# 2.2. Pin Settings

Table 2-2 describes the pin settings.

Table 2-2: Pin Settings

| Pin name   | Function                                                                                                                               |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0 051 (*)  | Source setting pin                                                                                                                     |  |  |  |  |  |  |

| S_SEL (*)  | For how to set this pin, ask the person in charge of Sharp Corporation.                                                                |  |  |  |  |  |  |

| 0.051.7*   | Gate setting pin                                                                                                                       |  |  |  |  |  |  |

| G_SEL (*)  | For how to set this pin, ask the person in charge of Sharp Corporation.                                                                |  |  |  |  |  |  |

| VDVC       | Gate driver scan direction setting                                                                                                     |  |  |  |  |  |  |

| VRVC       | Refer to Chapter 11 "Horizontal/Vertical Reverse Display".                                                                             |  |  |  |  |  |  |

| HRVC       | Source driver scan direction setting                                                                                                   |  |  |  |  |  |  |

| HRVC       | Refer to Chapter 11 "Horizontal/Vertical Reverse Display".                                                                             |  |  |  |  |  |  |

|            | Gate start pulse output setting                                                                                                        |  |  |  |  |  |  |

| GMDSEL     | Lo: Normal mode                                                                                                                        |  |  |  |  |  |  |

|            | Hi: Interlacing two-pulse mode                                                                                                         |  |  |  |  |  |  |

| D_SEL1 (*) | Input resolution switch setting pin  Resolution D_SEL1 D_SEL2                                                                          |  |  |  |  |  |  |

|            | WVGA 0 0                                                                                                                               |  |  |  |  |  |  |

|            | WQVGA 1 0                                                                                                                              |  |  |  |  |  |  |

| D_SEL2 (*) | WEGA1 0 1                                                                                                                              |  |  |  |  |  |  |

|            | WEGA2 1 1                                                                                                                              |  |  |  |  |  |  |

| ROMOFF (*) | EEPROM setting pin  Lo: EEPEOM is enabled.  Hi: EEPEOM is disabled.                                                                    |  |  |  |  |  |  |

|            | If ROMOFF is set to '1', this ASIC is used as a timing controller. Therefore, register control, DAC control, etc. cannot be performed. |  |  |  |  |  |  |

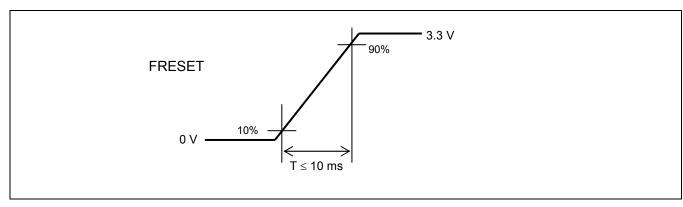

|            | Reset pin (Lo-Active)                                                                                                                  |  |  |  |  |  |  |

| FRESET     | * Time constant shall be 10 ms or less. Refer Figure 2-1.                                                                              |  |  |  |  |  |  |

Do not change any setting of pins marked with \*, after the ASIC power supply turns ON.

Figure 2-1 FREST Time Constant

# 3. Absolute Maximum Ratings

Table 3-1: Absolute Maximum Ratings

| Parameter             | Symbol           | Rating       | Unit |

|-----------------------|------------------|--------------|------|

| Supply voltage        | $V_{DD}$         | -0.5 to +4.6 | V    |

| Input voltage         | Vı               | -0.5 to +4.6 | V    |

| Output voltage        | Vo               | -0.5 to +4.6 | V    |

| Operating temperature | T <sub>A</sub>   | -40 to +85   | °C   |

| Storage temperature   | T <sub>stg</sub> | -65 to +150  | °C   |

# 4. Electrical Specification

# 4.1. Recommended Operating Range

Table 4-1: Recommended Operating Range

| Parameter                | Symbol          | Condition      | Min. | Тур. | Max.     | Unit |

|--------------------------|-----------------|----------------|------|------|----------|------|

| Supply voltage*1         | $V_{DD}$        |                | 2.7  | 3.15 | 3.6      | V    |

| Ambient temperature      | T <sub>A</sub>  |                | -40  |      | 85       | °C   |

| Input voltage, high*1    | V <sub>IH</sub> |                | 2.00 |      | $V_{DD}$ | V    |

| Input voltage, low* 1    | V <sub>IL</sub> |                | 0    |      | 0.8      | V    |

| Positive trigger voltage | $V_P$           |                | 1.4  |      | 2.4      | V    |

| Negative trigger voltage | $V_N$           | Schmitt Buffer | 0.8  |      | 1.6      | V    |

| Hysteresis voltage       | V <sub>H</sub>  |                | 0.3  |      | 1.5      | V    |

| Input rise time          | t <sub>ri</sub> |                | 0    |      | 200      | ns   |

| Input fall time          | t <sub>fi</sub> |                | 0    |      | 200      | ns   |

| Input rise time          | t <sub>ri</sub> | 0.1            | 0    |      | 10       | ms   |

| Input fall time          | t <sub>fi</sub> | Schmitt Buffer | 0    |      | 10       | ms   |

<sup>\*</sup> The following Supply voltage conditions operate.

# Condition1

| Parameter           | Symbol          | Min.               | Тур. | Max.        | Unit |  |  |  |

|---------------------|-----------------|--------------------|------|-------------|------|--|--|--|

| Supply voltage      | $V_{DD}$        | 3.0                |      | 3.6         | V    |  |  |  |

| Input voltage, high | V <sub>IH</sub> | 0.7V <sub>DD</sub> |      | $V_{DD}$    | V    |  |  |  |

| Input voltage, low  | V <sub>IL</sub> | 0                  |      | $0.3V_{DD}$ | V    |  |  |  |

# Condition2

| Parameter           | Symbol          | Min.                | Тур. | Max.                | Unit |

|---------------------|-----------------|---------------------|------|---------------------|------|

| Supply voltage      | $V_{DD}$        | 2.7                 |      | 3.0                 | V    |

| Input voltage, high | V <sub>IH</sub> | 0.75V <sub>DD</sub> |      | $V_{DD}$            | V    |

| Input voltage, low  | $V_{IL}$        | 0                   |      | 0.25V <sub>DD</sub> | V    |

# 4.2. DC Electrical Specification

Table 4-2: DC Electrical Specification

| Parameter                          | Symbol           | Condition                                          | Min.  | Тур. | Max.  | Unit |

|------------------------------------|------------------|----------------------------------------------------|-------|------|-------|------|

| Static current consumption         | I <sub>DDS</sub> | V <sub>I</sub> =V <sub>DD</sub> or GND             |       |      | 300   | μΑ   |

| Off-state output current           | l <sub>oz</sub>  | V <sub>0</sub> =V <sub>DD</sub> or GND             |       |      | ±10   | μΑ   |

| Output short-circuit current       | Ios              | V <sub>0</sub> =GND                                |       |      | -250  | mA   |

| Input leakage current              | I <sub>I</sub>   | V <sub>I</sub> =V <sub>DD</sub> or GND             |       |      | ±1.0  | μΑ   |

|                                    | I <sub>I</sub>   | V <sub>I</sub> =GND (pull-up 50kΩ)                 | -28   | -83  | -190  | μΑ   |

|                                    | II               | $V_I=V_{DD}$ (pull-down 50k $\Omega$ )             | 28    | 83   | 190   | μΑ   |

| Pull-up resistor (50k $\Omega$ )   | R <sub>PU</sub>  | V <sub>I</sub> =GND                                | 18.9  | 39.8 | 107.1 | kΩ   |

| Pull-down resistor (50k $\Omega$ ) | R <sub>PD</sub>  | V <sub>I</sub> =V <sub>DD</sub>                    | 18.9  | 39.8 | 107.1 | kΩ   |

| Output current,low                 | I <sub>OL</sub>  | V <sub>OL</sub> =0.4V (I <sub>OL</sub> =3mA type)  | 3.0   |      |       | mA   |

|                                    |                  | V <sub>OL</sub> =0.4V (I <sub>OL</sub> =6mA type)  | 6.0   |      |       | mA   |

|                                    |                  | V <sub>OL</sub> =0.4V (I <sub>OL</sub> =12mA type) | 12.0  |      |       | mA   |

| Output current,high                | I <sub>OH</sub>  | V <sub>OH</sub> =2.4V (I <sub>OL</sub> =3mA type)  | -3.0  |      |       | mA   |

|                                    |                  | V <sub>OH</sub> =2.4V (I <sub>OL</sub> =6mA type)  | -6.0  |      |       | mA   |

|                                    |                  | V <sub>OH</sub> =2.4V (I <sub>OL</sub> =12mA type) | -12.0 |      |       | mA   |

# 4.3. AC Electrical Specification

Table 4-3: AC Electrical Specification

| Parameter        | Symbol         | Condition                          | Min. | Тур. | Max. | Unit |

|------------------|----------------|------------------------------------|------|------|------|------|

| Output rise time | t <sub>r</sub> | Output buffer C <sub>L</sub> =15pF | 2    |      | 10   | ps   |

| Output fall time | t <sub>r</sub> | Output buffer C <sub>L</sub> =15pF | 2    |      | 10   | ps   |

# 5. Register Map

Table 5-1 shows the register map list of LQ0DZC2291.

Table 5-1: Register Map List

|             |         |           |      |      | Table 5-1. R | egister Map L | ISt   |        |         |               |

|-------------|---------|-----------|------|------|--------------|---------------|-------|--------|---------|---------------|

|             | address | bit7      | bit6 | bit5 | bit4         | bit3          | bit2  | bit1   | bit0    | Initial value |

| *           | 00h     |           |      |      | da_0d        | h[7:0]        |       |        |         | 0000_0000b    |

| *           | 01h     |           |      |      | da_1d        | h[7:0]        |       |        |         | 0000_0000b    |

| *           | 02h     |           |      |      | da_2c        | h[7:0]        |       |        |         | 0000_0000b    |

| *           | 03h     |           |      |      | da_3d        | h[7:0]        |       |        |         | 0000_0000b    |

| *           | 04h     |           |      |      | da_4d        | h[7:0]        |       |        |         | 0000_0000b    |

| *           | 05h     |           |      |      | da_5d        | h[7:0]        |       |        |         | 1111_111b     |

| *           | 06h     |           |      |      | da_6d        | h[7:0]        |       |        |         | 0111_1000b    |

| *           | 07h     |           |      |      | da7d         | h[7:0]        |       |        |         | 0000_0000b    |

| *           | 08h     |           |      |      | henal        | o[7:0]        |       |        |         | 1100_0010b    |

| *           | 09h     | -         |      |      |              | venab         | [7:0] |        |         | 0010_0011b    |

| *           | 0Ah     |           |      | -    |              |               | rsel  | vrvc   | hrvc    | 0000_0000b    |

| *           | 0Bh     |           |      |      |              | stb_hl[6:0]   |       |        |         | 0100_0101b    |

| *           | 0Ch     |           |      |      | gck_h        | ıl[7:0]       |       |        |         | 1010_1010b    |

| *           | 0Dh     | -         |      |      |              | slp_ctrl[6:0] |       |        |         | 0100_0011b    |

| *           | 0Eh     | gamma_enb |      |      |              | -             |       |        |         | 0000_0000b    |

| *           | 0Fh     |           |      |      | te           | st            |       |        |         | 0000_0000b    |

| *           | 10h     |           |      |      | te           | st            |       |        | T       | 0000_0000b    |

|             |         |           |      |      |              |               |       |        |         |               |

| 0           | 20h     |           |      |      | rom_ac       |               |       |        |         |               |

| 0           | 21h     |           |      |      | rom_da       | ata[7:0]      |       |        | T       |               |

| 0           | 22h     |           |      |      |              |               |       | r_read | r_write |               |

| 0           | 23h     |           |      |      | te           |               |       |        |         |               |

| 0           | 24h     |           |      |      | te           |               |       |        |         |               |

| 0           | 25h     |           |      |      | te           | st            |       |        |         |               |

|             | 001     | <b>.</b>  |      |      |              |               |       |        |         |               |

| $\triangle$ | 30h     |           |      |      | -            |               |       |        | allon   |               |

| $\triangle$ | 31h     |           |      |      | -            |               |       |        | als     |               |

| $\Diamond$  | 32h     | ready     |      |      | -            | -4            |       | jinput | jenable |               |

| $\triangle$ | 33h     |           |      |      | te           |               |       |        |         |               |

| $\Diamond$  | 34h     |           |      |      | adc_c        |               |       |        |         |               |

| $\Diamond$  | 35h     |           |      |      | adc_c        | วลเล2         |       |        |         |               |

#### ★: Register for auto-loading

als register value 0: Inaccessible.

als register value 1: Write/Read can be done from a host.

O: Register not for auto-loading

als register value 0: Inaccessible

als register value 1: Write/Read can be done from a host.

$\triangle$ : Register not for auto-loading

Regardless of the als register value, Write/Read can be done.

♦: Read-Only register

Regardless of the als register value, Read only can be done.

# 6. Conditions for Input Signal

#### 6.1. Conditions for Image Signal Input

Table 6-1 to Table 6-4 and Figure 6-1 to Figure 6-4 show the input range specifications for the WVGA, WQVGA, WEGA1 and WEGA2 modes. Also, Table 6-5 shows the horizontal/vertical display data capture position list in the WVGA, WQVGA, WEGA1 and WEGA2 display modes.

Table 6-1: WVGA Input Timing Specifications

### WVGA [D\_SEL1=0, D\_SEL2=0]

| ITE                       | M           | Symbol  | Min.  | Тур.  | Max.  | UNIT | Remark                   |

|---------------------------|-------------|---------|-------|-------|-------|------|--------------------------|

|                           | Frequency   | tCLK    | 26.62 | 33.26 | 34.60 | MHz  | Frequency:1/(tV/tH(clk)) |

| DCLK                      | Hi Time     | tWCH    | 5     | -     | -     | ns   |                          |

|                           | Low Width   | tWCL    | 5     | -     | -     | ns   |                          |

| Data[I* 0-5]              | Setup time  | tDS     | 5     | -     | -     | ns   |                          |

| טמנמןו ט-טן               | Hold time   | tDH     | 5     | -     | -     | ns   |                          |

|                           | Cycle       | tH(t)   | 31.45 | 31.75 | 38.46 | μs   |                          |

| Hsy                       |             | tH(clk) | 1024  | 1056  | 1088  | ck   |                          |

| •                         | Pulse Width | tHPW    | 5     | -     | tH-5  | ck   |                          |

| Vsy                       | Cycle       | tV      | 520   | 525   | 635   | line |                          |

| vsy                       | Pulse Width | tVPW    | 2     | -     | TV-2  | line |                          |

| frame rate                |             | fV      | 50    | 60    | 60    | Hz   |                          |

| Horizontal display perio  | d           | tHA     | -     | 800   | -     | ck   |                          |

| Hsy DCLK phase deffe      | erence      | tHC     | A-8   | Α     | A+8   | ns   | A=tWCH(1/2(DCLK))        |

| Hsy_Vsy phase deffere     | nce         | tVH     | -10   | 0     | 10    | ck   |                          |

| Vertical fromt porch      |             | tVFP    | 5     | -     | -     | line |                          |

| Vertical back porch       |             | tVBP    | -     | 35    | -     | line | In case ROMOFF='1'       |

| vertical back policii     |             | IVDF    | 10    | 28    | 35    | line | In case ROMOFF='0'       |

| Vertical display porch    |             | tVA     | -     | 480   | -     | line |                          |

|                           | Setup time  | tES     | 5     | -     | -     | ns   |                          |

| Enable signal[HENAB]      | Hold time   | tEH     | 5     | -     | -     | ns   |                          |

|                           | Pulse Width | tEP     | -     | 800   | -     | ck   |                          |

| Horizontal front porch    |             | tHFP    | 2     | -     | -     |      |                          |

| Harizantal dienlay eterti | na position | tHBP    | -     | 194   | -     |      | *1                       |

| Horizontal display starti | ng position | tHBP    | 20    | -     | 222   | ck   | *2                       |

<sup>\*1:</sup> This spec is appied for HENAB Lo mode and W/O EEPROM mode

Table 6-2: WQVGA Input Timing Specifications

#### WQVGA [D SEL1=1, D SEL2=0]

|                        | ГЕМ             | Symbol  | Min. | Тур. | Max. | UNIT | Remark                   |

|------------------------|-----------------|---------|------|------|------|------|--------------------------|

|                        | Frequency       | tCLK    | 6.96 | 7.99 | 9.19 |      | Frequency:1/(tV/tH(clk)) |

| DCLK                   | Hi Time         | tWCH    | 5    | -    | -    | ns   |                          |

|                        | Low Width       | tWCL    | 5    | -    | -    | ns   |                          |

| Data[I* 0-5]           | Setup time      | tDS     | 5    | -    | -    | ns   |                          |

| Dala[i U-J]            | Hold time       | tDH     | 5    | -    | -    | ns   |                          |

|                        | Cycle           | tH(t)   | 61.3 | 63.6 | 70.5 | μs   |                          |

| Hsy                    | Сусіе           | tH(clk) | 491  | 508  | 563  | ck   |                          |

|                        | Pulse Width     | tHPW    | 5    | -    | TH-5 | ck   |                          |

| Vov                    | Cycle           | tV      | 258  | 262  | 284  | line |                          |

| Vsy                    | Pulse Width     | tVPW    | 2    | -    | TV-2 | line |                          |

| frame rate             |                 | fV      | 50   | 60   | 60   | Hz   |                          |

| Horizontal display pe  | riod            | tHA     | -    | 400  | -    | ck   |                          |

| Hsy_DCLK phase de      | fference        | tHC     | A-8  | Α    | A+8  | ns   | A=tWCH(1/2(DCLK))        |

| Hsy_Vsy phase deffe    | erence          | tVH     | -10  | 0    | 10   | ck   |                          |

| Vertical fromt porch   |                 | tVFP    | 5    | -    | -    | line |                          |

| Vartical back parch    |                 | 4\ /DD  | -    | 20   | -    | line | In case ROMOFF='1'       |

| Vertical back porch    |                 | tVBP    | 9    | -    | 20   | line | In case ROMOFF='0'       |

| Vertical display porch | )               | tVA     | -    | 240  | -    | line |                          |

|                        | Setup time      | tES     | 5    | -    | -    | ns   |                          |

| Enable signal[HENAl    | Hold time       | tEH     | 5    | -    | -    | ns   |                          |

| <b>~</b> -             | Pulse Width     | tEP     | -    | 400  | -    | ck   |                          |

| Horizontal front porch | 1               | tHFP    | 2    | -    | -    |      |                          |

| Harizantal dianlay ata | erting position | tHBP    | -    | 87   | -    |      | *1                       |

| Horizontal display sta | irung position  | tHBP    | 20   | -    | 126  | ck   | *2                       |

<sup>\*1:</sup> This spec is appied for HENAB Lo mode and W/O EEPROM mode

<sup>\*2:</sup> This spec is applied for HENAB active mode or W/EEPROM mode

<sup>\*2:</sup> This spec is applied for HENAB active mode or W/EEPROM mode

Table 6-3: WEGA1 Input Timing Specifications

#### WEGA1 [D\_SEL1=0, D\_SEL2=1]

| ITE                       | M           | Symbol  | Min. | Тур. | Max.  | UNIT | Remark                   |

|---------------------------|-------------|---------|------|------|-------|------|--------------------------|

|                           | Frequency   | tCLK    | 8.58 | 9.70 | 10.99 | MHz  | Frequency:1/(tV/tH(clk)) |

| DCLK                      | Hi Time     | tWCH    | 5    | -    | -     | ns   |                          |

|                           | Low Width   | tWCL    | 5    | -    | -     | ns   |                          |

| Data[I* 0-5]              | Setup time  | tDS     | 5    | -    | -     | ns   |                          |

| Dala[i U-0]               | Hold time   | tDH     | 5    | -    | -     | ns   |                          |

|                           | Cycle       | tH(t)   | 58.8 | 64.1 | 66.5  | μs   |                          |

| Hsy                       | -           | tH(clk) | 571  | 622  | 646   | ck   |                          |

|                           | Pulse Width | tHPW    | 5    | -    | tH-5  | ck   |                          |

| Vsy                       | Cycle       | tV      | 283  | 312  | 344   | line |                          |

| vsy                       | Pulse Width | tVPW    | 2    | -    | TV-2  | line |                          |

| frame rate                |             | fV      | 50   | 50   | 60    | Hz   |                          |

| Horizontal display perio  |             | tHA     | -    | 480  | -     | ck   |                          |

| Hsy_DCLK phase deffe      | rence       | tHC     | A-8  | Α    | A+8   | ns   | A=tWCH(1/2(DCLK))        |

| Hsy_Vsy phase deffere     | nce         | tVH     | -10  | 0    | 10    | ck   |                          |

| Vertical fromt porch      |             | tVFP    | 2    | -    | -     | line |                          |

| Vertical back porch       |             | tVBP    | •    | 31   | -     | line | In case ROMOFF='1'       |

| vertical back policii     |             | LVDF    | 9    | -    | 41    | line | In case ROMOFF='0'       |

| Vertical display porch    |             | tVA     | •    | 272  | -     | line |                          |

|                           | Setup time  | tES     | 5    | -    | -     | ns   |                          |

| Enable signal[HENAB]      | Hold time   | tEH     | 5    | -    | -     | ns   |                          |

| <u> </u>                  | Pulse Width | tEP     | -    | 480  | -     | ck   |                          |

| Horizontal front porch    | ·           | tHFP    | 2    | -    | -     |      |                          |

| Horizontal display starti | na position | tHBP    | -    | 116  | -     |      | *1                       |

| Honzoniai dispiay starti  | ng position | tHBP    | 20   | -    | 164   | ck   | *2                       |

Table 6-4: WEGA2 Input Timing Specifications

# WEGA2 [D\_SEL1=1, D\_SEL2=1]

| WEGAL [B_GEE1-1, E         |             |         |      |      |       |      | r                        |

|----------------------------|-------------|---------|------|------|-------|------|--------------------------|

| ITE                        | IVI         | Symbol  | Min. | Typ. | Max.  |      | Remark                   |

|                            | Frequency   | tCLK    | 8.35 | 9.59 | 11.17 | MHz  | Frequency:1/(tV/tH(clk)) |

| DCLK                       | Hi Time     | tWCH    | 5    |      | -     | ns   |                          |

|                            | Low Width   | tWCL    | 5    | -    | -     | ns   |                          |

| Data[I* 0-5]               | Setup time  | tDS     | 5    | -    | -     | ns   |                          |

| Data[i 0-5]                | Hold time   | tDH     | 5    | -    | -     | ns   |                          |

|                            | Cycle       | tH(t)   | 61.3 | 63.6 | 70.5  | μs   |                          |

| Hsy                        |             | tH(clk) | 589  | 610  | 685   | ck   |                          |

|                            | Pulse Width | tHPW    | 5    |      | TH-5  | ck   |                          |

| Vsy                        | Cycle       | tV      | 258  | 262  | 284   | line |                          |

| vsy                        | Pulse Width | tVPW    | 2    | -    | TV-2  | line |                          |

| frame rate                 |             | fV      | 50   | 60   | 60    | Hz   |                          |

| Horizontal display perio   | d           | tHA     | -    | 480  | -     | ck   |                          |

| Hsy DCLK phase deffe       | rence       | tHC     | A-8  | Α    | A+8   | ns   | A=tWCH(1/2(DCLK))        |

| Hsy_Vsy phase deffere      | nce         | tVH     | -10  | 0    | 10    | ck   |                          |

| Vertical fromt porch       |             | tVFP    | 2    | -    | -     | line |                          |

| Vertical back porch        |             | tVBP    | -    | 20   | -     | line | In case ROMOFF='1'       |

| vertical back porch        |             | LVDF    | 9    | •    | 20    | line | In case ROMOFF='0'       |

| Vertical display porch     |             | tVA     | •    | 240  | -     | line |                          |

|                            | Setup time  | tES     | 5    | -    | -     | ns   |                          |

| Enable signal[HENAB]       | Hold time   | tEH     | 5    | •    | -     | ns   |                          |

|                            | Pulse Width | tEP     | -    | 480  | -     | ck   |                          |

| Horizontal front porch     |             | tHFP    | 2    | -    | -     |      |                          |

| Horizontal display starti  | na nosition | tHBP    | -    | 104  | -     |      | *1                       |

| i ionzoniai dispiay starti | ng position | tHBP    | 20   | -    | 152   | ck   | *2                       |

<sup>\*1:</sup> This spec is appied for HENAB Lo mode and W/O EEPROM mode

<sup>\*1:</sup> This spec is applied for HENAB Lo mode and W/O EEPROM mode \*2: This spec is applied for HENAB active mode or W/EEPROM mode

<sup>\*2:</sup> This spec is applied for HENAB active mode or W/EEPROM mode

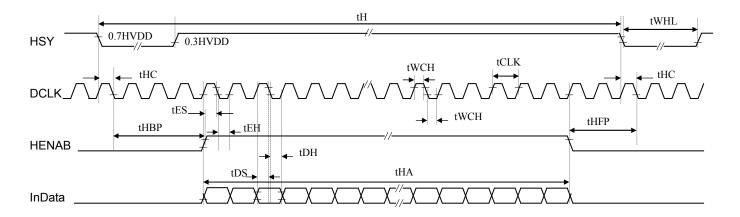

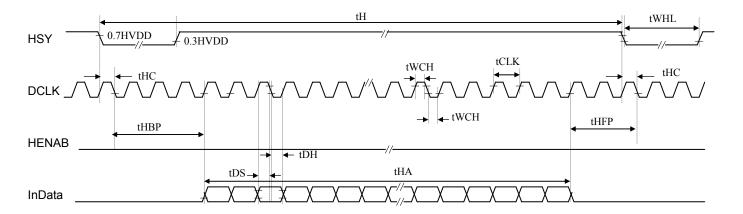

# 6.2. Horizontal timing 1 HENAB = Active input

Figure 6-1: WVGA/WQVGA/WEGA1/WEGA2 Input Data Format (HENAB active/horizontal timing)

"InData" above shows the image signal bus of IR0-5, IG0-5 and IB0-5 collectively. This applies to any "InData" after this.

# 6.3. Horizontal timing 2 HENAB = Fixed to Lo

Figure 6-2: WVGA/WQVGA/WEGA1/WEGA2 Input Data Format (HENAB\_Lo fixed/horizontal timing)

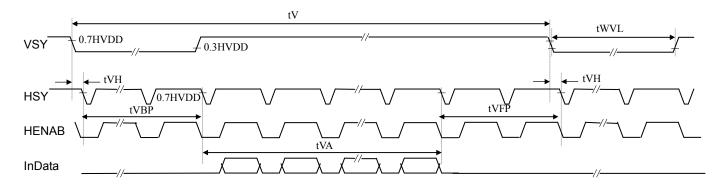

# 6.4. Vertical timing 1 HENAB = Active input

Figure 6-3: WVGA/WQVGA/WEGA1/WEGA2 Input Data Format (HENAB active/vertical timing)

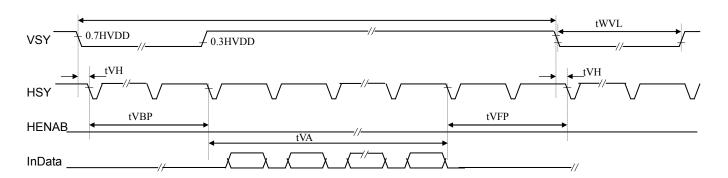

#### 6.5. Vertical timing 2 HENAB = Fixed to Lo

Figure 6-4: WVGA/WQVGA/WEGA1/WEGA2 Input Data Format (HENAB\_Lo fixed/vertical timing)

# 6.6. Horizontal/Vertical Data Capture Position

Table 6-5: Horizontal/Vertical Data Capture Position in WVGA/WQVGA/WEGA1/WEGA2 Display Mode

| HENAB input type | ROMOFF setting | tHBP                                 | tVBP                                 |

|------------------|----------------|--------------------------------------|--------------------------------------|

| F:               | 0              | А                                    | В                                    |

| Fixed to Lo      | 1              | Each condition for input signal tHBP | Each condition for input signal tVBP |

| A . C            | 0              | DENAB ↑                              | В                                    |

| Active input     | 1              | DENAB ↑                              | Each condition for input signal tVBP |

A: Decided according to a henab register set value.

B: Decided according to a venab register set value.

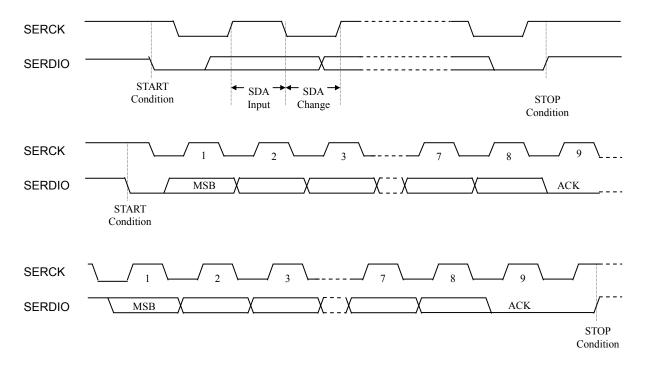

# 7. Serial Input Conditions (I2C)

# 7.1. Protocol

Figure 7-1 shows the protocol for I2C used for LQ0DZC2291.

Figure 7-1: I2C Protocol

# 7.2. Serial Interface AC Characteristics

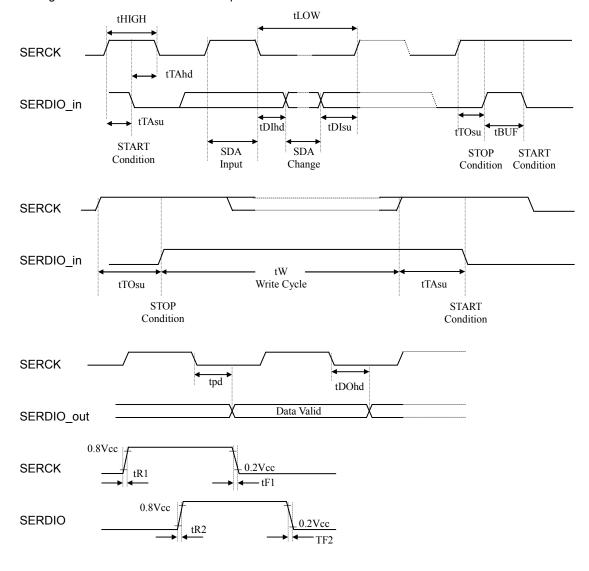

Figure 7-2 and Table 5-1 show the specifications for AC characteristics of I2C serial I/F.

Figure 7-2: AC Specifications for Serial I/F

Table 7-1: AC Specifications for Serial I/F

| Table 7-1. AC Specific                 | T TOTAL | Oction i/i |      |      |

|----------------------------------------|---------|------------|------|------|

| Item                                   | Symbol  | Min.       | Max. | Unit |

| Clock frequency                        | fSCK    |            | 400  | kHz  |

| Data clock "Hi" time                   | tHIGH   | 600        |      | ns   |

| Data clock "Lo" time                   | tLOW    | 1200       |      | ns   |

| Clock rise time                        | tR1     |            | 40   | ns   |

| Clock fall time                        | tF1     |            | 40   | ns   |

| Data rise time                         | tR2     |            | 40   | ns   |

| Data fall time                         | tF2     |            | 40   | ns   |

| Input data setup time                  | tDlsu   | 100        |      | ns   |

| Input data hold time                   | tDlhd   | 0          |      | ns   |

| Output data hold time                  | tDOhd   | 200        |      | ns   |

| Output data delay time                 | tpd     | 200        | 900  | ns   |

| Start condition setup time             | tTAsu   | 600        |      | ns   |

| Start condition hold time              | tTAhd   | 600        |      | ns   |

| Stop condition setup time              | tTOsu   | 600        | -    | ns   |

| Bus release time before transfer start | tBUF    | 1300       |      | ns   |

| Writing time                           | tW      |            | 10   | ms   |

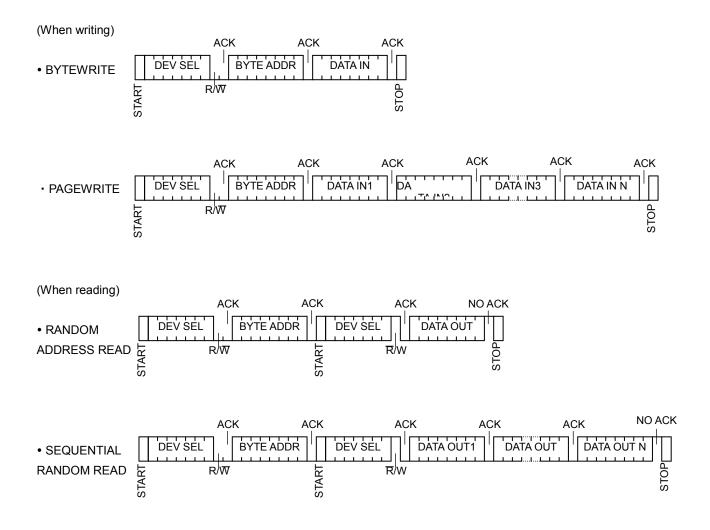

#### 7.3. Instruction to Write/Read to/from ASIC

Figure 7-3 shows how to Write/Read to/from ASIC with I2C of LQ0DZC2291.

\* DEV\_SEL of this ASIC is "1000111".

Figure 7-3: How to Write/Read with I2C

# 8. Description of Function and Supported Register

#### 8.1. Outline of Loading

This ASIC can transfer the initial values of ASIC's internal register and the parameters for gamma correction, which are stored in EEPROM, to ASIC, when external EEPROM is connected and the ROMOFF pin is set to "0". Transfer EEPROM data from EEPROM into ASIC's internal register and LUT is referred to as "loading" in this document. There are two types of loading in this ASIC, as described below.

#### (1) Initial loading

This refers to transferring a data in EEPROM as ASIC's initial value into the internal register and LUT after canceling ASIC reset (FREST). This allows to fix an initial operation of ASIC.

#### (2) Auto-loading

For address 0x31[0]:als = '0', this ASIC transfers a data in EEPROM into ASIC's internal register and LUT once a 64V period.

For the ASIC's internal register, all the registers are not always loaded from EEPROM. Refer to the register map of Table 5-1 and Table 8-1 below and check whether the register should be loaded or not.

Table 8-1: Enabling/Disabling Loading and Access from Host

|                                               | bing Loading and 7 toocoo in |                        |

|-----------------------------------------------|------------------------------|------------------------|

|                                               | ALS="0"                      | ALS="1"                |

| Register to be loaded                         | Access prohibited            | Write/Read can be done |

| (Marked with ★ in the register map)           |                              |                        |

| Register not to be loaded                     | Access prohibited            | Write/Read can be done |

| (Marked with ○ in the register map)           |                              |                        |

| Register not to be loaded                     | Write/Read can be done       | Write/Read can be done |

| (Marked with $\triangle$ in the register map) |                              |                        |

| Read-Only register                            | Read can be done             | Read can be done       |

| (Marked with ♦ in the register map)           |                              |                        |

#### 8.2. Description of Register Regarding Loading

Table 8-2 shows the registers regarding loading.

Table 8-2: Registers Regarding Loading

| address | bit7           | bit6                            | bit5            | bit4       | bit3 | bit2 | bit1             | bit0    | Initial value |

|---------|----------------|---------------------------------|-----------------|------------|------|------|------------------|---------|---------------|

| 31h     | <u> </u>       |                                 |                 | -          |      |      |                  | als     | xxxx_xxx0b    |

|         | als=0<br>als=1 | Auto-loading of Auto-loading of |                 |            |      |      | led is prohibite | d.      |               |

| 32h     | ready          |                                 |                 |            |      |      | jinput           | jenable |               |

|         | ready          | Hi: Initial EEP                 | ROM loading o   | ompleted.  |      |      |                  |         |               |

|         |                | Lo: Initial EEP                 | ROM loading i   | n process. |      |      |                  |         |               |

|         | jinput         | Hi: When HSY<br>Lo: At a norma  | //VSY has not y |            |      |      |                  |         |               |

|         | jenable        | Hi: When Hen                    |                 | •          |      |      |                  |         |               |

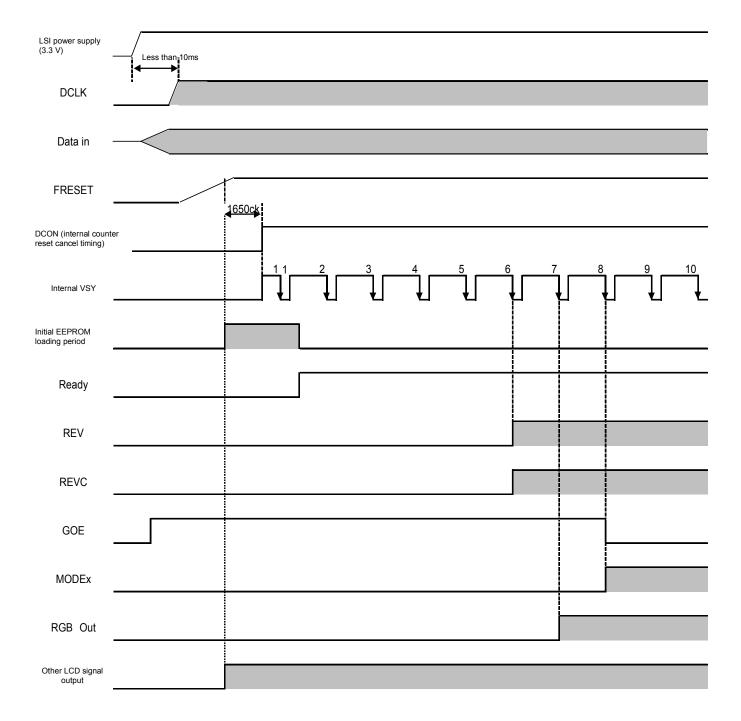

# 9. Power ON Sequence

Figure 9-1 below shows the power ON sequence.

Figure 9-1: Power ON Sequence

#### Procedure:

- (1) When ASIC has turned on, change the reset pin (FRESET) of this ASIC from "Lo" to "Hi" and cancel the reset.

- (2) When the reset has been cancelled, ASIC loads the initial values of internal register and LUT from EEPROM (for a maximum period of approximately 2 V).

- \* In this period, access with I2C from an external CPU to a register to be loaded is prohibited. When making access, check that the ready register is "1" (i.e., initial loading has been completed).

- (3) Power ON sequence starts with VsyActive immediately after DCON has become "Hi".

- (4) REV reversal starts according to the Vsy(6) timing. (Polarity reversal starts.)

- (5) Data output starts according to the Vsy(7) timing.

- (6) The liquid crystal display enters a normal operation state at Vsy(8).

# 10. I/O Format

Table 10-1 below describes the registers regarding I/O of timing controller (T-CON).

Table 10-1: Registers for I/O format

| 001                                               |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | h                                          | nah[7,0]          |                 |                 | T              | 0040 0044              |

|---------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------|-----------------|-----------------|----------------|------------------------|