### FIFTEEN OUTPUT DIFFERENTIAL ZBUFFER FOR PCIE GEN2/3 AND QPI

### 9ZX21501C

### Description

The 9ZX21501C is a 15-output version of the Intel DB1900Z Differential Buffer suitable for PCI-Express Gen3 or QPI applications. The part is backwards compatible to PCIe Gen1 and Gen2. A fixed external feedback maintains low drift for critical QPI applications. In bypass mode, the 9ZX21501C can provide outputs up to 400MHz.

# **Recommended Application**

15-output PCIe Gen3/QPI buffer with fixed feedback for Romley platforms

# **Output Features**

• 15 - 0.7V current mode differential HCSL output pairs

### Features/Benefits

- · Fixed feedback path; Ops input-to-output delay

- 9 Selectable SMBus addresses; multiple devices can share same SMBus segment

- 7 dedicated OE# pins; hardware control of outputs

- PLL or bypass mode; PLL can dejitter incoming clock

- Selectable PLL BW; minimizes jitter peaking in downstream PLL's

- Spread spectrum compatible; tracks spreading input clock for EMI reduction

- SMBus Interface; unused outputs can be disabled

- 100MHz & 133.33MHz PLL mode; legacy QPI support

- Undriven differential outputs in Power Down mode for maximum power savings

# **Key Specifications**

- Cycle-to-cycle jitter: <50ps

- Output-to-output skew: <65ps

- Input-to-output delay: Fixed at 0 ps

- Input-to-output delay variation: <50ps

- Phase jitter: PCIe Gen3 <1ps rms

- Phase jitter: QPI 9.6GB/s <0.2ps rms

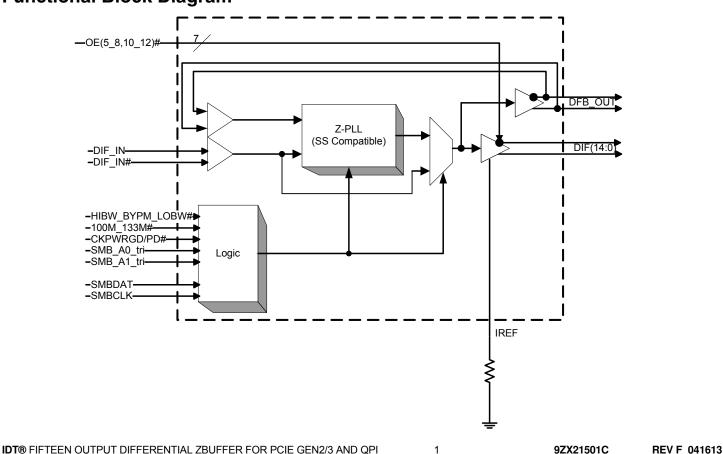

# **Functional Block Diagram**

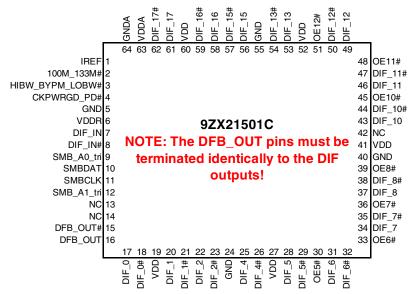

# **Pin Configuration**

### **Power Management Table**

| Inputs       |                    |                 | Contro | ol Bits/Pins                       |                   | Outputs              |              |  |

|--------------|--------------------|-----------------|--------|------------------------------------|-------------------|----------------------|--------------|--|

| CKPWRGD•/PD# | DIF_IN/<br>DIF_IN# | SMBus<br>EN bit |        | DIF(5:8,10:12)/<br>DIF(5:8,10:12)# |                   | DFB_OUT/<br>DFB_OUT# | PLL<br>State |  |

| 0            | Х                  | Х               | Х      | Hi-Z <sup>1</sup>                  | Hi-Z <sup>1</sup> | Hi-Z <sup>1</sup>    | OFF          |  |

|              |                    | 0               | Х      | Hi-Z <sup>1</sup>                  | Hi-Z <sup>1</sup> | Running              | ON           |  |

| 1            | Running            | 1               | 0      | Running                            | Running           | Running              | ON           |  |

|              |                    | 1               | 1      | Hi-Z <sup>1</sup>                  | Running           | Running              | ON           |  |

NOTE 1: Due to external pull down resistors, HI-Z results in Low/Low on the True/Complement outputs

### Functionality at Power-up (PLL mode)

| 100M_133M# | DIF_IN<br>(MHz) | DIF<br>MHz |

|------------|-----------------|------------|

| 1          | 100.00          | DIF_IN     |

| 0          | 133.33          | DIF_IN     |

#### **PLL Operating Mode**

| HiBW_BypM_LoBW# | MODE      |

|-----------------|-----------|

| Low             | PLL Lo BW |

| Mid             | Bypass    |

| High            | PLL Hi BW |

NOTE: PLL is OFF in Bypass Mode

### PLL Operating Mode Readback Table

| HiBW_BypM_LoBW# | Byte0, bit 7 | Byte 0, bit 6 |

|-----------------|--------------|---------------|

| Low (Low BW)    | 0            | 0             |

| Mid (Bypass)    | 0            | 1             |

| High (High BW)  | 1            | 1             |

### **Tri-Level Input Thresholds**

| Level | Voltage                           |

|-------|-----------------------------------|

| Low   | <0.8V                             |

| Mid   | 1.2 <vin<1.8v< td=""></vin<1.8v<> |

| High  | Vin > 2.2V                        |

IDT® FIFTEEN OUTPUT DIFFERENTIAL ZBUFFER FOR PCIE GEN2/3 AND QPI

### **Power Connections**

| Pin Nu                | Pin Number |               |  |  |

|-----------------------|------------|---------------|--|--|

| VDD                   | VDD GND    |               |  |  |

| 63                    | 64         | Analog PLL    |  |  |

| 6                     | 5          | Input Circuit |  |  |

| 19, 27, 41, 52,<br>60 | 24, 40, 55 | DIF clocks    |  |  |

#### **SMBus Addressing**

2

| Pi         | Pin        |                  |  |  |  |  |  |

|------------|------------|------------------|--|--|--|--|--|

| SMB_A1_tri | SMB_A0_tri | (Rd/Wrt bit = 0) |  |  |  |  |  |

| 0          | 0          | D8               |  |  |  |  |  |

| 0          | М          | DA               |  |  |  |  |  |

| 0          | 1          | DE               |  |  |  |  |  |

| М          | 0          | C2               |  |  |  |  |  |

| М          | М          | C4               |  |  |  |  |  |

| М          | 1          | C6               |  |  |  |  |  |

| 1          | 0          | CA               |  |  |  |  |  |

| 1          | М          | CC               |  |  |  |  |  |

| 1          | 1          | CE               |  |  |  |  |  |

# **Pin Descriptions**

| PIN # | PIN NAME        | TYPE | DESCRIPTION                                                                                                                        |

|-------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------|

|       |                 |      | This pin establishes the reference for the differential current-mode output pairs. It requires a fixed precision                   |

| 1     | IREF            | OUT  | resistor to ground. 4750hm is the standard value for 1000hm differential impedance. Other impedances                               |

|       |                 |      | require different values. See data sheet.                                                                                          |

| 2     | 100M_133M#      | IN   | 3.3V Input to select operating frequency                                                                                           |

| 2     | 100101_100101#  | IIN  | See Functionality Table for Definition                                                                                             |

| 3     | HIBW_BYPM_LOBW# | IN   | Trilevel input to select High BW, Bypass or Low BW mode.                                                                           |

|       |                 |      | See PLL Operating Mode Table for Details.                                                                                          |

| 4     | CKPWRGD_PD#     | IN   | Notifies device to sample latched inputs and start up on first high assertion, or exit Power Down Mode on                          |

|       | OND             | DWD  | subsequent assertions. Low enters Power Down Mode.                                                                                 |

| 5     | GND             | PWR  | Ground pin.                                                                                                                        |

| 6     | VDDR            | PWR  | 3.3V power for differential input clock (receiver). This VDD should be treated as an analog power rail and filtered appropriately. |

| 7     | DIF_IN          | IN   | 0.7 V Differential TRUE input                                                                                                      |

| 8     | DIF_IN#         | IN   | 0.7 V Differential Complementary Input                                                                                             |

| 9     | SMB_A0_tri      | IN   | SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A1 to decode 1 of 9                            |

|       |                 |      | SMBus Addresses.                                                                                                                   |

| 10    | SMBDAT          | I/O  | Data pin of SMBUS circuitry, 5V tolerant                                                                                           |

| 11    | SMBCLK          | IN   | Clock pin of SMBUS circuitry, 5V tolerant                                                                                          |

| 12    | SMB_A1_tri      | IN   | SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A0 to decode 1 of 9 SMBus Addresses.           |

| 13    | NC              | N/A  | No Connection.                                                                                                                     |

|       | NC              | N/A  | No Connection.                                                                                                                     |

|       |                 |      | Complementary half of differential feedback output, provides feedback signal to the PLL for                                        |

| 15    | DFB_OUT#        | OUT  | synchronization with input clock to eliminate phase error.                                                                         |

| 16    | DFB_OUT         | OUT  | True half of differential feedback output, provides feedback signal to the PLL for synchronization with the                        |

|       |                 | 001  | input clock to eliminate phase error.                                                                                              |

| 17    | DIF_0           | OUT  | 0.7V differential true clock output                                                                                                |

| 18    | DIF_0#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

| 19    | VDD             | PWR  | Power supply, nominal 3.3V                                                                                                         |

| 20    | DIF_1           | OUT  | 0.7V differential true clock output                                                                                                |

| 21    | DIF_1#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

|       | DIF_2           | OUT  | 0.7V differential true clock output                                                                                                |

| 23    | DIF_2#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

| 24    | GND             | PWR  | Ground pin.                                                                                                                        |

| 25    | DIF_4           | OUT  | 0.7V differential true clock output                                                                                                |

| 26    | DIF_4#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

| 27    | VDD             |      | Power supply, nominal 3.3V                                                                                                         |

| 28    | DIF_5           |      | 0.7V differential true clock output                                                                                                |

| 29    | DIF_5#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

| 30    | OE5#            | IN   | Active low input for enabling DIF pair 5.<br>1 =disable outputs, 0 = enable outputs                                                |

| 31    | DIF_6           | OUT  | 0.7V differential true clock output                                                                                                |

| 32    | DIF_6#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

| 33    | OE6#            | IN   | Active low input for enabling DIF pair 6.                                                                                          |

| 33    |                 | IIN  | 1 =disable outputs, 0 = enable outputs                                                                                             |

| 34    | DIF_7           | OUT  | 0.7V differential true clock output                                                                                                |

| 35    | DIF_7#          | OUT  | 0.7V differential Complementary clock output                                                                                       |

| 36    | OE7#            | IN   | Active low input for enabling DIF pair 7.                                                                                          |

| 00    |                 | 11 N | 1 =disable outputs, 0 = enable outputs                                                                                             |

# **Pin Descriptions (continued)**

| 37 | DIF 8   | OUT | 0.7V differential true clock output          |

|----|---------|-----|----------------------------------------------|

| -  | DIF 8#  | OUT | 0.7V differential Complementary clock output |

|    |         |     | Active low input for enabling DIF pair 8.    |

| 39 | OE8#    | IN  | 1 =disable outputs, 0 = enable outputs       |

| 40 | GND     | PWR | Ground pin.                                  |

| 41 | VDD     | PWR | Power supply, nominal 3.3V                   |

| 42 | NC      | N/A | No Connection.                               |

| 43 | DIF_10  | OUT | 0.7V differential true clock output          |

| 44 | DIF_10# | OUT | 0.7V differential Complementary clock output |

| 45 | OE10#   | IN  | Active low input for enabling DIF pair 10.   |

| 45 | 0E10#   | IIN | 1 =disable outputs, 0 = enable outputs       |

| 46 | DIF_11  | OUT | 0.7V differential true clock output          |

| 47 | DIF_11# | OUT | 0.7V differential Complementary clock output |

| 48 | OE11#   | IN  | Active low input for enabling DIF pair 11.   |

| 40 | OETT#   | IIN | 1 =disable outputs, 0 = enable outputs       |

| 49 | DIF_12  | OUT | 0.7V differential true clock output          |

| 50 | DIF_12# | OUT | 0.7V differential Complementary clock output |

| 51 | OE12#   | IN  | Active low input for enabling DIF pair 12.   |

| 51 | 0L12#   | IIN | 1 =disable outputs, 0 = enable outputs       |

| 52 | VDD     | PWR | Power supply, nominal 3.3V                   |

| 53 | DIF_13  | OUT | 0.7V differential true clock output          |

| 54 | DIF_13# | OUT | 0.7V differential Complementary clock output |

| 55 | GND     | PWR | Ground pin.                                  |

| 56 | DIF_15  | OUT | 0.7V differential true clock output          |

| 57 | DIF_15# | OUT | 0.7V differential Complementary clock output |

| 58 | DIF_16  | OUT | 0.7V differential true clock output          |

| 59 | DIF_16# | OUT | 0.7V differential Complementary clock output |

| 60 | VDD     | PWR | Power supply, nominal 3.3V                   |

| 61 | DIF_17  | OUT | 0.7V differential true clock output          |

| 62 | DIF_17# | OUT | 0.7V differential Complementary clock output |

| 63 | VDDA    | PWR | 3.3V power for the PLL core.                 |

| 64 | GNDA    | PWR | Ground pin for the PLL core.                 |

IDT® FIFTEEN OUTPUT DIFFERENTIAL ZBUFFER FOR PCIE GEN2/3 AND QPI

4

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 9ZX21501C. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER                 | SYMBOL          | CONDITIONS                 | MIN     | TYP | MAX            | UNITS | NOTES |

|---------------------------|-----------------|----------------------------|---------|-----|----------------|-------|-------|

| 3.3V Core Supply Voltage  | VDDA            |                            |         |     | 4.6            | V     | 1,2   |

| 3.3V Logic Supply Voltage | VDD             |                            |         |     | 4.6            | V     | 1,2   |

| Input Low Voltage         | V <sub>IL</sub> |                            | GND-0.5 |     |                | V     | 1     |

| Input High Voltage        | V <sub>IH</sub> | Except for SMBus interface |         |     | $V_{DD}$ +0.5V | V     | 1     |

| Input High Voltage        | VIHSMB          | SMBus clock and data pins  |         |     | 5.5V           | V     | 1     |

| Storage Temperature       | Ts              |                            | -65     |     | 150            | °C    | 1     |

| Junction Temperature      | Tj              |                            |         |     | 125            | °C    | 1     |

| Input ESD protection      | ESD prot        | Human Body Model           | 2000    |     |                | V     | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

### **Electrical Characteristics–Clock Input Parameters**

TA = T<sub>COM</sub>; Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

| PARAMETER                             | SYMBOL             | CONDITIONS                                        | MIN                   | TYP | MAX  | UNITS | NOTES |

|---------------------------------------|--------------------|---------------------------------------------------|-----------------------|-----|------|-------|-------|

| Input High Voltage - DIF_IN           | VIHDIF             | Differential inputs<br>(single-ended measurement) | 600                   | 750 | 1150 | mV    | 1     |

| Input Low Voltage - DIF_IN            | V <sub>ILDIF</sub> | Differential inputs<br>(single-ended measurement) | V <sub>SS</sub> - 300 | 0   | 300  | mV    | 1     |

| Input Common Mode<br>Voltage - DIF_IN | V <sub>COM</sub>   | Common Mode Input Voltage                         | 300                   |     | 1000 | mV    | 1     |

| Input Amplitude - DIF_IN              | V <sub>SWING</sub> | Peak to Peak value                                | 300                   |     | 1450 | mV    | 1     |

| Input Slew Rate - DIF_IN              | dv/dt              | Measured differentially                           | 0.4                   |     | 8    | V/ns  | 1,2   |

| Input Leakage Current                 | I <sub>IN</sub>    | $V_{IN} = V_{DD}, V_{IN} = GND$                   | -5                    |     | 5    | uA    | 1     |

| Input Duty Cycle                      | d <sub>tin</sub>   | Measurement from differential wavefrom            | 45                    |     | 55   | %     | 1     |

| Input Jitter - Cycle to Cycle         | J <sub>DIFIn</sub> | Differential Measurement                          | 0                     |     | 125  | ps    | 1     |

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Slew rate measured through +/-75mV window centered around differential zero

# **Electrical Characteristics–Input/Supply/Common Output Parameters**

TA =  $T_{COM}$ : Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

| PARAMETER                        | SYMBOL              | CONDITIONS                                                                                                                            | MIN       | TYP    | MAX                   | UNITS  | NOTES |

|----------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|-----------------------|--------|-------|

| Ambient Operating<br>Temperature | Т <sub>СОМ</sub>    | Commmercial range                                                                                                                     | 0         |        | 70                    | °C     | 1     |

| Input High Voltage               | V <sub>IH</sub>     | Single-ended inputs, except SMBus, low<br>threshold and tri-level inputs                                                              | 2         |        | V <sub>DD</sub> + 0.3 | v      | 1     |

| Input Low Voltage                | V <sub>IL</sub>     | Single-ended inputs, except SMBus, low<br>threshold and tri-level inputs                                                              | GND - 0.3 |        | 0.8                   | v      | 1     |

|                                  | I <sub>IN</sub>     | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = VDD$                                                                                  | -5        |        | 5                     | uA     | 1     |

| Input Current                    | I <sub>INP</sub>    | Single-ended inputs $V_{IN} = 0 V$ ; Inputs with internal pull-up resistors $V_{IN} = VDD$ ; Inputs with internal pull-down resistors | -200      |        | 200                   | uA     | 1     |

|                                  | F <sub>ibyp</sub>   | $V_{DD} = 3.3 V$ , Bypass mode                                                                                                        | 33        |        | 400                   | MHz    | 2     |

| Input Frequency                  | F <sub>ipll</sub>   | $V_{DD} = 3.3 V$ , 100MHz PLL mode                                                                                                    | 90        | 100.00 | 105                   | MHz    | 2     |

|                                  | F <sub>ipll</sub>   | V <sub>DD</sub> = 3.3 V, 133.33MHz PLL mode                                                                                           | 120       | 133.33 | 140                   | MHz    | 2     |

| Pin Inductance                   | L <sub>pin</sub>    |                                                                                                                                       |           |        | 7                     | nH     | 1     |

|                                  | CIN                 | Logic Inputs, except DIF_IN                                                                                                           | 1.5       |        | 5                     | pF     | 1     |

| Capacitance                      | $C_{INDIF_IN}$      | DIF_IN differential clock inputs                                                                                                      | 1.5       |        | 2.7                   | pF     | 1,4   |

|                                  | C <sub>OUT</sub>    | Output pin capacitance                                                                                                                |           |        | 6                     | pF     | 1     |

| Clk Stabilization                | T <sub>STAB</sub>   | From $V_{DD}$ Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock                                        |           |        | 1.8                   | ms     | 1,2   |

| Input SS Modulation<br>Frequency | f <sub>MODIN</sub>  | Allowable Frequency<br>(Triangular Modulation)                                                                                        | 30        |        | 33                    | kHz    | 1     |

| OE# Latency                      | t <sub>LATOE#</sub> | DIF start after OE# assertion<br>DIF stop after OE# deassertion                                                                       | 4         |        | 12                    | clocks | 1,3   |

| Tdrive_PD#                       | t <sub>DRVPD</sub>  | DIF output enable after<br>PD# de-assertion                                                                                           |           |        | 300                   | us     | 1,3   |

| Tfall                            | t <sub>F</sub>      | Fall time of control inputs                                                                                                           |           |        | 5                     | ns     | 1,2   |

| Trise                            | t <sub>R</sub>      | Rise time of control inputs                                                                                                           |           |        | 5                     | ns     | 1,2   |

| SMBus Input Low Voltage          | VILSMB              |                                                                                                                                       |           |        | 0.8                   | V      | 1     |

| SMBus Input High Voltage         | VIHSMB              |                                                                                                                                       | 2.1       |        | V <sub>DDSMB</sub>    | V      | 1     |

| SMBus Output Low Voltage         | VOLSMB              | @ I <sub>PULLUP</sub>                                                                                                                 |           |        | 0.4                   | V      | 1     |

| SMBus Sink Current               | I <sub>PULLUP</sub> | @ V <sub>OL</sub>                                                                                                                     | 4         |        |                       | mA     | 1     |

| Nominal Bus Voltage              | V <sub>DDSMB</sub>  | 3V to 5V +/- 10%                                                                                                                      | 2.7       |        | 5.5                   | V      | 1     |

| SCLK/SDATA Rise Time             | t <sub>RSMB</sub>   | (Max VIL - 0.15) to (Min VIH + 0.15)                                                                                                  |           |        | 1000                  | ns     | 1     |

| SCLK/SDATA Fall Time             | t <sub>FSMB</sub>   | (Min VIH + 0.15) to (Max VIL - 0.15)                                                                                                  |           |        | 300                   | ns     | 1     |

| SMBus Operating<br>Frequency     | f <sub>MAXSMB</sub> | Maximum SMBus operating frequency                                                                                                     |           |        | 100                   | kHz    | 1,5   |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Control input must be monotonic from 20% to 80% of input swing.

<sup>3</sup>Time from deassertion until outputs are >200 mV

<sup>4</sup> DIF\_IN input

<sup>5</sup>The differential input clock must be running for the SMBus to be active

# Electrical Characteristics–DIF 0.7V Current Mode Differential Outputs

| PARAMETER              | SYMBOL     | CONDITIONS                                                                                 | MIN  | TYP | MAX  | UNITS | NOTES   |

|------------------------|------------|--------------------------------------------------------------------------------------------|------|-----|------|-------|---------|

| Slew rate              | Trf        | Scope averaging on                                                                         | 1    | 2.5 | 4    | V/ns  | 1, 2, 3 |

| Slew rate matching     | ΔTrf       | Slew rate matching, Scope averaging on                                                     |      |     | 20   | %     | 1, 2, 4 |

| Voltage High           | VHigh      | Statistical measurement on single-ended signal<br>using oscilloscope math function. (Scope | 660  | 750 | 850  | mV    | 1       |

| Voltage Low            | VLow       | averaging on)                                                                              | -150 |     | 150  |       | 1       |

| Max Voltage            | Vmax       | Measurement on single ended signal using                                                   |      |     | 1150 | mV    | 1       |

| Min Voltage            | Vmin       | absolute value. (Scope averaging off)                                                      | -300 |     |      | 111.0 | 1       |

| Vswing                 | Vswing     | Scope averaging off                                                                        | 300  |     |      | mV    | 1, 2    |

| Crossing Voltage (abs) | Vcross_abs | Scope averaging off                                                                        | 250  |     | 550  | mV    | 1, 5    |

| Crossing Voltage (var) | ∆-Vcross   | Scope averaging off                                                                        |      |     | 140  | mV    | 1, 6    |

TA = T<sub>COM:</sub> Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production. IREF = VDD/(3xR<sub>B</sub>). For R<sub>B</sub> = 475 $\Omega$  (1%), I<sub>REF</sub> = 2.32mA. I<sub>OH</sub> = 6 x I<sub>REF</sub> and V<sub>OH</sub> = 0.7V @ Z<sub>O</sub>=50 $\Omega$  (100 $\Omega$  differential impedance).

<sup>2</sup> Measured from differential waveform

<sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of V\_cross\_min/max (V\_cross absolute) allowed. The intent is to limit Vcross induced modulation by setting V\_cross\_delta to be smaller than V\_cross absolute.

### **Electrical Characteristics–Current Consumption**

TA = T<sub>COM:</sub> Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

| PARAMETER                | SYMBOL                | CONDITIONS                                              | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|-----------------------|---------------------------------------------------------|-----|-----|-----|-------|-------|

| Operating Supply Current | I <sub>DD3.3OP</sub>  | All outputs active @100MHz, C <sub>L</sub> = Full load; |     | 390 | 425 | mA    | 1     |

| Powerdown Current        | I <sub>DD3.3PDZ</sub> | All differential pairs tri-stated                       |     | 5   | 15  | mA    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

# **Electrical Characteristics–Skew and Differential Jitter Parameters**

| PARAMETER              | SYMBOL                | CONDITIONS                                                                                 | MIN  | TYP | MAX | UNITS       | NOTES     |

|------------------------|-----------------------|--------------------------------------------------------------------------------------------|------|-----|-----|-------------|-----------|

| CLK_IN, DIF[x:0]       | t <sub>SPO_PLL</sub>  | Input-to-Output Skew in PLL mode<br>nominal value @ 25°C, 3.3V                             | -100 | 0   | 100 | ps          | 1,2,4,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>PD_BYP</sub>   | Input-to-Output Skew in Bypass mode<br>nominal value @ 25°C, 3.3V                          | 2.5  | 3.5 | 4.5 | ns          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DSPO_PLL</sub> | Input-to-Output Skew Varation in PLL mode<br>across voltage and temperature                | -50  | 0   | 50  | ps          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DSPO_BYP</sub> | Input-to-Output Skew Varation in Bypass mode<br>across voltage and temperature             | -250 | 0   | 250 | ps          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DTE</sub>      | Random Differential Tracking error beween two<br>9ZX devices in Hi BW Mode                 |      | 3   | 5   | ps<br>(rms) | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DSSTE</sub>    | Random Differential Spread Spectrum Tracking<br>error beween two 9ZX devices in Hi BW Mode |      | 15  | 75  | ps          | 1,2,3,5,8 |

| DIF{x:0]               | t <sub>SKEW_ALL</sub> | Output-to-Output Skew across all outputs<br>(Common to Bypass and PLL mode)                |      | 37  | 65  | ps          | 1,2,3,8   |

| PLL Jitter Peaking     | jpeak-hibw            | LOBW#_BYPASS_HIBW = 1                                                                      | 0    | 1.3 | 2.5 | dB          | 7,8       |

| PLL Jitter Peaking     | jpeak-lobw            | LOBW#_BYPASS_HIBW = 0                                                                      | 0    | 0.8 | 2   | dB          | 7,8       |

| PLL Bandwidth          | рІІ <sub>нівw</sub>   | LOBW#_BYPASS_HIBW = 1                                                                      | 2    | 3   | 4   | MHz         | 8,9       |

| PLL Bandwidth          | pll <sub>LOBW</sub>   | LOBW#_BYPASS_HIBW = 0                                                                      | 0.7  | 1.1 | 1.4 | MHz         | 8,9       |

| Duty Cycle             | t <sub>DC</sub>       | Measured differentially, PLL Mode                                                          | 45   | 50  | 55  | %           | 1         |

| Duty Cycle Distortion  | t <sub>DCD</sub>      | Measured differentially, Bypass Mode<br>@100MHz                                            | -2   | 0   | 2   | %           | 1,10      |

| Jitter, Cycle to cycle | t.                    | PLL mode                                                                                   |      | 41  | 50  | ps          | 1,11      |

|                        | t <sub>jcyc-cyc</sub> | Additive Jitter in Bypass Mode                                                             |      | 20  | 50  | ps          | 1,11      |

TA =  $T_{COM}$ : Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

#### Notes for preceding table:

<sup>1</sup> Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

<sup>2</sup> Measured from differential cross-point to differential cross-point. This parameter can be tuned with external feedback path, if present.

<sup>3</sup> All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

<sup>4</sup> This parameter is deterministic for a given device

<sup>5</sup> Measured with scope averaging on to find mean value. DIF\_IN slew rate must be matched to DIF output slew rate.

<sup>6.</sup>t is the period of the input clock

<sup>7</sup> Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

<sup>8.</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>9</sup> Measured at 3 db down or half power point.

<sup>10</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mod-

<sup>11</sup> Measured from differential waveform

# **Electrical Characteristics–Phase Jitter Parameters**

| PARAMETER                                    | SYMBOL                  | CONDITIONS                                             | MIN | TYP  | MAX | UNITS       | Notes   |

|----------------------------------------------|-------------------------|--------------------------------------------------------|-----|------|-----|-------------|---------|

|                                              | t <sub>jphPCleG1</sub>  | PCIe Gen 1                                             |     | 39   | 86  | ps (p-p)    | 1,2,3   |

|                                              | t <sub>jphPCleG2</sub>  | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz               |     | 1.1  | 3   | ps<br>(rms) | 1,2     |

|                                              |                         | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)   |     | 2.6  | 3.1 | ps<br>(rms) | 1,2     |

| Jitter, Phase                                | t <sub>jphPCleG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz)          |     | 0.6  | 1   | ps<br>(rms) | 1,2,4   |

|                                              |                         | QPI & SMI<br>(100MHz or 133MHz, 4.8Gb/s, 6.4Gb/s 12UI) |     | 0.36 | 0.5 | ps<br>(rms) | 1,5     |

|                                              | t <sub>jphQPI_SMI</sub> | QPI & SMI<br>(100MHz, 8.0Gb/s, 12UI)                   |     | 0.23 | 0.3 | ps<br>(rms) | 1,5     |

|                                              |                         | QPI & SMI<br>(100MHz, 9.6Gb/s, 12UI)                   |     | 0.18 | 0.2 | ps<br>(rms) | 1,5     |

|                                              | t <sub>jphPCleG1</sub>  | PCIe Gen 1                                             |     | 4    | 10  | ps (p-p)    | 1,2,3   |

|                                              |                         | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz               |     | 0.25 | 0.3 | ps<br>(rms) | 1,2,6   |

|                                              | t <sub>jphPCleG2</sub>  | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)   |     | 0.57 | 0.7 | ps<br>(rms) | 1,2,6   |

| <i>Additive</i> Phase Jitter,<br>Bypass mode | t <sub>jphPCleG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz)          |     | 0.20 | 0.3 | ps<br>(rms) | 1,2,4,6 |

| 2,9400 11000                                 |                         | QPI & SMI<br>(100MHz or 133MHz, 4.8Gb/s, 6.4Gb/s 12UI) |     | 0.22 | 0.3 | ps<br>(rms) | 1,5,6   |

|                                              | t <sub>jphQPI_SMI</sub> | QPI & SMI<br>(100MHz, 8.0Gb/s, 12UI)                   |     | 0.08 | 0.1 | ps<br>(rms) | 1,5,6   |

|                                              |                         | QPI & SMI<br>(100MHz, 9.6Gb/s, 12UI)                   |     | 0.08 | 0.1 | ps<br>(rms) | 1,5,6   |

TA = T<sub>COM</sub>: Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

<sup>1</sup> Applies to all outputs.

<sup>2</sup> See http://www.pcisig.com for complete specs

<sup>3</sup> Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

<sup>4</sup> Subject to final ratification by PCI SIG.

<sup>5</sup> Calculated from Intel-supplied Clock Jitter Tool v 1.6.3

<sup>6</sup> For RMS figures, additive jitter is calculated by solving the following equation: (Additive jitter)<sup>2</sup> = (total jitter)<sup>2</sup> - (input jitter)<sup>2</sup>

# **Clock Periods–Differential Outputs with Spread Spectrum Disabled**

|   |         | Center<br>Freq.<br>MHz |                              | Measurement Window                   |                                      |                            |                                      |                                      |                              |       |       |

|---|---------|------------------------|------------------------------|--------------------------------------|--------------------------------------|----------------------------|--------------------------------------|--------------------------------------|------------------------------|-------|-------|

|   |         |                        | 1 Clock                      | 1us                                  | 0.1s                                 | 0.1s                       | 0.1s                                 | 1us                                  | 1 Clock                      |       |       |

| ę | SSC OFF |                        | -c2c jitter<br>AbsPer<br>Min | -SSC<br>Short-Term<br>Average<br>Min | - ppm<br>Long-Term<br>Average<br>Min | 0 ppm<br>Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Max | +SSC<br>Short-Term<br>Average<br>Max | +c2c jitter<br>AbsPer<br>Max | Units | Notes |

|   | DIF     | 100.00                 | 9.94900                      |                                      | 9.99900                              | 10.00000                   | 10.00100                             |                                      | 10.05100                     | ns    | 1,2,3 |

|   | יוט     | 133.33                 | 7.44925                      |                                      | 7.49925                              | 7.50000                    | 7.50075                              |                                      | 7.55075                      | ns    | 1,2,4 |

# **Clock Periods–Differential Outputs with Spread Spectrum Enabled**

|        |                        |                              | Measurement Window                   |                                      |                            |                                      |                                      |                              |            |       |

|--------|------------------------|------------------------------|--------------------------------------|--------------------------------------|----------------------------|--------------------------------------|--------------------------------------|------------------------------|------------|-------|

|        | Contor                 | 1 Clock                      | 1us                                  | 0.1s                                 | 0.1s                       | 0.1s                                 | 1us                                  | 1 Clock                      |            |       |

| SSC ON | Center<br>Freq.<br>MHz | -c2c jitter<br>AbsPer<br>Min | -SSC<br>Short-Term<br>Average<br>Min | - ppm<br>Long-Term<br>Average<br>Min | 0 ppm<br>Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Max | +SSC<br>Short-Term<br>Average<br>Max | +c2c jitter<br>AbsPer<br>Max | er Units I | Notes |

| DIF    | 99.75                  | 9.94906                      | 9.99906                              | 10.02406                             | 10.02506                   | 10.02607                             | 10.05107                             | 10.10107                     | ns         | 1,2,3 |

| DIF    | 133.00                 | 7.44930                      | 7.49930                              | 7.51805                              | 7.51880                    | 7.51955                              | 7.53830                              | 7.58830                      | ns         | 1,2,4 |

### Notes:

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with CK420BQ/CK410B+ accuracy requirements (+/-100ppm). The 9ZX21501 itself does not contribute to ppm error.

<sup>3</sup> Driven by SRC output of main clock, 100 MHz PLL Mode or Bypass mode

<sup>4</sup> Driven by CPU output of main clock, 133 MHz PLL Mode or Bypass mode

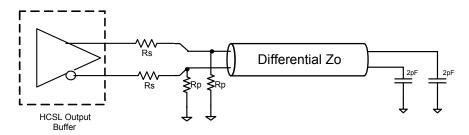

### Differential Output Termination Table

| DIF Zo (Ω) | Iref (Ω) | Rs ( $\Omega$ ) | Rp (Ω)       |

|------------|----------|-----------------|--------------|

| 100        | 475      | 33              | 50           |

| 85         | 412      | 27              | 42.2 or 43.2 |

9ZX21501 Differential Test Loads

# General SMBus Serial Interface Information for 9ZX21501C

### How to Write

- Controller (host) sends a start bit

- · Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) sends the byte count = X

- IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- IDT clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

### How to Read

- · Controller (host) will send a start bit

- Controller (host) sends the write address XX<sub>(H)</sub>

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- · Controller (host) will send a separate start bit

- Controller (host) sends the read address YY(H)

- IDT clock will acknowledge

- IDT clock will send the data byte count = X

- IDT clock sends Byte N+X-1

- IDT clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

|   |       | Index Block F               | Read O | peration            |

|---|-------|-----------------------------|--------|---------------------|

|   | Co    | ntroller (Host)             |        | IDT (Slave/Receiver |

|   | Т     | starT bit                   |        |                     |

| _ | Slave | e Address XX <sub>(H)</sub> |        |                     |

| _ | WR    | WRite                       |        |                     |

| - |       |                             |        | ACK                 |

| - | Beg   | inning Byte = N             |        |                     |

| - |       |                             |        | ACK                 |

|   | RT    | Repeat starT                |        |                     |

|   | Slave | e Address YY <sub>(H)</sub> |        |                     |

|   | RD    | ReaD                        |        |                     |

|   |       |                             |        | ACK                 |

|   |       |                             |        |                     |

|   |       | •                           |        | Data Byte Count=X   |

|   |       | ACK                         |        |                     |

|   |       |                             |        | Beginning Byte N    |

|   |       | ACK                         |        |                     |

|   |       |                             | e      | 0                   |

|   |       | 0                           | X Byte | 0                   |

|   |       | 0                           | ×      | 0                   |

|   |       | 0                           |        |                     |

|   |       |                             |        | Byte N + X - 1      |

|   | Ν     | Not acknowledge             |        |                     |

|   | Р     | stoP bit                    |        |                     |

11

#### **Index Block Write Operation Controller (Host) IDT (Slave/Receiver)** Т starT bit Slave Address XX(H) WR WRite ACK Beginning Byte = N ACK Data Byte Count = X ACK Beginning Byte N ACK 0 $\times$ Byte 0 Ο 0 0 0 Byte N + X - 1 ACK Р stoP bit

Note: XX<sub>(H)</sub> is defined by SMBus addess select pins.

| Byte  | e 0 Pin # | Name       | Control Function                 | Type | 0          | 1                      | Default |

|-------|-----------|------------|----------------------------------|------|------------|------------------------|---------|

| Bit 7 | 3         | PLL Mode 1 | PLL Operating Mode Rd back 1     | R    | See PLL Op | See PLL Operating Mode |         |

| Bit 6 | 3         | PLL Mode 0 | PLL Operating Mode Rd back 0     | R    | Readba     | Readback Table         |         |

| Bit 5 |           |            | Reserved                         |      |            |                        | 1       |

| Bit 4 | 61/62     | DIF_17_En  | Output Control overrides OE# pin | RW   | Hi-Z       | Enable                 | 1       |

| Bit 3 | 58/59     | DIF_16_En  | Output Control overrides OE# pin | RW   | Hi-Z       | Enable                 | 1       |

| Bit 2 |           |            | Reserved                         |      |            |                        | 0       |

| Bit 1 |           |            | Reserved                         |      |            |                        | 0       |

| Bit 0 | 2         | 100M_133#  | Frequency Select Readback        | R    | 133MHz     | 100MHz                 | Latch   |

#### SMBusTable: PLL Mode, and Frequency Select Register

### SMBusTable: Output Control Register

| Byte  | 1 Pin # | Name     | Control Function                 | Туре | 0    | 1      | Default |

|-------|---------|----------|----------------------------------|------|------|--------|---------|

| Bit 7 | 34/35   | DIF_7_En | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 6 | 31/32   | DIF_6_En | Output Control overrides OE# pin | RW   | Hi-Z | Enable | 1       |

| Bit 5 | 28/29   | DIF_5_En | Output Control overrides OE# pin | RW   |      | Enable | 1       |

| Bit 4 | 25/26   | DIF_4_En | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 3 |         |          | Reserved                         |      |      |        | 1       |

| Bit 2 | 22/23   | DIF_2_En | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 1 | 20/21   | DIF_1_En | Output Control overrides OE# pin | RW   | Hi-Z | Enable | 1       |

| Bit 0 | 17/18   | DIF_0_En | Output Control overrides OE# pin | RW   |      |        | 1       |

#### SMBusTable: Output Control Register

| Byte  | 2 Pin # | Name      | Control Function                 | Type | 0    | 1      | Default |

|-------|---------|-----------|----------------------------------|------|------|--------|---------|

| Bit 7 | 56/57   | DIF_15_En | Output Control overrides OE# pin | RW   | Hi-Z | Enable | 1       |

| Bit 6 |         |           | Reserved                         |      |      |        | 1       |

| Bit 5 | 53/54   | DIF_13_En | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 4 | 49/50   | DIF_12_En | Output Control overrides OE# pin | RW   | Hi-Z | Enable | 1       |

| Bit 3 | 46/47   | DIF_11_En | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 2 | 43/44   | DIF_10_En | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 1 |         |           | Reserved                         |      |      |        | 1       |

| Bit 0 | 37/38   | DIF_8_En  | Output Control overrides OE# pin | RW   | Hi-Z | Enable | 1       |

#### SMBusTable: Output Enable Pin Status Readback Register

| Byte  | e 3 Pin # | Name    | Control Function            | Туре | 0           | 1            | Default   |

|-------|-----------|---------|-----------------------------|------|-------------|--------------|-----------|

| Bit 7 | 51        | OE_RB12 | Real Time readback of OE#12 | R    |             |              | Real time |

| Bit 6 | 48        | OE_RB11 | Real Time readback of OE#11 | R    | OE# pin Low | OE# Pin High | Real time |

| Bit 5 | 45        | OE_RB10 | Real Time readback of OE#10 | R    |             |              | Real time |

| Bit 4 |           |         | Reserved                    |      |             |              | 0         |

| Bit 3 | 39        | OE_RB8  | Real Time readback of OE#8  | R    |             |              | Real time |

| Bit 2 | 36        | OE_RB7  | Real Time readback of OE#7  | R    | OE# pin Low | OE# Pin High | Real time |

| Bit 1 | 33        | OE_RB6  | Real Time readback of OE#6  | R    |             |              | Real time |

| Bit 0 | 30        | OE_RB5  | Real Time readback of OE#5  | R    |             |              | Real time |

#### SMBusTable: Reserved Register

| Byte 4 | 4 | Pin # | Name | Control Function | Туре | 0 | 1 | Default |  |  |

|--------|---|-------|------|------------------|------|---|---|---------|--|--|

| Bit 7  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 6  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 5  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 4  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 3  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 2  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 1  |   |       |      | Reserved         |      |   |   |         |  |  |

| Bit 0  |   |       |      | Reserved         |      |   |   |         |  |  |

#### SMBusTable: Vendor & Revision ID Register

| Byte  | 95 Pin # | Name | Control Function | Type | 0              | 1            | Default |  |

|-------|----------|------|------------------|------|----------------|--------------|---------|--|

| Bit 7 | -        | RID3 |                  |      | R              |              | Х       |  |

| Bit 6 | -        | RID2 |                  |      | R B rev = 0001 |              |         |  |

| Bit 5 | -        | RID1 |                  |      | C rev          | C rev = 0010 |         |  |

| Bit 4 | -        | RID0 |                  |      |                |              | Х       |  |

| Bit 3 | -        | VID3 |                  | R    | -              | -            | 0       |  |

| Bit 2 | -        | VID2 |                  | R    | -              | -            | 0       |  |

| Bit 1 | -        | VID1 | VENDOR ID        | R    | -              | -            | 0       |  |

| Bit 0 | -        | VID0 |                  | R    | -              | -            | 1       |  |

#### SMBusTable: DEVICE ID

| Byte  | e 6 Pin # | Name | Control Function  | Туре | 0                 | 1              | Default |  |   |

|-------|-----------|------|-------------------|------|-------------------|----------------|---------|--|---|

| Bit 7 | -         |      | Device ID 7 (MSB) |      | Device ID 7 (MSB) |                |         |  | 1 |

| Bit 6 | -         |      | Device ID 6       |      | R                 |                | 1       |  |   |

| Bit 5 | -         |      | Device ID 5       |      | 7                 |                | 0       |  |   |

| Bit 4 | -         |      | Device ID 4       |      | Device ID is 2    | 219 decimal or | 1       |  |   |

| Bit 3 | -         |      | Device ID 3       | R    | DB                | hex.           | 1       |  |   |

| Bit 2 | -         |      | Device ID 2       | R    |                   |                | 0       |  |   |

| Bit 1 | -         |      | Device ID 1       |      |                   |                | 1       |  |   |

| Bit 0 | -         |      | Device ID 0       | R    |                   |                | 1       |  |   |

#### SMBusTable: Byte Count Register

| Byte  | e7 Pin # | Name | Control Function                        | Туре | 0                | 1                 | Default |  |  |

|-------|----------|------|-----------------------------------------|------|------------------|-------------------|---------|--|--|

| Bit 7 |          |      | Reserved                                |      |                  |                   |         |  |  |

| Bit 6 |          |      | Reserved                                |      |                  |                   |         |  |  |

| Bit 5 |          |      | Reserved                                |      |                  |                   |         |  |  |

| Bit 4 | -        | BC4  |                                         | RW   |                  |                   | 0       |  |  |

| Bit 3 | -        | BC3  | Writing to this register configures how | RW   | Default value    | is 8 hex, so 9    | 1       |  |  |

| Bit 2 | -        | BC2  |                                         | RW   | bytes (0 to 8) v | vill be read back | 0       |  |  |

| Bit 1 | -        | BC1  | many bytes will be read back.           | RW   | by de            | efault.           | 0       |  |  |

| Bit 0 | -        | BC0  |                                         | RW   | -                |                   | 0       |  |  |

#### SMBusTable: Reserved Register

| Byte 8 | 8 Pin | ŧ | Name     | Control Function | Type | 0 | 1 | Default |  |  |  |

|--------|-------|---|----------|------------------|------|---|---|---------|--|--|--|

| Bit 7  |       |   | Reserved |                  |      |   |   |         |  |  |  |

| Bit 6  |       |   |          | Reserved         |      |   |   |         |  |  |  |

| Bit 5  |       |   |          | Reserved         |      |   |   |         |  |  |  |

| Bit 4  |       |   | Reserved |                  |      |   |   |         |  |  |  |

| Bit 3  |       |   | Reserved |                  |      |   |   |         |  |  |  |

| Bit 2  |       |   |          | Reserved         |      |   |   |         |  |  |  |

| Bit 1  |       |   | Reserved |                  |      |   |   |         |  |  |  |

| Bit 0  |       |   |          | Reserved         |      |   |   |         |  |  |  |

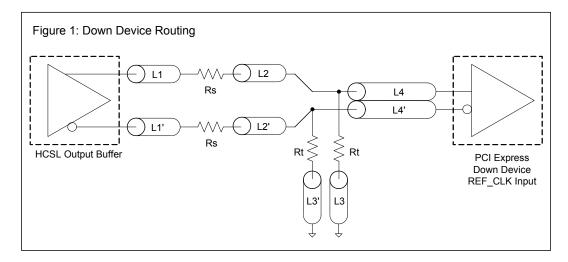

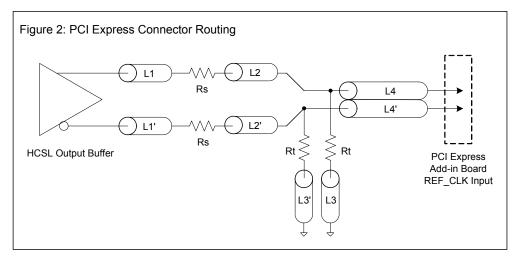

| DIF Reference Clock                             |                    |      |        |  |  |  |  |  |  |

|-------------------------------------------------|--------------------|------|--------|--|--|--|--|--|--|

| Common Recommendations for Differential Routing | Dimension or Value | Unit | Figure |  |  |  |  |  |  |

| L1 length, route as non-coupled 50ohm trace     | 0.5 max            | inch | 1      |  |  |  |  |  |  |

| L2 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |  |  |  |  |  |  |

| L3 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |  |  |  |  |  |  |

| Rs                                              | 33                 | ohm  | 1      |  |  |  |  |  |  |

| Rt                                              | 49.9               | ohm  | 1      |  |  |  |  |  |  |

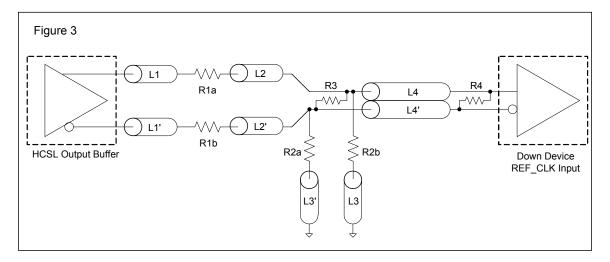

| Down Device Differential Routing                                 |                     |      |   |

|------------------------------------------------------------------|---------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 2 min to 16 max     | inch | 1 |

| L4 length, route as coupled stripline 100ohm differential trace  | 1.8 min to 14.4 max | inch | 1 |

| Differential Routing to PCI Express Connector                    |                       |      |   |

|------------------------------------------------------------------|-----------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 0.25 to 14 max        | inch | 2 |

| L4 length, route as coupled stripline 100ohm differential trace  | 0.225 min to 12.6 max | inch | 2 |

|              | Alternative Termination for LVDS and other Common Differential Signals (figure 3) |      |    |      |      |     |                                |  |  |

|--------------|-----------------------------------------------------------------------------------|------|----|------|------|-----|--------------------------------|--|--|

| Vdiff        | Vp-р                                                                              | Vcm  | R1 | R2   | R3   | R4  | Note                           |  |  |

| 0.45v        | 0.22v                                                                             | 1.08 | 33 | 150  | 100  | 100 |                                |  |  |

| 0.58         | 0.28                                                                              | 0.6  | 33 | 78.7 | 137  | 100 |                                |  |  |

| 0.80         | 0.40                                                                              | 0.6  | 33 | 78.7 | none | 100 | ICS874003i-02 input compatible |  |  |

| 0.60         | 0.3                                                                               | 1.2  | 33 | 174  | 140  | 100 | Standard LVDS                  |  |  |

| $D_{1a} = D$ |                                                                                   |      |    |      |      |     |                                |  |  |

R1a = R1b = R1

R2a = R2b = R2

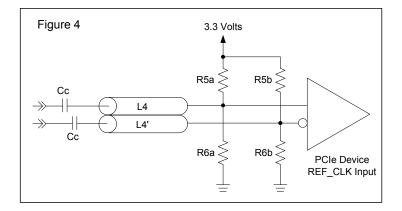

| Cable Connected AC Coupled Application (figure 4) |             |      |  |  |  |  |

|---------------------------------------------------|-------------|------|--|--|--|--|

| Component                                         | Value       | Note |  |  |  |  |

| R5a, R5b                                          | 8.2K 5%     |      |  |  |  |  |

| R6a, R6b                                          | 1K 5%       |      |  |  |  |  |

| Cc                                                | 0.1 µF      |      |  |  |  |  |

| Vcm                                               | 0.350 volts |      |  |  |  |  |

15

IDT® FIFTEEN OUTPUT DIFFERENTIAL ZBUFFER FOR PCIE GEN2/3 AND QPI

### **Marking Diagram**

Notes:

- 1. "LOT" is the lot number.

- 2. "COO" is the country of origin.

- 2. "YYWW" is the last two digits of the year and week that the part was assembled.

- 3. "L" denotes RoHS compliant package.

#### (Ref) Seating Plane (N<sub>D</sub>-1)x e N<sub>D</sub> & N<sub>E</sub> (Ref) Even Index Area A1 (Typ) A3 N If $N_D \& N_E$ 2 Anvil are Even Singulation (N<sub>E</sub>-1)x e Е -- or --E2 (Ref) E2 2 ¥. Top View Sawn Singulation Δ (Ref) D $N_D \& N_E$ е Thermal Base Odd D2 С -D2-0.08 С $\frown$ Millimeters Symbol Min Max 0.8 1.0 А 0.05 A1 0 A3 0.25 Reference

0.18

6.00

6.00

0.30

0.50 BASIC

9.00 x 9.00

16

16

64

0.3

6.25

6.25

0.50

17

### Package Outline and Package Dimensions (64-pin MLF)

### **Ordering Information**

| Part / Order Num | ber Shipping | Package Packag   | e Temperature |

|------------------|--------------|------------------|---------------|

| 9ZX21501CKLF     | Tray         | ys 64-pin M      | LF 0 to +70°C |

| 9ZX21501CKLF     | T Tape an    | id Reel 64-pin M | LF 0 to +70°C |

b

e D x E BASIC

D2 MIN./MAX.

E2 MIN./MAX.

L MIN./MAX.

ND

N<sub>E</sub> N

#### "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

"C" is the device revision designator (will not correlate with the datasheet revision).

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

### **Revision History**

| Rev. | Issue Date    | Who                               | Description                                                                           | Page # |  |

|------|---------------|-----------------------------------|---------------------------------------------------------------------------------------|--------|--|

| Α    | 8/3/2010      | RDW                               | Move to final.                                                                        |        |  |

|      |               |                                   | dded note to pinout indicating that DFB_OUT pins need to be terminated identically    |        |  |

| В    | 5/11/2011     | RDW                               | to normal DIF outputs.                                                                | 2      |  |

| С    | 12/8/2011     | RDW                               | 1. Updated tDSPO_BYP parameter from +/-350 to +/-250ps                                | 7      |  |

| D    | 12/15/2011    | RDW                               | 1. Lowered IDD3.3OP from MAX 500mA/TYP 407mA to MAX 425mA/ TYP 390mA                  | 6      |  |

| D    | 12/15/2011    | RDW                               | 2. Lowered IDD3.3PDZ from MAX36mA/TYP 12mA to MAX 15mA/ TYP 5mA                       | 0      |  |

| F    | 4/23/2012     | RDW                               | 1. Updated Rp values on Output Terminations Table from 43.2 ohms to 42.2 or 43.2      | 9      |  |

| E    | 4/23/2012     | ohms to be consistent with Intel. |                                                                                       | 9      |  |

| F    | 4/16/2013     | RDW                               | Corrected typo in OE# Latency parameter; changed 1 min. to 3 max. cycles to 4 min. to | 6      |  |

| Г    | 4/10/2013 RDW |                                   | 12 max. clocks                                                                        | 0      |  |

IDT® FIFTEEN OUTPUT DIFFERENTIAL ZBUFFER FOR PCIE GEN2/3 AND QPI

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>