**ON Semiconductor**

Is Now

# Onsemí

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# PLL Frequency Synthesizer for Electronic Tuning

#### Overview

The LC72121, LC72121M and LC72121V are high input sensitivity (20 mVrms at 130 MHz) PLL frequency synthesizers for 3 V systems. These ICs are serial data (CCB\*) compatible with the LC72131, and feature the improved input sensitivity and lower spurious radiation (provided by a redesigned ground system) required in high-performance AM/FM tuners.

#### Functions

- High-speed programmable divider

- FMIN: 10 to 160 MHz ... Pulse swallower technique (With built-in divide-by-2 prescaler)

- AMIN: 2 to 40 MHz ... Pulse swallower technique

0.5 to 10 MHz ... Direct division technique

- IF counter

- IFIN: 0.4 to 15 MHz ... For AM and FM IF counting

- Reference frequency

- One of 12 reference frequencies can be selected (using a 4.5 or 7.2 MHz crystal element)

- 1, 3, 5, 9, 10, 3.125, 6.25, 12.5, 15, 25, 50, and 100 kHz

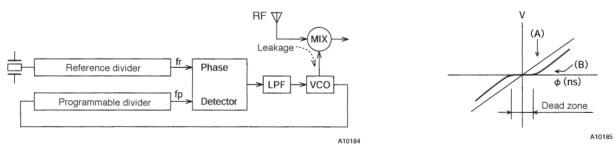

- Phase comparator

- Supports dead zone control.

- Built-in unlocked state detection circuit

- Built-in deadlock clear circuit

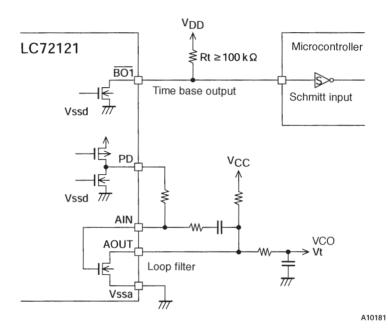

- An MOS transistor for an active low-pass filter is built in

- I/O ports

- Output-only ports: 4 pins

- I/O ports: 2 pins

- Supports the output of a clock time base signal

- Operating ranges

- Supply voltage: 2.7 to 3.6 V

- Operating temperature: 40 to 85°C

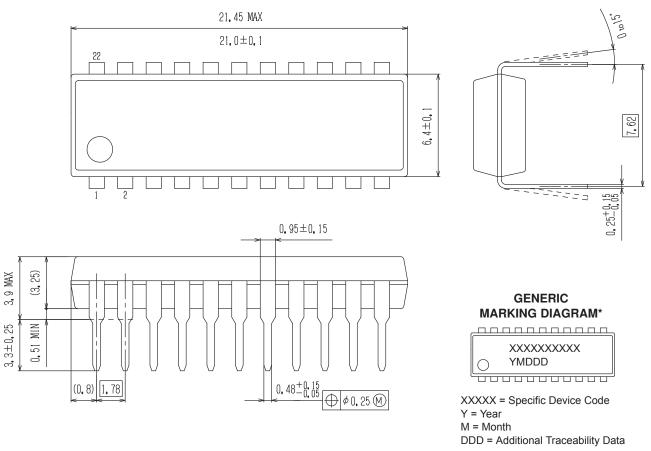

- Package

- DIP22S, MFP24S, SSOP24

ON

# **ON Semiconductor®**

www.onsemi.com

PDIP22 / DIP22S (300 mil) [LC72121]

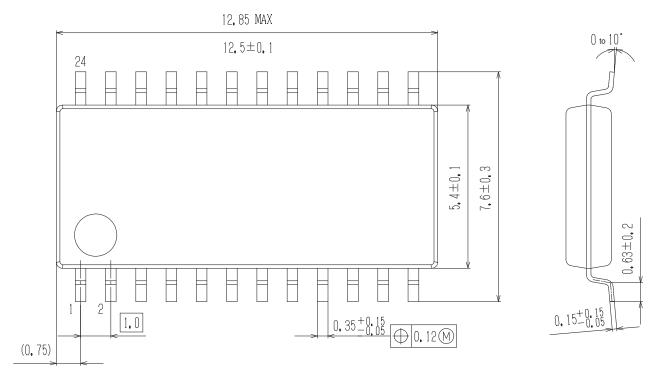

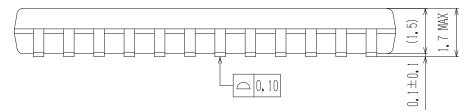

SOIC24 W / MFP24S (300 mil) [LC72121M]

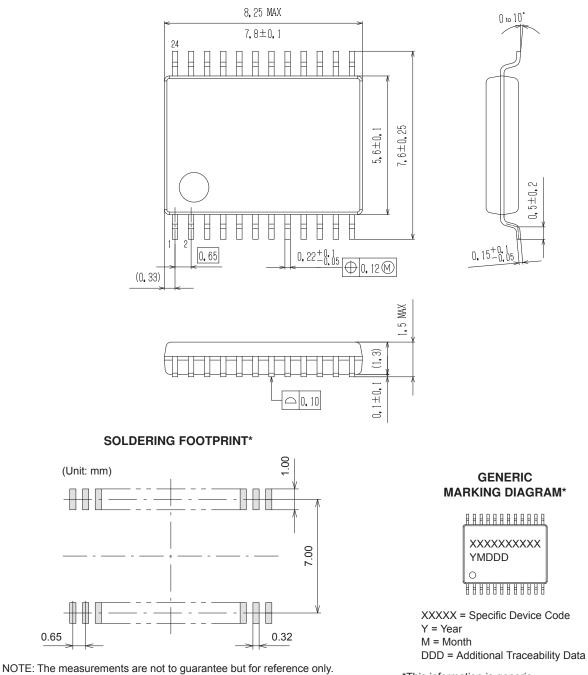

SSOP24 (275mil) [LC72121V]

\* Computer Control Bus (CCB) is an ON Semiconductor's original bus format and the bus addresses are controlled by ON Semiconductor.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 26 of this data sheet.

#### • Comparison with the LC72131/M

- Serial data compatible (CCB)

- Identical pin functions

- Two VSS pins were added

- The DIP version is pin compatible

- (VSS pins were inserted as the DIP22S NC pins)

- The MFP product provides a modified pin assignment

- (The MFP20 package was replaced by an MFP24 package, and extra VSS pins were added)

- The SSOP24 is a newly developed package that has the same pin assignment as the MFP24S product

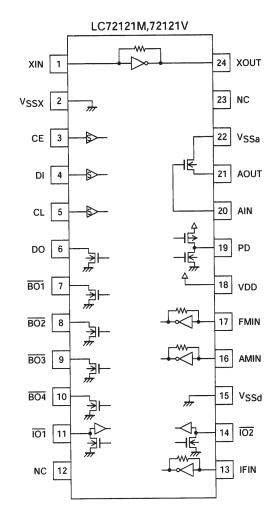

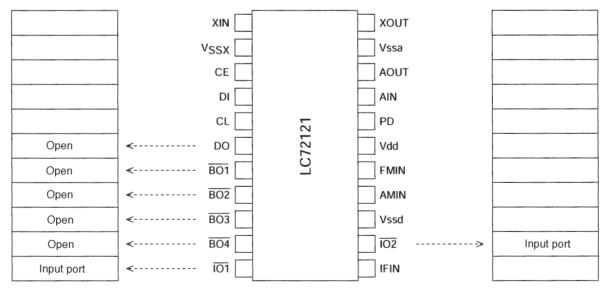

#### **Pin Assignment**

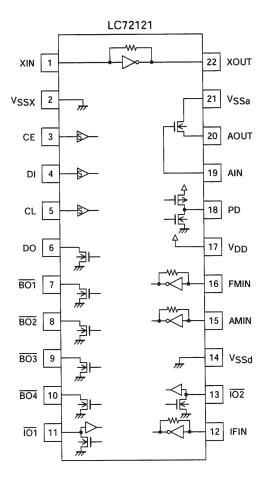

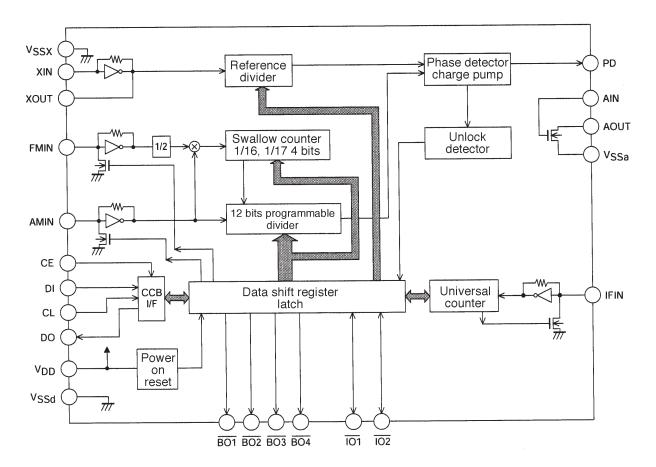

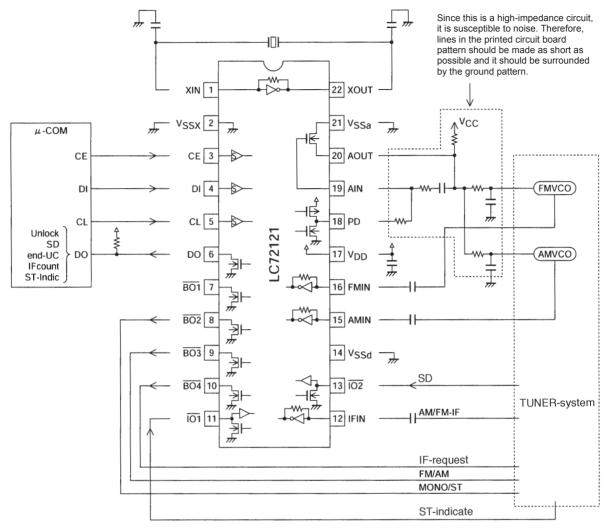

#### **Block Diagram**

#### Specifications Absolute Maximum Ratings at Ta = 25°C, V<sub>SSd</sub> = V<sub>SSa</sub>= V<sub>SSX</sub> = 0 V

| Parameter                   | Symbol                | Conditions                 |                              | Ratings      | Unit |

|-----------------------------|-----------------------|----------------------------|------------------------------|--------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max   | V <sub>DD</sub>            |                              | -0.3 to +7.0 | V    |

|                             | V <sub>IN</sub> 1 max | CE, DI, CL, AIN            | -0.3 to +7.0                 | V            |      |

| Maximum input voltage       | V <sub>IN</sub> 2 max | XIN, FMIN, AMIN, IFIN      | -0.3 to V <sub>DD</sub> +0.3 | V            |      |

|                             | V <sub>IN</sub> 3 max | ĪO1, ĪO2                   | -0.3 to +15                  | V            |      |

|                             | V <sub>O</sub> 1 max  | DO                         | -0.3 to +7.0                 | V            |      |

| Maximum output voltage      | V <sub>O</sub> 2 max  | XOUT, PD                   | -0.3 to V <sub>DD</sub> +0.3 | V            |      |

|                             | V <sub>O</sub> 3 max  | BO1 to BO4, IO1, IO2, AOUT | -0.3 to +15                  | V            |      |

| • • • • •                   | I <sub>O</sub> 1 max  | DO, AOUT                   | 0 to +6.0                    | mA           |      |

| Maximum output current      | I <sub>O</sub> 2 max  | BO1 to BO4, IO1, IO2       |                              | 0 to +10.0   | mA   |

|                             |                       |                            | DIP22S:                      | 350          | mW   |

| Allowable power dissipation | Pd max                | (Ta ≤ 85°C)                | MFP24S:                      | 200          | mW   |

|                             |                       |                            | SSOP24:                      | 150          | mW   |

| Operating temperature       | Topr                  |                            |                              | -40 to +85   | °C   |

| Storage temperature         | Tstg                  |                            |                              | -55 to +125  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Allowable Operating Ranges at Ta = -40 to $+85^{\circ}$ C, V<sub>SSd</sub> = V<sub>SSa</sub> = V<sub>SSX</sub> = 0 V

| Deremeter                               | Ourseland           | Conditions                        |                     | Ratings |                     | - Unit |

|-----------------------------------------|---------------------|-----------------------------------|---------------------|---------|---------------------|--------|

| Parameter                               | Symbol              | Conditions                        | min                 | typ     | max                 |        |

| Supply voltage                          | V <sub>DD</sub>     | V <sub>DD</sub>                   | 2.7                 |         | 3.6                 | V      |

| Innut high lovel veltage                | V <sub>IH</sub> 1   | CE, DI, CL                        | 0.7 V <sub>DD</sub> |         | 6.5                 | V      |

| Input high-level voltage                | V <sub>IH</sub> 2   | <u>101, 102</u>                   | 0.7 V <sub>DD</sub> |         | 13                  | V      |

| Input low-level voltage                 | V <sub>IL</sub>     | CE, DI, CL, IO1, IO2              | 0                   |         | 0.3 V <sub>DD</sub> | V      |

| Output veltage                          | V <sub>O</sub> 1    | DO                                | 0                   |         | 6.5                 | V      |

| Output voltage                          | V <sub>O</sub> 2    | BO1 to BO4, IO1, IO2, AOUT        | 0                   |         | 13                  | V      |

|                                         | f <sub>IN</sub> 1   | XIN: V <sub>IN</sub> 1            | 1                   |         | 8                   | MHz    |

|                                         | f <sub>IN</sub> 2   | FMIN: V <sub>IN</sub> 2           | 10                  |         | 160                 | MHz    |

| Input frequency                         | f <sub>IN</sub> 3   | AMIN (SNS = 1): V <sub>IN</sub> 3 | 2                   |         | 40                  | MHz    |

|                                         | f <sub>IN</sub> 4   | AMIN (SNS = 0): $V_{IN}4$         | 0.5                 |         | 10                  | MHz    |

|                                         | f <sub>IN</sub> 5   | IFIN: V <sub>IN</sub> 5           | 0.4                 |         | 15                  | MHz    |

|                                         | V <sub>IN</sub> 1   | XIN: f <sub>IN</sub> 1            | 200                 |         | 800                 | mVrms  |

|                                         | V <sub>IN</sub> 2-1 | FMIN: f = 10 to 130 MHz           | 20                  |         | 800                 | mVrms  |

|                                         | V <sub>IN</sub> 2-2 | FMIN: f = 130 to 160 MHz          | 40                  |         | 800                 | mVrms  |

| Input amplitude                         | V <sub>IN</sub> 3   | AMIN (SNS = 1): f <sub>IN</sub> 3 | 40                  |         | 800                 | mVrms  |

|                                         | V <sub>IN</sub> 4   | AMIN (SNS = 0): f <sub>IN</sub> 4 | 40                  |         | 800                 | mVrms  |

|                                         | V <sub>IN</sub> 5-1 | IFIN: f <sub>IN</sub> 5, IFS = 1  | 40                  |         | 800                 | mVrms  |

|                                         | V <sub>IN</sub> 5-2 | IFIN: f <sub>IN</sub> 5, IFS = 0  | 70                  |         | 800                 | mVrms  |

| Guaranteed crystal oscillator frequency | Xtal                | XIN, XOUT: *                      | 4                   |         | 8                   | MHz    |

Note: Recommended value for CI for the crystal oscillator element: CI  $\leq$  120 $\Omega$  (4.5MHz), CI  $\leq$  70 $\Omega$  (7.2MHz)

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Electrical Characteristics in the Allowable Operating Ranges

| Parameter                     | Cumbal            | Conditions                 | Ratings               |                     |     | Unit |  |

|-------------------------------|-------------------|----------------------------|-----------------------|---------------------|-----|------|--|

| Parameter                     | Symbol            | Conditions                 | min                   | typ                 | max | Unit |  |

|                               | Rf1               | XIN                        |                       | 1                   |     | MΩ   |  |

| Internal feedback resistance  | Rf2               | FMIN                       |                       | 500                 |     | kΩ   |  |

|                               | Rf3               | AMIN                       |                       | 500                 |     | kΩ   |  |

|                               | Rf4               | IFIN                       |                       | 250                 |     | kΩ   |  |

| Internal pull-down resistance | Rpd1              | FMIN                       | 100                   | 200                 | 400 | kΩ   |  |

|                               | Rpd2              | AMIN                       | 100                   | 200                 | 400 | kΩ   |  |

| Hysteresis                    | V <sub>HIS</sub>  | CE, DI, CL                 |                       | 0.1 V <sub>DD</sub> |     | V    |  |

| Output high-level voltage     | V <sub>OH</sub> 1 | PD: I <sub>O</sub> = -1 mA | V <sub>DD</sub> – 1.0 |                     |     | V    |  |

Continued on next page.

Continued from preceding page.

| Parameter                              | Symbol             | Conditions                                                                                                                           |     | Ratings |     | Unit |

|----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| Falameter                              | Symbol             | Conditions                                                                                                                           | min | typ     | max |      |

|                                        | V <sub>OL</sub> 1  | PD: I <sub>O</sub> = 1 mA                                                                                                            |     |         | 1.0 | V    |

|                                        |                    | $\overline{\text{BO1}}$ to $\overline{\text{BO4}}$ , $\overline{\text{IO1}}$ , $\overline{\text{IO2}}$ : I <sub>O</sub> = 1 mA       |     |         | 0.2 | V    |

| Output low-level voltage               | V <sub>OL</sub> 2  | $\overline{\text{BO1}}$ to $\overline{\text{BO4}}$ , $\overline{\text{IO1}}$ , $\overline{\text{IO2}}$ : I <sub>O</sub> = 8 mA       |     |         | 1.6 | V    |

|                                        |                    | DO: I <sub>O</sub> = 1 mA                                                                                                            |     |         | 0.2 | V    |

|                                        | V <sub>OL</sub> 3  | DO: I <sub>O</sub> = 5 mA                                                                                                            |     |         | 1.0 | V    |

|                                        | V <sub>OL</sub> 4  | AOUT: I <sub>O</sub> = 1 mA, AIN = 1.3 V                                                                                             |     |         | 0.5 | V    |

|                                        | I <sub>IH</sub> 1  | CE, DI, CL: V <sub>I</sub> = 6.5 V                                                                                                   |     |         | 5.0 | μA   |

|                                        | I <sub>IH</sub> 2  | <u>IO1</u> , <u>IO2</u> : V <sub>I</sub> = 13 V                                                                                      |     |         | 5.0 | μA   |

| Innut bird lovel ourrest               | I <sub>IH</sub> 3  | $XIN: V_1 = V_{DD}$                                                                                                                  | 1.3 |         | 8   | μA   |

| Input high-level current               | I <sub>IH</sub> 4  | FMIN, AMIN: V <sub>I</sub> = V <sub>DD</sub>                                                                                         | 2.5 |         | 15  | μA   |

|                                        | I <sub>IH</sub> 5  | IFIN: VI = VDD                                                                                                                       | 5.0 |         | 30  | μA   |

|                                        | I <sub>IH</sub> 6  | AIN: V <sub>1</sub> = 6.5 V                                                                                                          |     |         | 200 | nA   |

|                                        | I <sub>IL</sub> 1  | CE, DI, CL: VI = 0 V                                                                                                                 |     |         | 5.0 | μA   |

|                                        | I <sub>IL</sub> 2  | $\overline{IO1}, \overline{IO2}: V_I = 0 V$                                                                                          |     |         | 5.0 | μA   |

| Input low-level current                | I <sub>IL</sub> 3  | $XIN: V_1 = 0 V$                                                                                                                     | 1.3 |         | 8   | μA   |

| Input low-level current                | I <sub>IL</sub> 4  | FMIN, AMIN: $V_1 = 0 V$                                                                                                              | 2.5 |         | 15  | μA   |

|                                        | I <sub>IL</sub> 5  | IFIN: VI = 0 V                                                                                                                       | 5.0 |         | 30  | μA   |

|                                        | I <sub>IL</sub> 6  | AIN: $V_1 = 0 V$                                                                                                                     |     |         | 200 | nA   |

| Output off leakage current             | I <sub>OFF</sub> 1 | $\overline{\text{BO1}}$ to $\overline{\text{BO4}}$ , $\overline{\text{IO1}}$ , $\overline{\text{IO2}}$ , AOUT: V <sub>O</sub> = 13 V |     |         | 5.0 | μA   |

| Output on leakage current              | I <sub>OFF</sub> 2 | DO: V <sub>O</sub> = 6.5 V                                                                                                           |     |         | 5.0 | μA   |

| High-level 3-state off leakage current | I <sub>OFFH</sub>  | PD: $V_0 = V_{DD}$                                                                                                                   |     | 0.01    | 200 | nA   |

| Low-level 3-state off leakage current  | IOFFL              | PD: $V_0 = 0 V$                                                                                                                      |     | 0.01    | 200 | nA   |

| Input capacitance                      | C <sub>IN</sub>    | FMIN                                                                                                                                 |     | 6       |     | pF   |

|                                        | I <sub>DD</sub> 1  | $V_{DD}$ : Xtal = 7.2 MHz, f <sub>IN</sub> 2 = 130 MHz,<br>$V_{IN}2$ = 20 mVrms                                                      |     | 2.5     | 6   | mA   |

| Supply current                         | I <sub>DD</sub> 2  | V <sub>DD</sub> : PLL block stopped (PLL inhibit mode)<br>Crystal oscillator operating<br>(crystal frequency: 7.2 MHz)               |     | 0.3     |     | mA   |

|                                        | I <sub>DD</sub> 3  | V <sub>DD</sub> : PLL block stopped, crystal oscillator stopped                                                                      |     |         | 10  | μA   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **Pin Descriptions**

| Pin         | Pin I   | No.                  | Turne               | Function                                                                                                                                                           |                    |

|-------------|---------|----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| name        | LC72121 | LC72121M<br>LC72121V | Туре                | Function                                                                                                                                                           | Equivalent circuit |

| XIN<br>XOUT | 1<br>22 | 1<br>24              | Xtal                | Crystal oscillator element connections (4.5 or 7.2 MHz)                                                                                                            | A10146             |

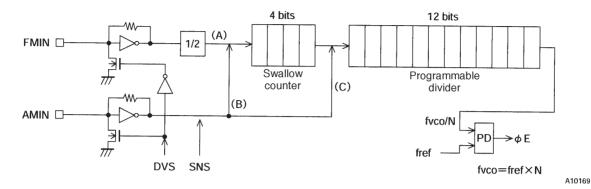

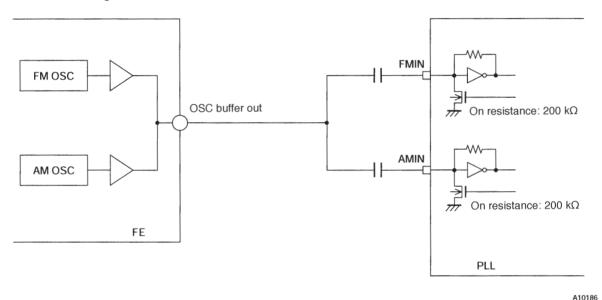

|             |         |                      |                     | <ul> <li>FMIN is selected when DVS in the serial data is set to 1.</li> </ul>                                                                                      |                    |

|             |         |                      |                     | Input frequency: 10 to 160 MHz                                                                                                                                     |                    |

| FMIN        | 16      | 17                   | oscillator          | • The signal is passed through an internal divide-by-two prescaler and then input to the swallow counter.                                                          |                    |

|             |         |                      |                     | • The divisor can be set to a value in the range 272 to 65535. Since the internal divide-by-two prescaler is used, the actual divisor will be twice the set value. | 7/7<br>A10147      |

|             |         |                      |                     | AMIN is selected when DVS in the serial data is set to 0.                                                                                                          |                    |

|             |         |                      |                     | When SNS in the serial data is set to 1:                                                                                                                           |                    |

|             |         |                      |                     | Input frequency: 2 to 40 MHz                                                                                                                                       |                    |

|             |         |                      |                     | <ul> <li>The signal is input to the swallow counter directly.</li> </ul>                                                                                           |                    |

| AMIN        | 15      | 16                   | Local<br>oscillator | • The divisor can be set to a value in the range 272 to 65535. The set value becomes the actual divisor.                                                           |                    |

|             |         |                      | signal input        | When SNS in the serial data is set to 0:                                                                                                                           | <u> </u>           |

|             |         |                      |                     | Input frequency: 0.5 to 10 MHz                                                                                                                                     |                    |

|             |         |                      |                     | <ul> <li>The signal is input to a 12-bit programmable divider directly.</li> </ul>                                                                                 | A10148             |

|             |         |                      |                     | • The divisor can be set to a value in the range 4 to 4095. The set value becomes the actual divisor.                                                              |                    |

Continued on next page.

Continued from preceding page.

| Pin                      | Pin I             | No.                  | -                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

|--------------------------|-------------------|----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| name                     | LC72121           | LC72121M<br>LC72121V | Туре                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Equivalent circuit |

| CE                       | 3                 | 3                    | Chip enable                                | <ul> <li>This pin must be set high to enable serial data input (DI) or serial<br/>data output (DO).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A10149             |

| DI                       | 4                 | 4                    | Input data                                 | Input for serial data transferred from the controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A10150             |

| CL                       | 5                 | 5                    | Clock                                      | <ul> <li>Clock used for data synchronization for serial data input (DI) and<br/>serial data output (DO).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | □\$>>><br>A10151   |

| DO                       | 6                 | 6                    | Output data                                | <ul> <li>Output for serial data transmitted to the controller. The content of the<br/>data transmitted is determined by DOC0 through DOC2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |

| V <sub>DD</sub>          | 17                | 18                   | Power supply                               | LC72121 power supply (V <sub>DD</sub> 2.7 to 3.6 V)     The power on reset circuit operates when power is first applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

| V <sub>SSX</sub>         | 2                 | 2                    | Ground                                     | Ground for the crystal oscillator circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |

| V <sub>SSA</sub>         | 21                | 22                   | Ground                                     | Ground for the low-pass filter MOS transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

|                          |                   |                      |                                            | Ground for the LC72121 digital systems other than those that use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

| V <sub>SSd</sub>         | 14                | 15                   | Ground                                     | $V_{SSa}$ or $V_{SSX}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |

| 101<br>102               | 11<br>13          | 11<br>14             | I/O port                                   | <ul> <li>Shared function I/O ports</li> <li>The pin function is determined by IOC1 and IOC2 in the serial data.<br/>When the data value 0: Input port</li> <li>When the data value 1: Output port</li> <li>When specified to function as an input port:<br/>The input pin state is reported to the controller through the DO pin.<br/>When the input state is low: The data will be 0:<br/>When the input state is low: The data will be 1:</li> <li>When specified to function as an output port:<br/>The output state is determined by IO1 and IO2 in the serial data.<br/>When the data value is 0: The output state will be the open circuit state.<br/>When the data value is 1: The output state will be a low level.</li> <li>These pins are set to input mode after a power on reset.</li> </ul> | A10153             |

| BO1<br>BO2<br>BO3<br>BO4 | 7<br>8<br>9<br>10 | 7<br>8<br>9<br>10    | Output port                                | <ul> <li>Output-only ports</li> <li>The output state is determined by BO1 through BO4 in the serial data.</li> <li>When the data value is 0: The output state will be the open circuit state.</li> <li>When the data value is 1: The output state will be a low level.</li> <li>A time base signal (8 Hz) is output from BO1 when TBC in the serial data is set to 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

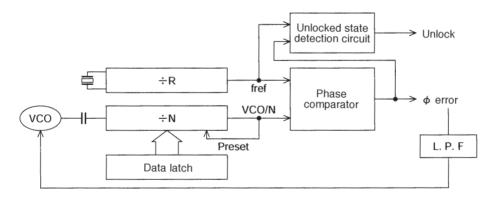

| PD                       | 18                | 19                   | Charge pump<br>output                      | <ul> <li>PLL charge pump output         A high level is output when the frequency of the local oscillator signal divided by N is higher than the reference frequency, and a low level is output when that frequency is lower. This pin goes to the high-impedance state when the frequencies match.     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A10155             |

| AIN<br>AOUT              | 19<br>20          | 20<br>21             | Low-pass filter<br>amplifier<br>transistor | Connections for the MOS transistor used for the PLL active low-pass filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |

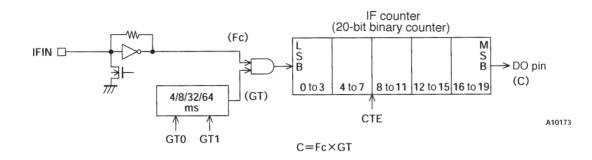

| IFIN                     | 12                | 13                   | IF counter                                 | <ul> <li>The input frequency range is 0.4 to 15 MHz</li> <li>The signal is passed directly to the IF counter.</li> <li>The result is output, MSB first, through the DO pin.</li> <li>Four measurement periods are supported: 4, 8, 32, and 64 ms.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A10157             |

| NC                       |                   | 12<br>23             | NC pin                                     | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |

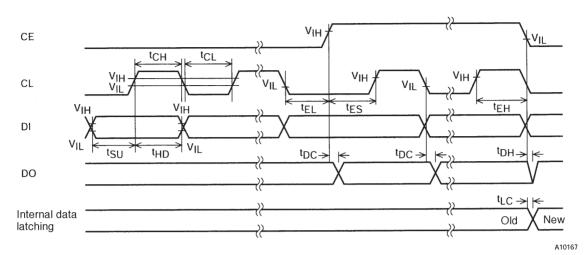

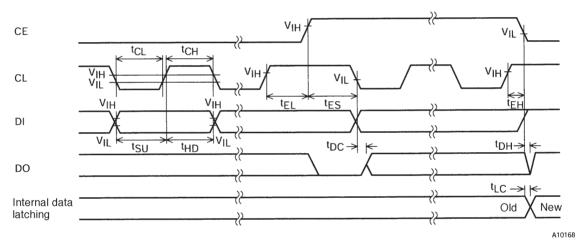

## Procedures for Input and Output of Serial Data

This product uses the CCB (Computer Control Bus), which is original audio product serial bus format, for data input and output. This product adopts an 8-bit address CCB format.

| $\square$ | 1/O mada |               |    |    | Add | lress |    |              |    | Eurofian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|-----------|----------|---------------|----|----|-----|-------|----|--------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|           | I/O mode | B0            | B1 | B2 | B3  | A0    | A1 | A2           | A3 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 1         | IN1 (82) | 0             | 0  | 0  | 1   | 0     | 1  | 0            | 0  | <ul> <li>Control data input (serial data input) mode</li> <li>24 bits of data are input.</li> <li>See the "DI Control Data (serial data input)" section for details on the content of the input data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 2         | IN2 (92) | 1             | 0  | 0  | 1   | 0     | 1  | 0            | 0  | <ul> <li>Control data input (serial data input) mode</li> <li>24 bits of data are input.</li> <li>See the "DI Control Data (serial data input)" section for details on the content of the input data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 3         | OUT (A2) | 0             | 1  | 0  | 1   | 0     | 1  | 0            | 0  | <ul> <li>Data output (serial data output) mode</li> <li>The number of bits output is equal to the number of clock cycles.</li> <li>See the "DO output Data (serial data output)" section for details on the content of the output data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| C         | @        | <u></u><br>Во |    |    | B2  | B3    |    | ) <b>X</b> , |    | I/O mode determined         I/O mode determin |  |  |  |  |  |  |

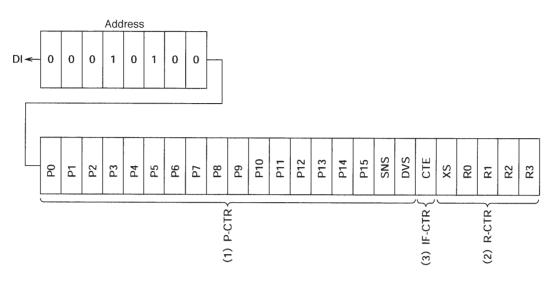

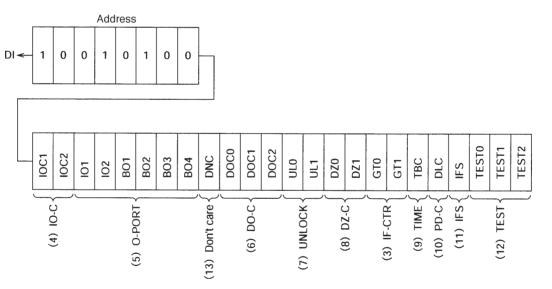

Structure of the DI Control Data (serial data input)

• IN1 mode

• IN2 mode

A10160

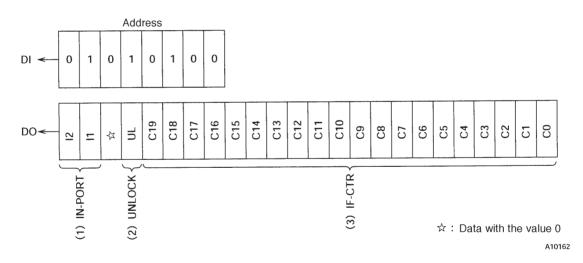

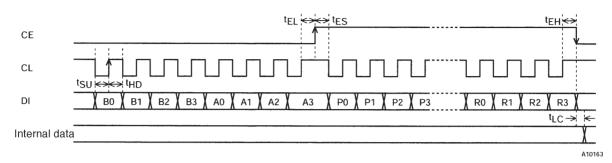

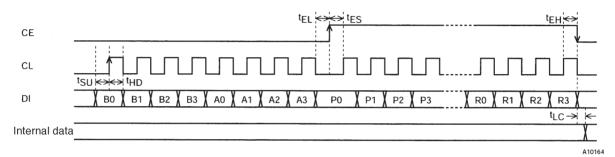

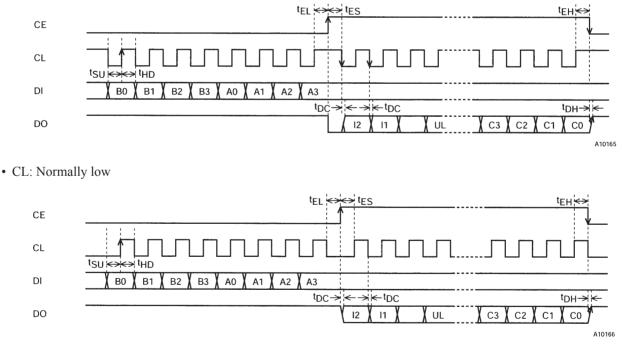

#### **DI Control Data**

| No. | Control block/data           |          |          |                  |         |         |               | F                | unction          |                  |                                         | Related data |

|-----|------------------------------|----------|----------|------------------|---------|---------|---------------|------------------|------------------|------------------|-----------------------------------------|--------------|

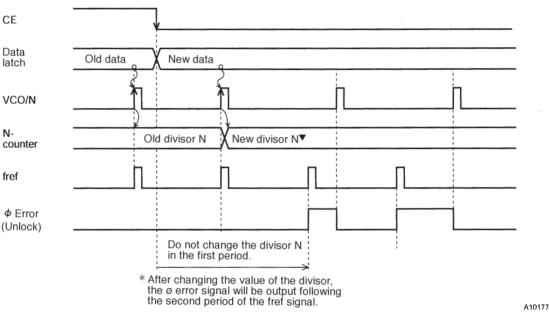

|     |                              | •        | Spec     | ifies th         | ne div  | isor fo | or the progra | ammable divide   | :                |                  |                                         |              |

|     |                              | •        | This i   | is a bir         | nary v  | alue i  | in which P1   | 5 is the MSB. T  | ne LSB change    | es depending or  | DVS and SNS.                            |              |

|     |                              |          |          |                  |         |         |               |                  | (* : do          | on't care)       |                                         |              |

|     |                              |          | D        | VS               | SI      | NS      | LSB           | Set divisor (N   | ) Actual d       | livisor          |                                         |              |

|     |                              |          |          | 1                |         | *       | P0            | 272 to 65535     | Twice the s      | set value        |                                         |              |

|     |                              |          |          | 0                |         | 1       | P0            | 272 to 65535     | The set          | value            |                                         |              |

|     |                              |          |          | 0                |         | 0       | P4            | 4 to 4095        | The set          | value            |                                         |              |

|     | Programmable<br>divider data | *        | I SB-    | When             | P4 is   | the l   | SB P0 to I    | P3 are ignored.  |                  |                  |                                         |              |

| 1   | P0 to P15                    | '        | LOD.     | which            | 11 4 10 |         | -00,10101     | o are ignored.   |                  |                  |                                         |              |

| '   | DVS, SNS                     |          |          |                  |         |         | signal input  | to the program   | mable divider (I | FMIN or AMIN)    | and switch the input                    |              |

|     |                              | 1        | frequ    | ency r           | ange.   |         |               |                  |                  |                  |                                         |              |

|     |                              |          |          |                  |         |         |               |                  |                  | (* : don't care) |                                         |              |

|     |                              |          | D        | VS               | SI      | NS      | Input pin     | Frequency rar    | ge accepted b    | y the input pin  |                                         |              |

|     |                              |          |          | 1                |         | *       | FMIN          |                  | 10 to 160 MHz    |                  |                                         |              |

|     |                              |          |          | 0                |         | 1       | AMIN          |                  | 2 to 40 MHz      |                  |                                         |              |

|     |                              |          |          | 0                |         | 0       | AMIN          |                  | 0.5 to 10 MHz    |                  |                                         |              |

|     |                              | * 9      | See t    | he "St           | ructu   | re of t | he Program    | mable Divider"   | section for deta | aile             |                                         |              |

|     |                              | `        |          |                  | luciu   |         | ne i rogran   |                  |                  |                  |                                         |              |

|     |                              | •        | Refer    | ence             | freque  | ency s  | selection     |                  |                  |                  |                                         |              |

|     |                              |          | R3       | R2               | R1      | R0      | Re            | ference frequen  | CV.              |                  |                                         |              |

|     |                              |          | 0        | 0                | 0       | 0       | 1.0           | 100 kHz          | -                |                  |                                         |              |

|     |                              |          | 0        | 0                | 0       | 1       |               | 50               |                  |                  |                                         |              |

|     |                              |          | 0        | 0                | 1       | 0       |               | 25               |                  |                  |                                         |              |

|     |                              |          | 0        | 0                | 1       | 1       |               | 25               |                  |                  |                                         |              |

|     |                              |          |          | 12.5             |         |         |               |                  |                  |                  |                                         |              |

|     |                              |          | 0        | 1                | 0       | 1       |               | 6.25             |                  |                  |                                         |              |

|     |                              |          | 0        | 1                | 1       | 0       |               | 3.125            |                  |                  |                                         |              |

|     |                              |          | 0        | 1                | 1       | 1       |               | 3.125            |                  |                  |                                         |              |

|     | Reference divider            |          | 1        | 0                | 0       | 0       |               | 10               |                  |                  |                                         |              |

|     | data                         |          | 1        | 0                | 0       | 1       |               | 9                |                  |                  |                                         |              |

| 2   | R0 to R3                     |          | 1        | 0                | 1       | 0       |               | 5                |                  |                  |                                         |              |

|     | XS                           |          | 1        | 0                | 1       | 1       |               | 1                |                  |                  |                                         |              |

|     |                              |          | 1        | 1                | 0       | 0       |               | 3                |                  |                  |                                         |              |

|     |                              |          | 1        | 1                | 0       | 1       |               | 15               |                  |                  |                                         |              |

|     |                              |          | 1        | 1                | 1       | 0       |               | IIBIT + Xtal OSC | , 510P           |                  |                                         |              |

|     |                              |          |          | 1                |         |         |               |                  |                  |                  |                                         |              |

|     |                              | 1        |          | NHIBI            |         |         |               |                  |                  |                  |                                         |              |

|     |                              |          |          |                  |         |         |               |                  |                  |                  | ne FMIN, AMIN, and IFIN mpedance state. |              |

|     |                              | 1        |          |                  |         |         | ent selectio  |                  | ump output goe   |                  | npedance state.                         |              |

|     |                              |          |          | 0: 4.5           |         |         | ent selectio  | ii dala          |                  |                  |                                         |              |

|     |                              |          |          | 1: 7.2           |         |         |               |                  |                  |                  |                                         |              |

|     |                              | N        | ote th   | at 7.2           | MHz     | is sel  | ected after   | a power on rese  | et.              |                  |                                         |              |

|     |                              | $\vdash$ |          |                  |         |         |               |                  |                  |                  |                                         |              |

|     |                              | 1        |          |                  |         |         |               | nmand data       |                  |                  |                                         |              |

|     |                              |          |          | = 1: S<br>= 0: P |         |         | ounter        |                  |                  |                  |                                         |              |

|     |                              |          |          |                  |         |         |               | rement time.     |                  |                  |                                         |              |

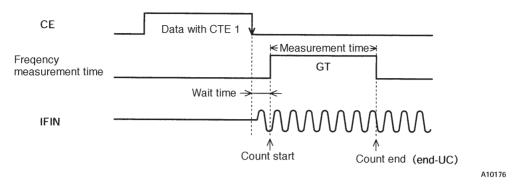

|     | IF counter control           | `'       |          |                  |         |         |               |                  |                  | 1                |                                         |              |

| 3   | data                         |          |          | ST1              |         | Т0      |               | ment time        | Wait time        | -                |                                         | IFS          |

|     | CTE                          |          | <u> </u> | 0                |         | 0       |               | ms               | 3 to 4 ms        | -                |                                         |              |

|     | GT0, GT1                     |          |          | 0                |         | 1       |               | 8                | 3 to 4           | -                |                                         |              |

|     |                              | 1        |          |                  |         |         |               |                  |                  |                  |                                         |              |

|     |                              |          |          | 1                |         | 0<br>1  |               | 32<br>54         | 7 to 8<br>7 to 8 |                  |                                         |              |

Continued on next page.

Continued from preceding page.

| No. | Control block/data                        |                                                                                                                                     |                                                                                                                                                          |                                                                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                               | Related data |

|-----|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 4   | I/O port setup data<br>IOC1,IOC2          | Data = 0: I                                                                                                                         |                                                                                                                                                          | out for the shared                                                                                                                                                                                       | function I/O pins ( $\overline{IO1}$ and $\overline{IO2}$ ).                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                               |              |

| 5   | Output port data<br>BO1 to BO4<br>IO1,IO2 | Data = 0: 0<br>Data = 1: L                                                                                                          | Dpen<br>₋ow level                                                                                                                                        |                                                                                                                                                                                                          | I through $\overline{BO4}$ , $\overline{IO1}$ , and $\overline{IO2}$ output to the open state, after a power on                                                                                                                                                                                                                                      |                                                                                                                                                                                                               | IOC1<br>IOC2 |

|     |                                           | Determine                                                                                                                           | s the DO pi                                                                                                                                              | n output.                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                               |              |

|     |                                           | DOC2                                                                                                                                | DOC1                                                                                                                                                     | DOC0                                                                                                                                                                                                     | DO pin state                                                                                                                                                                                                                                                                                                                                         | ]                                                                                                                                                                                                             |              |

|     |                                           | 0                                                                                                                                   | 0                                                                                                                                                        | 0                                                                                                                                                                                                        | Open                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |              |

|     |                                           | 0                                                                                                                                   | 0                                                                                                                                                        | 1 Lo                                                                                                                                                                                                     | w when the PLL is unlocked                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                               |              |

|     |                                           | 0                                                                                                                                   | 1                                                                                                                                                        | 0                                                                                                                                                                                                        | end-UC *1                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                               |              |

|     |                                           | 0                                                                                                                                   | 1                                                                                                                                                        | 1                                                                                                                                                                                                        | Open                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |              |

|     |                                           | 1                                                                                                                                   | 0                                                                                                                                                        | 0                                                                                                                                                                                                        | Open                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |              |

|     |                                           | 1                                                                                                                                   | 0                                                                                                                                                        | 1                                                                                                                                                                                                        | The IO1 pin state *2                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |              |

|     |                                           | 1                                                                                                                                   | 1                                                                                                                                                        | 0                                                                                                                                                                                                        | The IO2 pin state *2                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |              |

|     |                                           | 1                                                                                                                                   | 1                                                                                                                                                        | 1                                                                                                                                                                                                        | Open                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |              |

|     | DO pin control data                       | The open sta                                                                                                                        | ate is select                                                                                                                                            | ed after a power                                                                                                                                                                                         | on reset.                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                             | UL0, UL1     |

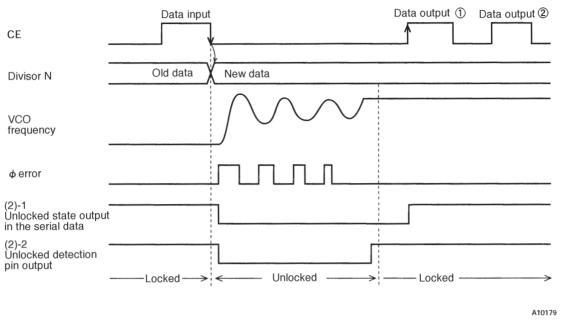

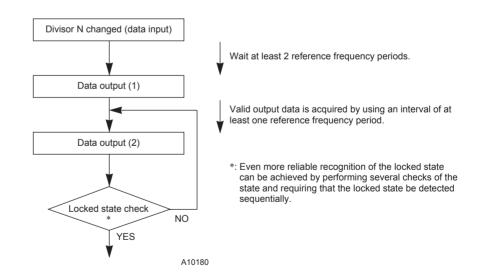

|     | DO pill control data                      | *1. end-UC:                                                                                                                         | IF counter                                                                                                                                               | measurement en                                                                                                                                                                                           | d check                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                               | CTE          |