# ML620Q150A Series User's Manual

16-bit Microcontroller

Rev.2 Issue Date: May.25, 2015

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Semiconductor.

Copyright 2015 LAPIS Semiconductor Co., Ltd.

## LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/

FEUL620Q150A i

## **Preface**

This manual describes the operation of the hardware of the 16-bit microcontroller ML620Q150A Series.

The following manuals are also available. Read them as necessary.

- nX-U16/100 Core Instruction Manual Description on the basic architecture and the each instruction of the nX-U16/100 Core.

- MACU8 Assembler Package User's Manual Description on the method of operating the relocatable assembler, the linker, the librarian, and the object converter and also on the specifications of the assembler language.

- CCU8 User's Manual

Description on the method of operating the compiler.

- CCU8 Programming Guide

Description on the method of programming.

- CCU8 Language Reference

Description on the language specifications.

- DTU8 Debugger User's Manual Description on the method of operating the debugger DTU8.

- IDEU8 User's Manual Description on the integrated development environment IDEU8.

- uEASE User's Manual

Description on the on-chip debug tool uEASE.

- uEASE connection Manual Description about the connection between uEASE.

- FWuEASE Flash Writer Host Program User's Manual Description on the Flash Writer host program.

FEUL620Q150A ii

## **Notation**

| Classification  | Notation               | Description                                                                                                                          |

|-----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ♦ Numeric value | xxh, xxH<br>xxb        | Indicates a hexadecimal number. x: Any value in the range of 0 to F Indicates a binary number; "b" may be omitted. x: A value 0 or 1 |

|                 |                        |                                                                                                                                      |

| ♦ Unit          | word, W                | 1  word = 16  bits                                                                                                                   |

|                 | byte, B                | 1 byte = $8 \text{ bits}$                                                                                                            |

|                 | nibble, N              | 1 nibble = 4 bits                                                                                                                    |

|                 | mega-, M               | $10^{6}$                                                                                                                             |

|                 | kilo-, K               | $2^{10} = 1024$                                                                                                                      |

|                 | kilo-, k               | $10^3 = 1000$                                                                                                                        |

|                 | milli-, m              | 10 <sup>-3</sup>                                                                                                                     |

|                 | micro-, µ              | 10 <sup>-6</sup>                                                                                                                     |

|                 | nano-, n               | 10-9                                                                                                                                 |

|                 | second, s (lower case) | second                                                                                                                               |

| ◆ Terminology   | "H" level, "1" level   | Indicates high voltage signal levels $V_{\text{IH}}$ and $V_{\text{OH}}$ as specified by the electrical characteristics.             |

|                 | "L" level, "0" level   | Indicates low voltage signal levels $V_{\text{IL}}$ and $V_{\text{OL}}$ as specified by the electrical characteristics.              |

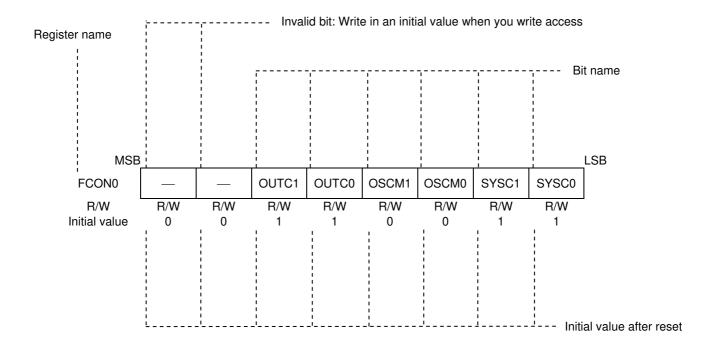

## ♦ Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

FEUL620Q150A iii

## Contents

| Chapter 1                                                       |      |

|-----------------------------------------------------------------|------|

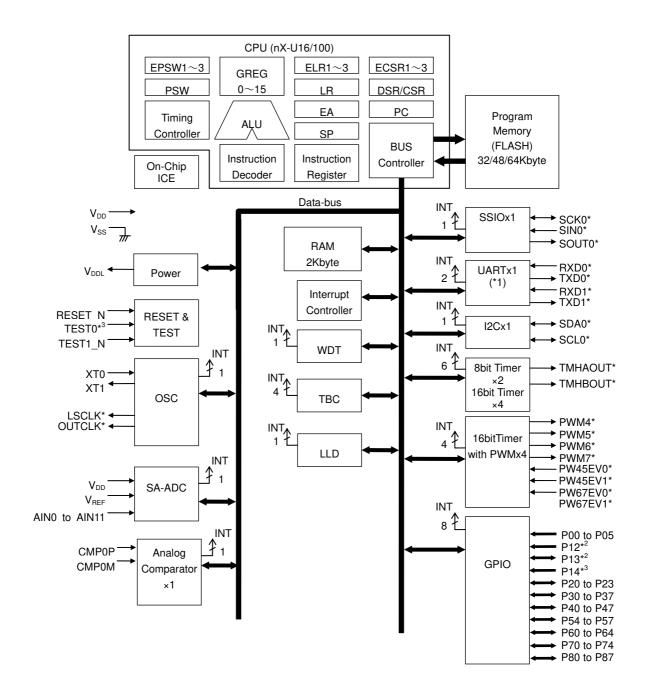

| 1. Overview                                                     | 1.1  |

| 1.1 Features                                                    |      |

| 1.2 Configuration of Functional Blocks                          |      |

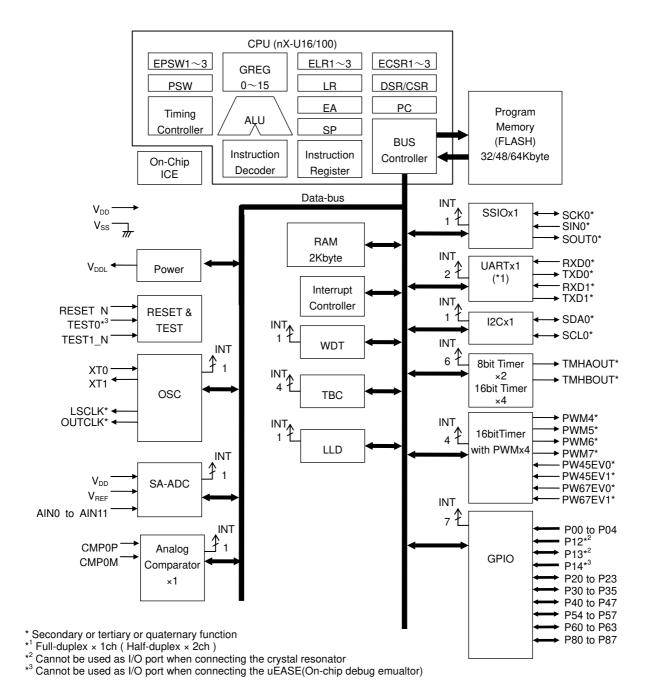

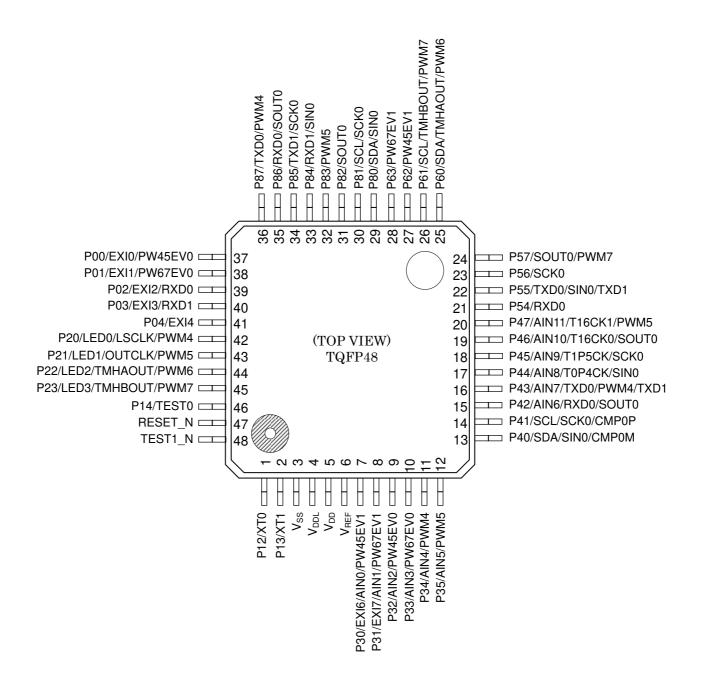

| 1.2.1 Block Diagram of ML620Q151A/ML620Q152A/ML620Q153A(TQFP48) |      |

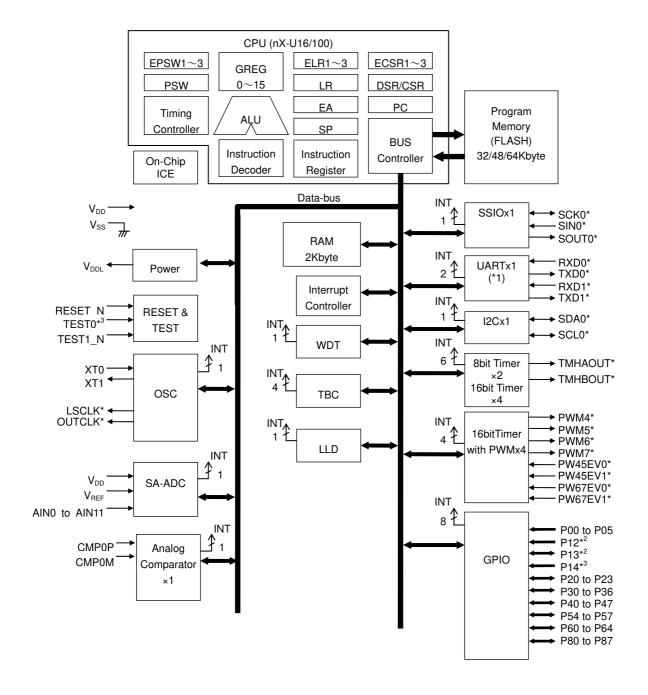

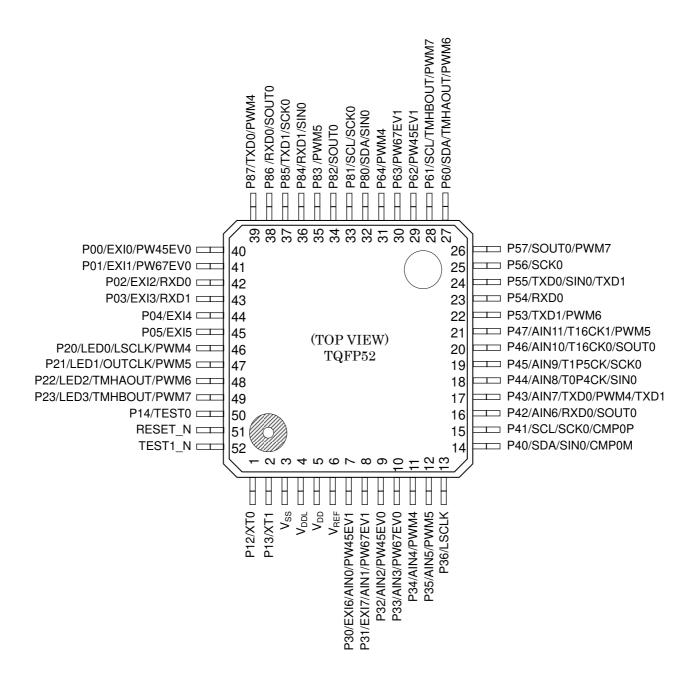

| 1.2.2 Block Diagram of ML620Q154A/ML620Q155A/ML620Q156A(TQFP52) |      |

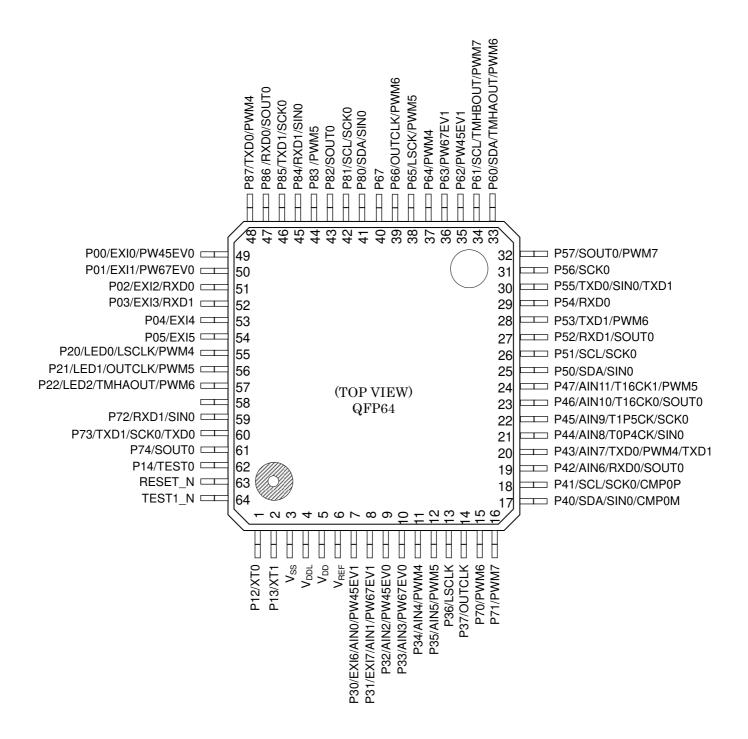

| 1.2.3 Block Diagram of ML620Q157A/ML620Q158A/ML620Q159A(QFP64)  |      |

| 1.3 Pins                                                        |      |

| 1.3.1 Pin Layout                                                |      |

| 1.3.2 List of Pins.                                             |      |

| 1.3.3 Pin Description                                           |      |

| 1.3.4 Handling of Unused Pins                                   |      |

| 1.5.4 Handling of Ordsed Files                                  | 1-1/ |

| Chapter 2                                                       |      |

| Chapter 2                                                       |      |

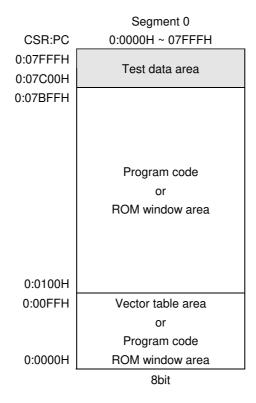

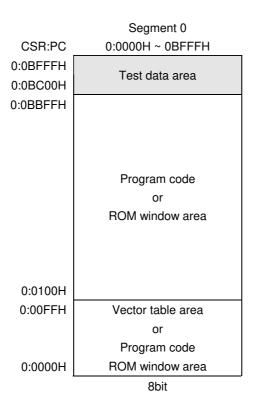

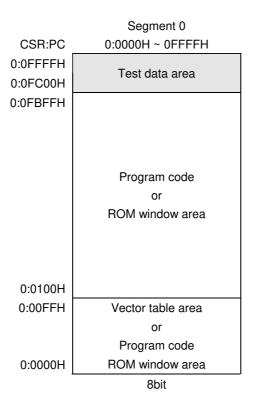

| 2 CPU and Memory Space                                          | 2-1  |

| 2.1 Genral Description                                          | 2-1  |

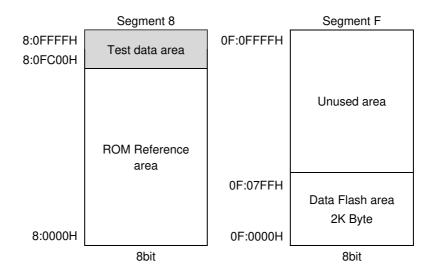

| 2.2 Program Memory Space                                        | 2-1  |

| 2.3 Data Memory Space                                           | 2-4  |

| 2.4 Instruction Length                                          | 2-7  |

| 2.5 Data Type                                                   |      |

| 2.6 Description of Registers                                    |      |

| 2.6.1 List of Registers                                         |      |

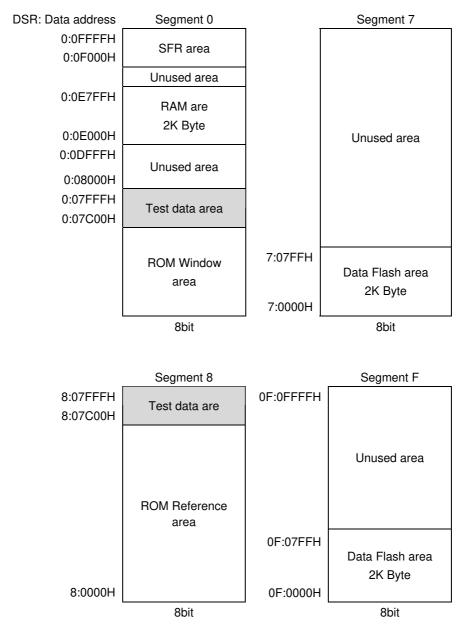

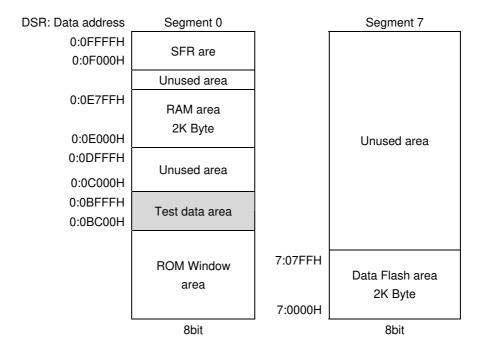

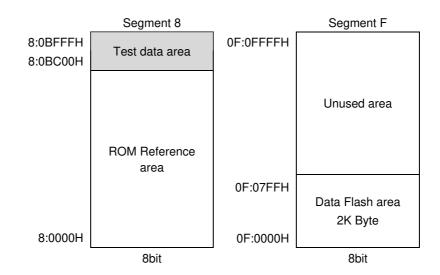

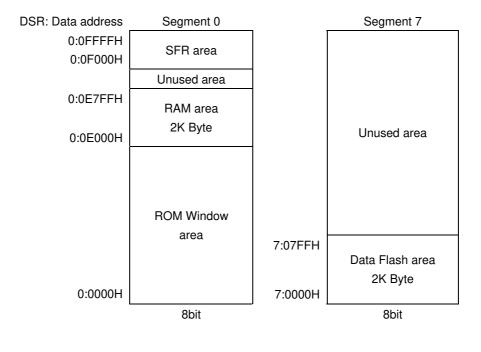

| 2.6.2 Data Segment Register (DSR)                               |      |

|                                                                 |      |

| Chapter 3                                                       |      |

|                                                                 |      |

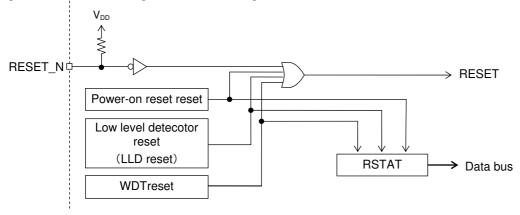

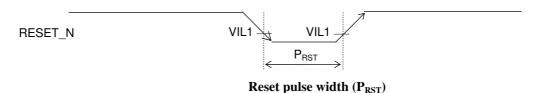

| 3. Reset Function                                               |      |

| 3.1 General Description                                         |      |

| 3.1.1 Features                                                  |      |

| 3.1.2 Configuration                                             |      |

| 3.1.3 List of Pin                                               |      |

| 3.2 Description of Registers                                    |      |

| 3.2.1 List of Registers                                         |      |

| 3.2.2 Reset Status Register (RSTAT)                             |      |

| 3.3 Description of Operation                                    |      |

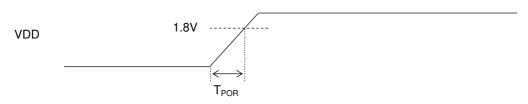

| 3.3.1 Operation of System Reset Mode                            | 3-3  |

|                                                                 |      |

| Chapter 4                                                       |      |

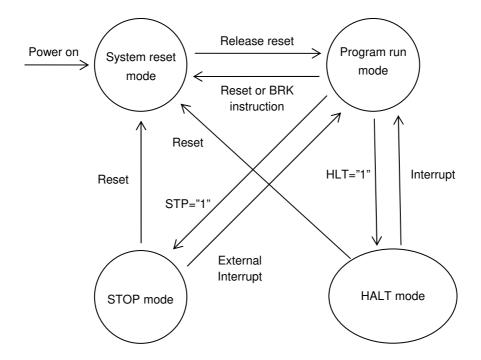

| 4. MCU Control Function                                         | 4.1  |

|                                                                 |      |

| 4.1 General Description                                         |      |

| 4.1.1 Features                                                  |      |

| 4.1.2 Configuration                                             |      |

| 4.2 Description of Registers                                    |      |

| 4.2.1 List of Registers                                         |      |

| 4.2.2 Stop Code Acceptor (STPACP)                               |      |

| 4.2.3 Standby Control Register (SBYCON)                         |      |

| 4.2.4 Block Control Register 0 (BLKCON0)                        |      |

| 4.2.5 Block Control Register 2 (BLKCON2)                        |      |

| 4.2.6 Block Control Register 3 (BLKCON3)                        |      |

| 4.2.7 Block Control Register 4 (BLKCON4)                        |      |

| 4.2.8 Block Control Register 6 (BLKCON6)                        |      |

| 4.2.9 Block Control Register 7 (BLKCON7)                        |      |

| 4.3 Description of Operation                                    |      |

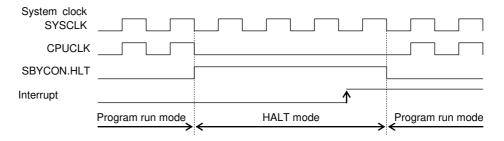

| 4.3.1 Program Run Mode                                          | 4-11 |

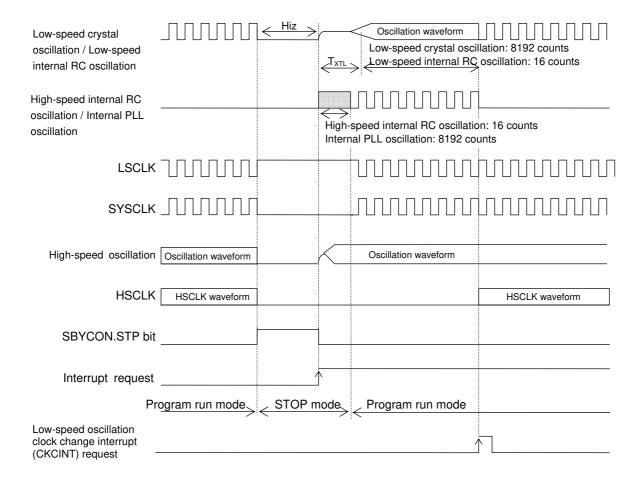

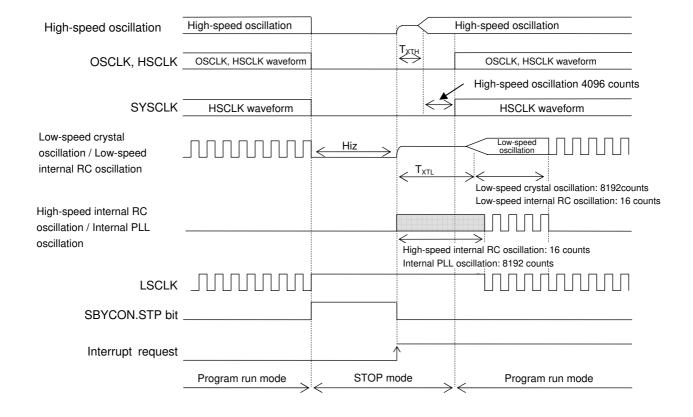

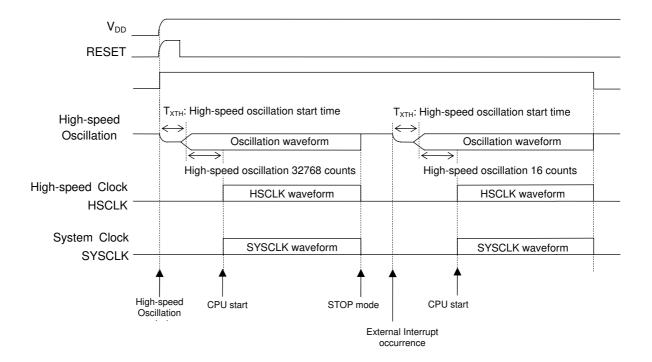

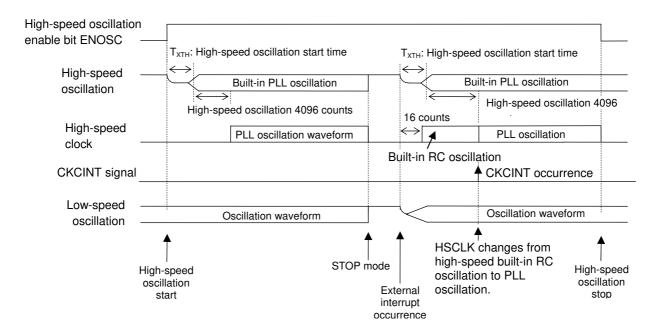

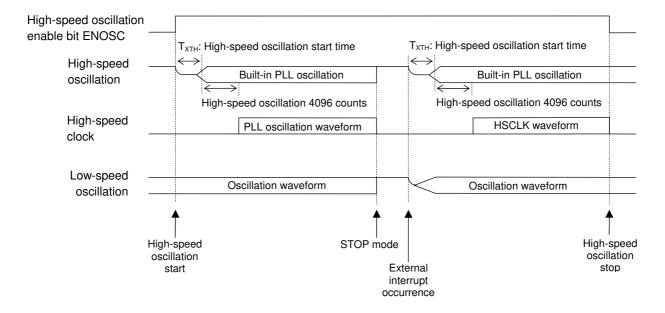

| 4.3.3     | STOP Mode                                                              | 4-12 |

|-----------|------------------------------------------------------------------------|------|

| 4.3.3     |                                                                        |      |

| 4.3.3     | 1                                                                      |      |

| 4.3.3     |                                                                        |      |

| 4.3.4     | Block control function                                                 |      |

|           | DIOCK CONTOL ISSISTING                                                 |      |

| Chapter 5 |                                                                        |      |

| Chapter 3 |                                                                        |      |

| 5. Inter  | rupts (INTs)                                                           | 5-1  |

|           | enral Description                                                      |      |

| 5.1.1     | Features                                                               | 5-1  |

| 5.2 De    | escription of Registers                                                | 5-2  |

| 5.2.1     | List of Registers                                                      |      |

| 5.2.2     | Interrupt Enable Register 0 (IE0)                                      |      |

| 5.2.3     | Interrupt Enable Register 1 (IE1)                                      |      |

| 5.2.4     | Interrupt Enable Register 2 (IE2)                                      |      |

| 5.2.5     | Interrupt Enable Register 3 (IE3)                                      |      |

| 5.2.6     | Interrupt Enable Register 4 (IE4)                                      |      |

| 5.2.7     | Interrupt Enable Register 5 (IE5)                                      |      |

| 5.2.8     | Interrupt Enable Register 6 (IE6)                                      |      |

| 5.2.9     | Interrupt Enable Register 7 (IE7)                                      |      |

| 5.2.10    | Interrupt Request Register 0 (IRQ0)                                    |      |

| 5.2.11    | Interrupt Request Register 1 (IRQ1)                                    |      |

|           | Interrupt Request Register 2 (IRQ2)                                    |      |

|           | Interrupt Request Register 3 (IRQ3)                                    |      |

|           | Interrupt Request Register 4 (IRQ4)                                    |      |

|           | Interrupt Request Register 5 (IRQ5)                                    |      |

|           | Interrupt Request Register 6 (IRQ6)                                    |      |

|           | Interrupt Request Register 7 (IRQ7)                                    |      |

|           | Interrupt Level Control Enable Register (ILENL)                        |      |

|           | Current Interrupt Request Level Register (CILL)                        |      |

|           | Interrupt Level Control Register 01 (ILC01)                            |      |

| 5.2.21    |                                                                        |      |

| 5.2.21    |                                                                        |      |

|           | Interrupt Level Control Register 11 (ILC11)                            |      |

|           | Interrupt Level Control Register 20 (ILC20)                            |      |

|           | Interrupt Level Control Register 21 (ILC21)                            |      |

|           | Interrupt Level Control Register 30 (ILC30)                            |      |

|           | Interrupt Level Control Register 31 (ILC31)                            |      |

| 5.2.27    | Interrupt Level Control Register 40 (ILC40)                            |      |

| 5.2.28    | Interrupt Level Control Register 51 (ILC51)                            |      |

|           | Interrupt Level Control Register 60 (ILC60)                            |      |

|           | Interrupt Level Control Register 61 (ILC61)                            |      |

|           | Interrupt Level Control Register 70 (ILC70)                            |      |

|           | escription of Operation                                                |      |

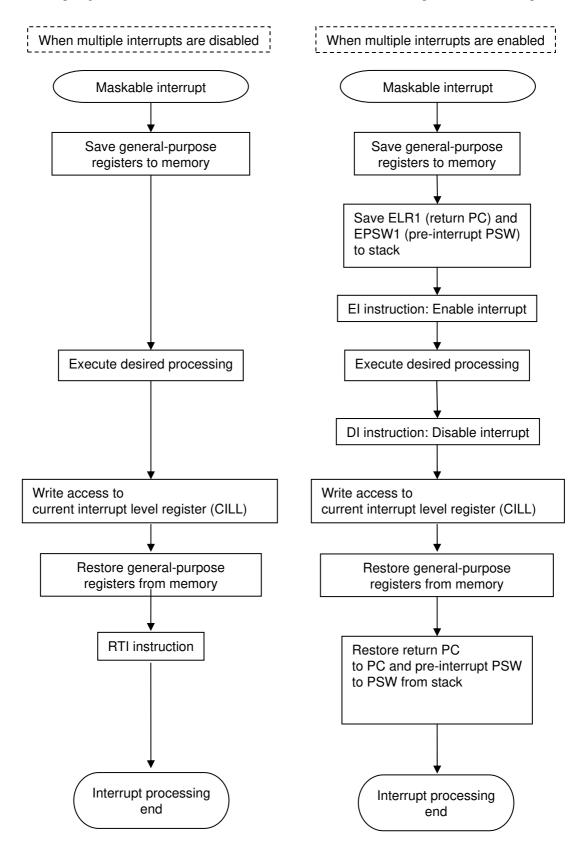

| 5.3.1     | Maskable Interrupt Processing                                          |      |

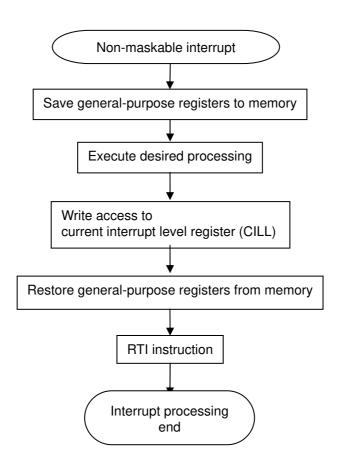

| 5.3.2     | Non-Maskable Interrupt Processing                                      |      |

| 5.3.3     | Software Interrupt Processing                                          |      |

| 5.3.4     | Notes on Interrupt Routine (When Interrupt Level Control Disabled)     |      |

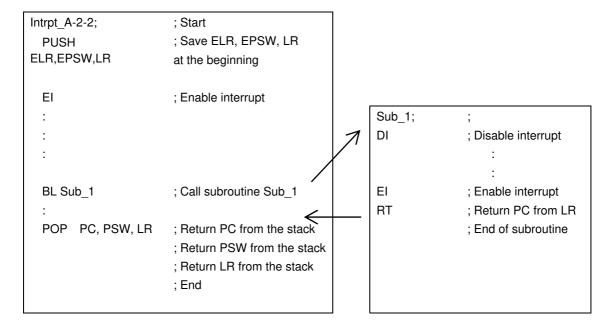

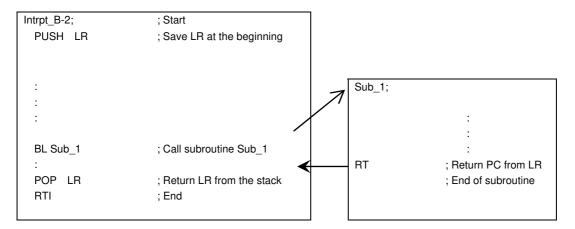

| 5.3.5     | Interrupt Processing When Interrupt Level Control Enabled              |      |

| 5.3.6     | Flow Chart When Interrupt Level Control Enabled                        |      |

| 5.3.7     | How To Write Interrupt Processing When Interrupt Level Control Enabled |      |

|           |                                                                        |      |

| 5.3.8     | Interrupt Disable State                                                | 3-48 |

| Chapter 6 |                                                                        |      |

|           |                                                                        |      |

|           | k Generation Circuit                                                   |      |

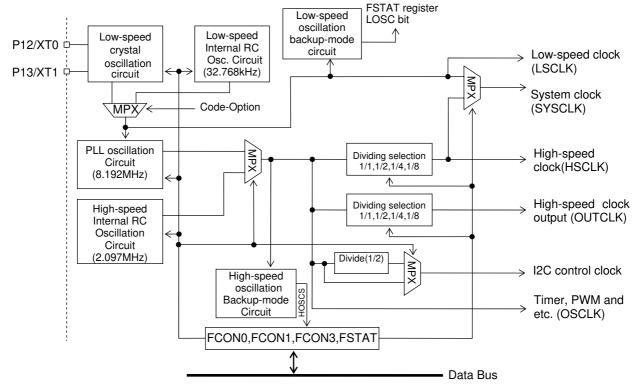

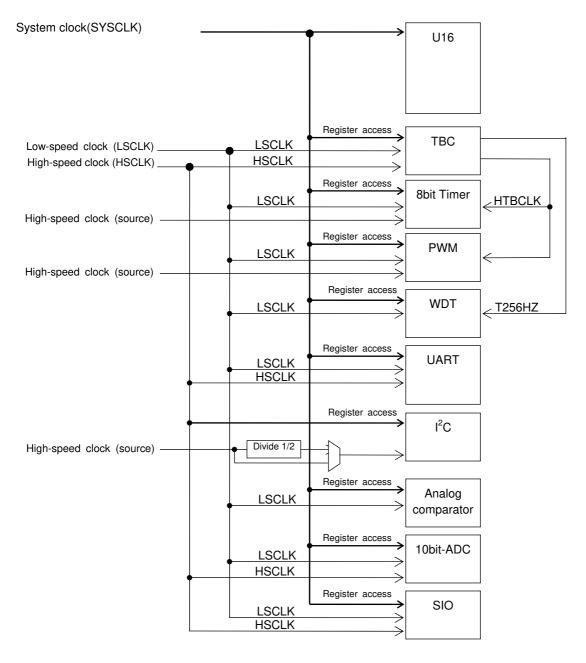

|           | enral Description                                                      |      |

| 6.1.1     | Features                                                               |      |

| 6.1.2     | Configuration                                                          |      |

| 6.1.3     | List of Pins                                                           | 6-3  |

| 61/       | Library Continuention Diagram                                          | 6.3  |

| 6.2 D     | escription of Registers                                             | 6-4  |

|-----------|---------------------------------------------------------------------|------|

| 6.2.1     | List of Registers                                                   |      |

| 6.2.2     | Frequency Control Register 0(FCON0)                                 |      |

| 6.2.3     | Frequency Control Register 1 (FCON1)                                |      |

| 6.2.4     | Frequency Control Register 3 (FCON3)                                |      |

| 6.2.5     | Frequency Status Register (FSTAT)                                   |      |

|           |                                                                     |      |

| 6.3 D     | escription of Operation                                             | 6-11 |

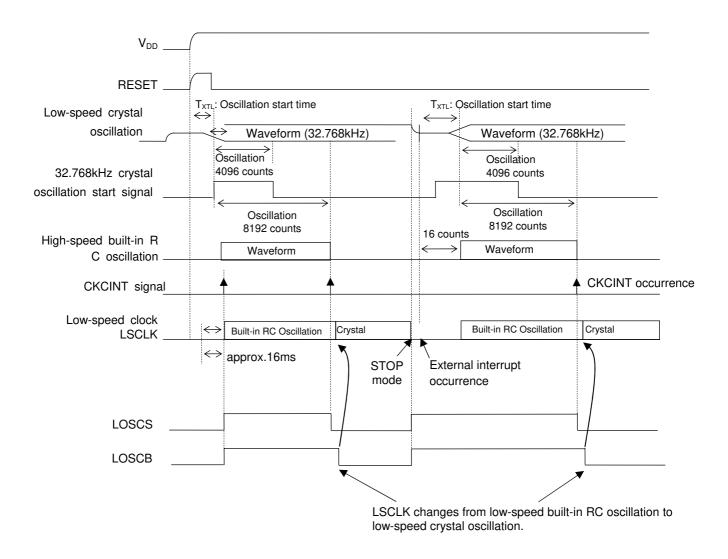

|           | Low-Speed Clock                                                     |      |

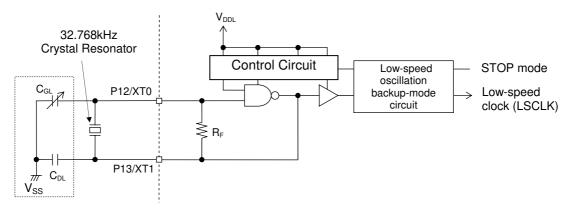

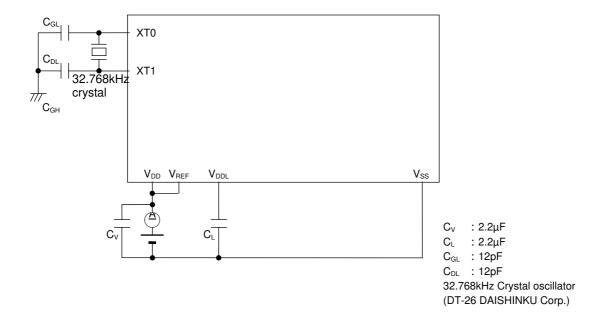

| 6.3.1     | .1 Low-Speed Crystal Oscillation Circuit                            | 6-11 |

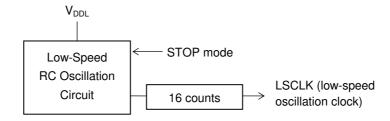

|           | .2 Low-Speed Built-In RC Oscillation Circuit                        |      |

| 6.3.1     |                                                                     |      |

|           | •                                                                   |      |

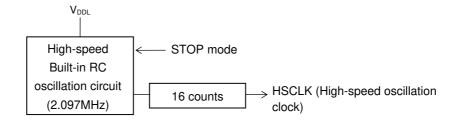

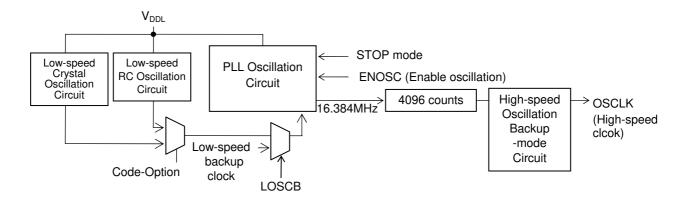

| 6.3.2     | High-Speed Clock                                                    | 6-13 |

| 6.3.2     |                                                                     |      |

| 6.3.2     |                                                                     |      |

| 6.3.2     |                                                                     |      |

| 6.3.2     |                                                                     |      |

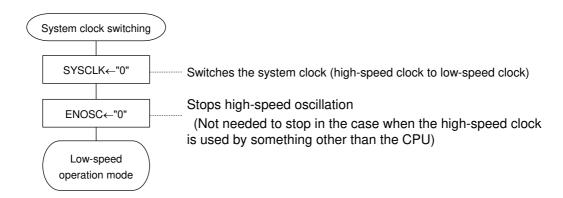

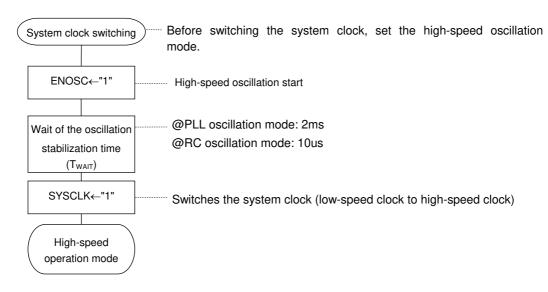

| 6.3.3     | Switching of System Clock                                           |      |

|           | pecifying Port Registers                                            |      |

| 6.4.1     | Functioning P21(OUTCLK) as the high-speed clock output              |      |

| 6.4.2     | Functioning P20 (LSCLK) as the low-speed clock output               |      |

| 6.4.3     | Functioning P36 (LSCLK) as the low-speed clock output               |      |

|           |                                                                     |      |

| Chapter 7 | 7                                                                   |      |

| Chapter   |                                                                     |      |

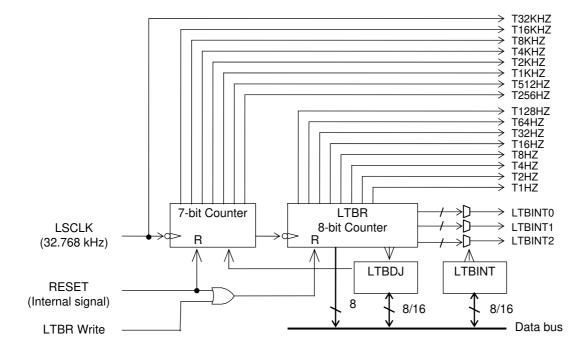

| 7. Time   | Base Counter                                                        | 7-1  |

| 7.1 G     | enral Description                                                   | 7-1  |

| 7.1.1     | Features                                                            | 7-1  |

| 7.1.2     | Configuration                                                       | 7-1  |

| 7.2 D     | escription of Registers                                             | 7-2  |

| 7.2.1     | List of Registers                                                   | 7-2  |

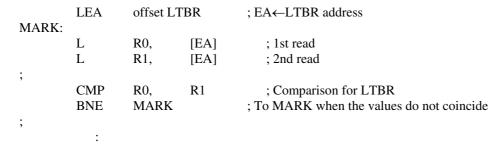

| 7.2.2     | Low-Speed Time Base Counter (LTBR)                                  | 7-3  |

| 7.2.3     | Low-Speed Time Base Counter Frequency Adjustment Registers (LTBADJ) | 7-4  |

| 7.2.4     | Low-Speed Time Base Counter Interrupt select Registers (LTBINT)     | 7-6  |

| 7.3 D     | escription of Operation                                             |      |

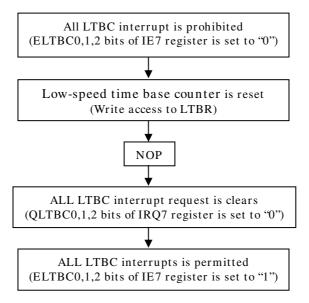

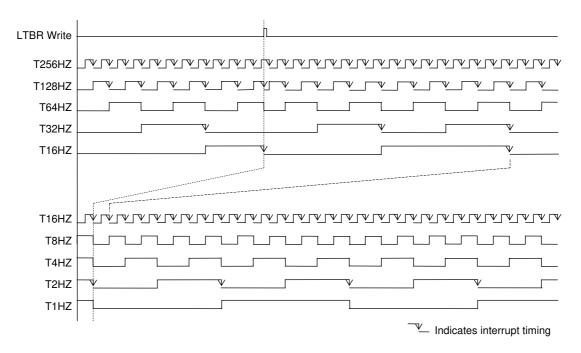

| 7.3.1     | Low-Speed Time Base Counter                                         |      |

|           | 1                                                                   |      |

| Chapter 8 | }                                                                   |      |

|           |                                                                     |      |

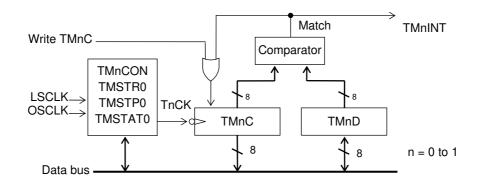

|           | Timer                                                               |      |

|           | enral Description                                                   |      |

| 8.1.1     | Features                                                            |      |

| 8.1.2     | Configuration                                                       |      |

| 8.2 D     | escription of Registers                                             |      |

| 8.2.1     | List of Registers                                                   |      |

| 8.2.2     | Timer n Data Register (TM0D)                                        | 8-3  |

| 8.2.3     | Timer n Data Register (TM1D)                                        |      |

| 8.2.4     | Timer 0 Counter Register (TM0C)                                     |      |

| 8.2.5     | Timer 1 Counter Register (TM1C)                                     |      |

| 8.2.6     | Timer 0 Control Register                                            |      |

| 8.2.7     | Timer 1 Control Register                                            |      |

| 8.2.8     | Timer Start Register 0 (TMSTR0)                                     |      |

| 8.2.9     | Timer Stop Register 0 (TMSTP0)                                      |      |

| 8.2.10    |                                                                     |      |

|           | escription of Operation                                             |      |

| Chapter 9      |                                                                  |      |

|----------------|------------------------------------------------------------------|------|

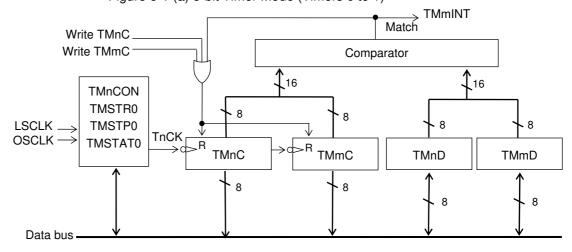

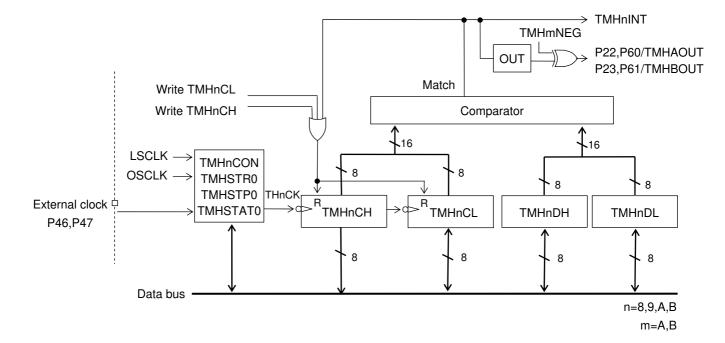

| 9. 16bit       | Timer                                                            | 9-1  |

| 9.1 Ge         | nral Description                                                 | 9-1  |

| 9.1.1          | Features                                                         |      |

| 9.1.2          | Configuration                                                    |      |

|                | scription of Registers                                           |      |

| 9.2.1          | List of Registers                                                |      |

| 9.2.2          | 16bit timer 8 data register L,H (TMH8DL,H)                       |      |

| 9.2.3          | 16bit timer 9 data register L,H (TMH9DL,H)                       |      |

| 9.2.4<br>9.2.5 | 16bit timer A data register L,H (TMHADL,H)                       |      |

| 9.2.5          | 16bit timer 8 counter register L,H (TMH8CL,H)                    |      |

| 9.2.0          | 16bit timer 9 counter register L,H (TMH9CL,H)                    |      |

| 9.2.8          | 16bit timer A counter register L,H (TMHACL,H)                    |      |

| 9.2.9          | 16bit timer B counter register L,H (TMHBCL,H)                    |      |

| 9.2.10         | 16bit timer 8 control register L,H (TMH8CON)                     |      |

| 9.2.11         | 16bit timer 9 control register L,H (TMH9CON)                     |      |

| 9.2.12         | 16bit timer A control register L,H (TMHACON)                     |      |

|                | 16bit timer B control register L,H (TMHBCON)                     |      |

| 9.2.14         | 16bit timer start register 0 (TMHSTR0)                           | 9-15 |

| 9.2.15         | 16bit timer stop register 0 (TMHSTP0)                            | 9-16 |

|                | 16bit timer status register 0 (TMHSTAT0)                         |      |

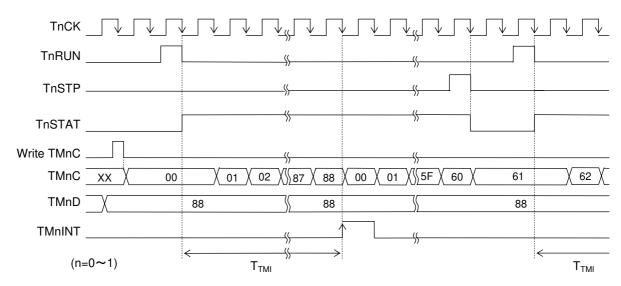

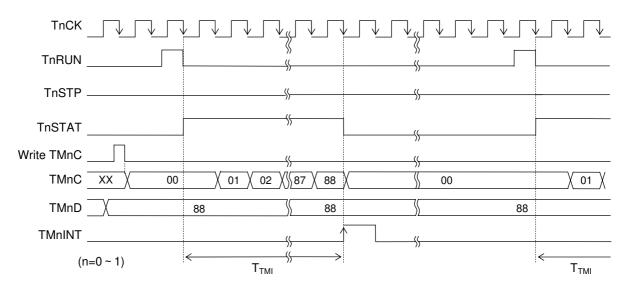

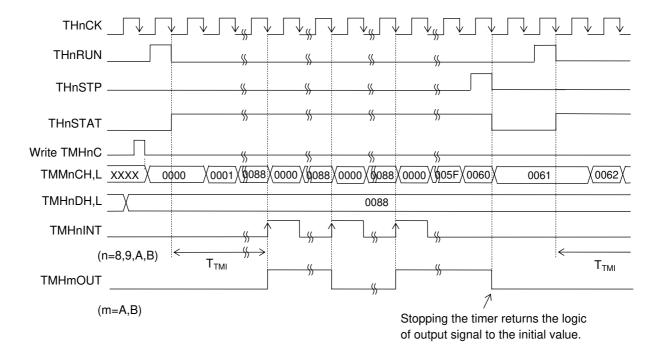

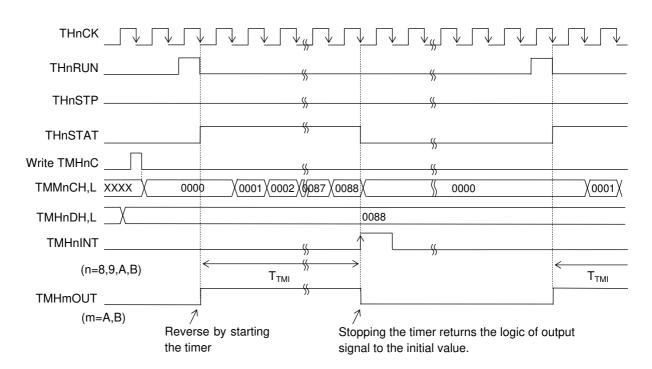

| 9.3 De         | scription of Operation                                           | 9-18 |

| Cl 1           |                                                                  |      |

| Chapter 1      | J                                                                |      |

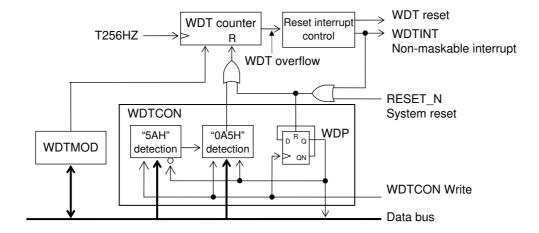

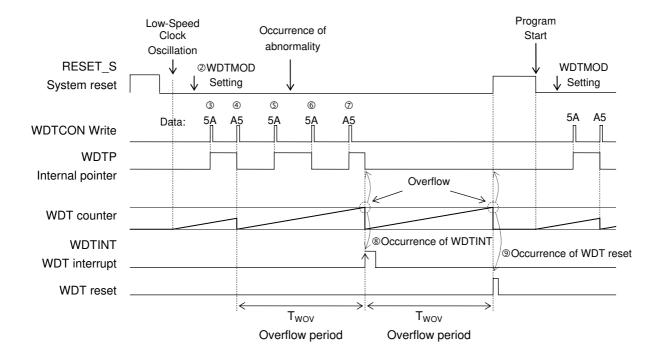

| 10. Watc       | ndog Timer                                                       | 10-1 |

| 10.1 Ge        | neral Description                                                | 10-1 |

|                | Features                                                         |      |

|                | Configuration                                                    |      |

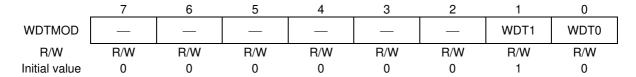

|                | scription of Registers                                           |      |

|                | List of Registers                                                |      |

|                | Watchdog Timer Control Register (WDTCON)                         |      |

|                | Watchdog Timer Mode Register (WDTMOD)                            |      |

|                | Scription of Operation                                           |      |

| 10.5.1         | Handling example when you do not want to use the watch dog timer | 10-7 |

| Chapter 1      | 1                                                                |      |

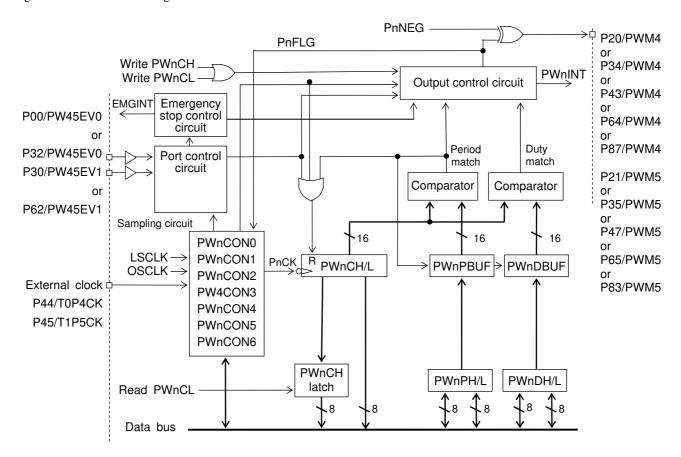

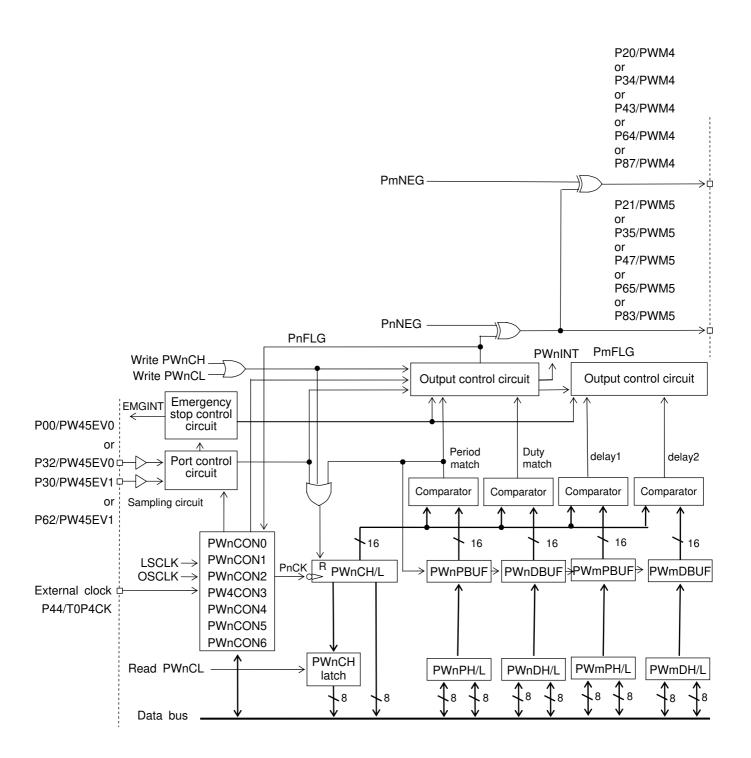

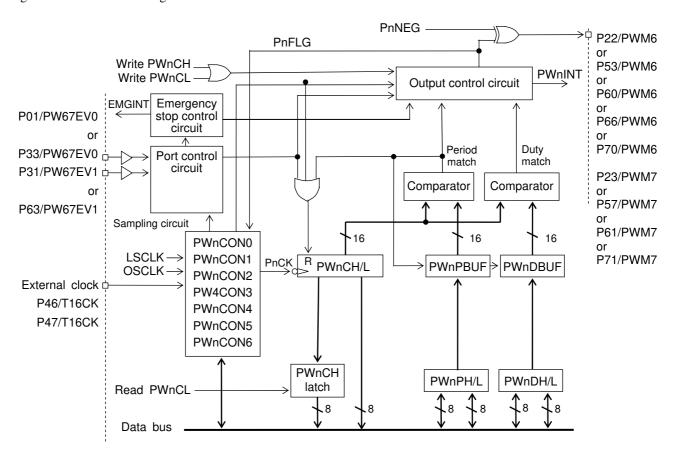

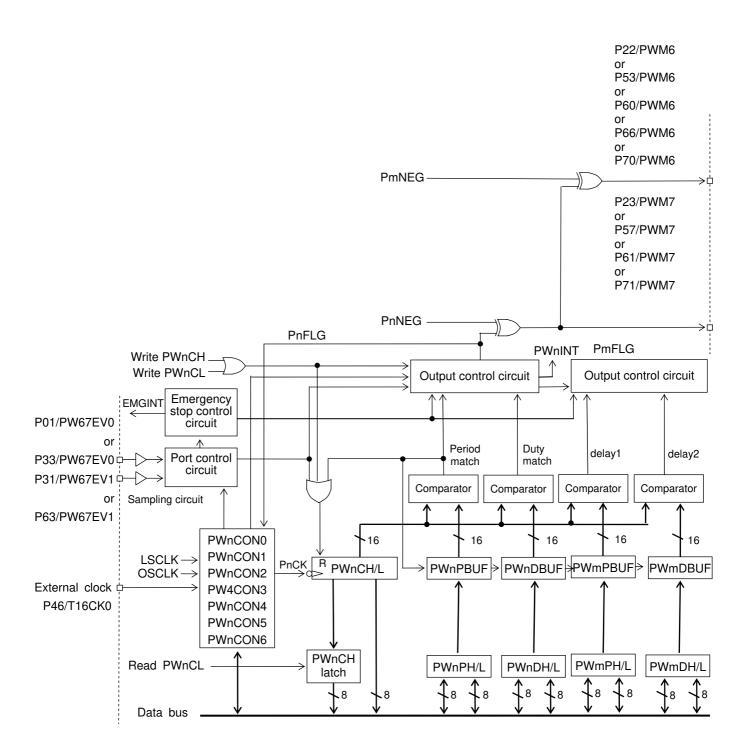

| 11. PWM        | [                                                                | 11-1 |

| 11.1 Ge        | neral Description                                                | 11-1 |

| 11.1.1         | Features                                                         | 11-1 |

|                | Configuration                                                    |      |

|                | List of Pins                                                     |      |

|                | scription of Registers                                           |      |

|                | List of Registers                                                |      |

|                | PWM4 period registers (PW4PL, PW4PH)                             |      |

|                | PWM4 duty registers (PW4DL, PW4DH)                               |      |

|                | PWM4 counter registers (PW4CL, PW4CH)                            |      |

|                | PWM4 control register 0 (PW4CON1)                                |      |

|                | PWM4 control register 1 (PW4CON1)                                |      |

|                | PWM4 control register 2 (PW4CON2)                                |      |

|                | PWM4 control register 4 (PW4CON4)                                |      |

|                | PWM4 control register 5 (PW4CON5)                                |      |

|                | PWM4 control register 6 (PW4CON6)                                |      |

|                | PWM5 period registers (PW5PL, PW5PH)                             |      |

|                | PWM5 duty registers (PW5DL, PW5DH)                               |      |

|                | PWM5 counter registers (PW5CL, PW5CH)                            |      |

|                | PWM5 control register 0 (PW5CON0)                                |      |

| 11.2.17                                                                                                                                                                                                                                                                                                                         | 7 PWM5 control register 2 (PW5CON2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-27                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                 | 3 PWM5 control register 4 (PW5CON4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                 | PWM5 control register 5 (PW5CON5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                 | PWM5 control register 6 (PW5CON6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                 | PWM6 period registers (PW6PL, PW6PH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

| 11.2.22                                                                                                                                                                                                                                                                                                                         | PWM6 duty registers (PW6DL, PW6DH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-33                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                 | B PWM6 counter registers (PW6CL, PW6CH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

| 11.2.24                                                                                                                                                                                                                                                                                                                         | PWM6 control register 0 (PW6CON0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-35                                                                                                               |

| 11.2.25                                                                                                                                                                                                                                                                                                                         | 5 PWM6 control register 1 (PW6CON1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-37                                                                                                               |

| 11.2.26                                                                                                                                                                                                                                                                                                                         | 6 PWM6 control register 2 (PW6CON2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-38                                                                                                               |

| 11.2.27                                                                                                                                                                                                                                                                                                                         | 7 PWM6 control register 3 (PW6CON3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-40                                                                                                               |

| 11.2.28                                                                                                                                                                                                                                                                                                                         | 3 PWM6 control register 4 (PW6CON4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-41                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                 | PWM6 control register 5 (PW6CON5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| 11.2.30                                                                                                                                                                                                                                                                                                                         | PWM6 control register 6 (PW6CON6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-43                                                                                                               |

| 11.2.31                                                                                                                                                                                                                                                                                                                         | PWM7 period registers (PW7PL, PW7PH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11-44                                                                                                               |

| 11.2.32                                                                                                                                                                                                                                                                                                                         | PWM7 duty registers (PW7DL, PW7DH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-45                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                 | B PWM7 counter registers (PW7CL, PW7CH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

| 11.2.34                                                                                                                                                                                                                                                                                                                         | PWM7 control register 0 (PW7CON0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-47                                                                                                               |

| 11.2.35                                                                                                                                                                                                                                                                                                                         | 5 PWM7 control register 1 (PW7CON1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-49                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                 | 6 PWM7 control register 2 (PW7CON2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| 11.2.37                                                                                                                                                                                                                                                                                                                         | 7 PWM7 control register 4 (PW7CON4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-52                                                                                                               |

| 11.2.38                                                                                                                                                                                                                                                                                                                         | 3 PWM7 control register 5 (PW7CON5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11-53                                                                                                               |

| 11.2.39                                                                                                                                                                                                                                                                                                                         | PWM7 control register 6 (PW7CON6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-54                                                                                                               |

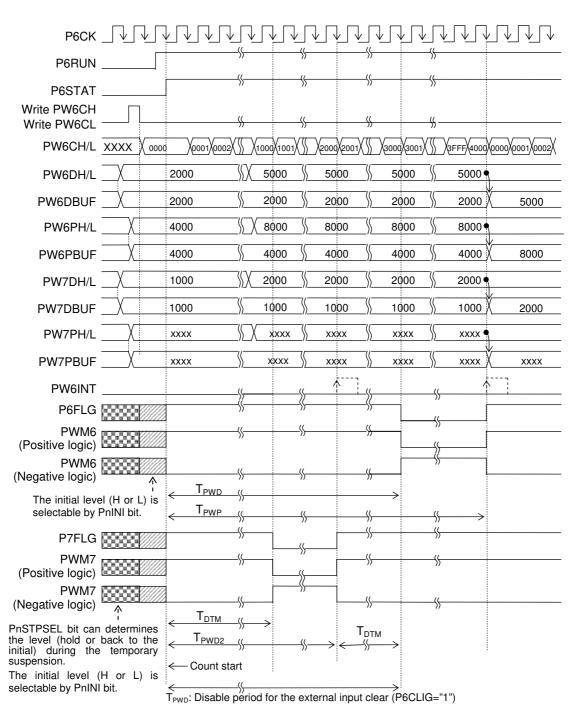

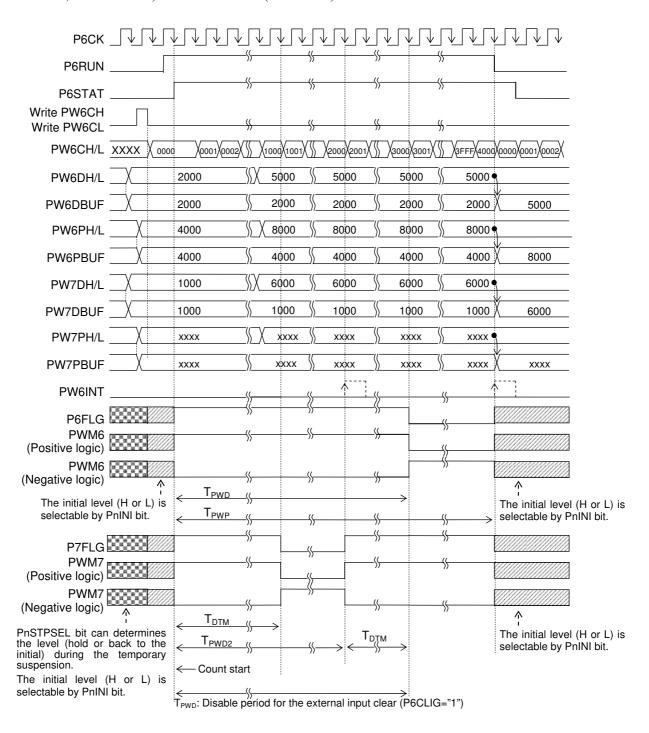

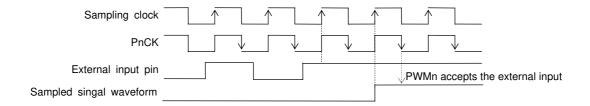

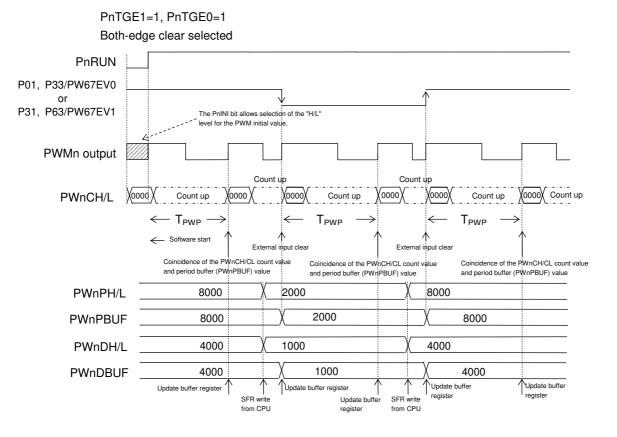

| 11.3 De                                                                                                                                                                                                                                                                                                                         | escription of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11-55                                                                                                               |

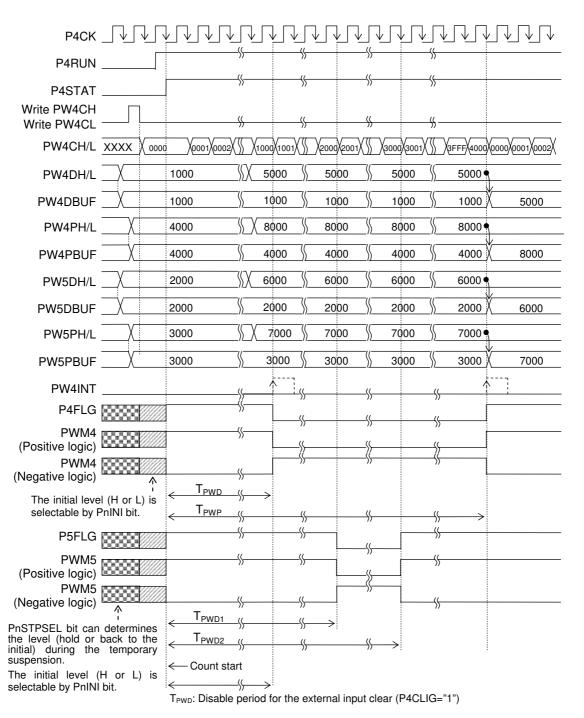

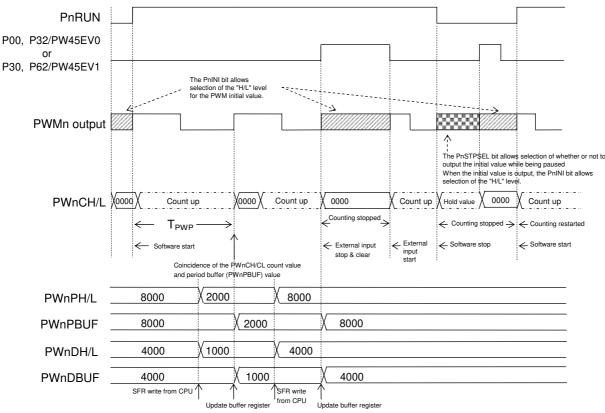

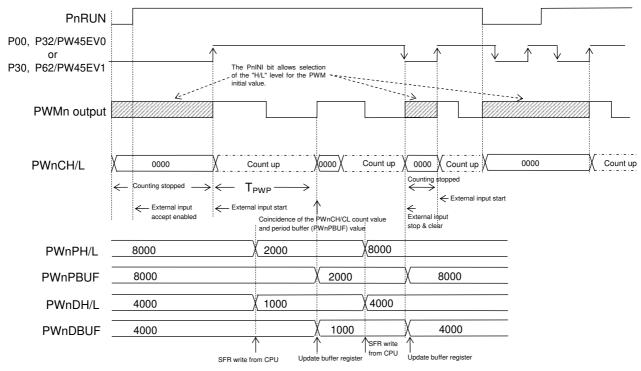

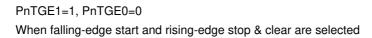

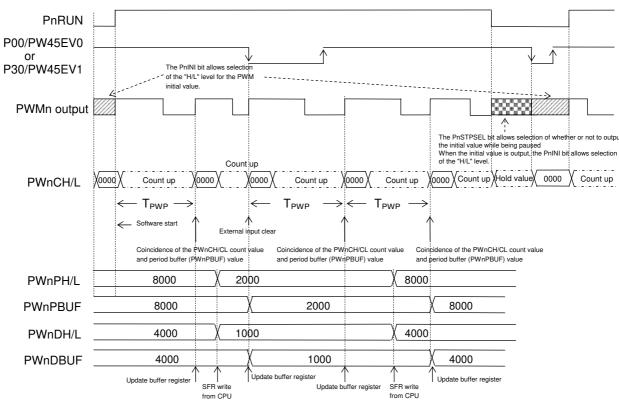

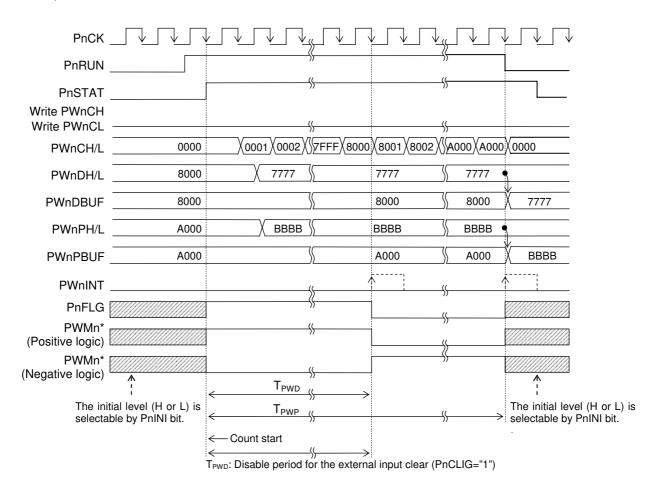

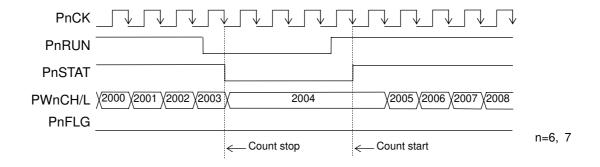

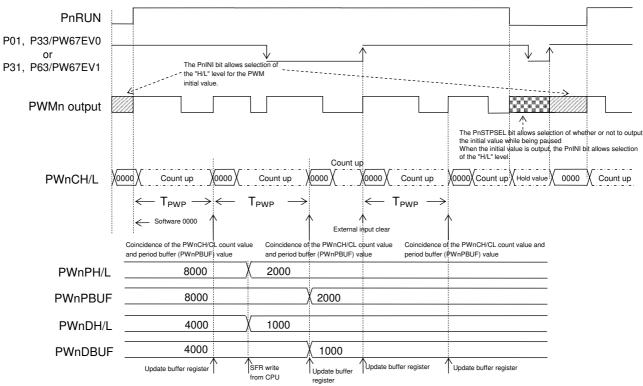

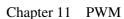

| 11.3.1                                                                                                                                                                                                                                                                                                                          | PWM4 and PWM5, Single mode / Repeat mode (P45MD="0", PnMD="0")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-59                                                                                                               |

| 11.3.2                                                                                                                                                                                                                                                                                                                          | PWM4 and PWM5, Single mode / One shot mode (P45MD="0", PnMD="1")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11-61                                                                                                               |

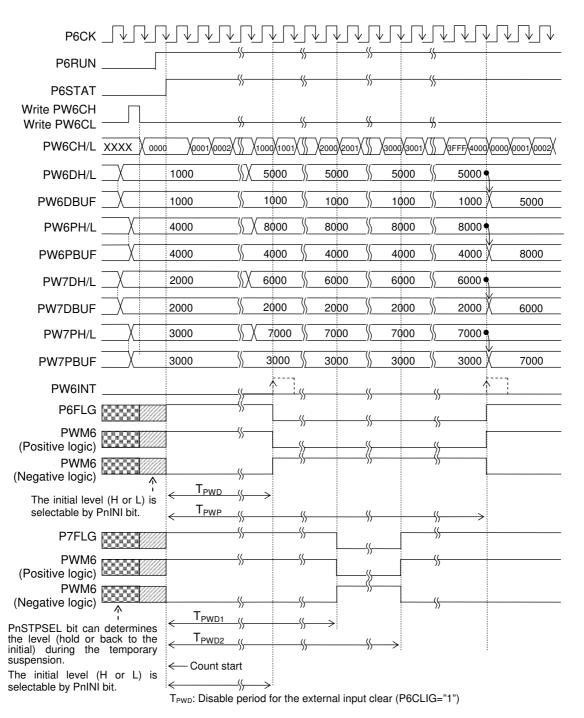

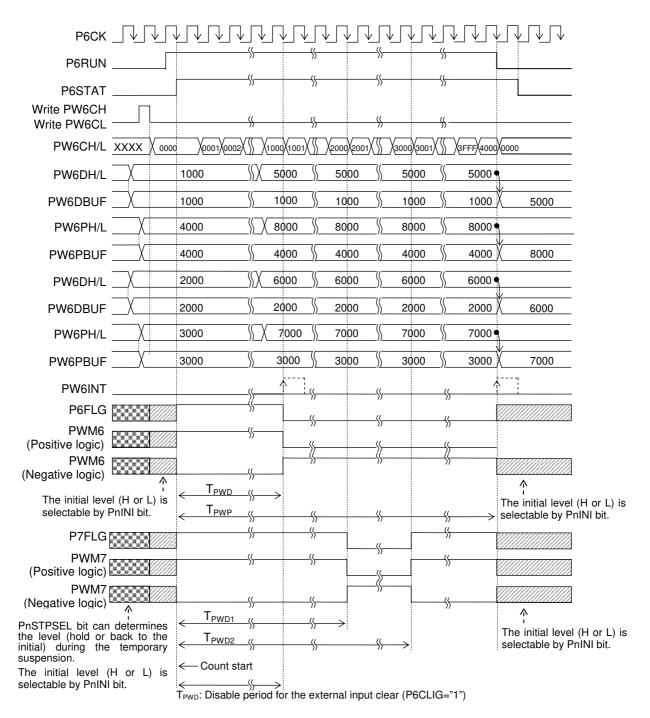

| 11.3.3                                                                                                                                                                                                                                                                                                                          | PWM4 and PWM5, Coupled mode (with no dead-time specified) / Repeat mode (P45MD="1",                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                 | P4DTMD="0", P4MD="0")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11-63                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

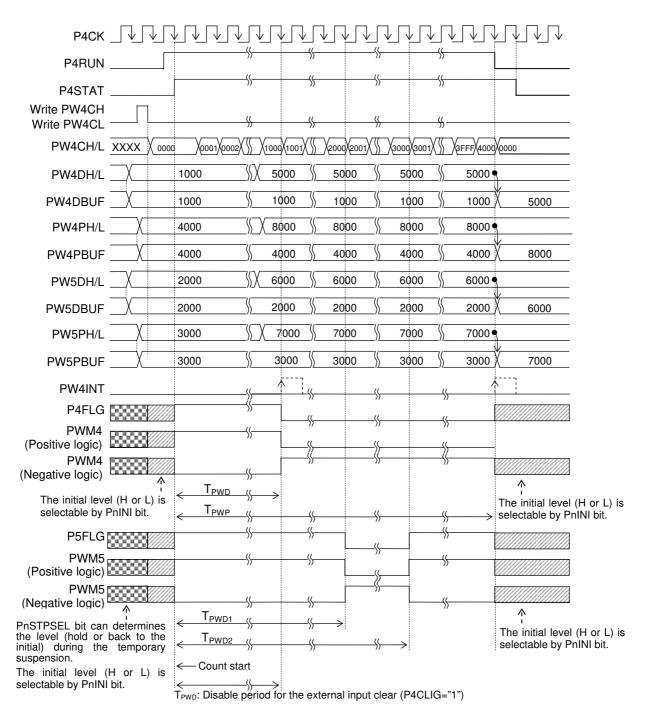

| 11.3.4                                                                                                                                                                                                                                                                                                                          | PWM4 and PWM5, Coupled mode (with no dead-time specified) / One shot mode (P45MD="1"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                 | P4DTMD="0", P4MD="1")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                                                                                                   |

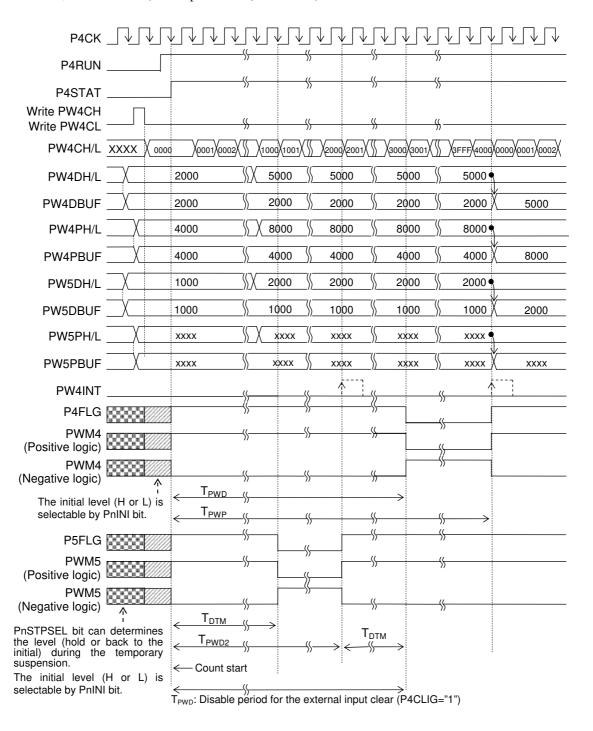

| 11.3.5                                                                                                                                                                                                                                                                                                                          | P4DTMD="0", P4MD="1")  PWM4 and PWM5, Coupled mode (with dead-time specified) / Repeat mode (P45MD="1", P4DTMD="1", P4MD="0")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ,<br>11-65                                                                                                          |

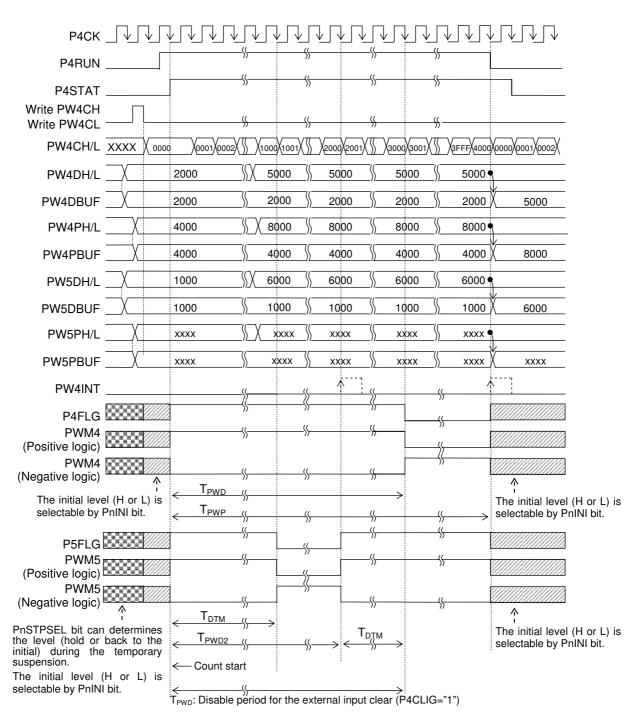

| 11.3.5                                                                                                                                                                                                                                                                                                                          | P4DTMD="0", P4MD="1")  PWM4 and PWM5, Coupled mode (with dead-time specified) / Repeat mode (P45MD="1", P4DTMD="1", P4MD="0")  PWM4 and PWM5, Coupled mode (with dead-time specified) / One shot mode (P45MD="1",                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ,<br>11-65<br>11-67                                                                                                 |

| 11.3.5<br>11.3.6                                                                                                                                                                                                                                                                                                                | P4DTMD="0", P4MD="1")  PWM4 and PWM5, Coupled mode (with dead-time specified) / Repeat mode (P45MD="1", P4DTMD="1", P4MD="0")  PWM4 and PWM5, Coupled mode (with dead-time specified) / One shot mode (P45MD="1", P4DTMD="1", P4MD="1")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,<br>11-65<br>11-67<br>11-70                                                                                        |

| 11.3.5<br>11.3.6                                                                                                                                                                                                                                                                                                                | P4DTMD="0", P4MD="1")  PWM4 and PWM5, Coupled mode (with dead-time specified) / Repeat mode (P45MD="1", P4DTMD="1", P4MD="0")  PWM4 and PWM5, Coupled mode (with dead-time specified) / One shot mode (P45MD="1",                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ,<br>11-65<br>11-67<br>11-70                                                                                        |

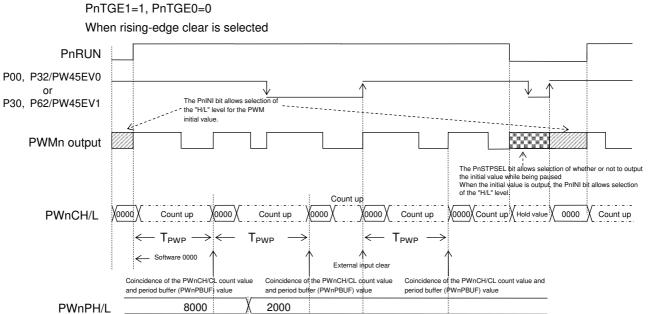

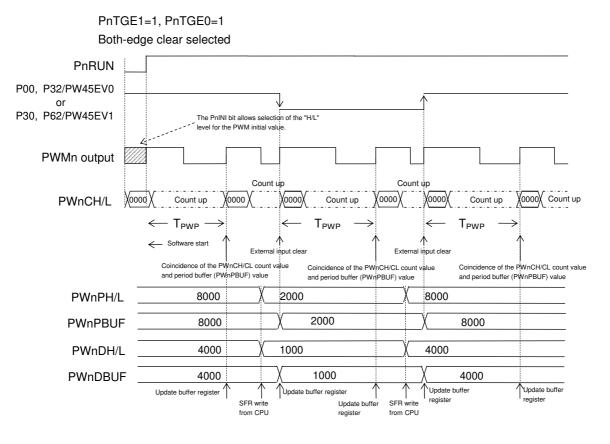

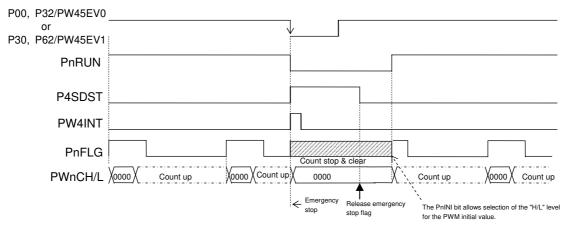

| 11.3.5<br>11.3.6<br>11.3.7<br>11.3.                                                                                                                                                                                                                                                                                             | P4DTMD="0", P4MD="1")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,<br>11-65<br>11-67<br>11-70<br>11-73                                                                               |