# **Low Profile Overvoltage Protection IC with Integrated MOSFET**

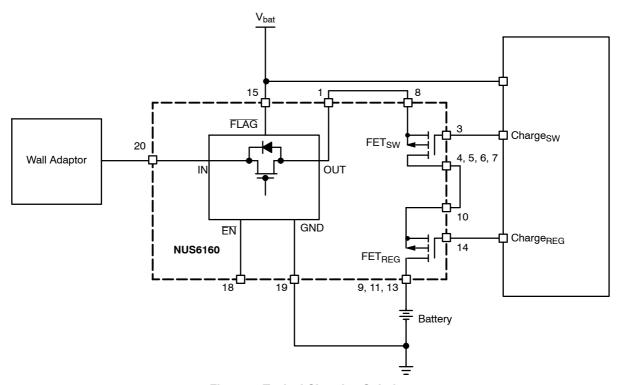

This device represents a new level of safety and integration by combining an overvoltage protection circuit (OVP) with a dual 20 V P-channel power MOSFET. The OVP is specifically designed to protect sensitive electronic circuitry from overvoltage transients and power supply faults. During such events, the IC quickly disconnects the input supply from the load, thus protecting it. The integration of the additional transistor and power MOSFET reduces layout space and promotes better charging performance.

The IC is optimized for applications that use an external AC-DC adapter or a car accessory charger to power a portable product or recharge its internal batteries.

#### **Features**

- Overvoltage Turn-Off Time of Less Than 1.5 µs

- Undervoltage Lockout Protection; 3.0 V, Nominal

- High Accuracy Undervoltage Threshold of 5.0%

- -20 V Integrated P-Channel Power MOSFET

- Low  $R_{DS(on)} = 64 \text{ m}\Omega @ -4.5 \text{ V}$

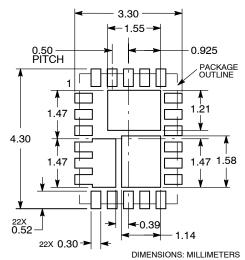

- Compact 3.0 x 4.0 mm QFN Package

- Maximum Solder Reflow Temperature @ 260°C

- This is a Pb-Free Device

#### **Benefits**

- Provide Battery Protection

- Integrated Solution Offers Cost and Space Savings

- Integrated Solution Improves System Reliability

- Optimized for Commercial PMUs from Top Suppliers

### **Applications**

- Portable Computers and PDAs

- Cell Phones and Handheld Products

- Digital Cameras

December, 2008 - Rev. 0

### ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAM**

CASE 485AT

NUS6160 = Device Code

= Assembly Location

L = Wafer Lot = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |  |  |

|--------------|--------------------|-----------------------|--|--|

| NUS6160MNTWG | QFN22<br>(Pb-Free) | 3000 /<br>Tape & Reel |  |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

**Publication Order Number:**

NUS6160MN/D

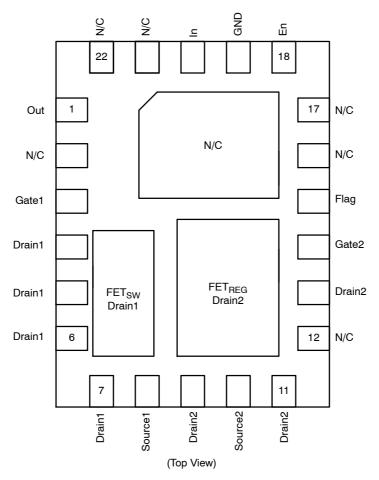

Figure 1. Pinout

Figure 2. Typical Charging Solution

## **MAXIMUM RATINGS** ( $T_J = 25^{\circ}C$ , unless otherwise stated)

| Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Symbol                                                  | Min                                                                  | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------|------|------|

| V <sub>IN</sub> to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>IN</sub>                                         | -0.3                                                                 | 21   | V    |

| OUT, EN, FLAG Pins Voltage to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_{OUT}$ , $\overline{V_{EN}}$ , $\overline{V_{FLAG}}$ | -0.3                                                                 | 7.0  | V    |

| Maximum Current from V <sub>IN</sub> to V <sub>OUT</sub> (PMOS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>max</sub>                                        |                                                                      | 600  | mA   |

| Drain-to-Source Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>DSS</sub>                                        |                                                                      | -20  | V    |

| Gate-to-Source Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>GS</sub>                                         | -8.0                                                                 | 8.0  | V    |

| Continuous Drain Current, Steady State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I <sub>D</sub>                                          |                                                                      | -2.0 | Α    |

| Pulsed Drain Current, t <sub>p</sub> = 10 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>DM</sub>                                         |                                                                      | -4.0 | Α    |

| Source Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Is                                                      |                                                                      | -1.1 | Α    |

| Operating Ambient Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T <sub>A</sub>                                          | -40                                                                  | 85   | °C   |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T <sub>STG</sub>                                        | -55                                                                  | 150  | °C   |

| Operating Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TJ                                                      |                                                                      | 150  | °C   |

| Thermal Resistance (Note 1)  1 in² (645 mm²) (All devices fully enhanced)  OVP FET  FET <sub>SW</sub> FET <sub>REG</sub> 1 in² (645 mm²) (OVP and FET <sub>SW</sub> fully enhanced, 1 V drop across FET <sub>REG</sub> )  OVP FET  FET <sub>SW</sub> FET <sub>REG</sub> 0.25 in² (161 mm²) (All devices fully enhanced)  OVP FET  FET <sub>SW</sub> FET <sub>REG</sub> 0.25 in² (161 mm²) (OVP and FET <sub>SW</sub> fully enhanced, 1 V drop across FET <sub>REG</sub> )  OVP FET  FET <sub>SW</sub> FET <sub>REG</sub> FET <sub>SW</sub> FET <sub>REG</sub> | θJA                                                     | 68<br>42<br>46<br>43<br>39<br>80<br>79<br>53<br>56<br>53<br>49<br>92 |      | °C/W |

| ESD Performance (Human Body Model) Pins 1, 15, 18, 19, 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                       |                                                                      | 2.5  | kV   |

| Lead Temperature for Soldering Purposes (1/8" from case for 10 s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | T <sub>L</sub>                                          |                                                                      | 260  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

<sup>1. 1</sup> oz. copper, double sided board. Thermal impedance requires total for  $\Delta T$  calculations. See example in thermal description.

### **PIN DESCRIPTION**

| Pin                  | Name                      | Description                                                                                                                                                                                                                                                                                                                  |

|----------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | Out                       | This pin is the output of the internal OVP chip. It must be connected to the source of the upper FET (Pin 8).                                                                                                                                                                                                                |

| 3                    | Gate FET <sub>SW</sub>    | This pin is the gate of the upper FET which is normally used for a switch in series with the battery. It is controlled by the PMU.                                                                                                                                                                                           |

| 4, 5, 6, 7           | Drain FET <sub>SW</sub>   | These pins are the drain of the upper FET. For the lowest on resistance connect all pins together. This set of pins must be connected to the source of the lower (regulator) FET, Pin 10.                                                                                                                                    |

| 8                    | Source FET <sub>SW</sub>  | This pin is the source of the upper FET and must be connected to the output pin of the internal OVP chip (Pin 1).                                                                                                                                                                                                            |

| 9, 11, 13            | Drain FET <sub>REG</sub>  | These pins are the drain of the lower FET which is normally used for the regulation function. It connects to the positive terminal of the battery.                                                                                                                                                                           |

| 10                   | Source FET <sub>REG</sub> | This pin is the source of the lower FET and must be connected to the drain pins of the upper FET.                                                                                                                                                                                                                            |

| 12                   | N/C                       | This pin has no internal connections and is isolated from all internal circuitry within the chip.                                                                                                                                                                                                                            |

| 14                   | Gate FET <sub>REG</sub>   | This pin is the gate of the lower FET which is normally used for the regulation function in series with the battery. It is controlled by the PMU.                                                                                                                                                                            |

| 15                   | FLAG                      | The fault flag is an open drain output and therefore requires a pullup resistor. The FLAG pin will be driven low when the input voltage exceeds the OVLO trip level.                                                                                                                                                         |

| 2, 16, 17,<br>21, 22 | N/C                       | These pins are connected to the ground of the analog chip. This is a medium impedance connection and should not be used for the ground signal. These pins should either be left floating or connected to ground, but not any other potential. If these pins are connected to ground, the ground pin (19) must still be used. |

| 18                   | EN                        | The ENABLE pin must be held low for normal operation. When this pin is tied high the unit will be shut down. The state of the enable pin has no impact on the FAULT pin.                                                                                                                                                     |

| 19                   | Gnd                       | This is the ground reference pin for the internal OVP chip.                                                                                                                                                                                                                                                                  |

| 20                   | In                        | This pin is the input to the internal OVP chip and connects to the wall, or car adaptor.                                                                                                                                                                                                                                     |

### **OVP ELECTRICAL CHARACTERISTICS**

(Min/Max limits values ( $-40^{\circ}C < T_A < +85^{\circ}C$ ) and  $V_{in} = +5.0$  V. Typical values are  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| Characteristic                                  | Symbol               | Conditions                                                                                                                                          | Min  | Тур  | Max  | Unit |

|-------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage Range                             | V <sub>in</sub>      |                                                                                                                                                     | 1.2  |      | 20   | V    |

| Undervoltage Lockout<br>Threshold               | UVLO                 | V <sub>in</sub> falls down UVLO threshold                                                                                                           | 2.85 | 3.0  | 3.15 | ٧    |

| Undervoltage Lockout<br>Hysteresis              | UVLO <sub>hyst</sub> |                                                                                                                                                     | 30   | 50   | 70   | mV   |

| Overvoltage Lockout Threshold                   | OVLO                 | V <sub>in</sub> rises up OVLO threshold                                                                                                             | 6.9  | 7.07 | 7.4  | V    |

| Overvoltage Lockout Hysteresis                  | OVLO <sub>hyst</sub> |                                                                                                                                                     | 50   | 100  | 125  | mV   |

| V <sub>in</sub> versus V <sub>out</sub> Dropout | $V_{drop}$           | V <sub>in</sub> = 5 V, I charge = 500 mA                                                                                                            |      | 105  | 200  | mV   |

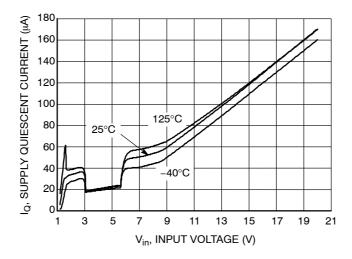

| Supply Quiescent Current                        | ldd                  | No Load, V <sub>in</sub> = 5.25 V                                                                                                                   |      | 24   | 35   | μΑ   |

| OVLO Supply Current                             | Idd <sub>ovlo</sub>  | V <sub>in</sub> = 8 V                                                                                                                               |      | 50   | 85   | μΑ   |

| Output Off State Current                        | I <sub>std</sub>     | V <sub>in</sub> = 5.25 V, EN = 1.2 V                                                                                                                |      | 26   | 37   | μΑ   |

| FLAG Output Low Voltage                         | Vol <sub>flag</sub>  | V <sub>in</sub> > OVLO, Sink 1 mA on FLAG pin                                                                                                       |      |      | 400  | mV   |

| FLAG Leakage Current                            | FLAG <sub>leak</sub> | FLAG level = 5 V                                                                                                                                    |      | 5.0  |      | nA   |

| EN Voltage High                                 | $V_{ih}$             | V <sub>in</sub> from 3.3 V to 5.25 V                                                                                                                | 1.2  |      |      | V    |

| EN Voltage Low                                  | V <sub>ol</sub>      | V <sub>in</sub> from 3.3 V to 5.25 V                                                                                                                |      |      | 0.4  | ٧    |

| EN Leakage Current                              | EN <sub>leak</sub>   | EN = 5.5 V or GND                                                                                                                                   |      | 170  |      | nA   |

| TIMINGS                                         |                      |                                                                                                                                                     |      |      |      |      |

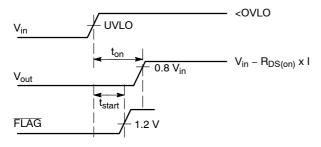

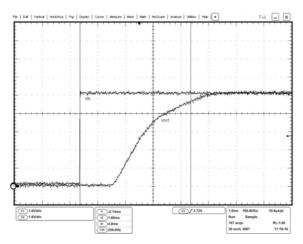

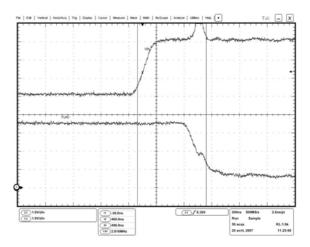

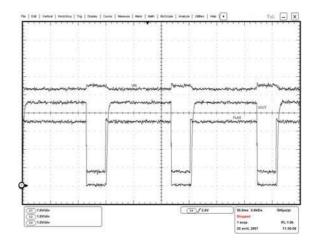

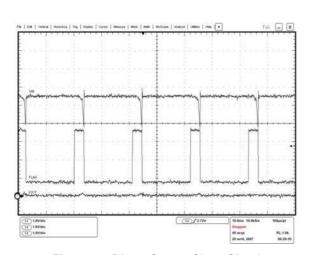

| Start Up Delay                                  | t <sub>on</sub>      | From V <sub>in</sub> > UVLO to V <sub>out</sub> = 0.8xV <sub>in</sub> , See Fig 3 & 9                                                               |      | 4.0  | 15   | ms   |

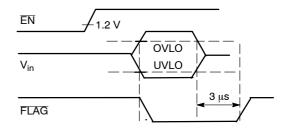

| FLAG going up Delay                             | t <sub>start</sub>   | From V <sub>in</sub> > UVLO to FLAG = 1.2 V, See Fig 3 & 10                                                                                         |      | 3.0  |      | μs   |

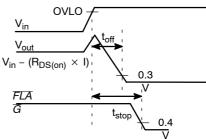

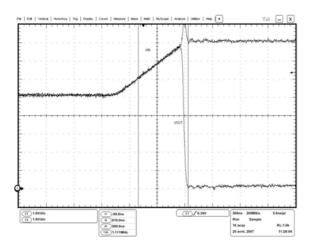

| Output Turn Off Time                            | t <sub>off</sub>     | From $V_{in}$ > OVLO to $V_{out} \le 0.3$ V, See Fig 4 & 11 $V_{in}$ increasing from normal operation to >OVLO at 1V/ $\mu$ s. No output capacitor. |      | 0.8  | 1.5  | μs   |

| Alert Delay                                     | t <sub>stop</sub>    | From $V_{in}$ > OVLO to $\overline{FLAG} \le 0.4$ V, See Fig 4 & 12 $V_{in}$ increasing from normal operation to >OVLO at $1V/\mu s$                |      | 1.0  | 2.0  | μs   |

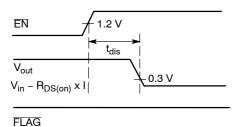

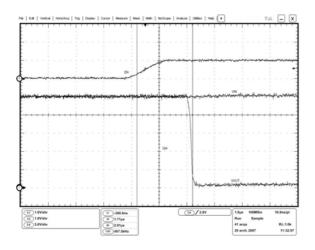

| Disable Time                                    | t <sub>dis</sub>     | From $\overline{\text{EN}}$ 0.4 to 1.2V to $V_{\text{out}} \leq$ 0.3V, See Fig 5 & 13 $V_{\text{in}} = 4.75$ V. No output capacitor.                |      | 2.0  |      | μs   |

| Thermal Shutdown Temperature                    | T <sub>sd</sub>      |                                                                                                                                                     |      | 150  |      | °C   |

| Thermal Shutdown Hysteresis                     | T <sub>sdhyst</sub>  |                                                                                                                                                     |      | 30   |      | °C   |

NOTE: Thermal Shutdown parameter has been fully characterized and guaranteed by design.

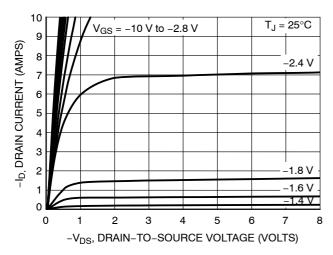

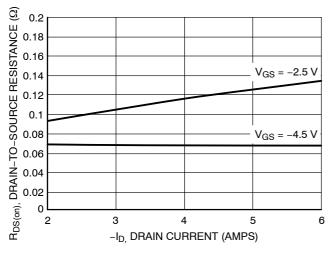

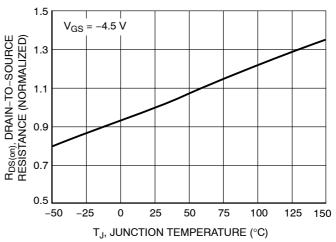

### $\textbf{MOSFET ELECTRICAL CHARACTERISTICS} \ (T_J = 25^{\circ}C \ unless \ otherwise \ noted, \ all \ parameters \ apply \ to \ both \ FET_{SW} \ and$ FET<sub>REG</sub>)

| Characteristic                                               | Symbol                               | Test Condition                                                                 | Min   | Тур  | Max          | Unit  |

|--------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------|-------|------|--------------|-------|

| OFF CHARACTERISTICS                                          | •                                    |                                                                                | l l   |      |              |       |

| Drain-to-Source Breakdown Voltage                            | V <sub>(Br)DSS</sub>                 | $V_{GS} = 0 \text{ V}, I_D = -250 \mu\text{A}$                                 | -20   |      |              | V     |

| Drain-to-Source Breakdown Voltage<br>Temperature Coefficient | V <sub>(Br)DSS/</sub> T <sub>J</sub> |                                                                                |       | -15  |              | mV/°C |

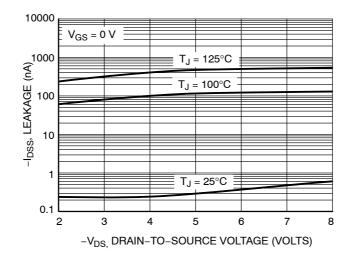

| Zero Gate Voltage Drain Current                              | I <sub>DSS</sub>                     | $V_{GS} = 0 V \ V_{DS} = -16 V \ T_{J} = 25^{\circ}C \ T_{J} = 85^{\circ}C$    |       |      | -1.0<br>-5.0 | μΑ    |

| Gate-to-Source Leakage Current                               | I <sub>GSS</sub>                     | $V_{DS} = 0 \text{ V}, V_{GS} = \pm 8.0 \text{ V}$                             |       |      | ±100         | nA    |

| ON CHARACTERISTICS (Note 2)                                  |                                      | <u> </u>                                                                       |       |      |              |       |

| Gate Threshold Voltage                                       | V <sub>GS(TH)</sub>                  | $V_{GS} = V_{DS}, I_{D} = -250 \mu A$                                          | -0.45 |      | -1.5         | V     |

| Gate Threshold Temperature Coefficient                       | V <sub>GS(TH)/</sub> T <sub>J</sub>  |                                                                                |       | 2.7  |              | mV/°C |

| Drain-to-Source On Resistance                                | R <sub>DS(ON)</sub>                  | $V_{GS} = -4.5 \text{ V}, I_D = -1.0 \text{ A}$                                |       | 64   | 80           | mΩ    |

|                                                              |                                      | V <sub>GS</sub> = -4.5 V, I <sub>D</sub> = -0.6 A                              |       | 62   | 80           |       |

| Forward Transconductance                                     | 9FS                                  | $V_{DS} = -10 \text{ V}, I_{D} = -2.9 \text{ A}$                               |       | 7.0  |              | S     |

| CHARGES, CAPACITANCES, AND GATE RESIST                       | ANCE                                 |                                                                                |       |      |              |       |

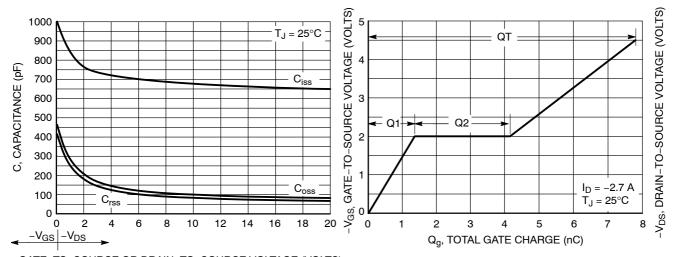

| Input Capacitance                                            | C <sub>ISS</sub>                     | V <sub>GS</sub> = 0 V, f = 1.0 MHz,                                            |       | 750  |              | pF    |

| Output Capacitance                                           | C <sub>OSS</sub>                     | V <sub>DS</sub> = -16 V                                                        |       | 100  |              | ] !   |

| Reverse Transfer Capacitance                                 | C <sub>RSS</sub>                     |                                                                                |       | 45   |              |       |

| Total Gate Charge                                            | Q <sub>G(TOT)</sub>                  |                                                                                |       | 7.6  | 8.6          | nC    |

| Gate-to-Source Charge                                        | Q <sub>GS</sub>                      | $V_{GS} = -4.5 \text{ V}, V_{DS} = -16 \text{ V},$<br>$I_{D} = -2.6 \text{ A}$ |       | 1.3  |              |       |

| Gate-to-Drain Charge                                         | $Q_{GD}$                             |                                                                                |       | 2.6  |              |       |

| SWITCHING CHARACTERISTICS (Note 3)                           | ·                                    |                                                                                |       |      |              |       |

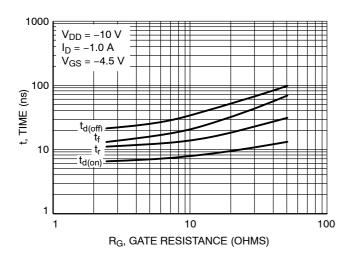

| Turn-On Delay Time                                           | t <sub>d(ON)</sub>                   |                                                                                |       | 5.5  |              | ns    |

| Rise Time                                                    | t <sub>r</sub>                       | $V_{GS} = -4.5 \text{ V}, V_{DD} = -16 \text{ V},$                             |       | 12   |              |       |

| Turn-Off Delay Time                                          | t <sub>d(OFF)</sub>                  | $I_D = -2.6 \text{ A}, R_G = 2.0 \Omega$                                       |       | 32   |              |       |

| Fall Time                                                    | t <sub>f</sub>                       |                                                                                |       | 23   |              |       |

| DRAIN-SOURCE DIODE CHARACTERISTICS                           | ·                                    |                                                                                |       |      |              |       |

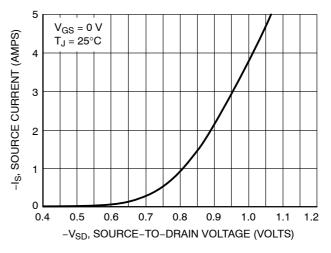

| Forward Diode Voltage                                        | V <sub>SD</sub>                      | V <sub>GS</sub> = 0 V, I <sub>S</sub> = -1.1 A                                 |       | -0.8 | -1.2         | V     |

| Reverse Recovery Time                                        | t <sub>RR</sub>                      |                                                                                |       | 20   |              | ns    |

| Charge Time                                                  | ta                                   | $V_{GS} = 0 \text{ V, } dl_S/dt = 100 \text{ A/}\mu\text{s,}$                  |       | 15   |              |       |

| Discharge Time                                               | tb                                   | I <sub>S</sub> = 1.0 A                                                         |       | 5    |              | 1     |

| Reverse Recovery Charge                                      | Q <sub>RR</sub>                      |                                                                                |       | 0.01 |              | μC    |

Pulse test: pulse width ≤ 300 μs, duty cycle ≤ 2%

Switching characteristics are independent of operating junction temperatures

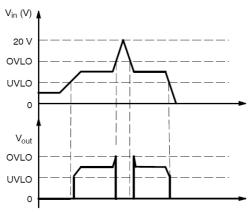

Figure 3. Start Up Sequence

Figure 4. Shutdown on Over Voltage Detection

Figure 5. Disable on  $\overline{EN} = 1$

Figure 6.  $\overline{FLAG}$  Response with  $\overline{EN} = 1$

Figure 7.

Figure 8.

### TYPICAL OPERATING CHARACTERISTICS

Figure 9. Startup V<sub>in</sub> = Ch1, V<sub>out</sub> = Ch3

Figure 11. Output Turn Off Time  $V_{in} = Ch1, V_{out} = Ch2$

Figure 13. Disable Time EN = Ch1, V<sub>out</sub> = Ch2, FLAG = Ch3

Figure 10. FLAG Going Up Delay V<sub>out</sub> = Ch3, FLAG = Ch2

Figure 12. Alert Delay V<sub>out</sub> = Ch1, FLAG = Ch3

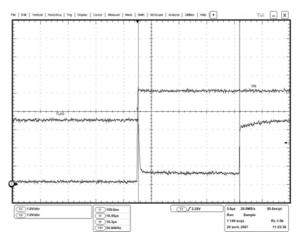

Figure 14. Thermal Shutdown  $V_{in}$  = Ch1,  $V_{out}$  = Ch2, FLAG = Ch3

### **TYPICAL OPERATING CHARACTERISTICS**

Figure 15. Direct Output Short Circuit

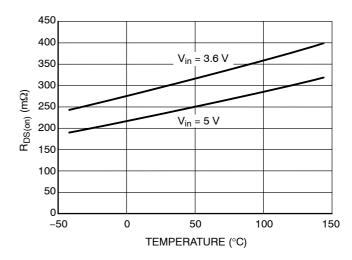

Figure 16. R<sub>DS(on)</sub> vs. Temperature (Load = 500 mA)

Figure 17. Supply Quiescent Current vs. V<sub>in</sub>

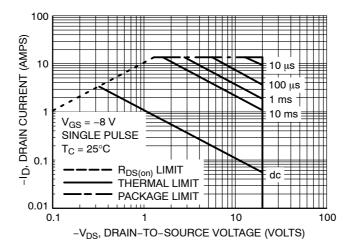

### TYPICAL PERFORMANCE CURVES (T<sub>J</sub> = 25°C unless otherwise noted)

8

7

(AMPS) ID, DRAIN CURRENT 6 5 3 125 2 25°C -55°C 0 0.5 0 2.5 3 3.5 1.5 2

Figure 18. On-Region Characteristics

-V<sub>GS</sub>, GATE-TO-SOURCE VOLTAGE (VOLTS) Figure 19. Transfer Characteristics

Figure 20. On-Resistance vs. Drain Current and Gate Voltage

Figure 21. On-Resistance Variation with **Temperature**

Figure 22. Drain-to-Source Leakage Current vs. Voltage

### TYPICAL PERFORMANCE CURVES (T<sub>J</sub> = 25°C unless otherwise noted)

GATE-TO-SOURCE OR DRAIN-TO-SOURCE VOLTAGE (VOLTS)

Figure 23. Capacitance Variation

Figure 24. Gate-to-Source and Drain-to-Source Voltage vs. Total Gate Charge

Figure 25. Resistive Switching Time Variation vs. Gate Resistance

Figure 26. Diode Forward Voltage vs. Current

Figure 27. Maximum Rated Forward Biased Safe Operating Area

#### **Operational Description**

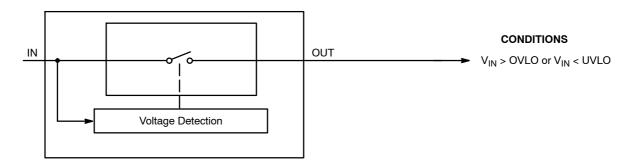

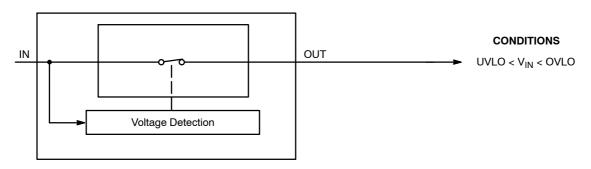

The NUS6160 provides overvoltage protection for positive voltages up to 20 V. A P–Channel FET protects the load connected on the  $V_{out}$  pin, against positive overvoltage conditions. The Output follows the  $V_{BUS}$  level until OVLO threshold is reached.

#### **Undervoltage Lockout (UVLO)**

To ensure proper operation under all conditions, the device has a built—in undervoltage lock out (UVLO) circuit. As the input ramps from 0 V, the output remains disconnected from input until the  $V_{in}$  voltage is above 3.2 V nominal. The FLAG output is pulled to low as long as  $V_{in}$  does not reach the UVLO threshold. This circuit incorporates hysteresis on the UVLO pin to provide noise immunity to transient condition.

Figure 28. Output Characteristic vs. Vin

#### Overvoltage Lockout (OVLO)

To protect connected systems on Vout Pin from overvoltage, the device has a built–in overvoltage lock out (OVLO) circuit. During an overvoltage condition, the output remains disabled until the input voltage is reduced to below the OVLO hysteresis level. The FLAG output is tied to low until Vin is higher than OVLO. This circuit incorporates hysteresis on the OVLO pin to provide noise immunity from transient conditions.

### **FLAG Output**

The NUS6160 provides a FLAG output, which alerts external systems that a fault has occurred. This pin goes low as soon as the OVLO threshold is exceeded. When Vin level recovers to its normal range the FLAG is set high.

The FLAG Pin is an open drain output, thus a pullup resistor (typically 1 M $\Omega$  – Minimum 10 k $\Omega$ ) must be provided to  $V_{battery}$ .

#### **EN Input**

To enable normal operation, the EN pin shall be forced low or connected to ground. A high level on the pin disconnects the OUT Pin from IN Pin. EN does not override an OVLO or UVLO fault.

#### Internal PMOS FET

The NUS6160 includes an internal PMOS FET which connects the input to the output pin. This FET is turned off

in the event of an overvoltage condition to protect the output from a positive overvoltage condition. The low Rds(on), during normal operation will minimize the voltage drop across the device. (See Figure 16).

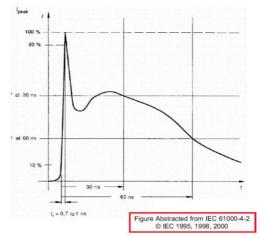

#### **ESD Tests**

The NUS6160 meets the requirements of the IEC61000-4-2, level 4 (Input pin, 1  $\mu$ F mounted on board). For the air discharge condition, Vin is protected up to  $\pm 15$  kV. In the contact condition, Vin is protected up to  $\pm 8$  kV ESD. Please refer to Figure 29 to see the IEC 61000-4-2 electrostatic discharge waveform.

Figure 29. IEC 61000-4-2 Curve

#### Thermal Impedance

Due to cross heating of the three dice in the package, the equivalent thetas are given for this device rather than the individual thetas. To calculate the junction temperatures of a single die, the total power must be used. For example, given the following parameters, the die temperatures will be as shown:

$I_{dc} = 500 \text{ mA}$

$R_{DS(on)}$  OVP = 305 m $\Omega$

$R_{DS(on)}$  FETsw = 72 m $\Omega$

FET<sub>reg</sub> has a 1.0 V Drop

Board copper area =  $161 \text{ mm}^2$

Calculate the individual power dissipations:

$P_{OVP} = (0.50 \text{ A})^2 \text{ x } .305 \Omega = 0.076 \text{ W}$

$P_{SW} = (0.50 \text{ A})^2 \text{ x .072 } \Omega = 0.018 \text{ W}$

$P_{REG} = 0.50 \text{ A} \text{ x } 1.0 \text{ V} = 0.50 \text{ W}$

$P_{TOT} = 0.076 + 0.018 + 0.50 = 0.594 \text{ W}$

From the Maximum ratings table for thetas, 161 mm<sup>2</sup> and 1 V drop across FET<sub>REG</sub>:

OVP FET  $53^{\circ}$ C/W FET<sub>SW</sub>  $49^{\circ}$ C/W FET<sub>REG</sub>  $92^{\circ}$ C/W

The die temperature rises above ambient are:

$T_{OVP} = 53^{\circ}C/W \times 0.594 W = 32^{\circ}C$

$T_{SW} = 49^{\circ}C/W \times 0.594 W = 29^{\circ}C$

$T_{REG} = 92^{\circ}C/W \times 0.594 W = 55^{\circ}C$

22X L

CAB

C NOTE 3

22X b

$\oplus$

е G2

D2

**BOTTOM VIEW**

0.10

0.05

G1

D4

D3

**DETAIL A**

**E3**

G

16X K

#### **DATE 17 SEP 2008** NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION 6 APPLIES TO PLATED

- TERMINAL AND IS MEASURED BETWEEN

0.15 AND 0.30 MM FROM TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED

PADS AS WELL AS THE TERMINALS.

|     | MILLIMETERS    |          |       |  |  |

|-----|----------------|----------|-------|--|--|

| DIM | MIN            | NOM      | MAX   |  |  |

| Α   | 0.80           | 0.90     | 1.00  |  |  |

| A1  | 0.00           | 0.025    | 0.05  |  |  |

| АЗ  |                | 0.20 REI |       |  |  |

| b   | 0.20           | 0.25     | 0.30  |  |  |

| D   |                | 3.00 BS0 |       |  |  |

| D2  | 1.45           | 1.50     | 1.55  |  |  |

| D3  | 0.52           | 0.57     | 0.62  |  |  |

| D4  | 1.02 1.07 1.12 |          |       |  |  |

| Е   |                | 4.00 BS0 |       |  |  |

| E2  | 1.05 1.10 1.1  |          |       |  |  |

| E3  | E3 1.30 1.35   |          | 1.40  |  |  |

| E4  | 1.40           | 1.45     | 1.50  |  |  |

| е   |                | 0.50 BS0 |       |  |  |

| K   | 0.25           |          |       |  |  |

| L   | 0.30           | 0.325    | 0.35  |  |  |

| L1  |                |          | 0.15  |  |  |

| G   | 1.35           | 1.40     | 1.50  |  |  |

| G1  | 0.95           | 1.05     | 1.15  |  |  |

| G2  | 0.855          | 0.885    | 0.915 |  |  |

XXXXX = Specific Device Code

= Assembly Location Α

= Wafer Lot

L Υ = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part

Pb-Free indicator, "G" or microdot " ■", may or may not be present.

#### **SOLDERING FOOTPRINT\***

| DOCUMENT NUMBER: | 98AON30555E       | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | QFN22, 3X4, 0.5 P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |  |

**GENERIC**

MARKING DIAGRAM\*

**XXXXX**

XXXXX

ALYW=

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales