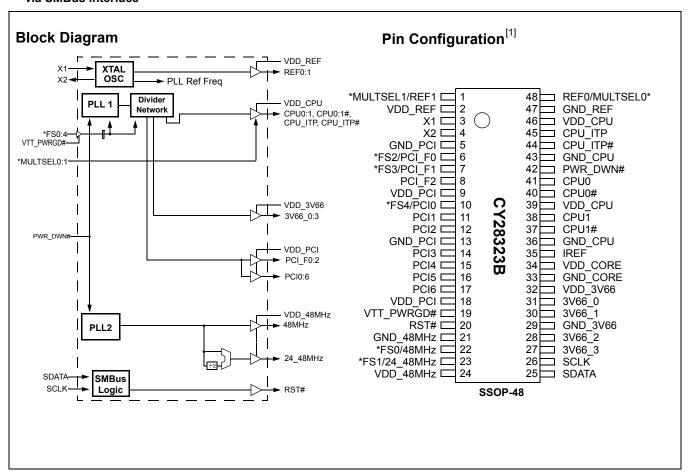

# FTG for Intel<sup>®</sup> Pentium<sup>®</sup> 4 CPU and Chipsets

#### **Features**

- Compatible to Intel® CK-Titan & CK-408 Clock Synthesizer/Driver Specifications

- System frequency synthesizer for Intel Brookdale 845 and Brookdale - G Pentium® 4 Chipsets

- Programmable clock output frequency with less than 1 MHz increment

- Integrated fail-safe Watchdog timer for system recovery

- Automatically switch to HW selected or SW programmed clock frequency when Watchdog timer times out

- Capable of generating system RESET after a Watchdog timer time-out occurs or a change in output frequency via SMBus interface

- Support SMBus byte read/write and block read/ write operations to simplify system BIOS development

- Vendor ID and Revision ID support

- · Programmable drive strength support

- Programmable output skew support

- · Power management control inputs

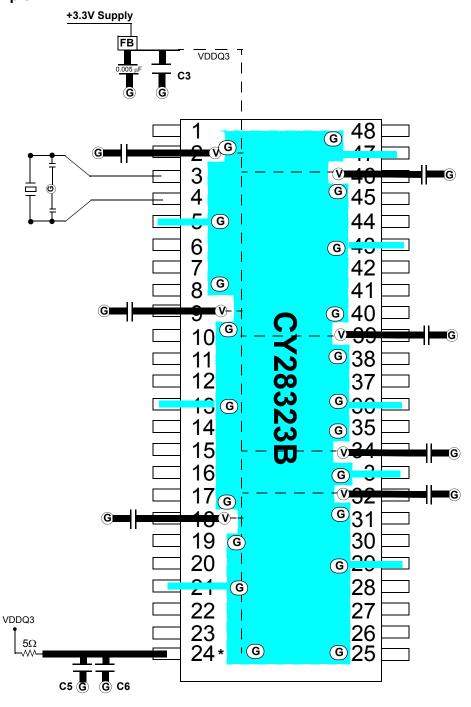

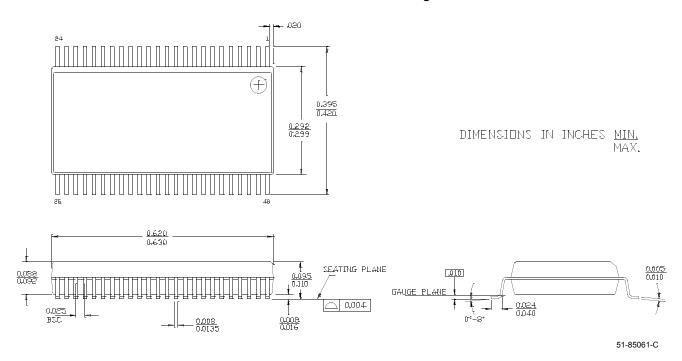

- Available in 48-pin SSOP

| CPU | 3V66 | PCI  | REF | 48M | 24_48M |

|-----|------|------|-----|-----|--------|

| x 3 | x 4  | x 10 | x 2 | x 1 | x 1    |

#### Note:

1. Signals marked with '\*' and "^" have internal pull-up and pull-down resistors respectively.

### **Pin Definitions**

| Pin Name             | Pin No.                   | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|---------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1                   | 3                         | I           | Crystal Connection or External Reference Frequency Input: This pin has dual functions. It can be used as an external 14.318-MHz crystal connection or as an external reference frequency input.                                                                                                                                                                                                        |

| X2                   | 4                         | 0           | <b>Crystal Connection:</b> Connection for an external 14.318-MHz crystal. If using an external reference, this pin must be left unconnected.                                                                                                                                                                                                                                                           |

| REF0/MULTSEL0        | 48                        | I/O         | Reference Clock 0/Current Multiplier Selection 0: 3.3V 14.318-MHz clock output. This pin also serves as a power-on strap option to determine the current multiplier for the CPU clock outputs. The MULTSEL1:0 definitions are as follows: MULTSEL1:0  00 = Ioh is 4 x IREF  01 = Ioh is 5 x IREF  10 = Ioh is 7 x IREF                                                                                 |

| REF1/MULTSEL1        | 1                         | I/O         | Reference Clock 1/Current Multiplier Selection 1: 3.3V 14.318-MHz clock output. This pin also serves as a power-on strap option to determine the current multiplier for the CPU clock outputs. The MULTSEL1:0 definitions are as follows: MULTSEL1:0  00 = Ioh is 4 x IREF  01 = Ioh is 5 x IREF  10 = Ioh is 7 x IREF                                                                                 |

| CPU0:1, CPU0:1#      | 41, 38, 40,<br>37         | 0           | <b>CPU Clock Outputs:</b> Frequency is set by the FS0:4 inputs or through serial input interface.                                                                                                                                                                                                                                                                                                      |

| CPU_ITP,<br>CPU_ITP# | 44, 45                    | I/O         | <b>CPU Clock Output for ITP:</b> Frequency is set by the FS0:4 inputs or through serial input interface.                                                                                                                                                                                                                                                                                               |

| 3V66_0:3             | 31, 30, 28,<br>27         | 0           | 66-MHz Clock Outputs: 3.3V fixed 66-MHz clock.                                                                                                                                                                                                                                                                                                                                                         |

| PCI_F0/FS2           | 6                         | I/O         | <b>Free-running PCI Output 0/Frequency Select 2:</b> 3.3V free-running PCI output. This pin also serves as a power-on strap option to determine device operating frequency as described in the Frequency Selection Table.                                                                                                                                                                              |

| PCI_F1/FS3           | 7                         | I/O         | <b>Free-running PCI Output 1/Frequency Select 3:</b> 3.3V free-running PCI output. This pin also serves as a power-on strap option to determine device operating frequency as described in <i>Table 4</i> .                                                                                                                                                                                            |

| PCI_F2               | 8                         | I/O         | Free-running PCI Output 2: 3.3V free-running PCI output.                                                                                                                                                                                                                                                                                                                                               |

| PCI0/FS4             | 10                        | I/O         | <b>PCI Output 0/Frequency Select 4:</b> 3.3V PCI output. This pin also serves as a power-on strap option to determine device operating frequency as described in <i>Table 4</i> .                                                                                                                                                                                                                      |

| PCI1:6               | 11, 12, 14,<br>15, 16, 17 | 0           | PCI Clock Output 1 to 6: 3.3V PCI clock outputs.                                                                                                                                                                                                                                                                                                                                                       |

| 48MHz/FS0            | 22                        | I/O         | 48-MHz Output/Frequency Select 0: 3.3V fixed 48-MHz, non-spread spectrum output. This pin also serves as a power-on strap option to determine device operating frequency as described in Table 4.  This output will be used as the reference clock for USB host controller in Intel 845 (Brookdale) platforms. For Intel Brookdale - G platforms, this output will be used as the VCH reference clock. |

# Pin Definitions (continued)

| D' N                                                        | 5: N                         | Pin                   | Dia Bassa di Ata                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------|------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                    | Pin No.                      | Type                  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 24_48MHz/FS1                                                | 23                           | I/O                   | 24- or 48-MHz Output/Frequency Select 1: 3.3V fixed 24-MHz or 48-MHz non-spread spectrum output. This pin also serves as a power-on strap option to determine device operating frequency as described in Table 4.  This output will be used as the reference clock for SIO devices in Intel 845 (Brookdale) platforms. For Intel Brookdale - G platforms, this output will be used as the reference clock for both USB host controller and SIO devices. We recommend system designer to configure this output as 48 MHz and "HIGH Drive" by setting Byte [5], Bit [0] and Byte [9], Bit [7], respectively. |

| PWR_DWN#                                                    | 42                           | I                     | <b>Power Down Control:</b> 3.3V LVTTL-compatible input that places the device in power-down mode when held LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCLK                                                        | 26                           | I                     | SMBus Clock Input: Clock pin for serial interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDATA                                                       | 25                           | I/O                   | SMBus Data Input: Data pin for serial interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RST#                                                        | 20                           | O<br>(open-<br>drain) | System Reset Output: Open-drain system reset output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IREF                                                        | 35                           | I                     | <b>Current Reference for CPU Output:</b> A precision resistor is attached to this pin which is connected to the internal current reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VTT_PWRGD#                                                  | 19                           | I                     | Powergood from Voltage Regulator Module (VRM): 3.3V LVTTL input. VTT_PWRGD# is a level-sensitive strobe used to determine when FS0:4 and MULTSEL0:1 inputs are valid and OK to be sampled (Active LOW). Once VTT_PWRGD# is sampled LOW, the status of this input will be ignored.                                                                                                                                                                                                                                                                                                                          |

| VDD_REF,<br>VDD_PCI,<br>VDD_48MHz,<br>VDD_3V66,<br>VDD_CPU  | 2, 9, 18, 24,<br>32, 39, 46  | Р                     | <b>3.3V Power Connection:</b> Power supply for CPU outputs buffers, 3V66 output buffers, PCI output buffers, reference output buffers and 48-MHz output buffers. Connect to 3.3V.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND_PCI,<br>GND_48MHz,<br>GND_3V66,<br>GND_CPU,<br>GND_REF, | 5, 13, 21, 29,<br>36, 43, 47 | G                     | <b>Ground Connection:</b> Connect all ground pins to the common system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDD_CORE                                                    | 34                           | Р                     | <b>3.3V Analog Power Connection:</b> Power supply for core logic, PLL circuitry. Connect to 3.3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND_CORE                                                    | 33                           | G                     | Analog Ground Connection: Ground for core logic, PLL circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Swing Select Functions**

| MULTSEL1 | MULTSEL0 | Board Target<br>Trace/Term Z | Reference R, IREF = VDD/(3*Rr) | Output<br>Current        | V <sub>OH</sub> @ Z |

|----------|----------|------------------------------|--------------------------------|--------------------------|---------------------|

| 0        | 0        | 50Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 4*Iref | 1.0V @ 50           |

| 0        | 0        | 60Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 4*Iref | 1.2V @ 60           |

| 0        | 1        | 50Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 5*Iref | 1.25V @ 50          |

| 0        | 1        | 60Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 5*Iref | 1.5V @ 60           |

| 1        | 0        | 50Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 6*Iref | 1.5V @ 50           |

| 1        | 0        | 60Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 6*Iref | 1.8V @ 60           |

| 1        | 1        | 50Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 7*Iref | 1.75V @ 50          |

| 1        | 1        | 60Ω                          | Rr = 221 1%,<br>IREF = 5.00 mA | I <sub>OH</sub> = 7*Iref | 2.1V @ 60           |

| 0        | 0        | 50Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 4*Iref | 0.47V @ 50          |

| 0        | 0        | 60Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 4*Iref | 0.56V @ 60          |

| 0        | 1        | 50Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 5*Iref | 0.58V @ 50          |

| 0        | 1        | 60Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 5*Iref | 0.7V @ 60           |

| 1        | 0        | $50\Omega$                   | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 6*Iref | 0.7V @ 50           |

| 1        | 0        | 60Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 6*Iref | 0.84V @ 60          |

| 1        | 1        | 50Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 7*Iref | 0.81V @ 50          |

| 1        | 1        | 60Ω                          | Rr = 475 1%,<br>IREF = 2.32 mA | I <sub>OH</sub> = 7*Iref | 0.97V @ 60          |

#### Serial Data Interface

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions such as individual clock output buffers, etc. can be individually enabled or disabled

The register associated with the Serial Data Interface initializes to its default setting upon power-up, and therefore use of this interface is optional. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power management functions.

#### **Data Protocol**

The clock driver serial protocol accepts byte write, byte read, block write and block read operation from the controller. For block write/read operation, the bytes must be accessed in sequential order from lowest to highest byte (most significant bit first) with the ability to stop after any complete byte has been transferred. For byte write and byte read operations, the system controller can access individual indexed bytes. The offset of the indexed byte is encoded in the command code, as described in *Table 1*.

The block write and block read protocol is outlined in *Table 2* while *Table 3* outlines the corresponding byte write and byte read protocol.

The slave receiver address is 11010010 (D2h).

Table 1. Command Code Definition

| Bit | Descriptions                                                                                                                 |

|-----|------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0 = Block read or block write operation 1 = Byte read or byte write operation                                                |

| 6:0 | Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be '0000000'. |

Table 2. Block Read and Block Write Protocol

|       | Block Write Protocol                                        |       | Block Read Protocol                                         |

|-------|-------------------------------------------------------------|-------|-------------------------------------------------------------|

| Bit   | Description                                                 | Bit   | Description                                                 |

| 1     | Start                                                       | 1     | Start                                                       |

| 2:8   | Slave address – 7 bits                                      | 2:8   | Slave address – 7 bits                                      |

| 9     | Write                                                       | 9     | Write                                                       |

| 10    | Acknowledge from slave                                      | 10    | Acknowledge from slave                                      |

| 11:18 | Command Code – 8 bits '00000000' stands for block operation | 11:18 | Command Code – 8 bits '00000000' stands for block operation |

| 19    | Acknowledge from slave                                      | 19    | Acknowledge from slave                                      |

| 20:27 | Byte Count – 8 bits                                         | 20    | Repeat start                                                |

| 28    | Acknowledge from slave                                      | 21:27 | Slave address – 7 bits                                      |

| 29:36 | Data byte 0 – 8 bits                                        | 28    | Read                                                        |

| 37    | Acknowledge from slave                                      | 29    | Acknowledge from slave                                      |

| 38:45 | Data byte 1 – 8 bits                                        | 30:37 | Byte count from slave – 8 bits                              |

| 46    | Acknowledge from slave                                      | 38    | Acknowledge                                                 |

|       | Data Byte N/Slave Acknowledge                               | 39:46 | Data byte from slave – 8 bits                               |

|       | Data Byte N – 8 bits                                        | 47    | Acknowledge                                                 |

|       | Acknowledge from slave                                      | 48:55 | Data byte from slave – 8 bits                               |

|       | Stop                                                        | 56    | Acknowledge                                                 |

|       |                                                             |       | Data bytes from slave/Acknowledge                           |

|       |                                                             |       | Data byte N from slave – 8 bits                             |

|       |                                                             |       | Not Acknowledge                                             |

|       |                                                             |       | Stop                                                        |

Table 3. Byte Read and Byte Write Protocol

|       | Byte Write Protocol                                                                                                                        |       | Byte Read Protocol                                                                                                                         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Description                                                                                                                                | Bit   | Description                                                                                                                                |

| 1     | Start                                                                                                                                      | 1     | Start                                                                                                                                      |

| 2:8   | Slave address – 7 bits                                                                                                                     | 2:8   | Slave address – 7 bits                                                                                                                     |

| 9     | Write                                                                                                                                      | 9     | Write                                                                                                                                      |

| 10    | Acknowledge from slave                                                                                                                     | 10    | Acknowledge from slave                                                                                                                     |

| 11:18 | Command Code – 8 bits '1xxxxxxx' stands for byte operation bit[6:0] of the command code represents the off- set of the byte to be accessed | 11:18 | Command Code – 8 bits '1xxxxxxx' stands for byte operation bit[6:0] of the command code represents the off- set of the byte to be accessed |

| 19    | Acknowledge from slave                                                                                                                     | 19    | Acknowledge from slave                                                                                                                     |

| 20:27 | Data byte – 8 bits                                                                                                                         | 20    | Repeat start                                                                                                                               |

| 28    | Acknowledge from slave                                                                                                                     | 21:27 | Slave address – 7 bits                                                                                                                     |

| 29    | Stop                                                                                                                                       | 28    | Read                                                                                                                                       |

|       |                                                                                                                                            | 29    | Acknowledge from slave                                                                                                                     |

|       |                                                                                                                                            | 30:37 | Data byte from slave – 8 bits                                                                                                              |

|       |                                                                                                                                            | 38    | Not Acknowledge                                                                                                                            |

|       |                                                                                                                                            | 39    | Stop                                                                                                                                       |

# **Data Byte Configuration Map**

### Data Byte 0

| Bit   | Pin# | Name           | Description                               | Power On<br>Default |

|-------|------|----------------|-------------------------------------------|---------------------|

| Bit 7 |      | Spread Select2 | '000' = OFF                               | 0                   |

| Bit 6 |      | Spread Select1 | '001' = Reserved                          | 0                   |

| Bit 5 |      | Spread Select0 | '010' = Reserved                          | 0                   |

|       |      |                | '011' = Reserved                          |                     |

|       |      |                | '100' = ±0.25%                            |                     |

|       |      |                | '101' = -0.5%                             |                     |

|       |      |                | '110' = ±0.5%                             |                     |

|       |      |                | '111' = ±0.38%                            |                     |

| Bit 4 |      | SEL4           | SW Frequency selection bits. See Table 4. | 0                   |

| Bit 3 |      | SEL3           |                                           | 0                   |

| Bit 2 |      | SEL2           |                                           | 0                   |

| Bit 1 |      | SEL1           |                                           | 0                   |

| Bit 0 |      | SEL0           |                                           | 0                   |

### Data Byte 1

| Bit   | Pin#   | Name        | Description       | Power On<br>Default |

|-------|--------|-------------|-------------------|---------------------|

| Bit 7 | 38, 37 | CPU1, CPU1# | (Active/Inactive) | 1                   |

| Bit 6 | 41, 40 | CPU0, CPU0# | (Active/Inactive) | 1                   |

| Bit 5 | 22     | 48MHz       | (Active/Inactive) | 1                   |

| Bit 4 | 23     | 24_48MHz    | (Active/Inactive) | 1                   |

| Bit 3 | 27     | 3V66_3      | (Active/Inactive) | 1                   |

Document #: 38-07453 Rev. \*B

### Data Byte 1 (continued)

| Bit   | Pin# | Name   | Description       | Power On<br>Default |

|-------|------|--------|-------------------|---------------------|

| Bit 2 | 28   | 3V66_2 | (Active/Inactive) | 1                   |

| Bit 1 | 30   | 3V66_1 | (Active/Inactive) | 1                   |

| Bit 0 | 31   | 3V66_0 | (Active/Inactive) | 1                   |

### Data Byte 2

| Bit   | Pin# | Name     | Pin Description   | Power On<br>Default |

|-------|------|----------|-------------------|---------------------|

| Bit 7 |      | Reserved | Reserved          | 0                   |

| Bit 6 | 17   | PCI6     | (Active/Inactive) | 1                   |

| Bit 5 | 16   | PCI5     | (Active/Inactive) | 1                   |

| Bit 4 | 15   | PCI4     | (Active/Inactive) | 1                   |

| Bit 3 | 14   | PCI3     | (Active/Inactive) | 1                   |

| Bit 2 | 12   | PCI2     | (Active/Inactive) | 1                   |

| Bit 1 | 11   | PCI1     | (Active/Inactive) | 1                   |

| Bit 0 | 10   | PCI0     | (Active/Inactive) | 1                   |

#### Data Byte 3

| Bit   | Pin#   | Name              | Pin Description   | Power On<br>Default |

|-------|--------|-------------------|-------------------|---------------------|

| Bit 7 | 8      | PCI_F2            | (Active/Inactive) | 1                   |

| Bit 6 | 7      | PCI_F1            | (Active/Inactive) | 1                   |

| Bit 5 | 6      | PCI_F0            | (Active/Inactive) | 1                   |

| Bit 4 |        | Reserved          | Reserved          | 0                   |

| Bit 3 | 44, 45 | CPU_ITP, CPU_ITP# | (Active/Inactive) | 1                   |

| Bit 2 |        | Reserved          | Reserved          | 0                   |

| Bit 1 | 1      | REF1              | (Active/Inactive) | 1                   |

| Bit 0 | 48     | REF0              | (Active/Inactive) | 1                   |

| Bit   | Pin# | Name             | Pin Description                                                          | Power On<br>Default |

|-------|------|------------------|--------------------------------------------------------------------------|---------------------|

| Bit 7 |      | MULTSEL_Override | This bit control the selection of IREF multiple.                         | 0                   |

|       |      |                  | 0 = HW control; IREF multiplier is determined by MULTSEL[0:1] input pins |                     |

|       |      |                  | 1 = SW control; IREF multiplier is determined by Byte[4], Bit[5:6].      |                     |

| Bit 6 |      | SW_MULTSEL1      | IREF multiplier                                                          | 0                   |

| Bit 5 |      | SW MULTSEL0      | 00 = loh is 4 x IREF                                                     | 0                   |

|       |      | _                | 01 = loh is 5 x IREF                                                     |                     |

|       |      |                  | 10 = loh is 6 x IREF                                                     |                     |

|       |      |                  | 11 = loh is 7 x IREF                                                     |                     |

| Bit 4 |      | Reserved         | Reserved                                                                 | Reserved            |

| Bit 3 |      | Reserved         | Reserved                                                                 | Reserved            |

| Bit 2 |      | Reserved         | Reserved                                                                 | Reserved            |

| Bit 1 |      | Reserved         | Reserved                                                                 | Reserved            |

| Bit 0 |      | Reserved         | Reserved                                                                 | Reserved            |

### Data Byte 5

| Bit   | Pin# | Name              | Pin Description                                                                                             | Power On<br>Default |

|-------|------|-------------------|-------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 | 10   | Latched FS4 input | Latched FS[4:0] inputs. These bits are read only.                                                           | Х                   |

| Bit 6 | 7    | Latched FS3 input |                                                                                                             | Х                   |

| Bit 5 | 6    | Latched FS2 input |                                                                                                             | Х                   |

| Bit 4 | 23   | Latched FS1 input |                                                                                                             | Х                   |

| Bit 3 | 22   | Latched FS0 input |                                                                                                             | Х                   |

| Bit 2 |      | FS_Override       | 0 = Select operating frequency by FS[4:0] input pins<br>1 = Select operating frequency by SEL[4:0] settings | 0                   |

| Bit 1 |      | Reserved          | Reserved                                                                                                    | 0                   |

| Bit 0 | 23   | SEL 48MHZ         | 0 = 24 MHz<br>1 = 48 MHz                                                                                    | 0                   |

# Data Byte 6

| Bit   | Pin# | Name         | Pin Description                                                     | Power On<br>Default |

|-------|------|--------------|---------------------------------------------------------------------|---------------------|

| Bit 7 |      | Revision_ID3 | Revision ID bit[3]                                                  | 0                   |

| Bit 6 |      | Revision_ID2 | Revision ID bit[2]                                                  | 0                   |

| Bit 5 |      | Revision_ID1 | Revision ID bit[1]                                                  | 0                   |

| Bit 4 |      | Revision_ID0 | Revision ID bit[0]                                                  | 0                   |

| Bit 3 |      | Vendor_ID3   | Bit[3] of Cypress Semiconductor's Vendor ID. This bit is read-only. | 1                   |

| Bit 2 |      | Vendor_ID2   | Bit[2] of Cypress Semiconductor's Vendor ID. This bit is read-only. | 0                   |

| Bit 1 |      | Vendor_ID1   | Bit[1] of Cypress Semiconductor's Vendor ID. This bit is read-only. | 0                   |

| Bit 0 |      | Vendor _ID0  | Bit[0] of Cypress Semiconductor's Vendor ID. This bit is read-only. | 0                   |

| Bit   | Pin# | Name     | Pin Description | Power On<br>Default |

|-------|------|----------|-----------------|---------------------|

| Bit 7 |      | Reserved | Reserved        | 0                   |

| Bit 6 |      | Reserved | Reserved        | 0                   |

| Bit 5 |      | Reserved | Reserved        | 0                   |

| Bit 4 |      | Reserved | Reserved        | 0                   |

| Bit 3 |      | Reserved | Reserved        | 0                   |

| Bit 2 |      | Reserved | Reserved        | 0                   |

| Bit 1 |      | Reserved | Reserved        | 0                   |

| Bit 0 |      | Reserved | Reserved        | 0                   |

### Data Byte 8

| Bit   | Pin# | Name          | Pin Description                                                                                                    | Power On<br>Default |

|-------|------|---------------|--------------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 |      | Reserved      | Reserved                                                                                                           | 0                   |

| Bit 6 |      | Reserved      | Reserved                                                                                                           | 0                   |

| Bit 5 |      | WD_TIMER4     | These bits store the time-out value of the Watchdog timer.                                                         | 1                   |

| Bit 4 |      | WD_TIMER3     | The scale of the timer is determine by the prescaler.                                                              | 1                   |

| Bit 3 |      | WD_TIMER2     | The timer can support a value of 150 ms to 4.8 sec when the prescaler is set to 150 ms. If the prescaler is set to | 1                   |

| Bit 2 |      | WD_TIMER1     | 2.5 sec, it can support a value from 2.5 sec to 80 sec.                                                            | 1                   |

| Bit 1 |      | WD_TIMER0     | When the Watchdog timer reaches "0," it will set the WD_TO_STATUS bit and generate Reset if RST_EN_WD is enabled.  | 1                   |

| Bit 0 |      | WD_PRE_SCALER | 0 = 150 ms                                                                                                         | 0                   |

|       |      |               | 1 = 2.5 sec                                                                                                        |                     |

| Bit   | Pin# | Name         | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power On<br>Default |

|-------|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 |      | 48MHz_DRV    | 48-MHz & 24_48-MHz clock output drive strength 0 = Normal 1 = High Drive (Recommend to set to high drive if this output is being used to drive both USB and SIO devices in Intel Brookdale - G platforms)                                                                                                                                                                                                                                                                                                               | 0                   |

| Bit 6 |      | PCI_DRV      | PCI clock output drive strength 0 = Normal 1 = High Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                   |

| Bit 5 |      | 3V66_DRV     | 3V66 clock output drive strength 0 = Normal 1 = High Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                   |

| Bit 4 |      | RST_EN_WD    | This bit will enable the generation of a Reset pulse when a Watchdog timer time-out occurs.  0 = Disabled  1 = Enabled                                                                                                                                                                                                                                                                                                                                                                                                  | 0                   |

| Bit 3 |      | RST_EN_FC    | This bit will enable the generation of a Reset pulse after a frequency change occurs.  0 = Disabled 1 = Enabled                                                                                                                                                                                                                                                                                                                                                                                                         | 0                   |

| Bit 2 |      | WD_TO_STATUS | Watchdog Timer Time-out Status bit 0 = No time-out occurs (Read); Ignore (Write) 1 = time-out occurred (Read); Clear WD_TO_STATUS (Write)                                                                                                                                                                                                                                                                                                                                                                               | 0                   |

| Bit 1 |      | WD_EN        | 0 = Stop and reload Watchdog timer 1 = Enable Watchdog timer. It will start counting down after a frequency change occurs.  Note: CY28323 will generate system reset, reload a recovery frequency, and lock itself into a recovery frequency mode after a Watchdog timer time-out occurs. Under recovery frequency mode, CY28323 will not respond to any attempt to change output frequency via the SMBus control bytes. System software can unlock CY28323 from its recovery frequency mode by clearing the WD_EN bit. | 0                   |

| Bit 0 |      | Reserved     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                   |

#### Data Byte 10

| Bit   | Pin# | Name       | Pin Description                | Power On Default |

|-------|------|------------|--------------------------------|------------------|

| Bit 7 |      | CPU_Skew2  | CPU skew control               | 0                |

| Bit 6 |      | CPU_Skew1  | 000 = Normal                   | 0                |

| Bit 5 |      | CPU_Skew0  | 001 = -150 ps<br>010 = -300 ps | 0                |

|       |      |            | 011 = -450 ps                  |                  |

|       |      |            | 100 = +150 ps                  |                  |

|       |      |            | 101 = +300 ps                  |                  |

|       |      |            | 110 = +450 ps                  |                  |

|       |      |            | 111 = +600 ps                  |                  |

| Bit 4 |      | Reserved   | Reserved                       | 0                |

| Bit 3 |      | PCI_Skew1  | PCI skew control               | 0                |

| Bit 2 |      | PCI_Skew0  | 00 = Normal                    | 0                |

|       |      | _          | 01 = -500  ps                  |                  |

|       |      |            | 10 = Reserved                  |                  |

|       |      |            | 11 = +500 ps                   |                  |

| Bit 1 |      | 3V66_Skew1 | 3V66 skew control              | 0                |

| Bit 0 |      | 3V66_Skew0 | 00 = Normal                    | 0                |

|       |      | _          | 01 = -150  ps                  |                  |

|       |      |            | 10 = +150 ps                   |                  |

|       |      |            | 11 = +300 ps                   |                  |

### Data Byte 11

| Bit   | Pin# | Name         | Pin Description                                                                                            | Power On<br>Default |

|-------|------|--------------|------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 |      | ROCV_FREQ_N7 | If ROCV_FREQ_SEL is set, the values programmed in                                                          | 0                   |

| Bit 6 |      | ROCV_FREQ_N6 | ROCV_FREQ_N[7:0] and ROCV_FREQ_M[6:0] will be use to determine the recovery CPU output frequency           | 0                   |

| Bit 5 |      | ROCV_FREQ_N5 | when a Watchdog timer time-out occurs.                                                                     | 0                   |

| Bit 4 |      | ROCV_FREQ_N4 | The setting of FS_Override bit determines the frequency                                                    | 0                   |

| Bit 3 |      | ROCV_FREQ_N3 | ratio for CPU and other output clocks. When the FS Override bit is cleared, the same frequency ratio stat- | 0                   |

| Bit 2 |      | ROCV_FREQ_N2 | ed in the Latched FS[4:0] register will be used. When it is                                                | 0                   |

| Bit 1 |      | ROCV_FREQ_N1 | set, the frequency ratio stated in the SEL[4:0] register will                                              | 0                   |

| Bit 0 |      | ROCV_FREQ_N0 | be used.                                                                                                   | 0                   |

| Bit   | Pin# | Name          | Pin Description                                                                                                                                                                                                          | Power On<br>Default |

|-------|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 |      | ROCV_FREQ_SEL | ROCV_FREQ_SEL determines the source of the recover frequency when a Watchdog timer time-out occurs. The clock generator will automatically switch to the recovery CPU frequency based on the selection on ROCV_FREQ_SEL. | 0                   |

|       |      |               | 0 = From latched FS[4:0]                                                                                                                                                                                                 |                     |

|       |      |               | 1 = From the settings of ROCV_FREQ_N[7:0] & ROCV_FREQ_M[6:0]                                                                                                                                                             |                     |

#### Data Byte 12 (continued)

| Bit   | Pin# | Name         | Pin Description                                                                                            | Power On<br>Default |

|-------|------|--------------|------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 6 |      | ROCV_FREQ_M6 | If ROCV_FREQ_SEL is set, the values programmed in                                                          | 0                   |

| Bit 5 |      | ROCV_FREQ_M5 | ROCV_FREQ_N[7:0] and ROCV_FREQ_M[6:0] will be use to determine the recovery CPU output frequen-            | 0                   |

| Bit 4 |      | ROCV_FREQ_M4 | cy.when a Watchdog timer time-out occurs.                                                                  | 0                   |

| Bit 3 |      | ROCV_FREQ_M3 | The setting of FS_Override bit determines the frequency                                                    | 0                   |

| Bit 2 |      | ROCV_FREQ_M2 | ratio for CPU and other output clocks. When the FS Override bit is cleared, the same frequency ratio stat- | 0                   |

| Bit 1 |      | ROCV_FREQ_M1 | ed in the Latched FS[4:0] register will be used. When it is                                                | 0                   |

| Bit 0 |      | ROCV_FREQ_M0 | set, the frequency ratio stated in the SEL[4:0] register will be used.                                     | 0                   |

### Data Byte 13

| Bit   | Pin# | Name        | Pin Description                                                                                              | Power On<br>Default |

|-------|------|-------------|--------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 |      | CPU_FSEL_N7 | If Prog_Freq_EN is set, the values programmed in                                                             | 0                   |

| Bit 6 |      | CPU_FSEL_N6 | CPU_FSEL_N[7:0] and CPU_FSEL_M[6:0] will be used to determine the CPU output frequency. The new frequency    | 0                   |

| Bit 5 |      | CPU_FSEL_N5 | will start to load whenever CPU_FSELM[6:0] is updated.                                                       | 0                   |

| Bit 4 |      | CPU_FSEL_N4 | The setting of the FS_Override bit determines the frequen-                                                   | 0                   |

| Bit 3 |      | CPU_FSEL_N3 | cy ratio for CPU and other output clocks. When it is cleared, the same frequency ratio stated in the Latched | 0                   |

| Bit 2 |      | CPU_FSEL_N2 | FS[4:0] register will be used. When it is set, the frequency                                                 | 0                   |

| Bit 1 |      | CPU_FSEL_N1 | ratio stated in the SEL[4:0] register will be used.                                                          | 0                   |

| Bit 0 |      | CPU_FSEL_N0 |                                                                                                              | 0                   |

### Data Byte 14

| Bit   | Pin# | Name          | Pin Description                                                                                              | Power On<br>Default |

|-------|------|---------------|--------------------------------------------------------------------------------------------------------------|---------------------|

| Bit 7 |      | Pro_Freq_EN   | Programmable output frequencies enabled 0 = disabled 1 = enabled                                             | 0                   |

| Dit 0 |      | 0011 5051 140 |                                                                                                              |                     |

| Bit 6 |      | CPU_FSEL_M6   | If Prog_Freq_EN is set, the values programmed in                                                             | 0                   |

| Bit 5 |      | CPU_FSEL_M5   | CPU_FSEL_N[7:0] and CPU_FSEL_M[6:0] will be used to determine the CPU output frequency. The new frequency    | 0                   |

| Bit 4 |      | CPU_FSEL_M4   | will start to load whenever CPU_FSELM[6:0] is updated.                                                       | 0                   |

| Bit 3 |      | CPU_FSEL_M3   | The setting of the FS_Override bit determines the frequen-                                                   | 0                   |

| Bit 2 |      | CPU_FSEL_M2   | cy ratio for CPU and other output clocks. When it is cleared, the same frequency ratio stated in the Latched | 0                   |

| Bit 1 |      | CPU_FSEL_M1   | FS[4:0] register will be used. When it is set, the frequency                                                 | 0                   |

| Bit 0 |      | CPU_FSEL_M0   | ratio stated in the SEL[4:0] register will be used.                                                          | 0                   |

| Bit   | Pin# | Name     | Pin Description | Power On<br>Default |

|-------|------|----------|-----------------|---------------------|

| Bit 7 |      | Reserved | Reserved        | 0                   |

| Bit 6 |      | Reserved | Reserved        | 0                   |

| Bit 5 |      | Reserved | Reserved        | 0                   |

| Bit 4 |      | Reserved | Reserved        | 0                   |

| Bit 3 |      | Reserved | Reserved        | 0                   |

| Bit 2 |      | Reserved | Reserved        | 0                   |

#### Data Byte 15 (continued)

| Bit   | Pin# | Name             | Pin Description          | Power On<br>Default |

|-------|------|------------------|--------------------------|---------------------|

| Bit 1 |      | Vendor Test Mode | Reserved. Write with "1" | 1                   |

| Bit 0 |      | Vendor Test Mode | Reserved. Write with "1" | 1                   |

#### Data Byte 16

| Bit   | Pin# | Name     | Pin Description | Power On<br>Default |

|-------|------|----------|-----------------|---------------------|

| Bit 7 |      | Reserved | Reserved        | 0                   |

| Bit 6 |      | Reserved | Reserved        | 0                   |

| Bit 5 |      | Reserved | Reserved        | 0                   |

| Bit 4 |      | Reserved | Reserved        | 0                   |

| Bit 3 |      | Reserved | Reserved        | 0                   |

| Bit 2 |      | Reserved | Reserved        | 0                   |

| Bit 1 |      | Reserved | Reserved        | 0                   |

| Bit 0 |      | Reserved | Reserved        | 0                   |

| Bit   | Pin# | Name     | Pin Description | Power On<br>Default |

|-------|------|----------|-----------------|---------------------|

| Bit 7 |      | Reserved | Reserved        | 0                   |

| Bit 6 |      | Reserved | Reserved        | 0                   |

| Bit 5 |      | Reserved | Reserved        | 0                   |

| Bit 4 |      | Reserved | Reserved        | 0                   |

| Bit 3 |      | Reserved | Reserved        | 0                   |

| Bit 2 |      | Reserved | Reserved        | 0                   |

| Bit 1 |      | Reserved | Reserved        | 0                   |

| Bit 0 |      | Reserved | Reserved        | 0                   |

**Table 4. Frequency Selection Table**

| FS4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input Conditions |      |      |      | Output Frequency |       |      |      |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|------------------|-------|------|------|----------|

| SEL4         SEL3         SEL2         SEL1         SEL0         CPU         3V66         PCI         (G)           0         0         0         0         102.0         68.0         34.0         48.00741           0         0         0         0         1         105.0         70.0         35.0         48.00741           0         0         0         1         1         111.0         74.0         37.0         48.00741           0         0         1         1         111.0         74.0         37.0         48.00741           0         0         1         0         0         114.0         76.0         38.0         48.00741           0         0         1         0         1         117.0         78.0         39.0         48.00741           0         0         1         1         1         122.0         82.0         41.0         48.00741           0         1         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         1         130.0         65.0         32.5         48.00741           0 </th <th>FS4</th> <th>FS3</th> <th>FS2</th> <th>FS1</th> <th>FS0</th> <th></th> <th></th> <th></th> <th></th>            | FS4              | FS3  | FS2  | FS1  | FS0              |       |      |      |          |

| 0         0         0         1         105.0         70.0         35.0         48.00741           0         0         0         1         0         108.0         72.0         36.0         48.00741           0         0         0         1         1         111.0         74.0         37.0         48.00741           0         0         1         0         0         114.0         76.0         38.0         48.00741           0         0         1         0         1         117.0         78.0         39.0         48.00741           0         0         1         1         0         120.0         80.0         40.0         48.00741           0         0         1         1         0         123.0         82.0         41.0         48.00741           0         1         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         130.0         65.0         32.5         48.00741           0         1         0         1         130.0         65.0         32.5         48.00741           0         1                                                                                                                                 | SEL4             | SEL3 | SEL2 | SEL1 | SEL0             | CPU   | 3V66 | PCI  |          |

| 0         0         0         1         0         108.0         72.0         36.0         48.00741           0         0         0         1         1         111.0         74.0         37.0         48.00741           0         0         1         0         0         114.0         76.0         38.0         48.00741           0         0         1         0         1         117.0         78.0         39.0         48.00741           0         0         1         1         0         120.0         80.0         40.0         48.00741           0         0         1         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         136.0         68.0         34.0         48.00741           0         1         0         1         140.0         70.0         35.0         48.00741           0         1                                                                                                                                 | 0                | 0    | 0    | 0    | 0                | 102.0 | 68.0 | 34.0 | 48.00741 |

| 0         0         0         1         1         111.0         74.0         37.0         48.00741           0         0         1         0         0         114.0         76.0         38.0         48.00741           0         0         1         0         1         117.0         78.0         39.0         48.00741           0         0         1         1         0         120.0         80.0         40.0         48.00741           0         0         1         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         1         130.0         65.0         32.5         48.00741           0         1         0         0         1         130.0         68.0         34.0         48.00741           0         1         0         1         140.0         70.0         35.0         48.00741           0         1         1         0         144.0         72.0         36.0         48.00741                                                                                                                                   | 0                | 0    | 0    | 0    | 1                | 105.0 | 70.0 | 35.0 | 48.00741 |

| 0         0         1         0         0         114.0         76.0         38.0         48.00741           0         0         1         0         1         117.0         78.0         39.0         48.00741           0         0         1         1         0         120.0         80.0         40.0         48.00741           0         0         1         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         1         130.0         65.0         32.5         48.00741           0         1         0         1         136.0         68.0         34.0         48.00741           0         1         0         1         1         140.0         70.0         35.0         48.00741           0         1         1         0         1         140.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741                                                                                                                                   | 0                | 0    | 0    | 1    | 0                | 108.0 | 72.0 | 36.0 | 48.00741 |

| 0         0         1         0         1         117.0         78.0         39.0         48.00741           0         0         1         1         0         120.0         80.0         40.0         48.00741           0         0         1         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         1         130.0         65.0         32.5         48.00741           0         1         0         1         130.0         68.0         34.0         48.00741           0         1         0         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         1         0         152.0         76.0         38.0         48.00741                                                                                                                                   | 0                | 0    | 0    | 1    | 1                | 111.0 | 74.0 | 37.0 | 48.00741 |

| 0         0         1         1         0         120.0         80.0         40.0         48.00741           0         0         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         136.0         68.0         34.0         48.00741           0         1         0         136.0         68.0         34.0         48.00741           0         1         0         140.0         70.0         35.0         48.00741           0         1         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741           0         1         1         1         1         1         148.0         74.0         37.0         48.00741           1         0         0         0         160.0         80.0 </td <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>114.0</td> <td>76.0</td> <td>38.0</td> <td>48.00741</td> | 0                | 0    | 1    | 0    | 0                | 114.0 | 76.0 | 38.0 | 48.00741 |

| 0         0         1         1         1         123.0         82.0         41.0         48.00741           0         1         0         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         1         130.0         65.0         32.5         48.00741           0         1         0         1         136.0         68.0         34.0         48.00741           0         1         0         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741           0         1         1         1         0         152.0         76.0         38.0         48.00741           1         0         0         0         160.0         80.0         40.0         48.00741           1                                                                                                                                 | 0                | 0    | 1    | 0    | 1                | 117.0 | 78.0 | 39.0 | 48.00741 |

| 0         1         0         0         0         126.0         63.0         31.5         48.00741           0         1         0         0         1         130.0         65.0         32.5         48.00741           0         1         0         1         0         136.0         68.0         34.0         48.00741           0         1         0         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741           0         1         1         1         0         152.0         76.0         38.0         48.00741           1         0         1         1         156.0         78.0         39.0         48.00741           1         0         0         0         160.0         80.0         40.0         48.00741           1                                                                                                                                 | 0                | 0    | 1    | 1    | 0                | 120.0 | 80.0 | 40.0 | 48.00741 |

| 0         1         0         0         1         130.0         65.0         32.5         48.00741           0         1         0         136.0         68.0         34.0         48.00741           0         1         0         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741           0         1         1         1         0         152.0         76.0         38.0         48.00741           0         1         1         1         1         156.0         78.0         39.0         48.00741           1         0         0         0         160.0         80.0         40.0         48.00741           1         0         0         0         160.0         82.0         41.0         48.00741           1         0         0         1         164.0         82.0         41.0         48.00741           1         0         0         1                                                                                                                                 | 0                | 0    | 1    | 1    | 1                | 123.0 | 82.0 | 41.0 | 48.00741 |

| 0         1         0         1         0         136.0         68.0         34.0         48.00741           0         1         0         1         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741           0         1         1         1         0         152.0         76.0         38.0         48.00741           0         1         1         1         1         156.0         78.0         39.0         48.00741           1         0         0         0         160.0         80.0         40.0         48.00741           1         0         0         0         166.6         66.6         33.3         48.00741           1         0         0         1         164.0         82.0         41.0         48.00741           1         0         0         1         170.0         68.0         34.0         48.00741           1         0                                                                                                                                 | 0                | 1    | 0    | 0    | 0                | 126.0 | 63.0 | 31.5 | 48.00741 |

| 0         1         0         1         1         140.0         70.0         35.0         48.00741           0         1         1         0         0         144.0         72.0         36.0         48.00741           0         1         1         0         1         148.0         74.0         37.0         48.00741           0         1         1         1         0         152.0         76.0         38.0         48.00741           0         1         1         1         156.0         78.0         39.0         48.00741           1         0         0         0         160.0         80.0         40.0         48.00741           1         0         0         0         166.0         82.0         41.0         48.00741           1         0         0         1         164.0         82.0         41.0         48.00741           1         0         0         1         170.0         68.0         34.0         48.00741           1         0         1         1         170.0         68.0         34.0         48.00741           1         0         1         1                                                                                                                                 | 0                | 1    | 0    | 0    | 1                | 130.0 | 65.0 | 32.5 | 48.00741 |