## Successive Approximation Registers

The MC14549B and MC14559B successive approximation registers are 8-bit registers providing all the digital control and storage necessary for successive approximation analog-to-digital conversion systems. These parts differ in only one control input. The Master Reset (MR) on the MC14549B is required in the cascaded mode when more than 8 bits are desired. The Feed Forward (FF) of the MC14559B is used for register shortening where End-of-Conversion (EOC) is required after less than eight cycles.

Applications for the MC14549B and MC14559B include analog-to-digital conversion, with serial and parallel outputs.

#### Features

- Totally Synchronous Operation

- All Outputs Buffered

- Single Supply Operation

- Serial Output

- Retriggerable

- Compatible with a Variety of Digital and Analog Systems such as the MC1408 8–Bit D/A Converter

- All Control Inputs Positive-Edge Triggered

- Supply Voltage Range = 3.0 Vdc to 18 Vdc

- Capable of Driving 2 Low–Power TTL Loads, 1 Low–Power Schottky TTL Load or 2 HTL Loads Over the Rated Temperature Range

- Chip Complexity: 488 FETs or 122 Equivalent Gates

- This Device is Pb–Free and is RoHS Compliant

#### MAXIMUM RATINGS (Voltages Referenced to V<sub>SS</sub>)

| Parameter                              | Symbol           | Value                         | Unit |

|----------------------------------------|------------------|-------------------------------|------|

| DC Supply Voltage Range                | V <sub>DD</sub>  | -0.5 to +18.0                 | V    |

| Input Voltage Range, All Inputs        | V <sub>in</sub>  | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Input Current per Pin               | l <sub>in</sub>  | ±10                           | mA   |

| Power Dissipation per Package (Note 1) | PD               | 500                           | mW   |

| Operating Temperature Range            | T <sub>A</sub>   | -55 to +125                   | °C   |

| Storage Temperature Range              | T <sub>stg</sub> | -65 to +150                   | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Temperature Derating: "D/DW" Package: –7.0 mW/°C From 65°C To 125°C This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation, V<sub>in</sub> and V<sub>out</sub> should be constrained to the range V<sub>SS</sub>  $\leq$  (V<sub>in</sub> or V<sub>out</sub>)  $\leq$  V<sub>DD</sub>.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ).

#### **ON Semiconductor®**

http://onsemi.com

SOIC-16 WB DW SUFFIX CASE 751G

#### **PIN ASSIGNMENT**

| Q4       | ۵ | 1● |    |      |

|----------|---|----|----|------|

| Q5       | q | 2  | 15 | ] Q3 |

| Q6       | q | 3  | 14 | ] Q2 |

| Q7       | q | 4  | 13 | ] Q1 |

| Sout     | q | 5  | 12 | ] Q0 |

| D        | q | 6  | 11 | вос  |

| С        | d | 7  | 10 | ] ∗  |

| $V_{SS}$ | q | 8  | 9  | ] sc |

\*For MC14549B Pin 10 is MR input. For MC14559B Pin 10 is FF input.

#### MARKING DIAGRAM

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.

#### **TRUTH TABLES**

| SC | SC( <sub>t-1</sub> ) | MR | MR( <sub>t-1</sub> ) | Clock | Action                            |

|----|----------------------|----|----------------------|-------|-----------------------------------|

| Х  | Х                    | Х  | Х                    | ~     | None                              |

| Х  | Х                    | 1  | Х                    | 7     | Reset                             |

| 1  | 0                    | 0  | 0                    | 7     | Start<br>Conversion               |

| 1  | Х                    | 0  | 1                    | 7     | Start<br>Conversion               |

| 1  | 1                    | 0  | 0                    | Υ     | Continue<br>Conversion            |

| 0  | х                    | 0  | Х                    | 7     | Continue<br>Previous<br>Operation |

X = Don't Care t-1 = State at Previous Clock  $\checkmark$

#### ELECTRICAL CHARACTERISTICS (Voltages Referenced to Ves)

|                                                                                                                                                                                                                 |                             |                 |                        | - 5                            | 5°C                  |                              | 25°C                                            |                      | 125                            | °℃                   |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|------------------------|--------------------------------|----------------------|------------------------------|-------------------------------------------------|----------------------|--------------------------------|----------------------|----------|

| Characteris                                                                                                                                                                                                     | tic                         | Symbol          | V <sub>DD</sub><br>Vdc | Min                            | Max                  | Min                          | Typ<br>(Note 2)                                 | Max                  | Min                            | Max                  | Unit     |

| Output Voltage<br>V <sub>in</sub> = V <sub>DD</sub> or 0                                                                                                                                                        | "0" Level                   | V <sub>OL</sub> | 5.0<br>10<br>15        | _<br>_<br>_                    | 0.05<br>0.05<br>0.05 | _<br>_<br>_                  | 0<br>0<br>0                                     | 0.05<br>0.05<br>0.05 | -<br>-<br>-                    | 0.05<br>0.05<br>0.05 | Vdc      |

| $V_{in} = 0 \text{ or } V_{DD}$                                                                                                                                                                                 | "1" Level                   | V <sub>OH</sub> | 5.0<br>10<br>15        | 4.95<br>9.95<br>14.95          | _<br>_<br>_          | 4.95<br>9.95<br>14.95        | 5.0<br>10<br>15                                 | _<br>_<br>_          | 4.95<br>9.95<br>14.95          |                      | Vdc      |

| Input Voltage (Note 2)<br>( $V_O = 4.5 \text{ or } 0.5 \text{ Vdc}$ )<br>( $V_O = 9.0 \text{ or } 1.0 \text{ Vdc}$ )<br>( $V_O = 13.5 \text{ or } 1.5 \text{ Vdc}$ )                                            | "0" Level                   | V <sub>IL</sub> | 5.0<br>10<br>15        | _<br>_<br>_                    | 1.5<br>3.0<br>4.0    | _<br>_<br>_                  | 2.25<br>4.50<br>6.75                            | 1.5<br>3.0<br>4.0    | -<br>-<br>-                    | 1.5<br>3.0<br>4.0    | Vdc      |

| $(V_{O} = 0.5 \text{ or } 4.5 \text{ Vdc})$<br>$(V_{O} = 1.0 \text{ or } 9.0 \text{ Vdc})$<br>$(V_{O} = 1.5 \text{ or } 13.5 \text{ Vdc})$                                                                      | "1" Level                   | V <sub>IH</sub> | 5.0<br>10<br>15        | 3.5<br>7.0<br>11               | -<br>-<br>-          | 3.5<br>7.0<br>11             | 2.75<br>5.50<br>8.25                            |                      | 3.5<br>7.0<br>11               |                      | Vdc      |

| $\begin{array}{l} \text{Output Drive Current} \\ (\text{V}_{OH} = 2.5 \text{ Vdc}) \\ (\text{V}_{OH} = 4.6 \text{ Vdc}) \\ (\text{V}_{OH} = 9.5 \text{ Vdc}) \\ (\text{V}_{OH} = 13.5 \text{ Vdc}) \end{array}$ | Source                      | I <sub>OH</sub> | 5.0<br>5.0<br>10<br>15 | -1.2<br>-0.25<br>-0.62<br>-1.8 | -<br>-<br>-          | -1.0<br>-0.2<br>-0.5<br>-1.5 | -1.7<br>-0.36<br>-0.9<br>-3.5                   |                      | -0.7<br>-0.14<br>-0.35<br>-1.1 |                      | mAd<br>c |

| $(V_{OL} = 0.4 \text{ Vdc})$<br>$(V_{OL} = 0.5 \text{ Vdc})$<br>$(V_{OL} = 1.5 \text{ Vdc})$                                                                                                                    | Sink<br>Q Outputs           | I <sub>OL</sub> | 5.0<br>10<br>15        | 1.28<br>3.2<br>8.4             | _<br>_<br>_          | 1.02<br>2.6<br>6.8           | 1.76<br>4.5<br>17.6                             | _<br>_<br>_          | 0.72<br>1.8<br>4.8             |                      | mAd<br>c |

| (V <sub>OL</sub> = 0.4 Vdc)<br>(V <sub>OL</sub> = 0.5 Vdc)<br>(V <sub>OL</sub> = 1.5 Vdc)                                                                                                                       | Sink<br>Pin 5, 11 only      |                 | 5.0<br>10<br>15        | 0.64<br>1.6<br>4.2             | _<br>_<br>_          | 0.51<br>1.3<br>3.4           | 0.88<br>2.25<br>8.8                             | _<br>_<br>_          | 0.36<br>0.9<br>2.4             |                      | mAd<br>c |

| Input Current                                                                                                                                                                                                   |                             | l <sub>in</sub> | 15                     | -                              | ±0.1                 | -                            | ±0.00001                                        | ±0.1                 | -                              | ±1.0                 | μAdc     |

| Input Capacitance                                                                                                                                                                                               |                             | C <sub>in</sub> | -                      | -                              | -                    | -                            | 5.0                                             | 7.5                  | -                              | -                    | pF       |

| Quiescent Current<br>(Per Package)<br>(Clock = 0 V,<br>Other Inputs = V <sub>DD</sub> or 0                                                                                                                      | V, I <sub>out</sub> = 0 μA) | I <sub>DD</sub> | 5.0<br>10<br>15        | _<br>_<br>_                    | 5.0<br>10<br>20      | _<br>_<br>_                  | 0.005<br>0.010<br>0.015                         | 5.0<br>10<br>20      |                                | 150<br>300<br>600    | μAdc     |

| Total Supply Current (No<br>(Dynamic plus Quiesce<br>Per Package) (C <sub>L</sub> = 50<br>outputs, all buffers swit                                                                                             | ent,<br>pF on all           | ŀτ              | 5.0<br>10<br>15        |                                | 1                    | $I_{T} = ('$                 | 1.8 μA/kHz) f<br>1.6 μA/kHz) f<br>2.4 μA/kHz) f | + I <sub>DD</sub>    |                                |                      | μAdc     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Noise immunity specified for worst-case input combination.

Noise Margin for both "1" and "0" level = 1.0 V min @ V<sub>DD</sub> = 5.0 V= 2.0 V min @ V<sub>DD</sub> = 10 V= 2.5 V min @ V<sub>DD</sub> = 15 V

To calculate total supply current at loads other than 50 pF: I<sub>T</sub>(C<sub>L</sub>) = I<sub>T</sub>(50 pF) + 3.5 x 10<sup>-3</sup> (C<sub>L</sub> = 50) V<sub>DD</sub>f where: I<sub>T</sub> is in μA (per package), C<sub>L</sub> in pF, V<sub>DD</sub> in V, and f in kHz is input frequency.

The formulas given are for the typical characteristics only at 25°C.

| MC14559B |                      |     |          |                                |  |  |  |

|----------|----------------------|-----|----------|--------------------------------|--|--|--|

| SC       | SC( <sub>t-1</sub> ) | EOC | Clock    | Action                         |  |  |  |

| Х        | Х                    | Х   | $\sim$   | None                           |  |  |  |

| 1        | 0                    | 0   | 7        | Start<br>Conversion            |  |  |  |

| Х        | 1                    | 0   | 7        | Continue<br>Conversion         |  |  |  |

| 0        | 0                    | 0   | 7        | Continue<br>Conversion         |  |  |  |

| 0        | х                    | 1   | <u>`</u> | Retain<br>Conversion<br>Result |  |  |  |

| 1        | Х                    | 1   | ~        | Start<br>Conversion            |  |  |  |

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Symbol                                 | V <sub>DD</sub>                                       | Min                             | Тур                                                         | Max                                                           | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------|---------------------------------|-------------------------------------------------------------|---------------------------------------------------------------|------|

| Output Rise Time<br>$t_{TLH} = (3.0 \text{ ns/pF}) C_L + 30 \text{ ns}$<br>$t_{TLH} = (1.5 \text{ ns/pF}) C_L + 15 \text{ ns}$<br>$t_{TLH} = (1.1 \text{ ns/pF}) C_L + 10 \text{ ns}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | t <sub>TLH</sub>                       | 5.0<br>10<br>15                                       | -<br>-<br>-                     | 180<br>90<br>65                                             | 360<br>180<br>130                                             | ns   |

| Output Fall Time<br>$t_{THL} = (1.5 \text{ ns/pF}) C_L + 25 \text{ ns}$<br>$t_{THL} = (0.75 \text{ ns/pF}) C_L + 12.5 \text{ ns}$<br>$t_{THL} = (0.55 \text{ ns/pF}) C_L + 9.5 \text{ ns}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>THL</sub>                       | 5.0<br>10<br>15                                       | -<br>-<br>-                     | 100<br>50<br>40                                             | 200<br>100<br>80                                              | ns   |

| Propagation Delay Time<br>Clock to Q<br>$t_{PLH}$ , $t_{PHL} = (1.7 \text{ ns/pF}) C_L + 415 \text{ ns}$<br>$t_{PLH}$ , $t_{PHL} = (0.66 \text{ ns/pF}) C_L + 177 \text{ ns}$<br>$t_{PLH}$ , $t_{PHL} = (0.5 \text{ ns/pF}) C_L + 130 \text{ ns}$<br>Clock to S <sub>out</sub><br>$t_{PLH}$ , $t_{PHL} = (1.7 \text{ ns/pF}) C_L + 665 \text{ ns}$<br>$t_{PLH}$ , $t_{PHL} = (0.66 \text{ ns/pF}) C_L + 277 \text{ ns}$<br>$t_{PLH}$ , $t_{PHL} = (0.5 \text{ ns/pF}) C_L + 195 \text{ ns}$<br>Clock to EOC<br>$t_{PLH}$ , $t_{PHL} = (1.7 \text{ ns/pF}) C_L + 215 \text{ ns}$<br>$t_{PLH}$ , $t_{PHL} = (0.66 \text{ ns/pF}) C_L + 97 \text{ ns}$<br>$t_{PLH}$ , $t_{PHL} = (0.66 \text{ ns/pF}) C_L + 75 \text{ ns}$ | t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | 5.0<br>10<br>15<br>5.0<br>10<br>15<br>5.0<br>10<br>15 | -<br>-<br>-<br>-<br>-<br>-<br>- | 500<br>210<br>155<br>750<br>310<br>220<br>300<br>130<br>100 | 1000<br>420<br>310<br>1500<br>620<br>440<br>600<br>260<br>200 | ns   |

| SC, D, FF or MR Setup Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>su</sub>                        | 5.0<br>10<br>15                                       | 250<br>100<br>80                | 125<br>50<br>40                                             | -<br>-<br>-                                                   | ns   |

| Clock Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>WH(cl)</sub>                    | 5.0<br>10<br>15                                       | 700<br>270<br>200               | 350<br>135<br>100                                           | -<br>-<br>-                                                   | ns   |

| Pulse Width — D, SC, FF or MR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>WH</sub>                        | 5.0<br>10<br>15                                       | 500<br>200<br>160               | 250<br>100<br>80                                            | -<br>-<br>-                                                   | ns   |

| Clock Rise and Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>TLH</sub> ,<br>t <sub>THL</sub> | 5.0<br>10<br>15                                       | -<br>-<br>-                     | _                                                           | 15<br>1.0<br>0.5                                              | μs   |

| Clock Pulse Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>cl</sub>                        | 5.0<br>10<br>15                                       | -<br>-<br>-                     | 1.5<br>3.0<br>4.0                                           | 0.8<br>1.5<br>2.0                                             | MHz  |

#### **SWITCHING CHARACTERISTICS** (Note 5) ( $C_L = 50 \text{ pF}, T_A = 25^{\circ}C$ )

5. The formulas given are for the typical characteristics only.

#### **ORDERING INFORMATION**

| Device        | Package                 | Shipping <sup>†</sup> |

|---------------|-------------------------|-----------------------|

| MC14549BDWR2G | SOIC-16 WB<br>(Pb-Free) | 1000 / Tape & Reel    |

| MC14559BDWR2G | SOIC-16 WB<br>(Pb-Free) | 1000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

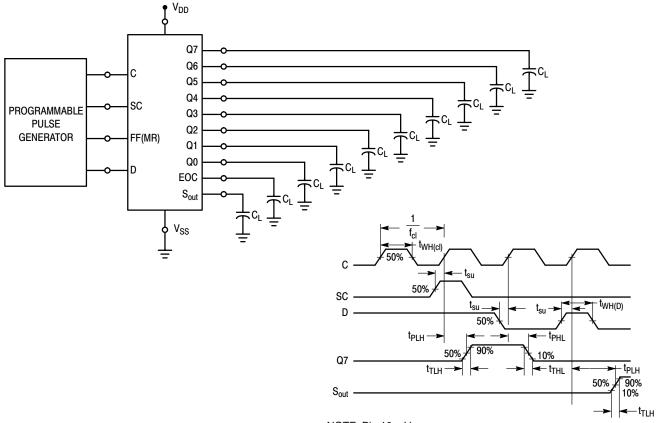

#### SWITCHING TIME TEST CIRCUIT AND WAVEFORMS

NOTE: Pin 10 = V<sub>SS</sub>

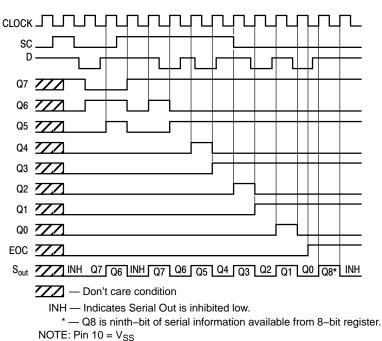

#### TIMING DIAGRAM

#### **OPERATING CHARACTERISTICS**

Both the MC14549B and MC14559B can be operated in either the "free run" or "strobed operation" mode for conversion schemes with any number of bits. Reliable cascading and/or recirculating operation can be achieved if the End of Convert (EOC) output is used as the controlling function, since with EOC = 0 (and with SC = 1 for MC14549B but either 1 or 0 for MC14559B) no stable state exists under continual clocked operation. The MC14559B will automatically recirculate after EOC = 1 during externally strobed operation, provided SC = 1.

All data and control inputs for these devices are triggered into the circuit on the positive edge of the clock pulse.

Operation of the various terminals is as follows:

C = Clock — A positive–going transition of the Clock is required for data on any input to be strobed into the circuit.

**SC** = **Start Convert** — A conversion sequence is initiated on the positive–going transition of the SC input on succeeding clock cycles.

$\mathbf{D} = \mathbf{Data}$  in — Data on this input (usually from a comparator in A/D applications) is also entered into the circuit on a positive–going transition of the clock. This input is Schmitt triggered and synchronized to allow fast response and guaranteed quality of serial and parallel data.

**MR** = Master Reset (MC14549B Only) — Resets all output to 0 on positive–going transitions of the clock. If removed while SC = 0, the circuit will remain reset until SC = 1. This allows easy cascading of circuits.

**FF** = **Feed Forward** (MC14559B Only) — Provides register shortening by removing unwanted bits from a system.

For operation with less than 8 bits, tie the output *following* the least significant bit of the circuit to EOC. E.g., for a 6–bit

conversion, tie Q1 to FF; the part will respond as shown in the timing diagram less two bit times. Not that Q1 and Q0 will still operate and must be disregarded.

For 8-bit operation, FF is tied to V<sub>SS</sub>.

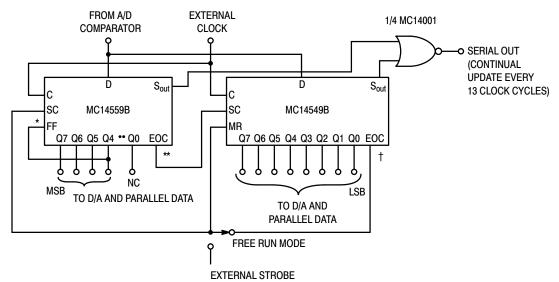

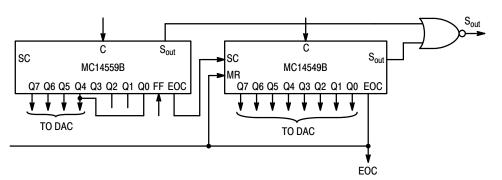

For applications with more than 8 but less than 16 bits, use the basic connections shown in Figure 1. The FF input of the MC14559B is used to shorten the setup. Tying FF directly to the least significant bit used in the MC14559B allows EOC to provide the cascading signal, and results in smooth transition of serial information from the MC14559B to the MC14559B remains inactive one cycle after EOC goes high, while S<sub>out</sub> of the MC14549B remains inhibited until the second clock cycle of its operation.

$Q_n = Data Outputs$  — After a conversion is initiated the Q's on succeeding cycles go high and are then conditionally reset dependent upon the state of the D input. Once conditionally reset they remain in the proper state until the circuit is either reset or reinitiated.

**EOC = End of Convert** — This output goes high on the negative–going transition of the clock following FF = 1 (for the MC14559B) or the conditional reset of Q0. This allows settling of the digital circuitry prior to the End of Conversion indication. Therefore either level or edge triggering can indicate complete conversion.

$S_{out}$  = Serial Out — Transmits conversion in serial fashion. Serial data occurs during the clock period when the corresponding parallel data bit is conditionally reset. Serial Out is inhibited on the initial period of a cycle, when the circuit is reset, and on the second cycle after EOC goes high. This provides efficient operation when cascaded.

\* FF allows EOC to activate as if in 4-stage register.

\*\* Cascading using EOC guaranteed; no stable unfunctional state.

+Completion of conversion automatically re-initiates cycle in free run mode.

#### Figure 1. 12–Bit Conversion Scheme

#### **TYPICAL APPLICATIONS**

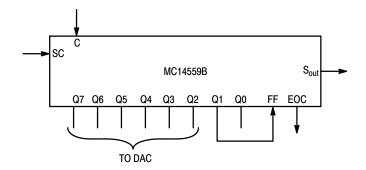

#### Externally Controlled 6-Bit ADC (Figure 2)

Several features are shown in this application:

- Shortening of the register to six bits by feeding the seventh output bit into the FF input.

- Continuous conversion, if a continuous signal is applied to SC.

- Externally controlled updating (the start pulse must be shorter than the conversion cycle).

- The EOC output indicating that the parallel data are valid and that the serial output is complete.

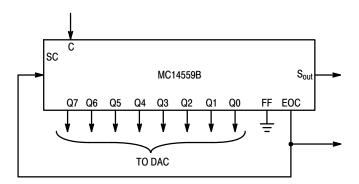

#### Continuously Cycling 8–Bit ADC (Figure 3)

This ADC is running continuously because the EOC signal is fed back to the SC input, immediately initiating a new cycle on the next clock pulse.

#### Continuously Cycling 12–Bit ADC (Figure 4)

Because each successive approximation register (SAR) has a capability of handling only an eight–bit word, two must be cascaded to make an ADC with more than eight bits.

When it is necessary to cascade two SAR's, the second SAR must have a stable resettable state to remain in while awaiting a subsequent start signal. However, the first stage must not have a stable resettable state while recycling, because during switch–on or due to outside influences, the first stage has entered a reset state, the entire ADC will remain in a stable non–functional condition.

This 12–bit ADC is continuously recycling. The serial as well as the parallel outputs are updated every thirteenth clock pulse. The EOC pulse indicates the completion of the 12–bit conversion cycle, the end of the serial output word, and the validity of the parallel data output.

Figure 2. Externally Controlled 6–Bit ADC

Figure 3. Continuously Cycling 8-Bit ADC

Figure 4. Continuously Cycling 12-Bit ADC

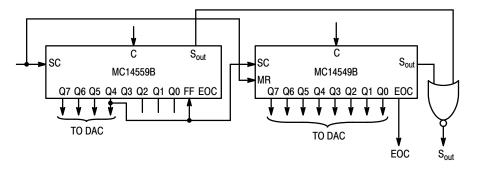

#### Externally Controlled 12–Bit ADC (Figure 5)

In this circuit the external pulse starts the first SAR and simultaneously resets the cascaded second SAR. When Q4 of the first SAR goes high, the second SAR starts conversion, and the first one stops conversion. EOC indicates that the parallel data are valid and that the serial output is complete. Updating the output data is started with every external control pulse.

#### Additional Motorola Parts for Successive Approximation ADC

**Monolithic digital-to-analog converters** — The MC1408/1508 converter has eight-bit resolution and is available with 6, 7, and 8-bit accuracy. **The amplifier-comparator block** — The MC1407/1507 contains a high speed operational amplifier and a high speed comparator with adjustable window.

With these two linear parts it is possible to construct SA–ADCs with an accuracy of up to eight bits, using as the register one MC14549B or one MC14559B. An additional CMOS block will be necessary to generate the clock frequency.

Additional information on successive approximation ADC is found in Motorola Application Note AN–716.

Figure 5. Externally Controlled 12–Bit ADC

#### **MECHANICAL CASE OUTLINE** PACKAGE DIMENSIONS

#### SOIC-16 WB CASE 751G ISSUE E SCALE 1:1 NOTES A DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 1. CONTROLLING DIMENSION: MILLIMETERS 2. 16 🗢 0.25@ B@ В DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. з. <u>A A A A</u> RRRR ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS. 4. MAXIMUM MOLD PROTRUSION OR FLASH TO BE 0.15 PER SIDE. 5. MILLIMETERS DIM MIN. MAX. H Н Α 2.35 2.65 h 8 45 0.25 A1 0.10 -16X B e DETAIL A в 0.35 0.49 0.2500 TAS BS END VIEW С 0.23 0.32 TOP VIEW D 10.15 10.45 7.40 7.60 Ε 1.27 BSC e 16X н 10.05 10.55 -L h 0.53 REF SEATIN **A1** 0.50 0.90 L SIDE VIEW М 0\* 7\* DETAIL A 2X SCALE 0000|0000 GENERIC 11.00 **MARKING DIAGRAM\*** 1 16X 1.62 .27 XXXXXXXXXXXX PITCH XXXXXXXXXXXX RECOMMENDED AWLYYWWG MOUNTING FOOTPRINT H H Η 1 H Н XXXXX = Specific Device Code = Assembly Location А = Wafer Lot WL YY = Year ww = Work Week G = Pb-Free Package \*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may

| DOCUMENT NUMBER:                                                                      | BASB42567B     Electronic versions are uncontrolled except when accessed directly from the Document Repository.       Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |             |  |  |  |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|--|

| DESCRIPTION:                                                                          | N: SOIC-16 WB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  | PAGE 1 OF 1 |  |  |  |

| the right to make changes without furthe<br>purpose, nor does <b>onsemi</b> assume an | onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves<br>the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular<br>purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation<br>special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |  |             |  |  |  |

or may not be present. Some products may

not follow the Generic Marking.

# DUSEM

DATE 08 OCT 2021

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales