# **4-Bit Magnitude** Comparator

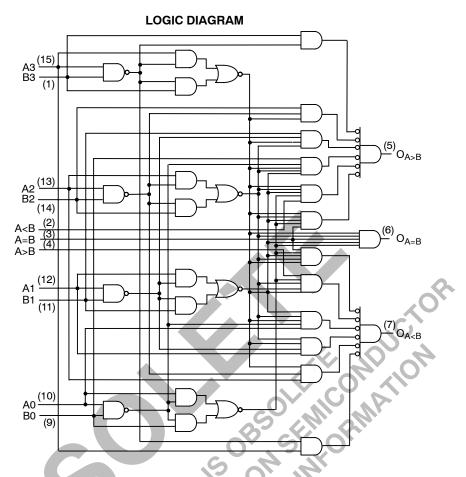

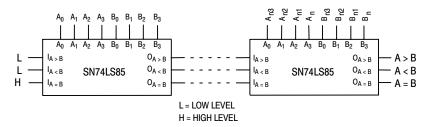

The SN74LS85 is a 4-Bit Magnitude Camparator which compares two 4-bit words (A, B), each word having four Parallel Inputs (A<sub>0</sub>-A<sub>3</sub>, B<sub>0</sub>-B<sub>3</sub>); A<sub>3</sub>, B<sub>3</sub> being the most significant inputs. Operation is not restricted to binary codes, the device will work with any monotonic code. Three Outputs are provided: "A greater than B"  $(O_{A>B})$ , "A less than B"  $(O_{A<B})$ , "A equal to B"  $(O_{A=B})$ . Three Expander Inputs, I<sub>A>B</sub>, I<sub>A<B</sub>, I<sub>A=B</sub>, allow cascading without external gates. For proper compare operation, the Expander Inputs to the least significant position must be connected as follows:  $I_{A < B} = I_{A > B} = L_{a}$  $I_{A=B} = H$ . For serial (ripple) expansion, the  $O_{A>B}$ ,  $O_{A<B}$  and  $O_{A=B}$ Outputs are connected respectively to the  $I_{A>B}$ ,  $I_{A<B}$ , and  $I_{A=B}$ Inputs of the next most significant comparator, as shown in Figure 1. Refer to Applications section of data sheet for high speed method of comparing large words.

The Truth Table on the following page describes the operation of the SN74LS85 under all possible logic conditions. The upper 11 lines describe the normal operation under all conditions that will occur in a Max Uni<sup>4</sup> 5.25 single device or in a series expansion scheme. The lower five lines describe the operation under abnormal conditions on the cascading inputs. These conditions occur when the parallel expansion technique is used.

- Easily Expandable

- Binary or BCD Comparison

- $O_{A>B}$ ,  $O_{A<B}$ , and  $O_{A=B}$  Outputs Available

| GOAIIAN         | TEED OF EIRAING HANG                   |      |     |      |      |  |

|-----------------|----------------------------------------|------|-----|------|------|--|

| Symbol          | Parameter                              | Min  | Тур | Max  | Unit |  |

| V <sub>CC</sub> | Supply Voltage                         | 4.75 | 5.0 | 5.25 | V    |  |

| T <sub>A</sub>  | Operating Ambient<br>Temperature Range | 0    | 25  | 70   | °C   |  |

| I <sub>OH</sub> | Output Current – High                  | 6    |     | -0.4 | mA   |  |

| I <sub>OL</sub> | Output Current – Low                   | 5    |     | 8.0  | mA   |  |

|                 | PLEA                                   | R    |     |      |      |  |

### **GUARANTEED OPERATING RANGES**

## **ON Semiconductor™**

http://onsemi.com

LOW POWER SCHOTTKY

**CASE 648**

SOIC **D SUFFIX** CASE 751B

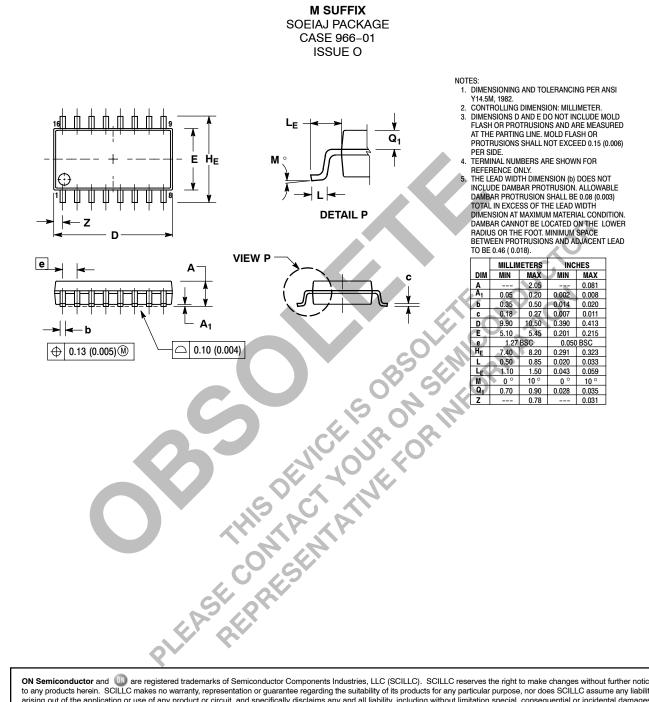

**M SUFFIX CASE 966**

## **ORDERING INFORMATION**

| Device      | Package    | Shipping         |  |  |

|-------------|------------|------------------|--|--|

| SN74LS85N   | 16 Pin DIP | 2000 Units/Box   |  |  |

| SN74LS85D   | SOIC-16    | 38 Units/Rail    |  |  |

| SN74LS85DR2 | SOIC-16    | 2500/Tape & Reel |  |  |

| SN74LS85M   | SOEIAJ-16  | See Note 1       |  |  |

| SN74LS85MEL | SOEIAJ-16  | See Note 1       |  |  |

1. For ordering information on the EIAJ version of the SOIC package, please contact your local ON Semiconductor representative.

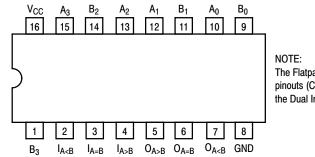

### CONNECTION DIAGRAM DIP (TOP VIEW)

The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package.

|                                                                   | _                              | LOADING  | (Note a)       | _        |

|-------------------------------------------------------------------|--------------------------------|----------|----------------|----------|

| PIN NAMES                                                         |                                | HIGH     | LOW            | _        |

| A <sub>0</sub> - A <sub>3</sub> , B <sub>0</sub> - B <sub>3</sub> | Parallel Inputs                | 1.5 U.L. | 0.75 U.L.      | -        |

| I <sub>A = B</sub>                                                | A = B Expander Inputs          | 1.5 U.L. | 0.75 U.L.      | <b>^</b> |

| I <sub>A &lt; B</sub> , I <sub>A &gt; B</sub>                     | A < B, A > B, Expander Inputs  | 0.5 U.L. | 0.25 U.L.      |          |

| O <sub>A &gt; B</sub>                                             | A Greater than B Output        | 10 U.L.  | 5 U.L.         |          |

| O <sub>A &lt; B</sub>                                             | B Greater than A Output        | 10 U.L.  | 5 U.L.         |          |

| O <sub>A</sub> = B                                                | A Equal to B Output            | 10 U.L.  | 5 U.L.         |          |

| NOTES:<br>a) 1 TTL Unit L                                         | oad (U.L.) = 40 μΑ HIGH/1.6 mA | LOW.     | INCON<br>INCON | ATION    |

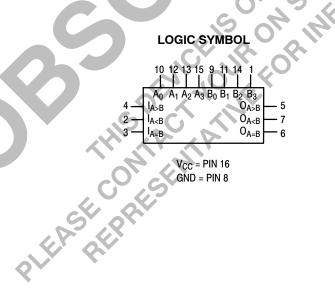

|                                                                   | LOGIC SYMBOL                   |          |                |          |

|                                                                   |                                | 40°      |                |          |

NOTES:

TRUTH TABLE

|   |                                 |                                |                                                                                            | TI                              | RUTH T              | ABLE                           |                  |                     |                                |                  |

|---|---------------------------------|--------------------------------|--------------------------------------------------------------------------------------------|---------------------------------|---------------------|--------------------------------|------------------|---------------------|--------------------------------|------------------|

|   | COMPARING INPUTS                |                                |                                                                                            |                                 | SCADIN<br>NPUTS     | IG O                           | OUTPUTS          |                     |                                |                  |

| A | A <sub>3</sub> ,B <sub>3</sub>  | A <sub>2</sub> ,B <sub>2</sub> | A <sub>1</sub> ,B <sub>1</sub>                                                             | A <sub>0</sub> ,B <sub>0</sub>  | I <sub>A&gt;B</sub> | I <sub>A<b< sub=""></b<></sub> | I <sub>A=B</sub> | O <sub>A&gt;B</sub> | O <sub>A<b< sub=""></b<></sub> | O <sub>A=B</sub> |

| A | <sub>3&gt;</sub> B <sub>3</sub> | X                              | Х                                                                                          | X                               | X                   | X                              | X                | Н                   | L                              | L                |

| A | <sub>3</sub> <b<sub>3</b<sub>   | x                              | Х                                                                                          | <b>2</b> X                      | X                   | X                              | Х                | L                   | Н                              | L                |

| A | <sub>3=B3</sub>                 | $A_2 > B_2$                    | Х                                                                                          | Х                               | X                   | X                              | Х                | Н                   | L                              | L                |

| A | <sub>3=B3</sub>                 | $A_2 < B_2$                    | X                                                                                          | Х                               | X                   | Х                              | Х                | L                   | Н                              | L                |

|   | <sub>3=B3</sub>                 | $A_2 = B_2$                    | A <sub>1</sub> >B <sub>1</sub>                                                             | X                               | X                   | Х                              | Х                | Н                   | L                              | L                |

| A |                                 | $A_2 = B_2$                    | A1 <b1< td=""><td>X</td><td>X</td><td>Х</td><td>Х</td><td>L</td><td>Н</td><td>L</td></b1<> | X                               | X                   | Х                              | Х                | L                   | Н                              | L                |

| A | <sub>3</sub> =B <sub>3</sub>    | $A_2 = B_2$                    | A <sub>1</sub> =B1                                                                         | $A_0 > B_0$                     | Х                   | Х                              | Х                | Н                   | L                              | L                |

| A | <sub>3=</sub> B <sub>3</sub>    | $A_2=B_2$                      | A1=B1                                                                                      | A <sub>0</sub> <b<sub>0</b<sub> | Х                   | Х                              | Х                | L                   | Н                              | L                |

|   |                                 | A <sub>2</sub> =B <sub>2</sub> | A <sub>1</sub> =B <sub>1</sub>                                                             | $A_0 = B_0$                     | Н                   | L                              | L                | Н                   | L                              | L                |

| A | <sub>3=</sub> B <sub>3</sub>    | $A_2 = B_2$                    | A1=B1                                                                                      | $A_0 = B_0$                     | L                   | Н                              | L                | L                   | Н                              | L                |

| A | <sub>3</sub> =B <sub>3</sub> ,  | $A_2 = B_2$                    | $A_1 = B_1$                                                                                | $A_0 = B_0$                     | Х                   | Х                              | Н                | L                   | L                              | Н                |

| A | <sub>3</sub> =B <sub>3</sub>    | $A_2=B_2$                      | $A_1 = B_1$                                                                                | $A_0 = B_0$                     | Н                   | Н                              | L                | L                   | L                              | L                |

| A | <sub>3=B3</sub>                 | $A_2 = B_2$                    | $A_1 = B_1$                                                                                | $A_0 = B_0$                     | L                   | L                              | L                | Н                   | Н                              | L                |

H = HIGH Level L = LOW Level X = IMMATERIAL

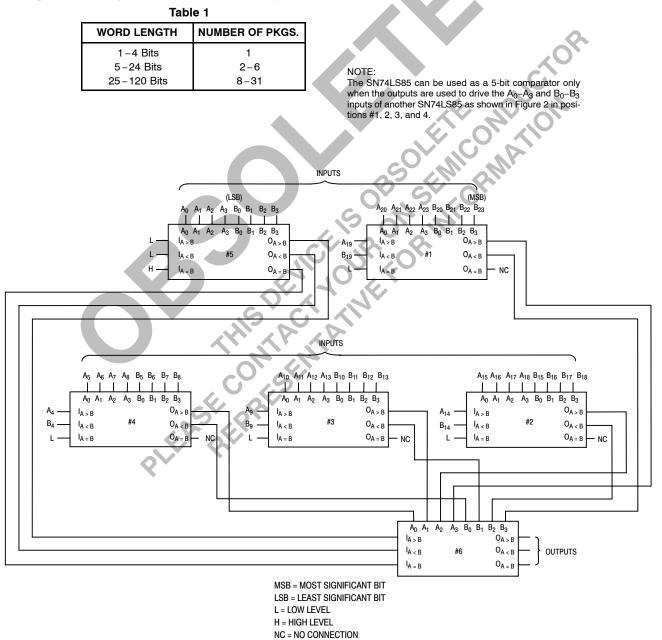

#### Figure 1. Comparing Two n-Bit Words

### **APPLICATIONS**

Figure 2 shows a high speed method of comparing two 24-bit words with only two levels of device delay. With the technique shown in Figure 1, six levels of device delay result

when comparing two 24-bit words. The parallel technique can be expanded to any number of bits, see Table 1.

Figure 2. Comparison of Two 24-Bit Words

| DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE | (unless otherwise specified) |

|-----------------------------------------------------|------------------------------|

|-----------------------------------------------------|------------------------------|

|                 |                                                    | Limits |       |              |      |                                                                            |                                                                         |  |

|-----------------|----------------------------------------------------|--------|-------|--------------|------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Symbol          | Parameter                                          | Min    | Тур   | Max          | Unit | Tes                                                                        | t Conditions                                                            |  |

| V <sub>IH</sub> | Input HIGH Voltage                                 | 2.0    |       |              | V    | Guaranteed Input HIGH Voltage for<br>All Inputs                            |                                                                         |  |

| V <sub>IL</sub> | Input LOW Voltage                                  |        |       | 0.8          | V    | Guaranteed Input LOW Voltage for<br>All Inputs                             |                                                                         |  |

| V <sub>IK</sub> | Input Clamp Diode Voltage                          |        | -0.65 | -1.5         | V    | $V_{CC}$ = MIN, $I_{IN}$ =                                                 | –18 mA                                                                  |  |

| V <sub>OH</sub> | Output HIGH Voltage                                | 2.7    | 3.5   |              | V    | V <sub>CC</sub> = MIN, I <sub>OH</sub> =<br>or V <sub>IL</sub> per Truth T | = MAX,  V <sub>IN</sub> = V <sub>IH</sub><br>īable                      |  |

| .,              | Output LOW Voltage                                 |        | 0.25  | 0.4          | V    | l <sub>OL</sub> = 4.0 mA                                                   | $V_{CC} = V_{CC} MIN,$                                                  |  |

| V <sub>OL</sub> |                                                    |        | 0.35  | 0.5          | V    | l <sub>OL</sub> = 8.0 mA                                                   | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub><br>per Truth Table |  |

| IIH             | Input HIGH Current<br>A < B, A > B<br>Other Inputs |        |       | 20<br>60     | μΑ   | $V_{CC}$ = MAX, $V_{IN}$                                                   | = 2.7 V                                                                 |  |

|                 | A < B, A > B<br>Other Inputs                       |        |       | 0.1<br>0.3   | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                     | = 7.0 V                                                                 |  |

| IIL             | Input LOW Current<br>A < B, A > B<br>Other Inputs  |        |       | -0.4<br>-1.2 | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                     | = 0.4 V                                                                 |  |

| I <sub>OS</sub> | Output Short Circuit Current (Note 2)              | -20    |       | -100         | mA   | V <sub>CC</sub> = MAX                                                      |                                                                         |  |

|                 | Power Supply Current                               |        |       | 20           | mA   | V <sub>CC</sub> = MAX                                                      |                                                                         |  |

# AC CHARACTERISTICS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

| 2. Not more th                       | an one output should be shorted at a tin                            | ne, nor fo | r more th | an 1 seco | ond. | N' All                                            |

|--------------------------------------|---------------------------------------------------------------------|------------|-----------|-----------|------|---------------------------------------------------|

| AC CHARAC                            | <b>TERISTICS</b> ( $T_A = 25^{\circ}C$ , $V_{CC} = 5.0 \text{ V}$ ) |            |           | <u> </u>  | 29   | 60                                                |

|                                      |                                                                     |            | Limits    | 2 C       |      |                                                   |

| Symbol                               | Parameter                                                           | Min        | Тур       | Max       | Unit | Test Conditions                                   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Any A or B to A < B, A > B                                          | 7.         | 24<br>20  | 36<br>30  | ns   |                                                   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Any A or B to A = B                                                 |            | 27<br>23  | 45<br>45  | ns   |                                                   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | A < B or A = B to A > B                                             |            | 14<br>11  | 22<br>17  | ns   | V <sub>CC</sub> = 5.0 V<br>C <sub>L</sub> = 15 pF |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | A = B to A = B                                                      | S          | 13<br>13  | 20<br>26  | ns   |                                                   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | A > B  or  A = B  to  A < B                                         |            | 14<br>11  | 22<br>17  | ns   |                                                   |

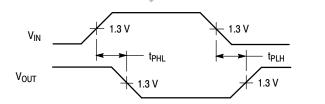

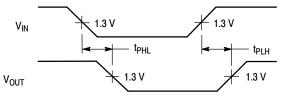

AC WAVEFORMS

Figure 3.

Figure 4.

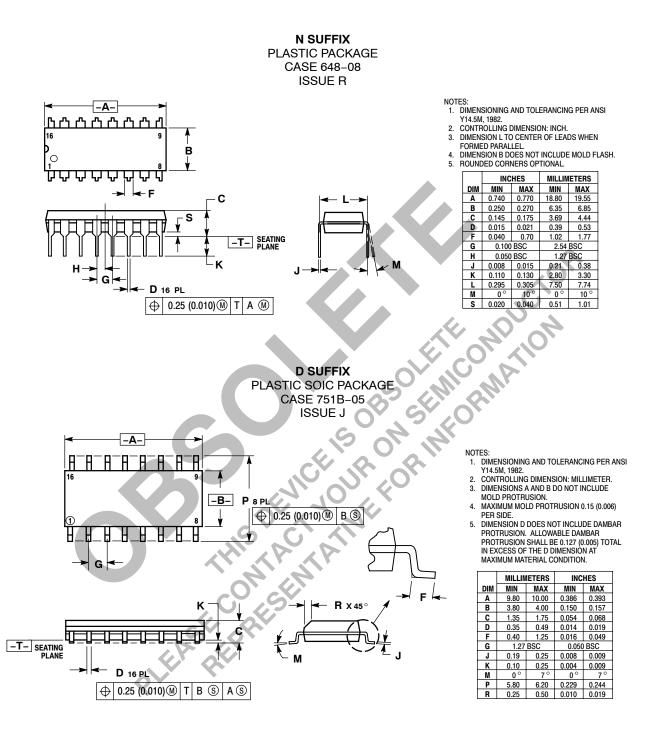

#### PACKAGE DIMENSIONS

### PACKAGE DIMENSIONS

ON Semiconductor and IIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use persons, and reasonable attorney fees andising out of, directly or indirectly, any claim of personal injury or death agolocation with such unintended or unauthorized use persons, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agolocated with such unintended or unauthorized use persons, and reasonable attorney fees anising out of, directly or indirectly, any claim of personal in

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative