SBAS019A – JANUARY 1992 – REVISED MAY 2003

# 12-Bit 10μs Sampling CMOS ANALOG-to-DIGITAL CONVERTER

## **FEATURES**

- 100kHz min SAMPLING RATE

- STANDARD ±10V INPUT RANGE

- 72dB min SINAD WITH 45kHz INPUT

- ±0.45 LSB max INL

- DNL: 12 Bits "No Missing Codes"

- SINGLE +5V SUPPLY OPERATION

- PIN-COMPATIBLE WITH 16-BIT ADS7805

- USES INTERNAL OR EXTERNAL REFERENCE

- COMPLETE WITH S/H, REF, CLOCK, ETC.

- FULL PARALLEL DATA OUTPUT

- 100mW max POWER DISSIPATION

- 28-PIN 0.3" PLASTIC DIP AND SO PACKAGES

## DESCRIPTION

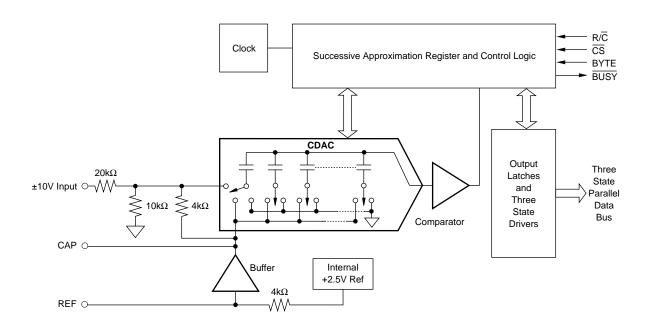

The ADS7804 is a complete 12-bit sampling analog-to-digital (A/D) converter using state-of-the-art CMOS structures. It contains a complete 12-bit, capacitor-based, SAR A/D converter with S/H, reference, clock, interface for microprocessor use, and three-state output drivers.

The ADS7804 is specified at a 100kHz sampling rate, and guaranteed over the full temperature range. Laser-trimmed scaling resistors provide an industry-standard  $\pm 10V$  input range, while the innovative design allows operation from a single +5V supply, with power dissipation under 100mW.

The 28-pin ADS7804 is available in plastic 0.3" DIP and SO packages, both fully specified for operation over the industrial -40°C to +85°C range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **ABSOLUTE MAXIMUM RATINGS**

|                                                                                                                                                                                 | ±25V<br>+V <sub>ANA</sub> +0.3V to AGND2 -0.3V<br>Indefinite Short to AGND2<br>Momentary Short to V <sub>ANA</sub> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Ground Voltage Differences: DGND, V <sub>ANA</sub> V <sub>DIG</sub> to V <sub>ANA</sub> V <sub>DIG</sub> Digital Inputs Maximum Junction Temperature Internal Power Dissipation | AGND1, AGND2                                                                                                       |

| Lead Temperature (soldering, 10s)                                                                                                                                               | +300 C                                                                                                             |

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **PACKAGE/ORDERING INFORMATION**

| PRODUCT   | MAXIMUM<br>LINEARITY<br>ERROR<br>(LSB) | MINIMUM<br>SIGNAL-TO-<br>(NOISE+DISTORTION)<br>RATIO (LSB) | PACKAGE-LEAD<br>(DESIGNATOR) <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER        | TRANSPORT<br>MEDIA, QUANTITY    |

|-----------|----------------------------------------|------------------------------------------------------------|---------------------------------------------|-----------------------------------|--------------------|---------------------------|---------------------------------|

| ADS7804P  | ±0.9                                   | 70                                                         | DIP-28 (NT)                                 | -40°C to +85°C                    | ADS7804P           | ADS7804P                  | Tube, 13                        |

| ADS7804PB | ±0.45                                  | 72                                                         | DIP-28 (NT)                                 | -40°C to +85°C                    | ADS7804PB          | ADS7804PB                 | Tube, 13                        |

| ADS7804U  | ±0.9                                   | 70<br>"                                                    | SO-28 (DW)                                  | -40°C to +85°C                    | ADS7804U<br>"      | ADS7804U<br>ADS7804U/1K   | Tube, 28<br>Tape and Reel, 1000 |

| ADS7804UB | ±0.45<br>"                             | 72<br>"                                                    | SO-28 (DW)                                  | -40°C to +85°C                    | ADS7804UB<br>"     | ADS7804UB<br>ADS7804UB/1K | Tube, 28<br>Tape and Reel, 1000 |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $f_S = 100$ kHz, and  $V_{DIG} = V_{ANA} = +5V$ , using internal reference, unless otherwise specified.

|                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                         |                | ADS7804P, U          |                                             |               | ADS7804PB, UB     |                                         |                                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|---------------------------------------------|---------------|-------------------|-----------------------------------------|-----------------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                             | CONDITIONS                                                                                                                                                              | MIN            | TYP                  | MAX                                         | MIN           | TYP               | MAX                                     | UNITS                                                           |  |

| RESOLUTION                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                         |                |                      | 12                                          |               |                   | *                                       | Bits                                                            |  |

| ANALOG INPUT Voltage Ranges Impedance Capacitance                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |                | ±10V<br>23<br>35     |                                             |               | *<br>*<br>*       |                                         | V<br>kΩ<br>pF                                                   |  |

| THROUGHPUT SPEED Conversion Time Complete Cycle Throughput Rate                                                                                                                                                                                                                                                                                                       | Acquire and Convert                                                                                                                                                     | 100            | 5.7                  | 8<br>10                                     | *             | *                 | *                                       | μs<br>μs<br>kHz                                                 |  |

| DC ACCURACY Integral Linearity Error Differential Linearity Error No Missing Codes Transition Noise <sup>(2)</sup> Full Scale Error <sup>(3,4)</sup> Full Scale Error Drift Full Scale Error Drift Full Scale Error Drift Bipolar Zero Error <sup>(3)</sup> Bipolar Zero Error Drift Power Supply Sensitivity (V <sub>DIG</sub> = V <sub>ANA</sub> = V <sub>D</sub> ) | Ext. 2.5000V Ref<br>Ext. 2.5000V Ref<br>+4.75V < V <sub>D</sub> < +5.25V                                                                                                |                | Ensured 0.1 ±7 ±2 ±2 | ±0.9<br>±0.9<br>±0.5<br>±0.5<br>±10<br>±0.5 |               | *<br>*<br>±5<br>* | ±0.45<br>±0.45<br>±0.25<br>±0.25<br>±10 | LSB <sup>(1)</sup> LSB Bits LSB % ppm/°C % ppm/°C mV ppm/°C LSB |  |

| AC ACCURACY Spurious-Free Dynamic Range Total Harmonic Distortion Signal-to-(Noise+Distortion) Signal-to-Noise Full-Power Bandwidth <sup>(6)</sup>                                                                                                                                                                                                                    | $\begin{aligned} f_{\text{IN}} &= 45 \text{kHz} \\ \end{aligned}$ | 80<br>70<br>70 | 250                  | -80                                         | *<br>72<br>72 | *                 | *                                       | dB <sup>(5)</sup><br>dB<br>dB<br>dB<br>kHz                      |  |

| SAMPLING DYNAMICS Aperture Delay Aperture Jitter Transient Response Overvoltage Recovery <sup>(7)</sup>                                                                                                                                                                                                                                                               | FS Step                                                                                                                                                                 | Sufficie       | 40<br>ent to meet A  | .C specs<br>2                               |               | *                 | *                                       | ns<br>μs<br>ns                                                  |  |

## **ELECTRICAL CHARACTERISTICS (Cont.)**

At  $T_A = -40^{\circ}C$  to +85°C,  $f_S = 100$ kHz, and  $V_{DIG} = V_{ANA} = +5V$ , using internal reference, unless otherwise specified.

|                                                                                                            |                                                                                                  |                   | DS7804P,              | U                                          | А                   | DS7804PB,        | UB          |                    |  |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------|-----------------------|--------------------------------------------|---------------------|------------------|-------------|--------------------|--|

| PARAMETER                                                                                                  | CONDITIONS                                                                                       | MIN               | TYP                   | MAX                                        | MIN                 | TYP              | MAX         | UNITS              |  |

| REFERENCE Internal Reference Voltage Internal Reference Source Current (Must use external buffer.)         |                                                                                                  | 2.48              | 2.5<br>1              | 2.52                                       | *                   | *                | *           | V<br>μA            |  |

| Internal Reference Drift External Reference Voltage Range for Specified Linearity                          | Fut 0 5000V Dut                                                                                  | 2.3               | 8<br>2.5              | 2.7                                        | *                   | *                | *           | ppm/°C<br>V        |  |

| External Reference Current Drain                                                                           | Ext. 2.5000V Ref                                                                                 |                   |                       | 100                                        |                     |                  | *           | μΑ                 |  |

| DIGITAL INPUTS Logic Levels V <sub>IL</sub> V <sub>IH</sub> I <sub>IL</sub> I <sub>IH</sub>                |                                                                                                  | -0.3<br>+2.0      |                       | +0.8<br>V <sub>D</sub> +0.3V<br>±10<br>±10 | *                   |                  | *<br>*<br>* | V<br>V<br>μΑ<br>μΑ |  |

| DIGITAL OUTPUTS Data Format Data Coding                                                                    |                                                                                                  |                   |                       | Parallel<br>Binary Two's                   | 12 Bits<br>Compleme | nt               |             |                    |  |

| V <sub>OL</sub><br>V <sub>OH</sub><br>Leakage Current                                                      | $I_{SINK}$ = 1.6mA<br>$I_{SOURCE}$ = 500 $\mu$ A<br>High-Z State,<br>$V_{OUT}$ = 0V to $V_{DIG}$ | +4                |                       | +0.4<br>±5                                 | *                   |                  | *           | V<br>V<br>μA       |  |

| Output Capacitance                                                                                         | High-Z State                                                                                     |                   |                       | 15                                         |                     |                  | 15          | pF                 |  |

| DIGITAL TIMING Bus Access Time Bus Relinquish Time                                                         |                                                                                                  |                   |                       | 83<br>83                                   |                     |                  | *           | ns<br>ns           |  |

| POWER SUPPLIES Specified Performance V <sub>DIG</sub> V <sub>ANA</sub> +I <sub>DIG</sub> +I <sub>ANA</sub> | Must be $\leq V_{ANA}$                                                                           | +4.75<br>+4.75    | +5<br>+5<br>0.3<br>16 | +5.25<br>+5.25                             | * *                 | *<br>*<br>*<br>* | *           | V<br>V<br>mA<br>mA |  |

| Power Dissipation                                                                                          | f <sub>S</sub> = 100kHz                                                                          |                   |                       | 100                                        |                     |                  | *           | mW                 |  |

| TEMPERATURE RANGE Specified Performance Derated Performance Storage Thermal Resistance ( $\theta_{10}$ )   |                                                                                                  | -40<br>-55<br>-65 |                       | +85<br>+125<br>+150                        | *<br>*<br>*         |                  | *<br>*<br>* | °C<br>°C<br>°C     |  |

| Plastic DIP<br>SO                                                                                          |                                                                                                  |                   | 75<br>75              |                                            |                     | *                |             | °C/W               |  |

NOTES: (1) LSB means Least Significant Bit. For the 12-bit,  $\pm 10V$  input ADS7804, one LSB is 4.88mV. (2) Typical rms noise at worst case transitions and temperatures. (3) As measured with fixed resistors shown in Figure 4. Adjustable to zero with external potentiometer. (4) Full scale error is the worst case of –Full Scale or +Full Scale untrimmed deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and includes the effect of offset error. (5) All specifications in dB are referred to a full-scale  $\pm 10V$  input. (6) Full-Power Bandwidth defined as Full-Scale input frequency at which Signal-to-(Noise + Distortion) degrades to 60dB, or 10 bits of accuracy. (7) Recovers to specified performance after 2 x FS input overvoltage.

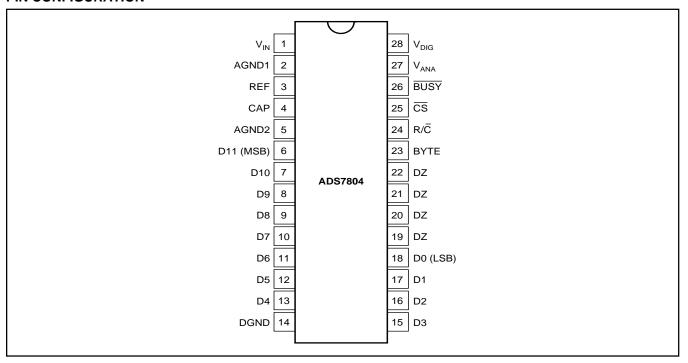

|      |                 | DIGITAL |                                                                                                                                                                                                                                                   |

|------|-----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN# | NAME            | I/O     | DESCRIPTION                                                                                                                                                                                                                                       |

| 1    | V <sub>IN</sub> |         | Analog Input. See Figure 7.                                                                                                                                                                                                                       |

| 2    | AGND1           |         | Analog Ground. Used internally as ground reference point.                                                                                                                                                                                         |

| 3    | REF             |         | Reference Input/Output. 2.2μF tantalum capacitor to ground.                                                                                                                                                                                       |

| 4    | CAP             |         | Reference Buffer Capacitor. 2.2μF tantalum capacitor to ground.                                                                                                                                                                                   |

| 5    | AGND2           |         | Analog Ground.                                                                                                                                                                                                                                    |

| 6    | D11 (MSB)       | 0       | Data Bit 11. Most Significant Bit (MSB) of conversion results. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                           |

| 7    | D10             | 0       | Data Bit 10. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when $R/\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 8    | D9              | 0       | Data Bit 9. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 9    | D8              | 0       | Data Bit 8. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 10   | D7              | 0       | Data Bit 7. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 11   | D6              | 0       | Data Bit 6. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 12   | D5              | 0       | Data Bit 5. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when $R/\overline{C}$ is LOW.                                                                                                                                                      |

| 13   | D4              | 0       | Data Bit 4. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 14   | DGND            |         | Digital Ground.                                                                                                                                                                                                                                   |

| 15   | D3              | 0       | Data Bit 3. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 16   | D2              | 0       | Data Bit 2. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 17   | D1              | 0       | Data Bit 1. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                                                                              |

| 18   | D0 (LSB)        | 0       | Data Bit 0. Lease Significant Bit (LSB) of conversion results. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/C is LOW.                                                                                                                |

| 19   | DZ              | 0       | LOW when $\overline{\text{CS}}$ LOW, R/ $\overline{\text{C}}$ HIGH. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                      |

| 20   | DZ              | 0       | LOW when $\overline{\text{CS}}$ LOW, R/ $\overline{\text{C}}$ HIGH. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                      |

| 21   | DZ              | 0       | LOW when $\overline{\text{CS}}$ LOW, R/ $\overline{\text{C}}$ HIGH. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                      |

| 22   | DZ              | 0       | LOW when $\overline{\text{CS}}$ LOW, R/ $\overline{\text{C}}$ HIGH. Hi-Z state when $\overline{\text{CS}}$ is HIGH, or when R/ $\overline{\text{C}}$ is LOW.                                                                                      |

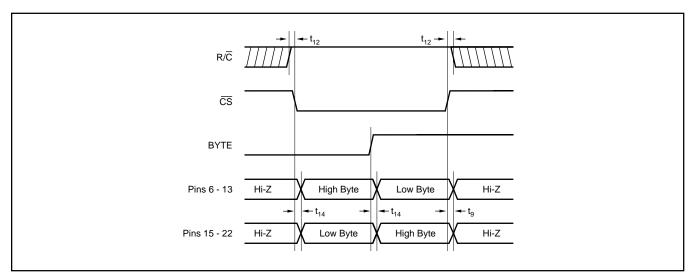

| 23   | BYTE            | 1       | Selects 8 most significant bits (LOW) or 8 least significant bits (HIGH).                                                                                                                                                                         |

| 24   | R/C             | I       | With $\overline{\text{CS}}$ LOW and $\overline{\text{BUSY}}$ HIGH, a Falling Edge on R/ $\overline{\text{C}}$ Initiates a New Conversion. With $\overline{\text{CS}}$ LOW, a rising edge on R/ $\overline{\text{C}}$ enables the parallel output. |

| 25   | cs              | 1       | Internally OR'd with R/ $\overline{C}$ . If R/ $\overline{C}$ LOW, a falling edge on $\overline{CS}$ initiates a new conversion.                                                                                                                  |

| 26   | BUSY            | 0       | At the start of a conversion, $\overline{\text{BUSY}}$ goes LOW and stays LOW until the conversion is completed and the digital outputs have been updated.                                                                                        |

| 27   | $V_{ANA}$       |         | Analog Supply Input. Nominally +5V. Decouple to ground with 0.1μF ceramic and 10μF tantalum capacitors.                                                                                                                                           |

| 28   | $V_{DIG}$       |         | Digital Supply Input. Nominally +5V. Connect directly to pin 27. Must be $\leq$ $V_{ANA}$ .                                                                                                                                                       |

TABLE I. Pin Assignments.

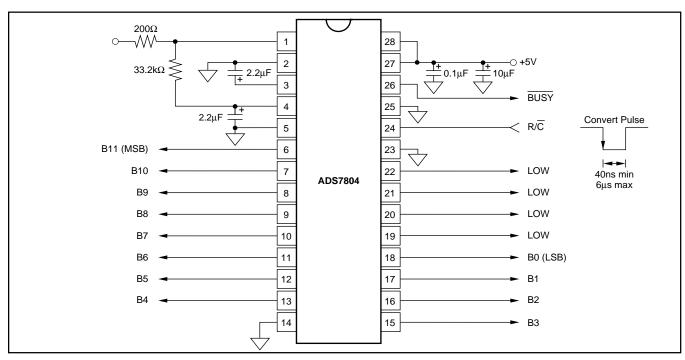

## **BASIC OPERATION**

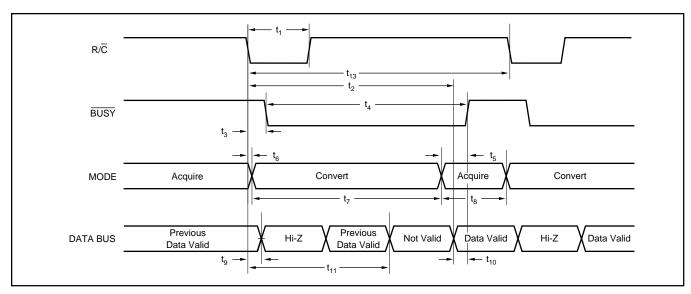

Figure 1 shows a basic circuit to operate the ADS7804 with a full parallel data output. Taking R/C (pin 24) LOW for a minimum of 40ns (6µs max) will initiate a conversion. BUSY (pin 26) will go LOW and stay LOW until the conversion is completed and the output registers are updated. Data will be output in Binary Two's Complement with the MSB on pin 6. BUSY going HIGH can be used to latch the data. All convert commands will be ignored while BUSY is LOW.

The ADS7804 will begin tracking the input signal at the end of the conversion. Allowing 10µs between convert commands assures accurate acquisition of a new signal.

The offset and gain are adjusted internally to allow external trimming with a single supply. The external resistors compensate for this adjustment and can be left out if the offset and gain will be corrected in software (refer to the Calibration section).

## STARTING A CONVERSION

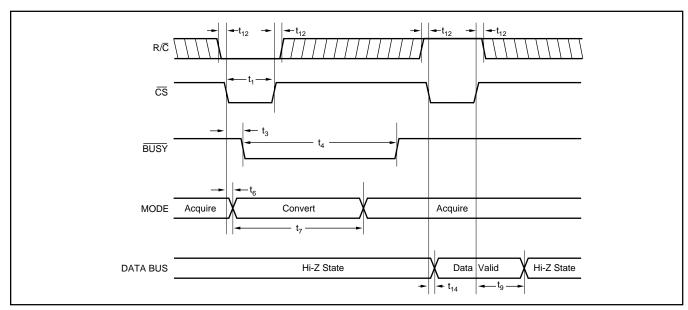

The combination of  $\overline{CS}$  (pin 25) and  $R/\overline{C}$  (pin 24) LOW for a minimum of 40ns immediately puts the sample/hold of the ADS7804 in the hold state and starts conversion 'n'.  $\overline{BUSY}$  (pin 26) will go LOW and stay LOW until conversion 'n' is completed and the internal output register has been updated. All new convert commands during  $\overline{BUSY}$  LOW will be ignored.  $\overline{CS}$  and/or  $R/\overline{C}$  must go HIGH before  $\overline{BUSY}$  goes HIGH or a new conversion will be initiated without sufficient time to acquire a new signal.

The ADS7804 will begin tracking the input signal at the end of the conversion. Allowing 10 $\mu$ s between convert commands assures accurate acquisition of a new signal. Refer to Table II for a summary of  $\overline{\text{CS}}$ ,  $\overline{\text{R/C}}$ , and  $\overline{\text{BUSY}}$  states and Figures 3 through 5 for timing diagrams.

| cs       | R/C      | BUSY     | OPERATION                                                                                                                                                                  |

|----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Х        | Х        | None. Databus is in Hi-Z state.                                                                                                                                            |

| <b>\</b> | 0        | 1        | Initiates conversion 'n'. Databus remains in Hi-Z state.                                                                                                                   |

| 0        | <b>→</b> | 1        | Initiates conversion 'n'. Databus enters Hi-Z state.                                                                                                                       |

| 0        | 1        | <b>↑</b> | Conversion 'n' completed. Valid data from conversion 'n' on the databus.                                                                                                   |

| <b>\</b> | 1        | 1        | Enables databus with valid data from conversion 'n'.                                                                                                                       |

| <b>\</b> | 1        | 0        | Enables databus with valid data from conversion 'n-1'(1). Conversion n in process.                                                                                         |

| 0        | 1        | 0        | Enables databus with valid data from conversion 'n-1'(1). Conversion 'n' in process.                                                                                       |

| 0        | 0        | 1        | New conversion initiated without acquisition of a new signal. Data will be invalid. $\overline{CS}$ and/or $R/\overline{C}$ must be HIGH when $\overline{BUSY}$ goes HIGH. |

| Х        | Х        | 0        | New convert commands ignored. Conversion 'n' in process.                                                                                                                   |

NOTE: (1) See Figures 2 and 3 for constraints on data valid from conversion "n-1".

Table II. Control Line Functions for Read and Convert.

$\overline{\text{CS}}$  and  $\overline{\text{R/C}}$  are internally OR'd and level triggered. There is not a requirement which input goes LOW first when initiating a conversion. If, however, it is critical that  $\overline{\text{CS}}$  or  $\overline{\text{R/C}}$  initiates conversion 'n', be sure the less critical input is LOW at least 10ns prior to the initiating input.

To reduce the number of control pins,  $\overline{CS}$  can be tied LOW using R/ $\overline{C}$  to control the read and convert modes. This will have no effect when using the internal data clock in the serial output mode. However, the parallel output will become active whenever R/ $\overline{C}$  goes HIGH. Refer to the Reading Data section.

FIGURE 1. Basic Operation.

## READING DATA

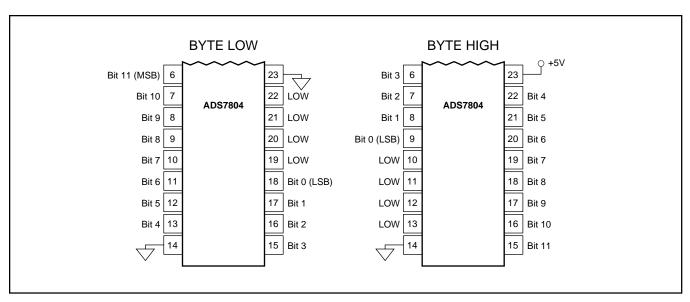

The ADS7804 outputs full or byte-reading parallel data in Binary Two's Complement data output format. The parallel output will be active when R/ $\overline{C}$  (pin 24) is HIGH and  $\overline{CS}$  (pin 25) is LOW. Any other combination of  $\overline{CS}$  and R/ $\overline{C}$  will tristate the parallel output. Valid conversion data can be read in a full parallel, 12-bit word or two 8-bit bytes on pins 6-13 and pins 15-22. BYTE (pin 23) can be toggled to read both bytes within one conversion cycle. Refer to Table III for ideal output codes and Figure 2 for bit locations relative to the state of BYTE.

|                                |              | DIGITAL OUTPUT<br>BINARY TWO'S COMPLEMENT |          |  |  |  |  |

|--------------------------------|--------------|-------------------------------------------|----------|--|--|--|--|

| DESCRIPTION                    | ANALOG INPUT | BINARY CODE                               | HEX CODE |  |  |  |  |

| Full Scale Range               | ±10V         |                                           |          |  |  |  |  |

| Least Significant<br>Bit (LSB) | 4.88mV       |                                           |          |  |  |  |  |

| +Full Scale<br>(10V – 1LSB)    | 9.99512V     | 0111 1111 1111                            | 7FF      |  |  |  |  |

| Midscale                       | 0V           | 0000 0000 0000                            | 000      |  |  |  |  |

| One LSB below<br>Midscale      | –4.88mV      | 1111 1111 1111                            | FFF      |  |  |  |  |

| -Full Scale                    | -10V         | 1000 0000 0000                            | 800      |  |  |  |  |

Table III. Ideal Input Voltages and Output Codes.

#### PARALLEL OUTPUT (After a Conversion)

After conversion 'n' is completed and the output registers have been updated, BUSY (pin 26) will go HIGH. Valid data from conversion 'n' will be available on D11-D0 (pin 6-13 and 15-18 when BYTE is LOW). BUSY going HIGH can be used to latch the data. Refer to Table IV and Figures 3 and 5 for timing specifications.

#### PARALLEL OUTPUT (During a Conversion)

After conversion 'n' has been initiated, valid data from conversion 'n-1' can be read and will be valid up to 16µs after the start of conversion 'n'. Do not attempt to read data from 16µs after the start of conversion 'n' until BUSY (pin 26) goes HIGH; this may result in reading invalid data. Refer to Table IV and Figures 3 and 5 for timing specifications.

**Note!** For the best possible performance, data should not be read during a conversion. The switching noise of the asynchronous data transfer can cause digital feedthrough degrading the converter's performance.

The number of control lines can be reduced by tieing CS LOW while using  $R/\overline{C}$  to initiate conversions and activate the output mode of the converter. See Figure 3.

| SYMBOL                           | DESCRIPTION                                    | MIN | TYP | MAX     | UNITS    |

|----------------------------------|------------------------------------------------|-----|-----|---------|----------|

| t <sub>1</sub>                   | Convert Pulse Width                            | 40  |     | 6000    | ns       |

| t <sub>2</sub>                   | Data Valid Delay after R/C LOW                 |     |     | 8       | μs       |

| t <sub>3</sub><br>t <sub>4</sub> | BUSY Delay from R/C LOW BUSY LOW               |     |     | 65<br>8 | ns<br>μs |

| t <sub>5</sub>                   | BUSY Delay after<br>End of Conversion          |     | 220 |         | ns       |

| t <sub>6</sub>                   | Aperture Delay                                 |     | 40  |         | ns       |

| t <sub>7</sub>                   | Conversion Time                                |     | 7.6 | 8       | μs       |

| t <sub>8</sub>                   | Acquisition Time                               |     |     | 2       | μs       |

| t <sub>9</sub>                   | Bus Relinquish T <u>im</u> e                   | 10  | 35  | 83      | ns       |

| t <sub>10</sub>                  | BUSY Delay after Data Valid                    | 50  | 200 |         | ns       |

| t <sub>11</sub>                  | Previous Data Valid<br>after R/C LOW           |     | 7.4 |         | μs       |

| t <sub>7</sub> + t <sub>6</sub>  | Throughput Time                                |     | 9   | 10      | μs       |

| t <sub>12</sub>                  | $R/\overline{C}$ to $\overline{CS}$ Setup Time | 10  |     |         | ns       |

| t <sub>13</sub>                  | Time Between Conversions                       | 10  |     |         | μs       |

| t <sub>14</sub>                  | Bus Access Time and BYTE Delay                 | 10  |     | 83      | ns       |

TABLE IV. Conversion Timing.

FIGURE 2. Bit Locations Relative to State of BYTE (pin 23).

FIGURE 3. Conversion Timing with Outputs Enabled after Conversion (CS Tied LOW.)

FIGURE 4. Using  $\overline{\text{CS}}$  to Control Conversion and Read Timing.

FIGURE 5. Using  $\overline{\text{CS}}$  and BYTE to Control Data Bus.

#### **INPUT RANGES**

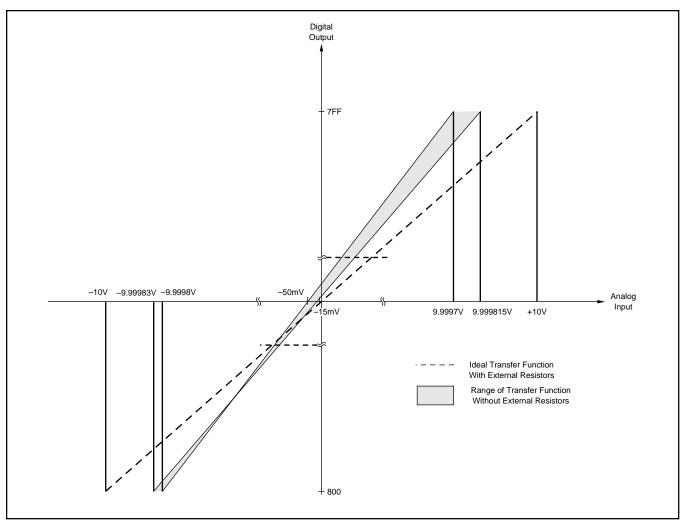

The ADS7804 offers a standard  $\pm 10V$  input range. Figure 6 shows the necessary circuit connections for the ADS7804 with and without hardware trim. Offset and full scale error<sup>(1)</sup> specifications are tested and guaranteed with the fixed resistors shown in Figure 6b. Adjustments for offset and gain are described in the Calibration section of this data sheet.

The offset and gain are adjusted internally to allow external trimming with a single supply. The external resistors compensate for this adjustment and can be left out if the offset and gain will be corrected in software (refer to the Calibration section).

The nominal input impedance of 23kW results from the combination of the internal resistor network shown on the front page of the product data sheet and the external resistors. The input resistor divider network provides inherent overvoltage protection guaranteed to at least  $\pm 25$ V. The 1% resistors used for the external circuitry do not compromise the accuracy or drift of the converter. They have little influence relative to the internal resistors, and tighter tolerances are not required.

NOTE: (1) Full scale error includes offset and gain errors measured at both +FS and -FS

## CALIBRATION

The ADS7804 can be trimmed in hardware or software. The offset should be trimmed before the gain since the offset directly affects the gain. To achieve optimum performance, several iterations may be required.

#### HARDWARE CALIBRATION

To calibrate the offset and gain of the ADS7804, install the proper resistors and potentiometers as shown in Figure 6a. The calibration range is  $\pm 15$ mV for the offset and  $\pm 60$ mV for the gain.

#### **SOFTWARE CALIBRATION**

To calibrate the offset and gain of the ADS7804 in software, no external resistors are required. See the No Calibration section for details on the effects of the external resistors. Refer to Table V for range of offset and gain errors with and without external resistors.

#### **NO CALIBRATION**

See Figure 6b for circuit connections. The external resistors shown in Figure 6b may not be necessary in some applications. These resistors provide compensation for an internal adjustment of the offset and gain which allows calibration with a single supply. The nominal transfer function of the ADS7804 will be bound by the shaded region seen in Figure 7 with a typical offset of –30mV and a typical gain error of –1.5%. Refer to Table V for range of offset and gain errors with and without external resistors.

|                       | WITH<br>EXTERNAL<br>RESISTORS       | WITHOUT<br>EXTERNAL<br>RESISTORS    | UNITS    |  |  |  |  |  |

|-----------------------|-------------------------------------|-------------------------------------|----------|--|--|--|--|--|

| BPZ                   | −10 < BPZ < 10                      | −45 < BPZ < 5                       | mV       |  |  |  |  |  |

|                       | −2 < BPZ < 2                        | −8 < BPZ < 1                        | LSBs     |  |  |  |  |  |

| Gain                  | -0.5 < error < 0.5                  | -0.6 < error < -0.55                | % of FSR |  |  |  |  |  |

| Error                 | -0.25 < error < 0.25 <sup>(1)</sup> | -0.45 < error < -0.3 <sup>(1)</sup> |          |  |  |  |  |  |

| NOTE: (1) High Grade. |                                     |                                     |          |  |  |  |  |  |

TABLE VII. Bipolar Offset and Gain Errors With and Without External Resistors.

| a) ±10V With Hardware                                 | b) ±10V Without Hardware                                       |

|-------------------------------------------------------|----------------------------------------------------------------|

| Trim                                                  | Trim                                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\pm 10V \bigcirc$ $200\Omega$ $V_{IN}$ AGND1  REF  CAP  AGND2 |

FIGURE 6. Circuit Diagram With and Without External Resistors.

FIGURE 7. Full Scale Transfer Function.

## REFERENCE

The ADS7804 can operate with its internal 2.5V reference or an external reference. By applying an external reference to pin 5, the internal reference can be bypassed. The reference voltage at REF is buffered internally with the output on CAP (pin 4).

The internal reference has an 8 ppm/°C drift (typical) and accounts for approximately 20% of the full scale error (FSE =  $\pm 0.5\%$  for low grade,  $\pm 0.25\%$  for high grade).

#### **REF**

REF (pin 3) is an input for an external reference or the output for the internal 2.5V reference. A  $2.2\mu F$  capacitor should be connected as close to the REF pin as possible. The capacitor and the output resistance of REF create a low pass filter to bandlimit noise on the reference. Using a smaller value capacitor will introduce more noise to the reference degrading the SNR and SINAD. The REF pin should not be used to drive external AC or DC loads.

The range for the external reference is 2.3V to 2.7V and determines the actual LSB size. Increasing the reference voltage will increase the full scale range and the LSB size of the converter which can improve the SNR.

#### CAP

CAP (pin 4) is the output of the internal reference buffer. A  $2.2\mu F$  capacitor should be placed as close to the CAP pin as possible to provide optimum switching currents for the CDAC throughout the conversion cycle and compensation for the output of the internal buffer. Using a capacitor any smaller than  $1\mu F$  can cause the output buffer to oscillate and may not have sufficient charge for the CDAC. Capacitor values larger than  $2.2\mu F$  will have little affect on improving performance.

The output of the buffer is capable of driving up to 2mA of current to a DC load. DC loads requiring more than 2mA of current from the CAP pin will begin to degrade the linearity of the ADS7804. Using an external buffer will allow the internal reference to be used for larger DC loads and AC loads. Do not attempt to directly drive an AC load with the output voltage on CAP. This will cause performance degradation of the converter.

#### LAYOUT

#### **POWER**

For optimum performance, tie the analog and digital power pins to the same +5V power supply and tie the analog and digital grounds together. As noted in the electrical specifications, the ADS7804 uses 90% of its power for the analog circuitry. The ADS7804 should be considered as an analog component.

The +5V power for the A/D should be separate from the +5V used for the system's digital logic. Connecting  $V_{DIG}$  (pin 28) directly to a digital supply can reduce converter performance due to switching noise from the digital logic. For best performance, the +5V supply can be produced from whatever analog supply is used for the rest of the analog signal conditioning. If +12V or +15V supplies are present, a simple +5V regulator can be used. Although it is not suggested, if the digital supply must be used to power the converter, be sure to properly filter the supply. Either using a filtered digital supply or a regulated analog supply, both  $V_{DIG}$  and  $V_{ANA}$  should be tied to the same +5V source.

#### **GROUNDING**

Three ground pins are present on the ADS7804. DGND is the digital supply ground. AGND2 is the analog supply ground. AGND1 is the ground which all analog signals internal to the A/D are referenced. AGND1 is more susceptible to current induced voltage drops and must have the path of least resistance back to the power supply.

All the ground pins of the A/D should be tied to the analog ground plane, separated from the system's digital logic ground, to achieve optimum performance. Both analog and digital ground planes should be tied to the "system" ground as near to the power supplies as possible. This helps to prevent dynamic digital ground currents from modulating the analog ground through a common impedance to power ground.

#### SIGNAL CONDITIONING

The FET switches used for the sample hold on many CMOS A/D converters release a significant amount of charge injection which can cause the driving op amp to oscillate. The FET switch on the ADS7804, compared to the FET switches on other CMOS A/D converters, releases 5%-10% of the charge. There is also a resistive front end which attenuates any charge which is released. The end result is a minimal requirement for the anti-alias filter on the front end. Any op amp sufficient for the signal in an application will be sufficient to drive the ADS7804.

The resistive front end of the ADS7804 also provides a guaranteed  $\pm 25$ V overvoltage protection. In most cases, this eliminates the need for external input protection circuitry.

#### INTERMEDIATE LATCHES

The ADS7804 does have tri-state outputs for the parallel port, but intermediate latches should be used if the bus will be active during conversions. If the bus is not active during conversion, the tri-state outputs can be used to isolate the A/D from other peripherals on the same bus. Tri-state outputs can also be used when the A/D is the only peripheral on the data bus.

Intermediate latches are beneficial on any monolithic A/D converter. The ADS7804 has an internal LSB size of  $610\mu V$ . Transients from fast switching signals on the parallel port, even when the A/D is tri-stated, can be coupled through the substrate to the analog circuitry causing degradation of converter performance. The effects of this phenomenon will be more obvious when using the pin-compatible ADS7805 or any of the other 16-bit converters in the ADS Family. This is due to the smaller internal LSB size of  $38\mu V$ .

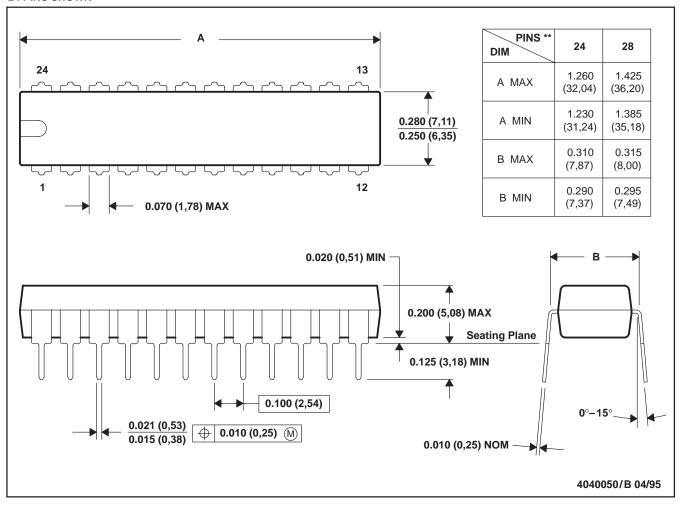

#### NT (R-PDIP-T\*\*)

#### PLASTIC DUAL-IN-LINE PACKAGE

#### **24 PINS SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

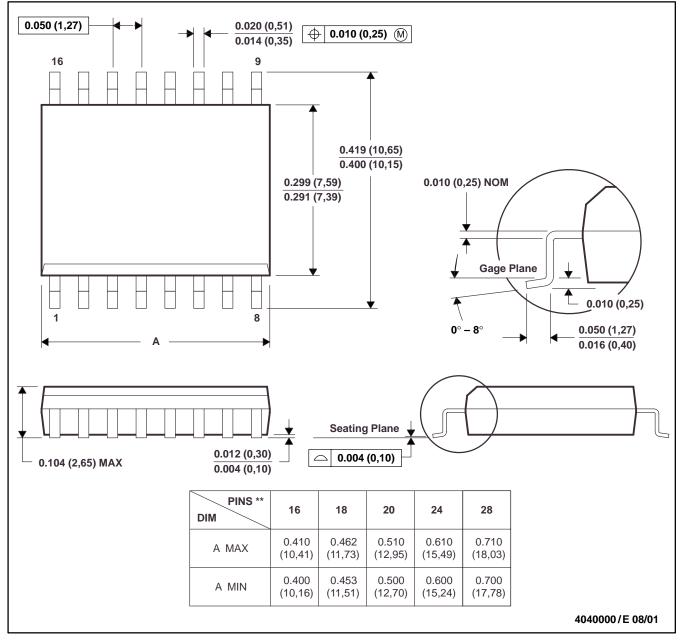

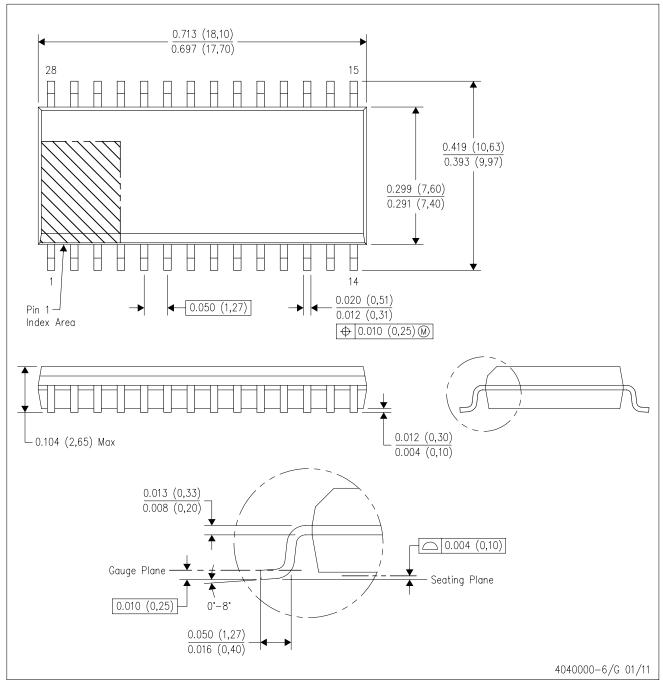

#### DW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### **16 PINS SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013

6-Feb-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| ADS7804U         | ACTIVE | SOIC         | DW                 | 28   | 20             | Green (RoHS<br>& no Sb/Br) | NIPDAU-DCC       | Level-3-260C-168 HR | -40 to 85    | ADS7804U<br>B        | Samples |

| ADS7804U/1K      | ACTIVE | SOIC         | DW                 | 28   | 1000           | Green (RoHS<br>& no Sb/Br) | NIPDAU-DCC       | Level-3-260C-168 HR | -40 to 85    | ADS7804U<br>B        | Samples |

| ADS7804UB        | ACTIVE | SOIC         | DW                 | 28   | 20             | Green (RoHS<br>& no Sb/Br) | NIPDAU-DCC       | Level-3-260C-168 HR | -40 to 85    | ADS7804U<br>B        | Samples |

| ADS7804UG4       | ACTIVE | SOIC         | DW                 | 28   | 20             | Green (RoHS<br>& no Sb/Br) | NIPDAU-DCC       | Level-3-260C-168 HR | -40 to 85    | ADS7804U<br>B        | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

## **PACKAGE OPTION ADDENDUM**

6-Feb-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

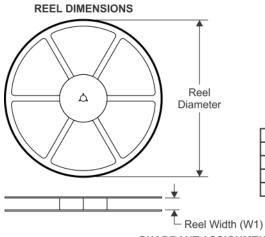

## PACKAGE MATERIALS INFORMATION

www.ti.com 26-Jan-2013

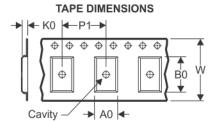

## TAPE AND REEL INFORMATION

|   |    | Dimension designed to accommodate the component width     |

|---|----|-----------------------------------------------------------|

|   |    | Dimension designed to accommodate the component length    |

| K | (0 | Dimension designed to accommodate the component thickness |

| ٧ | Λ  | Overall width of the carrier tape                         |

| F | 21 | Pitch between successive cavity centers                   |

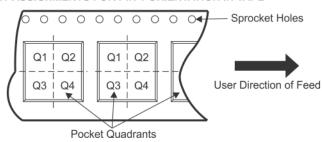

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADS7804U/1K | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Jan-2013

#### \*All dimensions are nominal

| Device      | Package Type | ge Type Package Drawing |    | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-------------|--------------|-------------------------|----|------|-------------|------------|-------------|--|

| ADS7804U/1K | SOIC         | DW                      | 28 | 1000 | 367.0       | 367.0      | 55.0        |  |

DW (R-PDSO-G28)

## PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AE.

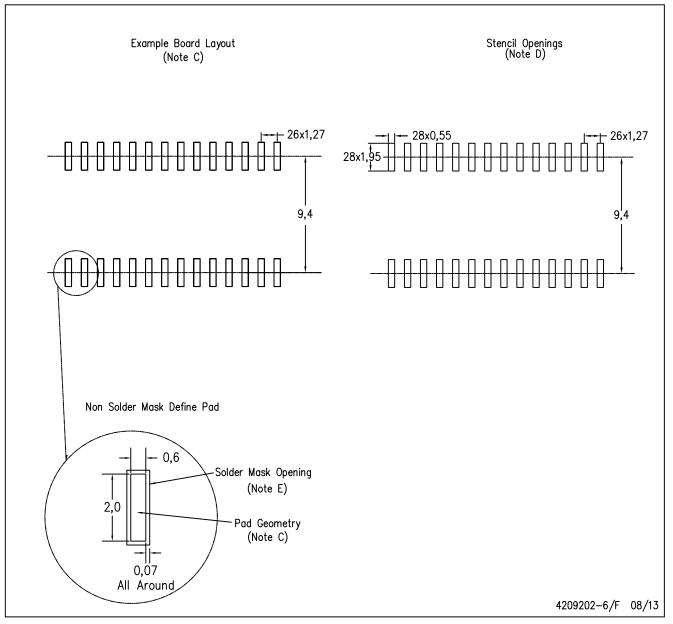

## DW (R-PDSO-G28)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Refer to IPC7351 for alternate board design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated