## 10-Bit 60 MSPS A/D Converter

# AD9020

#### FEATURES

Monolithic 10-Bit/60 MSPS Converter TTL Outputs Bipolar (±1.75 V) Analog Input 56 dB SNR @ 2.3 MHz Input Low (45 pF) Input Capacitance MIL-STD-883-Compliant Versions Available

#### APPLICATIONS

Digital Oscilloscopes Medical Imaging Professional Video Radar Warning/Guidance Systems Infrared Systems

#### **GENERAL DESCRIPTION**

The AD9020 A/D converter is a 10-bit monolithic converter capable of word rates of 60 MSPS and above. Innovative architecture using 512 input comparators instead of the traditional 1024 required by other flash converters reduces input capacitance and improves linearity.

Encode and outputs are TTL-compatible, making the AD9020 an ideal candidate for use in low power systems. An overflow bit is provided to indicate analog input signals greater than  $+V_{\text{SENSE}}$ .

Voltage sense lines are provided to insure accurate driving of the  $\pm V_{REF}$  voltages applied to the units. Quarter-point taps on the resistor ladder help optimize the integral linearity of the unit.

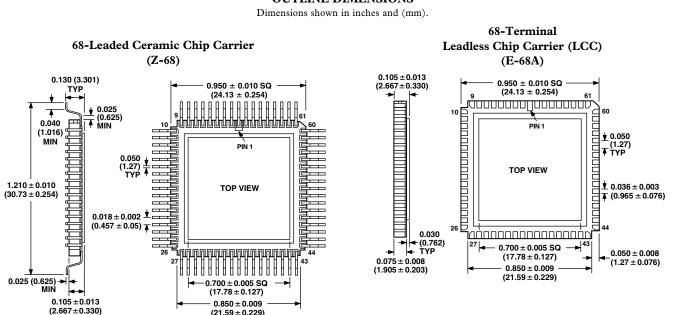

Either 68-pin ceramic leaded (gull wing) packages or ceramic LCCs are available and are specifically designed for low thermal impedances. Two performance grades for temperatures of both  $0^{\circ}$ C to  $70^{\circ}$ C and  $-55^{\circ}$ C to  $+125^{\circ}$ C ranges are offered to allow the user to select the linearity best suited for each application. Dynamic performance is fully characterized and production tested at  $25^{\circ}$ C. MIL-STD-883 units are available.

The AD9020 A/D Converter is available in versions compliant with MIL-STD-883. Refer to the Analog Devices Military Products Databook or current AD9020/883B data sheet for detailed specifications.

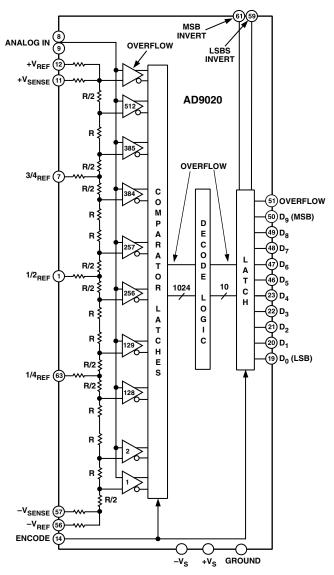

#### FUNCTIONAL BLOCK DIAGRAM

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2001

# AD9020-SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| +V <sub>s</sub>                                       |

|-------------------------------------------------------|

| -V <sub>S</sub> 6 V                                   |

| ANALOG IN                                             |

| $+V_{REF}, -V_{REF}, 3/4_{REF}, 1/2_{REF}, 1/4_{REF}$ |

| +V <sub>REF</sub> to $-V_{REF}$                       |

| DIGITAL INPUTS0.5 V to $+V_s$                         |

| $3/4_{\text{REF}}$ , $1/2_{\text{REF}}$ , $1/4_{\text{REF}}$ Current |

|----------------------------------------------------------------------|

| Operating Temperature                                                |

| AD9020JE/KE/JZ/KZ0°C to 70°C                                         |

| Storage Temperature65°C to +150°C                                    |

| Maximum Junction Temperature <sup>2</sup> 150°C                      |

| Lead Soldering Temp (10 sec) 300°C                                   |

|                                                                      |

### **ELECTRICAL CHARACTERISTICS** ( $\pm V_s = \pm 5 V$ ; $\pm V_{SENSE} = \pm 1.75 V$ ; ENCODE = 40 MSPS unless otherwise noted)

|                                                                               | Test         |        | AD9020JE/JZ |         |          | AD9020KE/KZ |         |          |                    |

|-------------------------------------------------------------------------------|--------------|--------|-------------|---------|----------|-------------|---------|----------|--------------------|

| Parameter (Conditions)                                                        | Temp         | Level  | Min         | Тур     | Max      | Min         | Тур     | Max      | Unit               |

| RESOLUTION                                                                    |              |        | 10          |         |          | 10          |         |          | Bits               |

| DC ACCURACY <sup>3</sup>                                                      |              |        |             |         |          |             |         |          |                    |

| Differential Nonlinearity                                                     | 25°C         | I      |             | 1.0     | 1.25     |             | 0.75    | 1.0      | LSB                |

|                                                                               | Full         | VI     |             |         | 1.5      |             |         | 1.25     | LSB                |

| Integral Nonlinearity                                                         | 25°C         | I      |             | 1.25    | 2.75     |             | 1.0     | 2.25     | LSB                |

|                                                                               | Full         | VI     |             |         | 3.0      |             |         | 2.50     | LSB                |

| No Missing Codes                                                              | Full         | VI     |             |         |          |             | Guara   |          |                    |

| ANALOG INPUT                                                                  |              |        |             |         |          |             |         |          |                    |

| Input Bias Current <sup>4</sup>                                               | 25°C         | I      |             | 0.4     | 1.0      |             | 0.4     | 1.0      | mA                 |

|                                                                               | Full         | VI     |             |         | 2.0      |             |         | 2.0      | mA                 |

| Input Resistance                                                              | 25°C         | I      | 2.0         | 7.0     |          | 2.0         | 7.0     |          | kΩ                 |

| Input Capacitance <sup>4</sup>                                                | 25°C         | v      |             | 45      |          |             | 45      |          | pF                 |

| Analog Bandwidth                                                              | 25°C         | V      |             | 175     |          |             | 175     |          | MHz                |

| REFERENCE INPUT                                                               |              |        |             | 1.5     |          |             | 1.5     |          |                    |

| Reference Ladder Resistance                                                   | 25°C         | I      | 22          | 37      | 56       | 22          | 37      | 56       | Ω                  |

| Reference Lauder Resistance                                                   | Full         | VI     | 14          | 51      | 50<br>66 | 14          | 51      | 50<br>66 | Ω                  |

| Ladder Tempco                                                                 | Full         | V      | 14          | 0.1     | 00       | 14          | 0.1     | 00       | $\Omega/^{\circ}C$ |

| Reference Ladder Offset                                                       | 1'un         | v      |             | 0.1     |          |             | 0.1     |          | 32/ C              |

| Top of Ladder                                                                 | 25°C         | I      |             | 45      | 90       |             | 45      | 90       | mV                 |

| T op of Ladder                                                                | Full         | VI     |             | 47      | 90<br>90 |             | 47      | 90<br>90 | mV                 |

| Bottom of Ladder                                                              | 25°C         | I      |             | 45      | 90<br>90 |             | 45      | 90<br>90 | mV                 |

| Bottom of Ladder                                                              | Full         | VI     |             | 45      | 90<br>90 |             | 4)      | 90<br>90 | mV                 |

| Offset Drift Coefficient                                                      | Full         | V      |             | 50      | 90       |             | 50      | 90       | μV/°C              |

| SWITCHING PERFORMANCE                                                         |              |        |             |         |          |             |         |          |                    |

| Conversion Rate                                                               | 25°C         | T      | 60          |         |          | 60          |         |          | MSPS               |

|                                                                               | 25°C<br>25°C | I<br>V | 00          | 1       |          | 00          | 1       |          |                    |

| Aperture Delay $(t_A)$                                                        | 25°C<br>25°C | VV     |             | 1<br>5  |          |             | 1<br>5  |          | ns                 |

| Aperture Uncertainty (Jitter)                                                 | 25°C<br>25°C |        | 6           | 5<br>10 | 12       | 6           | 5<br>10 | 12       | ps, rms            |

| Output Delay (t <sub>OD</sub> ) <sup>5</sup><br>Output Time Skew <sup>5</sup> | 25°C<br>25°C | I<br>I | 6           | 3       | 13<br>5  | 6           | 3       | 13<br>5  | ns                 |

|                                                                               | 25°C         |        |             | 3       | 5        |             | 3       | 2        | ns                 |

| DYNAMIC PERFORMANCE                                                           |              |        |             |         |          |             |         |          |                    |

| Transient Response                                                            | 25°C         | V      |             | 10      |          |             | 10      |          | ns                 |

| Overvoltage Recovery Time                                                     | 25°C         | V      |             | 10      |          |             | 10      |          | ns                 |

| Effective Number of Bits (ENOB)                                               |              |        |             |         |          |             |         |          |                    |

| $f_{IN} = 2.3 \text{ MHz}$                                                    | 25°C         | I      | 7.9         | 9.0     |          | 7.9         | 9.0     |          | Bits               |

| $f_{IN} = 10.3 \text{ MHz}$                                                   | 25°C         | IV     | 7.6         | 8.4     |          | 7.6         | 8.4     |          | Bits               |

| $f_{IN} = 15.3 \text{ MHz}$                                                   | 25°C         | IV     | 7.2         | 8.0     |          | 7.2         | 8.0     |          | Bits               |

| Signal-to-Noise Ratio <sup>6</sup>                                            |              |        |             |         |          |             |         |          |                    |

| $f_{IN} = 2.3 \text{ MHz}$                                                    | 25°C         | I      | 49.5        | 56      |          | 49.5        | 56      |          | dB                 |

| $f_{IN} = 10.3 \text{ MHz}$                                                   | 25°C         | I      | 47.5        | 53      |          | 47.5        | 53      |          | dB                 |

| $f_{IN} = 15.3 \text{ MHz}$                                                   | 25°C         | I      | 45.5        | 50      |          | 45.5        | 50      |          | dB                 |

| Signal-to-Noise Ratio <sup>6</sup>                                            |              |        |             |         |          |             |         |          |                    |

| (Without Harmonics)                                                           |              |        |             |         |          |             |         |          |                    |

| $f_{IN} = 2.3 \text{ MHz}$                                                    | 25°C         | I      | 49.5        | 56      |          | 49.5        | 56      |          | dB                 |

| $f_{IN} = 10.3 \text{ MHz}$                                                   | 25°C         | I      | 49.5        | 54      |          | 49.5        | 54      |          | dB                 |

| $f_{IN} = 15.3 \text{ MHz}$                                                   | 25°C         | I      | 48          | 52      |          | 48          | 52      |          | dB                 |

|                                               |        | Test  | AD9020JE/JZ |     | AD9020KE/KZ |      |     |     |        |

|-----------------------------------------------|--------|-------|-------------|-----|-------------|------|-----|-----|--------|

| Parameter (Conditions)                        | Temp   | Level | Min         | Тур | Max         | Min  | Тур | Max | Unit   |

| DYNAMIC PERFORMANCE (cont                     | inued) |       |             |     |             |      |     |     |        |

| Harmonic Distortion                           |        |       |             |     |             |      |     |     |        |

| $f_{IN} = 2.3 \text{ MHz}$                    | 25°C   | I     | 54.5        | 67  |             | 54.5 | 67  |     | dBc    |

| $f_{IN} = 10.3 \text{ MHz}$                   | 25°C   | I     | 48.5        | 59  |             | 48.5 | 59  |     | dBc    |

| $f_{IN} = 15.3 \text{ MHz}$                   | 25°C   | I     | 46.5        | 53  |             | 46.5 | 53  |     | dBc    |

| Two-Tone Intermodulation                      |        |       |             |     |             |      |     |     |        |

| Distortion Rejection <sup>7</sup>             | 25°C   | V     |             | 70  |             |      | 70  |     | dBc    |

| Differential Phase                            | 25°C   | V     |             | 0.5 |             |      | 0.5 |     | Degree |

| Differential Gain                             | 25°C   | V     |             | 1   |             |      | 1   |     | %      |

| ENCODE INPUT                                  |        |       |             |     |             |      |     |     |        |

| Logic "1" Voltage                             | Full   | VI    | 2.0         |     |             | 2.0  |     |     | V      |

| Logic "0" Voltage                             | Full   | VI    |             |     | 0.8         |      |     | 0.8 | V      |

| Logic "1" Current                             | Full   | VI    |             |     | 500         |      |     | 500 | μA     |

| Logic "0" Current                             | Full   | VI    |             |     | 800         |      |     | 800 | μA     |

| Input Capacitance                             | 25°C   | V     |             | 5   |             |      | 5   |     | pF     |

| Pulsewidth (High)                             | 25°C   | I     | 6           |     |             | 6    |     |     | ns     |

| Pulsewidth (Low)                              | 25°C   | I     | 6           |     |             | 6    |     |     | ns     |

| DIGITAL OUTPUTS                               |        |       |             |     |             |      |     |     |        |

| Logic "1" Voltage ( $I_{OH} = 2 \text{ mA}$ ) | Full   | VI    | 2.4         |     |             | 2.4  |     |     | V      |

| Logic "0" Voltage ( $I_{OL} = 6 \text{ mA}$ ) | Full   | VI    |             |     | 0.4         |      |     |     | V      |

| POWER SUPPLY                                  |        |       |             |     |             |      |     |     |        |

| +V <sub>s</sub> Supply Current                | 25°C   | I     |             | 440 | 530         |      | 440 | 530 | mA     |

|                                               | Full   | VI    |             |     | 542         |      |     | 542 | mA     |

| -V <sub>S</sub> Supply Current                | 25°C   | I     |             | 140 | 170         |      | 140 | 170 | mA     |

| 5 " <b>F J -</b> "                            | Full   | VI    |             |     | 177         |      |     | 177 | mA     |

| Power Dissipation                             | 25°C   | I     |             | 2.8 | 3.3         |      | 2.8 | 3.3 | W      |

| ·····                                         | Full   | VI    |             |     | 3.4         |      |     | 3.4 | W      |

| Power Supply Rejection                        |        |       |             |     |             |      |     |     |        |

| Ratio (PSRR) <sup>8</sup>                     | Full   | VI    |             | 6   | 10          |      | 6   | 10  | mV/V   |

NOTES

<sup>1</sup>Absolute maximum ratings are limiting values to be applied individually, and beyond which the service ability of the circuit may be impaired. Functional operability is not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

<sup>2</sup>Typical thermal impedances (part soldered onto board): 68-pin leaded ceramic chip carrier:  $\theta_{JC} = 1^{\circ}C/W$ ;  $\theta_{JA} = 17^{\circ}C/W$  (no air flow);  $\theta_{JA} = 15^{\circ}C/W$  (air flow = 500 LFM). 68-pin ceramic LCC:  $\theta_{JC} = 2.6^{\circ}C/W$ ;  $\theta_{JA} = 15^{\circ}C/W$  (no air flow);  $\theta_{JA} = 13^{\circ}C/W$  (air flow = 500 LFM). <sup>3</sup>3/4<sub>REF</sub>, 1/2<sub>REF</sub>, and 1/4<sub>REF</sub> reference ladder taps are driven from dc sources at +0.875 V, 0 V, and -0.875 V, respectively. Accuracy of the overflow comparator is not tested and not included in linearity specifications.

<sup>4</sup>Measured with ANALOG IN =  $+V_{\text{SENSE}}$ .

<sup>5</sup>Output delay measured as worst-case time from 50% point of the rising edge of ENCODE to 50% point of the slowest rising or falling edge of D<sub>0</sub>-D<sub>9</sub>. Output skew measured as worst-case difference in output delay among  $D_0-D_9$ .

<sup>6</sup>RMS signal to rms noise with analog input signal 1 dB below full scale at specified frequency.

<sup>7</sup>Intermodulation measured with analog input frequencies of 2.3 MHz and 3.0 MHz at 7 dB below full scale.

$^{8}$ Measured as the ratio of the worst-case change in transition voltage of a single comparator for a 5% change in +V<sub>S</sub> or -V<sub>S</sub>.

Specifications subject to change without notice.

#### **EXPLANATION OF TEST LEVELS**

Test Level

- I 100% production tested.

- II 100% production tested at 25°C, and sample tested at specified temperatures.

- III Sample tested only.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI All devices are 100% production tested at 25°C. 100% production tested at temperature extremes for extended temperature devices; sample tested at temperature extremes for commercial/industrial devices.

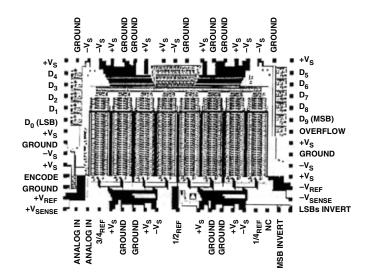

#### DIE LAYOUT AND MECHANICAL INFORMATION

| Die Dimensions $\dots \dots \dots$ |

|------------------------------------------------------------------------------------------------------------------------------------|

| Pad Dimensions $\dots \dots \dots$ |

| Metalization                                                                                                                       |

| Backing None                                                                                                                       |

| Substrate PotentialV <sub>S</sub>                                                                                                  |

| Passivation Nitride                                                                                                                |

#### **ORDERING GUIDE**

| Device | Temperature<br>Range                                                                                                                                | Description                                                                                                                                                                                                                          | Package<br>Option*                     |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|        | 0°C to 70°C<br>0°C to 70°C<br>0°C to 70°C<br>0°C to 70°C<br>-55°C to +125°C<br>-55°C to +125°C<br>-55°C to +125°C<br>-55°C to +125°C<br>0°C to 70°C | 68-Lead Leaded Ceramic<br>68-Terminal Ceramic LCC<br>68-Lead Leaded Ceramic<br>68-Terminal Ceramic LCC<br>68-Lead Leaded Ceramic<br>68-Terminal Ceramic LCC<br>68-Lead Leaded Ceramic<br>68-Terminal Ceramic LCC<br>Evaluation Board | Z-68<br>E-68A<br>Z-68<br>E-68A<br>Z-68 |

\*E = Ceramic Leadless Chip Carrier; Z = Ceramic Leaded Chip Carrier.

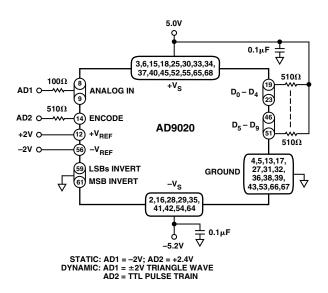

Figure 1. Burn-In Circuit

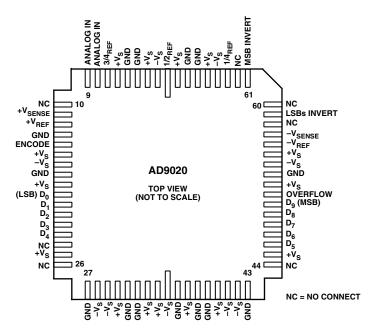

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin No.                                                     | Name                   | Function                                                                                                                        |

|-------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1                                                           | $1/2_{\text{REF}}$     | Midpoint of internal reference ladder.                                                                                          |

| 2, 16, 28, 29, 35, 41, 42,<br>54, 64                        | $-V_S$                 | Negative supply voltage; nominally $-5.0 \text{ V} \pm 5\%$ .                                                                   |

| 3, 6, 15, 18, 25, 30, 33, 34,<br>37, 40, 45, 52, 55, 65, 68 | +V <sub>S</sub>        | Positive supply voltage; nominally 5 V $\pm$ 5%.                                                                                |

| 4, 5, 13, 17, 27, 31, 32,<br>36, 38, 39, 43, 53, 66, 67     | GROUND                 | All ground pins should be connected together and to low impedance ground plane.                                                 |

| 7                                                           | $3/4_{\text{REF}}$     | Three-quarter point of internal reference ladder.                                                                               |

| 8, 9                                                        | ANALOG IN              | Analog input; nominally between $\pm 1.75$ V.                                                                                   |

| 11                                                          | $+V_{SENSE}$           | Voltage sense line to most positive point on internal resistor ladder.<br>Normally 1.75 V.                                      |

| 12                                                          | $+V_{REF}$             | Voltage force connection for top of internal reference ladder. Normally driven to provide 1.75 V at $+V_{SENSE}$ .              |

| 14                                                          | ENCODE                 | TTL-compatible convert command used to begin digitizing process.                                                                |

| 19–23, 46–50                                                | $D_0 - D_4, D_5 - D_9$ | TTL-compatible digital output data.                                                                                             |

| 51                                                          | OVERFLOW               | TTL-compatible output indicating ANALOG IN > $+V_{SENSE}$ .                                                                     |

| 56                                                          | -V <sub>REF</sub>      | Voltage force connection for bottom of internal reference ladder. Normally driven to provide $-1.75$ V at $-V_{\text{SENSE}}$ . |

| 57                                                          | -V <sub>SENSE</sub>    | Voltage sense line to most negative point on internal resistor ladder.<br>Normally –1.75 V.                                     |

| 59                                                          | LSBs INVERT            | Normally grounded. When connected to $+V_S$ , lower order bits $(D_0-D_8)$ are inverted.                                        |

| 61                                                          | MSB INVERT             | Normally grounded. When connected to $+V_s$ , most significant bit (MSB; D <sub>9</sub> ) is inverted.                          |

| 63                                                          | $1/4_{REF}$            | One-quarter point of internal reference ladder.                                                                                 |

#### THEORY OF OPERATION

Refer to the AD9020 block diagram. As shown, the AD9020 uses a modified "flash," or parallel, A/D architecture. The analog input range is determined by an external voltage reference (+V<sub>REF</sub> and -V<sub>REF</sub>), nominally ±1.75 V. An internal resistor ladder divides this reference into 512 steps, each representing two quantization levels. Taps along the resistor ladder ( $1/4_{REF}$ ,  $1/2_{REF}$  and  $3/4_{REF}$ ) are provided to optimize linearity. Rated performance is achieved by driving these points at 1/4, 1/2, and 3/4, respectively, of the voltage reference range.

The A/D conversion for the nine most significant bits (MSBs) is performed by 512 comparators. The value of the least significant bit (LSB) is determined by a unique interpolation scheme between adjacent comparators. The decoding logic processes the comparator outputs and provides a 10-bit code to the output stage of the converter.

Flash architecture has an advantage over other A/D architectures because conversion occurs in one step. This means the performance of the converter is primarily limited by the speed and matching of the individual comparators. In the AD9020, an innovative interpolation scheme takes advantage of flash architecture but minimizes the input capacitance, power and device count usually associated with that method of conversion.

These advantages occur by using only half the normal number of input comparator cells to accomplish the conversion. In addition, a proprietary decoding scheme minimizes error codes. Input control pins allow the user to select from among Binary, Inverted Binary, Two's Complement and Inverted Two's Complement coding (see Table I).

#### APPLICATIONS

Many of the specifications used to describe analog/digital converters have evolved from system performance requirements in these applications. Different systems emphasize particular specifications, depending on how the part is used. The following applications highlight some of the specifications and features that make the AD9020 attractive in these systems.

#### Wideband Receivers

Radar and communication receivers (baseband and direct IF digitization), ultrasound medical imaging, signal intelligence and spectral analysis all place stringent ac performance requirements on analog-to-digital converters (ADCs).

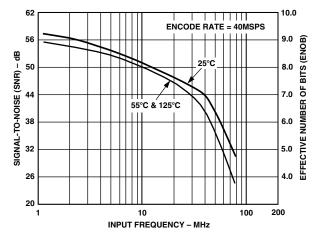

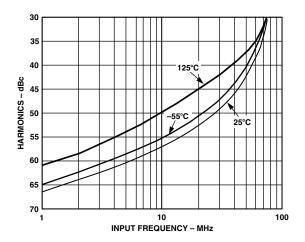

Frequency domain characterization of the AD9020 provides signal-to-noise ratio (SNR) and harmonic distortion data to simplify selection of the ADC.

Receiver sensitivity is limited by the Signal-to-Noise Ratio of the system. The SNR for an ADC is measured in the frequency domain and calculated with a Fast Fourier Transform (FFT). The SNR equals the ratio of the fundamental component of the signal (rms amplitude) to the rms value of the noise. The noise is the sum of all other spectral components, including harmonic distortion, but excluding dc.

Good receiver design minimizes the level of spurious signals in the system. Spurious signals developed in the ADC are the result of imperfections (nonlinearities, delay mismatch, varying input impedance, etc.) in the device transfer function. In the ADC, these spurious signals appear as Harmonic Distortion. Harmonic Distortion is also measured with an FFT and is specified as the ratio of the fundamental component of the signal (rms amplitude) to the rms value of the worst-case harmonic (usually the 2nd or 3rd).

*Two-Tone Intermodulation Distortion (IMD)* is a frequently cited specification in receiver design. In narrow-band receivers, third-order IMD products result in spurious signals in the passband of the receiver. Like mixers and amplifiers, the ADC is characterized with two, equal-amplitude, pure input frequencies. The IMD equals the ratio of the power of either of the two input signals to the power of the strongest third-order IMD signal. Unlike mixers and amplifiers, the IMD does not always behave as it does in linear devices (reduced input levels do not result in predictable reductions in IMD).

Performance graphs provide typical harmonic and SNR data for the AD9020 for increasing analog input frequencies. In choosing an A/D converter, always look at the dynamic range for the analog input frequency of interest. The AD9020 specifications provide guaranteed minimum limits at three analog test frequencies.

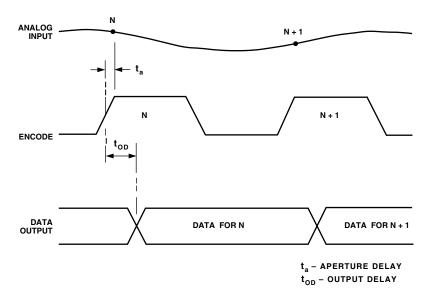

Aperture Delay is the delay between the rising edge of the ENCODE command and the instant at which the analog input is sampled. Many systems require simultaneous sampling of more than one analog input signal with multiple ADCs. In these situations, timing is critical and the absolute value of the aperture delay is not as critical as the matching between devices.

Aperture Uncertainty, or jitter, is the sample-to-sample variation in aperture delay. This is especially important when sampling high slew rate signals in wide bandwidth systems. Aperture uncertainty is one of the factors that degrade dynamic performance as the analog input frequency is increased.

#### **Digitizing Oscilloscopes**

Oscilloscopes provide amplitude information about an observed waveform with respect to time. Digitizing oscilloscopes must accurately sample this signal, without distorting the information to be displayed.

One figure of merit for the ADC in these applications is *Effective Number of Bits (ENOBs)*. ENOB is calculated with a sine wave curve fit and equals:

$ENOB = N - LOG_2$  [Error (measured)/Error (ideal)]

N is the resolution (number of bits) of the ADC. The measured error is the actual rms error calculated from the converter outputs with a pure sine wave input.

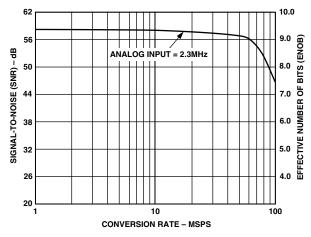

The Analog Bandwidth of the converter is the analog input frequency at which the spectral power of the fundamental signal is reduced 3 dB from its low frequency value. The analog bandwidth is a good indicator of a converter's stewing capabilities. The *Maximum Conversion Rate* is defined as the encode rate at which the SNR for the lowest analog signal test frequency tested drops by no more than 3 dB below the guaranteed limit.

#### Imaging

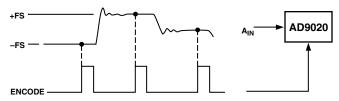

Both visible and infrared imaging systems require similar characteristics from ADCs. The signal input (from a CCD camera, or multiplexer) is a time division multiplexed signal consisting of a series of pulses whose amplitude varies in direct proportion to the intensity of the radiation detected at the sensor. These varying levels are then digitized by applying encode commands at the correct times, as shown in Figure 2.

Figure 2. Imaging Application Using AD9020

The actual resolution of the converter is limited by the thermal and quantization noise of the ADC. The low frequency test for SNR or ENOB is a good measure of the noise of the AD9020. At this frequency, the static errors in the ADC determine the useful dynamic range of the ADC.

Although the signal being sampled does not have a significant slew rate, this does not imply dynamic performance is not important. The *Transient Response and Overvoltage Recovery Time* specifications ensure that the ADC can track full-scale changes in the analog input sufficiently fast to capture a valid sample.

*Transient Response* is the time required for the AD9020 to achieve full accuracy when a step function is applied. *Overvoltage Recovery Time* is the time required for the AD9020 to recover to full accuracy after an analog input signal 150% of full scale is reduced to the full-scale range of the converter.

#### **Professional Video**

Digital Signal Processing (DSP) is now common in television production. Modern studios rely on digitized video to create state-of-the-art special effects. Video instrumentation also requires high resolution ADCs for studio quality measurement and frame storage.

The AD9020 provides sufficient resolution for these demanding applications. Conversion speed, dynamic performance and analog bandwidth are suitable for digitizing both composite and RGB video sources.

#### USING THE AD9020 Voltage References

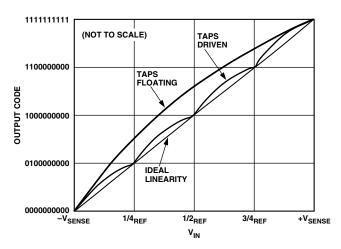

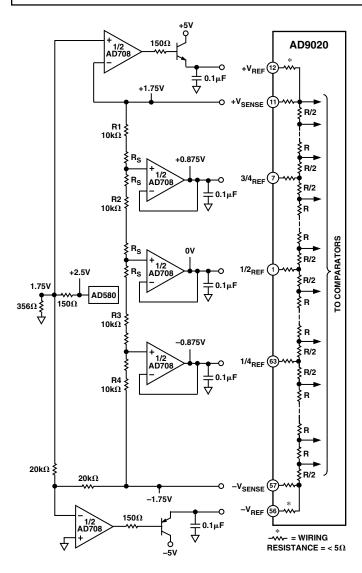

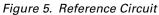

The AD9020 requires that the user provide two voltage references:  $+V_{REF}$  and  $-V_{REF}$ . These two voltages are applied across an internal resistor ladder (nominally 37  $\Omega$ ) and set the analog input voltage range of the converter. The voltage references should be driven from a stable, low impedance source. In addition to these two references, three evenly spaced taps on the resistor ladder ( $1/4_{REF}$ ,  $1/2_{REF}$ ,  $3/4_{REF}$ ) are available. Providing a reference to these quarter points on the resistor ladder wil improve the integral linearity of the converter and improve ac performance. (ac and dc specifications are tested while driving the quarter points at the indicated levels.) Figure 3 is not intended to show the transfer function of the ADC, but illustrates how the linearity of the ladder.

Figure 3. Effect of Reference Taps on Linearity

Resistance between the reference connections and the taps of the first and last comparators causes offset errors. These errors, called "top and bottom of the ladder offsets," can be nulled by using the voltage sense lines,  $+V_{\text{SENSE}}$  and  $-V_{\text{SENSE}}$ , to adjust the reference voltages. Current through the sense lines should be limited to less than 100  $\mu$ A. Excessive current drawn through the voltage sense lines will affect the accuracy of the sense line voltage.

Figure 5 shows a reference circuit that nulls out the offset errors using two op amps, and provides appropriate voltage references to the quarter-point taps. Feedback from the sense lines causes the op amps to compensate for the offset errors. The two transistors limit the amount of current drawn directly from the op amps; resistors at the base connections stabilize their operation. The 10 k $\Omega$  resistors (R1–R4) between the voltage sense lines form an external resistor ladder; the quarter point voltages are taken off this external ladder and buffered by an op amp. The actual values of resistors R1–R4 are not critical, but they should match well and be large enough ( $\geq$ 10 k $\Omega$ ) to limit the amount of current drawn from the voltage sense lines.

The select resistors  $(R_S)$  shown in the schematic (each pair can be a potentiometer) are chosen to adjust the quarter-point voltage references, but are not necessary if R1–R4 match within 0.05%.

An alternative approach for defining the quarter-point references of the resistor ladder is to evaluate the integral linearity error of an individual device, and adjust the voltage at the quarter-points to minimize this error. This may improve the low frequency ac performance of the converter.

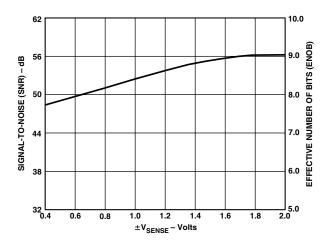

Performance of the AD9020 has been optimized with an analog input voltage of  $\pm 1.75$  V (as measured at  $\pm V_{SENSE}$ ). If the analog input range is reduced below these values, relatively larger differential nonlinearity errors may result because of comparator mismatches. As shown in Figure 4, performance of the converter is a function of  $\pm V_{SENSE}$ .

Figure 4. SNR and ENOB vs. Reference Voltage

Applying a voltage greater than 4 V across the internal resistor ladder will cause current densities to exceed rated values, and may cause permanent damage to the AD9020. The design of the reference circuit should limit the voltage available to the references.

#### **Analog Input Signal**

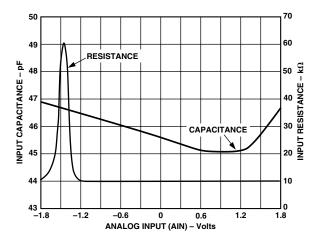

The signal applied to ANALOG IN drives the inputs of 512 parallel comparator cells (see Figure 6). This connection typically has an input resistance of 7 k $\Omega$ , and input capacitance of 45 pF. The input capacitance is nearly constant over the analog input voltage range, as shown in the graph that illustrates that characteristic.

The analog input signal should be driven from a low-distortion, low-noise amplifier. A good choice is the AD9617, a wide bandwidth, monolithic operational amplifier with excellent ac and dc performance. The input capacitance should be isolated by a small series resistor ( $24 \Omega$  for the AD9617) to improve the ac performance of the amplifier (see Figure 14).

Figure 6. Equivalent Analog Input

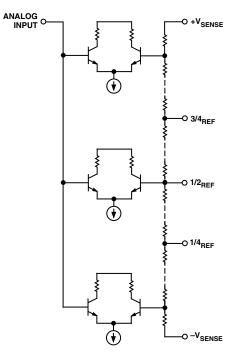

Figure 7. Equivalent Digital Outputs

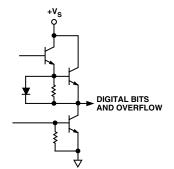

Figure 8. Equivalent Encode Circuit

Figure 9. Timing Diagram

#### Timing

In the AD9020, the rising edge of the ENCODE signal triggers the A/D conversion by latching the comparators. (See Figure 9.)

The ENCODE is TTL/CMOS-compatible and should be driven from a low jitter (phase noise) source. Jitter on the ENCODE signal will raise the noise floor of the converter. Fast, clean edges will reduce the jitter in the signal and allow optimum ac performance. Locking the system clock to a crystal oscillator also helps reduce jitter. The AD9020 is designed to operate with a 50% duty cycle; small (10%) variations in duty cycle should not degrade performance.

#### Data Format

The format of the output data  $(D_0-D_9)$  is controlled by the MSB INVERT and LSBs INVERT pins. These inputs are dc control inputs, and should be connected to GROUND or +V<sub>S</sub>. Table I gives information to choose from among Binary, Inverted Binary, Two's Complement and Inverted Two's Complement coding.

The OVERFLOW output is an indication that the analog input signal has exceeded the voltage at  $+V_{SENSE}$ . The accuracy of the overflow transition voltage and output delay are not tested or included in the data sheet limits. Performance of the overflow indicator is dependent on circuit layout and slew rate of the encode signal. The operation of this function does not affect the other data bits (D<sub>0</sub>-D<sub>9</sub>). It is not recommended for applications requiring a critical measure of the analog input voltage.

#### Layout and Power Supplies

Proper layout of high speed circuits is always critical but particularly important when both analog and digital signals are involved.

Analog signal paths should be kept as short as possible and be properly terminated to avoid reflections. The analog input voltage and the voltage references should be kept away from digital signal paths; this reduces the amount of digital switching noise that is capacitively coupled into the analog section of the circuit. Digital signal paths should also be kept short, and run lengths should be matched to avoid propagation delay mismatch.

In high-speed circuits, layout of the ground circuit is a critical factor. A single, low impedance ground plane, on the component side of the board, will reduce noise on the circuit ground. Power supplies should be capacitively coupled to the ground plane to reduce noise in the circuit. Multilayer boards allow designers to lay out signal traces without interrupting the ground plane and provide low impedance power planes.

It is especially important to maintain the continuity of the ground plane under and around the AD9020. In systems with dedicated digital and analog grounds, all grounds of the AD9020 should be connected to the analog ground plane.

The power supplies (+V<sub>S</sub> and  $-V_S$ ) of the AD9020 should be isolated from the supplies used for external devices; this further reduces the amount of noise coupled into the A/D converter. Sockets limit the dynamic performance and should be used only for prototypes or evaluation—PCK Elastomerics Part # CCS-68-55 is recommended for the LCC package.

An evaluation board is available to aid designers and provide a suggested layout.

Figure 10. SNR and ENOB vs. Input Frequency

Figure 12. SNR and ENOB vs. Conversion Rate

Figure 11. Harmonics vs. Input Frequency

Figure 13. Input Capacitance/Resistance vs. Input Voltage

| Table I. | Truth | Table |

|----------|-------|-------|

|----------|-------|-------|

|              |                                      | Offset l                                | Binary                                      | Two's Complement                        |                                             |  |  |

|--------------|--------------------------------------|-----------------------------------------|---------------------------------------------|-----------------------------------------|---------------------------------------------|--|--|

| Step         | Range<br>0 = -1.75 V<br>FS = +1.75 V | True<br>MSB INV = "0"<br>LSBs INV = "0" | Inverted<br>MSB INV = "1"<br>LSBs INV = "1" | True<br>MSB INV = "1"<br>LSBs INV = "0" | Inverted<br>MSB INV = "0"<br>LSBs INV = "1" |  |  |

| 1024         | > +1.7500                            | (1)111111111                            | (1)000000000                                | (1)011111111                            | (1)100000000                                |  |  |

| 1023<br>1022 | +1.7466<br>+1.7432                   | 1111111111<br>1111111110                | 0000000000<br>0000000001                    | 0111111111<br>0111111110                | $1000000000 \\ 1000000001$                  |  |  |

| •            | •                                    | •                                       | •                                           | •                                       | •                                           |  |  |

| •            | •                                    | •                                       | •                                           | •                                       | •                                           |  |  |

| •            | •                                    | •                                       | •                                           | •                                       | •                                           |  |  |

| 512          | +0.0034                              | 100000000                               | 0111111111                                  | 000000000                               | 1111111111                                  |  |  |

| 511          | 0.000                                | 0111111111                              | 100000000                                   | 1111111111                              | 0000000000                                  |  |  |

| 510          | -0.0034                              | 0111111110                              | 100000001                                   | 1111111110                              | 000000001                                   |  |  |

| •            | •                                    | •                                       | •                                           | •                                       | •                                           |  |  |

| •            | •                                    | •                                       | •                                           | •                                       | •                                           |  |  |

| •            | •                                    | •                                       | •                                           | •                                       | •                                           |  |  |

| 02           | -1.7432                              | 000000010                               | 1111111101                                  | 100000010                               | 0111111101                                  |  |  |

| 01           | -1.7466                              | 000000001                               | 1111111110                                  | 100000001                               | 0111111110                                  |  |  |

| 00           | <-1.7466                             | 0000000000                              | 1111111111                                  | 100000000                               | 0111111111                                  |  |  |

The overflow bit is always 0 except where noted in parentheses (). MSB INVERT and LSBs INVERT are considered dc controls.

#### REV. C

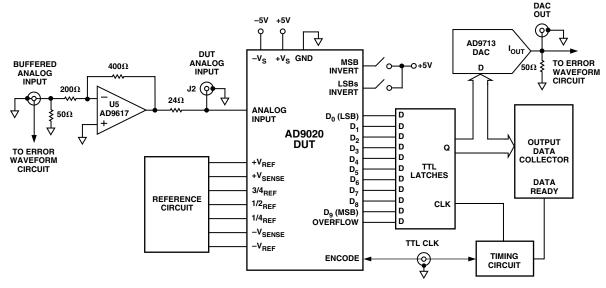

#### AD9020/PCB EVALUATION BOARD

The AD9020/PCB Evaluation Board is available from the factory and is shown here in block diagram form. The board includes a reference circuit that allows the user to adjust both references and the quarter-point voltages. The AD9617 is included as the drive amplifier, and the user can configure the gain from -1 to -15. On-board reconstruction of the digital data is provided through the AD9713, a 12-bit monolithic DAC. The analog and reconstructed waveforms can be summed on the board to allow the user to observe the linearity of the AD9020 and the effects of the quarterpoint voltages. The digital data and an adjustable Data Ready signal are available through a 37-pin edge connector.

Figure 14. AD9020/PCB Evaluation Board Block Diagram

### AD9020–Revision History

# LocationPageData Sheet changed from REV. B to REV. C.2Edit to ABSOLUTE MAXIMUM RATINGS2

#### **OUTLINE DIMENSIONS**