### **Smart Dual Port RAM (S-DPRAM)**

#### Description

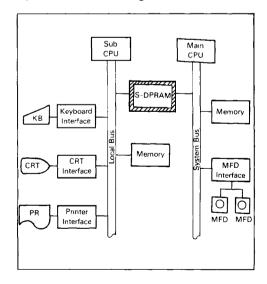

Driven by the declining costs of VLSI CPUs, new multiprocessing and parallel-processing architectures are being explored to break the performance barrier of single CPU designs. A critical factor for multiprocessor performance is the choice of the communication mechanism between CPUs. A poorly designed communication scheme can destroy the potential for a multiprocessor design since message passing overhead can quickly offset the performance advantage of multiple CPUs.

An HD63310R S-DPRAM acts as a communication link between two CPUs. Thus, it replaces older, less flexible communication schemes such as parallel ports and FIFO ICs.

Programmable operating mode and bus interface tailor the S-DPRAM for a wide variety of multiprocessor system designs using industry standard MPUs.

#### Pin Arrangement

#### **Features**

- 1024-byte data buffer with dual ports

—Configurable as a RAM (DPRAM mode)

or two FIFOs (FIFO mode)

- Asynchronous bus operation on each port

- Programmable bus interface

- Each bus configurable as a multiplexed or non-multiplexed address and data bus

- Built-in programmable registers

- —8 semaphore registers for multiprocessing applications, 32 user-definable registers

- Programmable outputs

- -Interrupt outputs

- -FIFO status (full empty, etc) outputs

- High speed operation and low power dissipation 2-µm CMOS circuit

- Single + 5V power supply

#### System Block Diagram

### Pin Description

| Symbol                                                                       | Pin Number Name |                                                                   | I/O |

|------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------|-----|

| Vcc                                                                          | 1               | Power supply                                                      |     |

| V <sub>SS</sub>                                                              | 16, 33          | Ground                                                            |     |

| RESET                                                                        | 48              | Reset                                                             | 1   |

| A <sub>0</sub> -A <sub>5</sub> (A)<br>A <sub>0</sub> -A <sub>5</sub> (B)     | 2-7<br>47-42    | Address bus                                                       | 1   |

| AD <sub>0</sub> -AD <sub>7</sub> (A)<br>AD <sub>0</sub> -AD <sub>7</sub> (B) | 17-24<br>32-25  | Address/data bus                                                  | 1/0 |

| $A_6/A_8/\overline{FRQ_0}(A)$ $A_6/A_8/\overline{FRQ_0}(B)$                  | 8<br>41         | Multipurpose line (1):<br>Address bit 6/8,<br>FIFO data request 0 | 1/0 |

| $A_7/A_9/\overline{FRQ_1}(A)$<br>$A_7/A_9/\overline{FRQ_1}(B)$               | 9<br>40         | Multipurpose line (2):<br>Address bit 7/9,<br>FIFO data request 1 | 1/0 |

| A <sub>8</sub> / <del>AS</del> (A)<br>A <sub>8</sub> / <del>AS</del> (B)     | 10<br>39        | Multipurpose line (3):<br>Address bit 8,<br>Address strobe        | 1   |

| RS (A/B)                                                                     | 11, 38          | Register select                                                   | 1   |

| RDS (A/B)                                                                    | 12, 37          | Read strobe                                                       | 1   |

| WRS (A/B)                                                                    | 13, 36          | Write strobe                                                      | I   |

| READY (A/B)                                                                  | 14, 35          | Ready                                                             | 0   |

| ĪRQ(A/B)                                                                     | 15, 34          | Interrupt request                                                 | 0   |

#### Pin Function

This section describes the input and output signals. As shown in "Pin Arrangement", the S-DPRAM has two data ports (designated port A and port B). Identical interface signals are provided for each port except V<sub>SS</sub>, V<sub>CC</sub>, and RESET which are common to the chip. An "(A)" or a "(B)" after a signal name designates a port A or port B signal.

#### Power Supply (Vcc)

$V_{CC}$  is the +5 V  $\pm$  5% power supply.

#### Ground (Vss)

Vss is the signal and power ground.

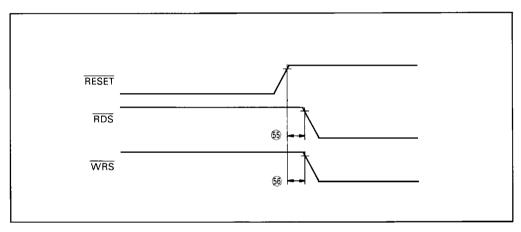

#### Reset (RESET)

RESET places all the registers of the S-

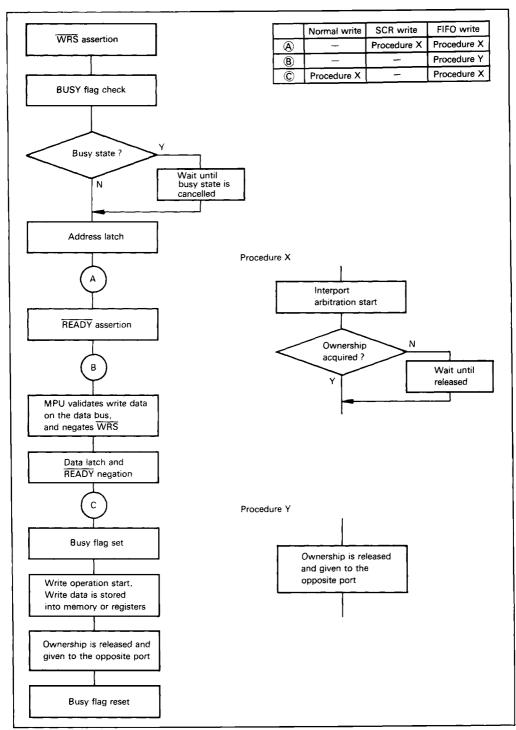

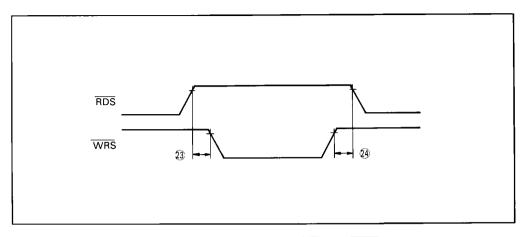

Register Read/Write

DPRAM in the initial state when asserted (refer to "Register Description" for details). This function is designated a hardware reset, as distinguished from a software reset which can be performed by a program. Active low.

#### Address Bus $(A_0(A)-A_5(A), A_0(B)-A_5(B))$

$A_0-A_6$  are the lower 6-bit address input pins when the I/O bus is configured as non-multiplexed. They should be connected to  $V_{SS}$  when the I/O bus is configured as multiplexed. (A CNFG register is selected by the address input 0)

During a RAM access, these lines, together with the  $A_6$ ,  $A_7$ ,  $A_8$  address inputs and internal bank select bit, address one of the 1024 RAM bytes (in DPRAM mode).

Table 1. Address and Data Assignment for Each Operating Mode

| <b>6</b> :                                                                        |                                        | M Mode<br>Addressing)                                                               |                                | M Mode<br>ddressing)                                             | FIFO Mode                      |                                                                  |  |

|-----------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------|--|

| Signal<br>Name                                                                    | Non-mult.                              | Mult.                                                                               | Non-mult.                      | Mult.                                                            | Non-mult.                      | Mult.                                                            |  |

| Address<br>bus<br>A <sub>0</sub> -A <sub>5</sub>                                  | A <sub>0</sub> -A <sub>5</sub>         | Not used                                                                            | A <sub>0</sub> -A <sub>5</sub> | Not used                                                         | A <sub>0</sub> -A <sub>5</sub> | Not used                                                         |  |

| Address/<br>data bus<br>AD <sub>0</sub> -AD <sub>7</sub>                          | Data<br>D <sub>0</sub> -D <sub>7</sub> | Address<br>A <sub>0</sub> -A <sub>7</sub><br>Data<br>D <sub>0</sub> -D <sub>7</sub> | D <sub>0</sub> -D <sub>7</sub> | A <sub>0</sub> -A <sub>7</sub><br>D <sub>0</sub> -D <sub>7</sub> | D <sub>0</sub> -D <sub>7</sub> | A <sub>0</sub> -A <sub>5</sub><br>D <sub>0</sub> -D <sub>7</sub> |  |

| Multi-<br>purpose<br>line (1)<br>A <sub>6</sub> /A <sub>8</sub> /FRQ <sub>0</sub> | No                                     | t used                                                                              | A <sub>6</sub>                 | Α <sub>8</sub>                                                   | FRQ <sub>0</sub>               |                                                                  |  |

| Multi-<br>purpose<br>line (2)<br>A <sub>7</sub> /A <sub>9</sub> /FRQ <sub>1</sub> | No                                     | t used                                                                              | Α <sub>7</sub>                 | Ag                                                               | FF                             | RQ <sub>1</sub>                                                  |  |

| Multi-<br>purpose<br>line (3)<br>A <sub>8</sub> /AS                               | Not used                               | ĀŜ                                                                                  | Α <sub>8</sub>                 | ĀS                                                               | Not used                       | ĀS                                                               |  |

Notes: 1. Non-mult. I/O bus is configured as non-multiplexed.

Mult. I/O bus is configured as multiplexed address and data bus.

<sup>2.</sup> A hardware reset places the S-DPRAM in DPRAM mode, and defines the I/O bus as non-multiplexed. The operation mode can be altered by setting the internal CNFG register as required.

During a register access, these lines select one of the 62 internal registers.

# Address/Data Bus $(AD_0(A)-AD_7(A), AD_0(B)-AD_7(B))$

$AD_0-AD_7$  are the input/output pins for the data bus when the I/O bus is configured as non-multiplexed. They are the input pins for the lower 8-bit address, and input/output pins for data when the I/O bus is configured as multiplexed. Three-state.

# Multipurpose Lines $(A_6(A)/A_8(A)/\overline{FRQ_0}$ (A), $A_6(B)/A_8(B)/\overline{FRQ_0}(B)$ , $A_7(A)/A_9(A)/\overline{FRQ_1}(A)$ , $A_7(B)/A_9(B)/\overline{FRQ_1}(B)$ , $A_8(A)/\overline{AS}(A)$ , $A_8(B)/\overline{AS}(B)$

The function of the multipurpose lines varies according to the operation mode of the S-DPRAM (table 1). These functions are as follows.

$A_6-A_8$  or  $A_8$ ,  $A_9$  Address Bit (Upper): The  $A_6-A_8$  upper address inputs are used together with  $A_0-A_5$  for RAM addressing (in DPRAM mode), when the I/O bus is configured as non-multiplexed. Since only 512 bytes can be addressed by the address pins, the upper or lower 512 RAM bytes should be selected by the bank select bits (bit 0 or 1) of the CMD register.

When the I/O bus is configured as multiplexed, RAM addressing utilizes  $A_8$  and  $A_9$  as the input pins for the upper address bits, along with lower address bits  $A_0 - A_7$ .

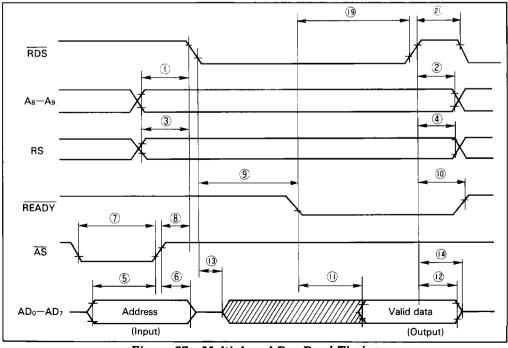

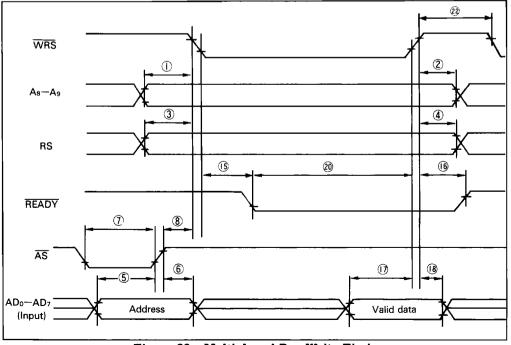

**Address Strobe (\overline{AS}):**  $\overline{AS}$  latches the address  $A_0-A_7$  on the address/data bus  $AD_0-AD_7$  when the I/O bus is configured as a multiplexed bus. The address presented on  $AD_0-AD_7$  pins is latched at the rising edge of  $\overline{AS}$ . Active low.

FIFO Data Request (FRQ<sub>0</sub>, FRQ<sub>1</sub>): The  $FRQ_0/FRQ_1$  active low outputs represent the state of a programmable FIFO threshold: FIFO 0/1 full, empty, not full, or not empty. The operation of these signals are controlled by the internal FRC (FIFO request control) register. Active low.

#### Register Select (RS(A), RS(B))

RS indicates whether the address specified during the current read/write operation refers to a RAM byte or an internal register. If RS is asserted high, then the address refers to one of the internal registers. If RS is low the address refers to a RAM byte.

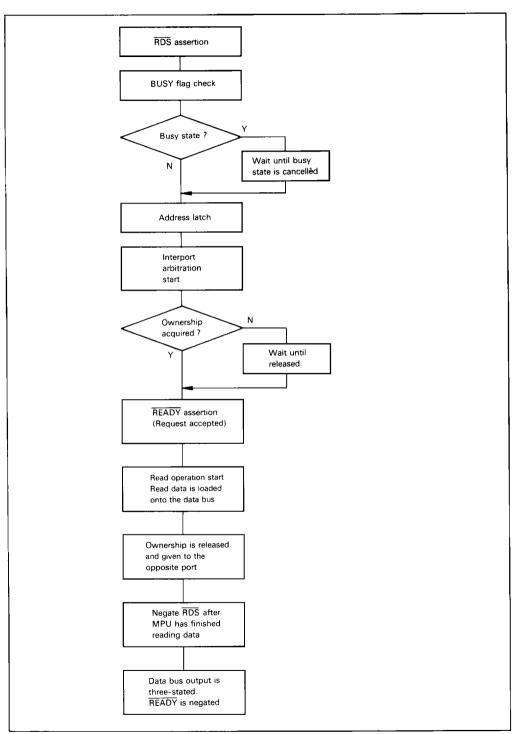

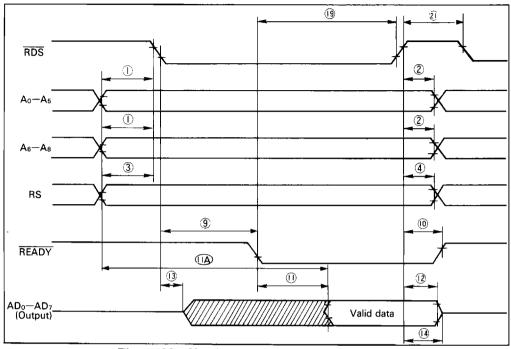

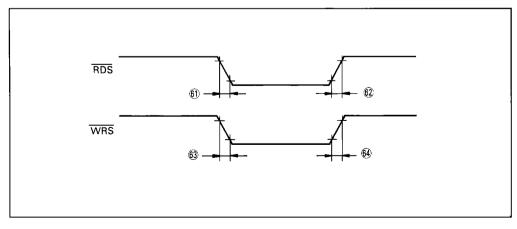

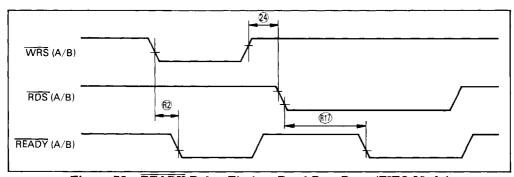

#### Read Strobe ( $\overline{RDS}(A)$ , $\overline{RDS}(B)$ )

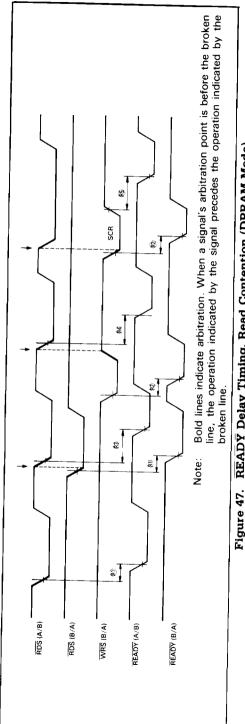

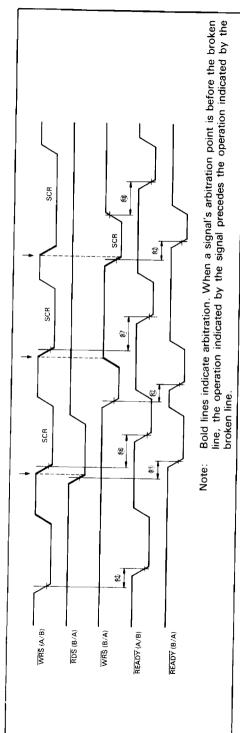

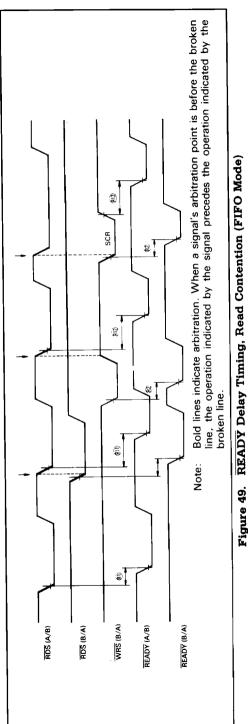

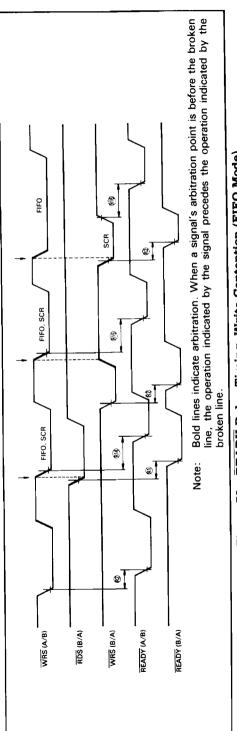

$\overline{RDS}$  selects the S-DPRAM for a read transaction. Whenever  $\overline{RDS}$  is asserted low the data from the addressed internal register or RAM location is transferred to the data bus. In case of simultaneous transfer requests from both ports, the internal arbiter determines the order in which the requests are serviced at the falling edge of  $\overline{RDS}$ . Active low.

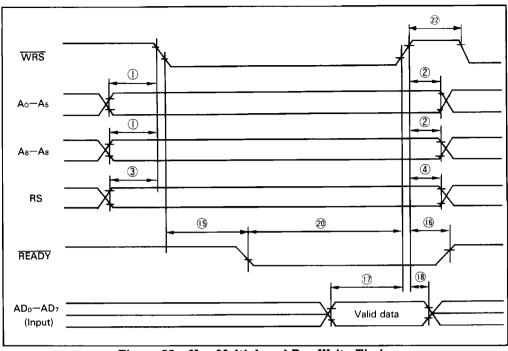

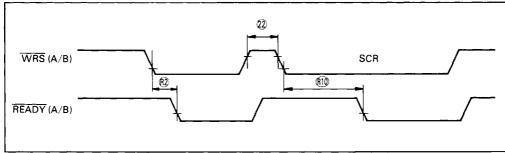

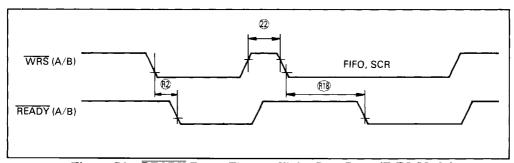

#### Write Strobe (WRS(A), WRS(B))

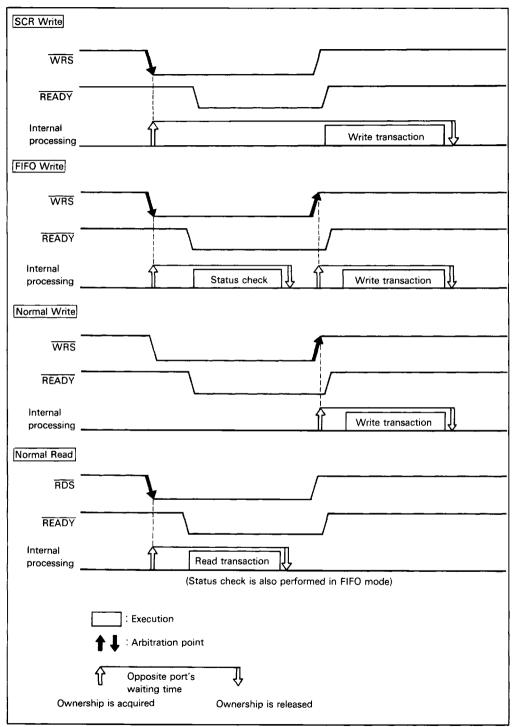

WRS selects the S-DPRAM for a write transaction. Whenever WRS is asserted low, a write access to an internal register or RAM is initiated. Write transactions are bufferred. The data is temporarily latched into the buffer register upon negation of WRS. It is subsequently written into the specified internal register or RAM, using the internal clock timing. Active low.

In case of simultaneous transfer requests from both ports, the internal arbiter determines the order in which the requests are serviced. (Detailed explanations are shown in the paragraph "Arbitration (Hardware)".)

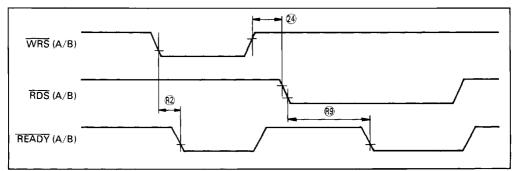

#### Ready ( $\overline{READY}(A)$ , $\overline{READY}(B)$ )

$\overline{\text{READY}}$  reports the successful acceptance of the  $\overline{\text{RDS}}$  (or  $\overline{\text{WRS}}$ ) signal to the MPU. After its assertion,  $\overline{\text{RDS}}$  (or  $\overline{\text{WRS}}$ ) must be kept low for a minimum period specified in the bus timing characteristics in order to assure a proper completion of internal processing. Active low.

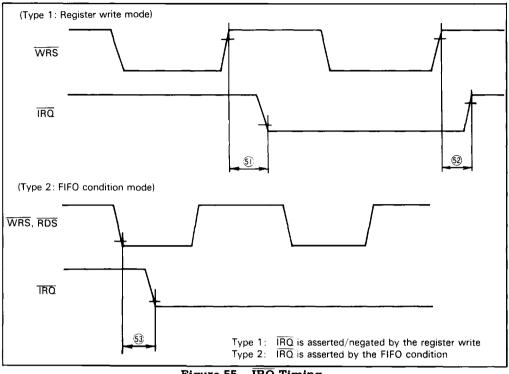

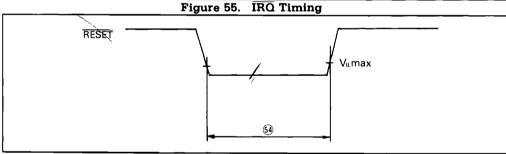

#### Interrupt Request (IRQ (A), IRQ (B))

The IRQ open-drain output is asserted low when at least one bit of the AND of the corresponding bits of a port's ISRC and IEN register is set to 1. Active low, open drain.

### Comparison between HD63310 and HD63310R

The HD63310R is an advanced R version of the HD63310, characterized by the following features: FIFO status operation error has been corrected (already reported by Hitachi Microcomputer Technical Update, TN-PSY- 503A), some limitations have been eliminated, and noise resistance has been improved (noise caused by undefined read data has been removed). Table 2 shows a comparison between the HD63310 and HD63310R.

Table 2. HD63310R and HD63310

| Item                                                                                |                                                         | HD63310RP20                                                       | HD63310P20                                                        |

|-------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| FCR register                                                                        | In DPRAM mode                                           | Read/write accessible                                             | Write invalid, read as 0                                          |

|                                                                                     | In FIFO mode                                            | Read/write accessible                                             | Read/write accessible                                             |

| FRQ output timing characteristics                                                   | No. 32;<br>FRQ negation delay time<br>(at write access) | t <sub>FNLW</sub> = 150 ns                                        | t <sub>FNLW</sub> = 300 ns                                        |

| FRQ output timing specification (FRQ timing at write access in level mode) [type 1] |                                                         | FRQ is negated at the rising edge of WRS WRS FRQ                  | FRQ is negated at the fall-<br>ing edge of WRS<br>WRS<br>FRQ      |

| FRQ output timing item                                                              | FRQ timing at write access in pulse mode [type 1]       | No. 35;<br>FRQ negation delay time;<br>t <sub>FNPW</sub> = 250 ns | No. 32;<br>FRQ negation delay time;<br>t <sub>FNLW</sub> = 300 ns |

|                                                                                     | FRQ timing at read access in pulse mode                 | No. 38;<br>FRQ negation delay time;<br>t <sub>FNPR</sub> =300 ns  | No. 34;<br>FRQ negation delay time;<br>t <sub>FNLR</sub> = 300 ns |

| Notes                                                                               | limitations on ISRC register                            | Removed                                                           | Remain                                                            |

Note: In FIFO operation, the HD63310R is not compatible with the HD63310 in order to improve the FIFO contention error (at enpty condition). Therefore some changes in the circuit are required around the FRQ signals.

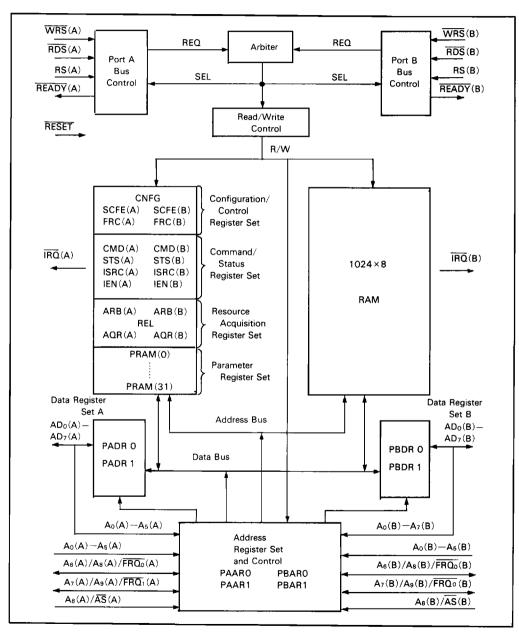

#### **Block Diagram**

The S-DPRAM consists of 1024 bytes of static

RAM and 32 bytes of register. See figure 1.

Figure 1. Block Diagram

### **@**HITACHI

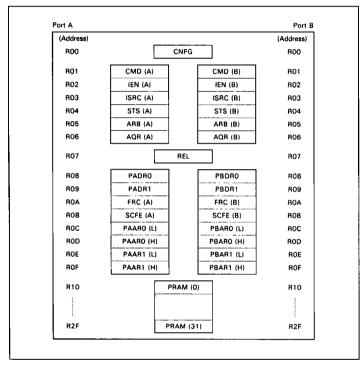

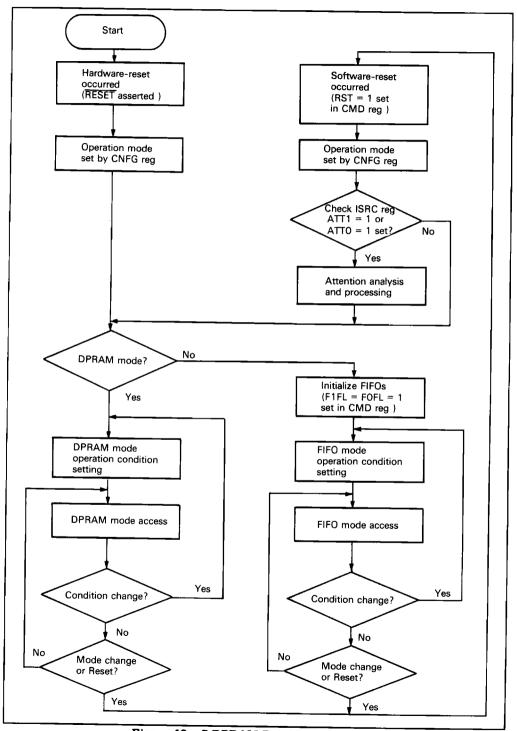

#### Register Description

The operation of the S-DPRAM is controlled, as well as monitored, by a number of on-chip user-accessible registers. Some of these registers are shared by both ports, while others are for exclusive use of each port. The CNFG (configuration), REL (release/available), and PRAM (parameter) registers are shared by

both ports, while the rest of them are provided for each port. An "(A)" or a "(B)" after a register name indicates a port A or port B register respectively. The internal register configuration is shown in figure 2, and their bit definition is in table 3.

Table 3. Internal Register: Bit Configuration and Operation

| Add. | Reg.           |           |      | Bit  | Confi            | igura            | tion |             |                |                |              | F | tead/    | Write | о Оре  | ratio | n   |    |               |

|------|----------------|-----------|------|------|------------------|------------------|------|-------------|----------------|----------------|--------------|---|----------|-------|--------|-------|-----|----|---------------|

| #    | Name           | 7         | 6    | 5    | 4                | 3                | 2    | 1           | 0              | Reset          | 7            | 6 | 5        | 4     | 3      | 2     | 1   | 0  | Remarks       |

| R00  | CNFG           | !<br>ABUS | BBUS |      | RCFG             |                  | 0    | F1D         | FOD            | 00             |              |   | R/W      |       |        | 0     | R/  | w  | Common<br>SCR |

| R01  | CMD            | AP1       | AP0  | RST  | 0                | 0                | 0    |             | FOFL<br>BOSL   | 00<br>(Note1)  | R/           | W | RO<br>/W | 0     | 0      | 0     | R,  | w  | SCR           |

| R02  | IEN            | ENA7      | ENA6 | ENA5 | ENA4             | ENA3             | ENA2 | ENA1        | ENAO           | 00             |              |   |          | R,    | w      |       |     |    | SCR           |

| R03  | ISRC           | ATT1      | ATT0 | RELE | FERR             | F1F              | F1E  | FOF         | FOE            | 00<br>(Note1)  |              | - |          | R/V   | V1C    |       |     |    | SCR           |

| R04  | STS<br>(A/B)   | IRQ       | FRQ1 | FRQ0 | FERR             | F1F              | F1E  | FOF<br>B1EN | FOE<br>BOEN    | 01             |              |   |          |       | R      |       |     |    |               |

| R05  | ARB<br>(A/B)   |           |      | •    | Р                | ID               |      |             |                | 00             |              |   |          | RΛ    | VID    |       |     |    |               |

| R06  | AQR<br>(A/B)   | OWN7      | OWN6 | OWN5 | OWN4             | OWN3             | OWN2 | OWN1        | owno           | 00             |              |   | -        | R/W ( | Note 2 | )     |     |    | :             |

| R07  | REL            | AVL7      | AVL6 | AVL5 | AVL4             | AVL3             | AVL2 | AVL1        | AVLO           | FF             | R/W (Note 2) |   |          |       | Common |       |     |    |               |

| R08  | PA/BDRC        |           |      |      | D <sub>7</sub>   | - D <sub>0</sub> |      |             |                | un-<br>defined |              |   |          | R,    | w      |       |     |    |               |

| R09  | PA/BDR1        |           |      |      | D <sub>7</sub>   | - D <sub>0</sub> |      |             |                | un-<br>defined |              |   |          | R,    | w      |       |     |    |               |

| ROA  | FRC<br>(A/B)   | 0         | FR1E | FR1T | FR1M             | 0                | FROE | FROT        | FROM           | 00             | 0            |   | R/W      |       | 0      |       | R/W |    | SCR           |

| ROB  | SCFE<br>(A/B)  | CNT1      | DEC1 | CNTO | DECO             | F10              | F1U  | F00         | FOU            | 00             |              | R | /W       | -     |        |       | ₹   |    | SCR           |

| POC  | PA/BARC<br>(L) | )         |      |      | Α7               | -A <sub>0</sub>  |      | •           |                | 00             |              |   |          | R     | w      |       |     |    |               |

| POD  | PA/BARC<br>(H) | REG       | 0    | 0    | 0                | 0                | 0    | Ag          | Aa             | 00             | R/W          | 0 | 0        | 0     | 0      | 0     | R,  | /W |               |

| POE  | PA/BAR1        |           |      |      | A <sub>7</sub> - | -A <sub>0</sub>  |      |             |                | 00             |              |   |          | R,    | w      |       | -   |    | i             |

| POF  | PA/BAR1        | REG       | 0    | 0    | 0                | 0                | 0    | Ag          | A <sub>8</sub> | 00             | R/W          | 0 | 0        | 0     | 0      | 0     | R.  | /W |               |

| R10  |                |           |      |      | ·                |                  |      |             |                |                |              |   |          | -     |        |       | •   |    | _             |

|      | PRAM           |           |      |      | PR               | AM               |      |             |                | un-<br>defined |              |   |          | R.    | w      |       |     |    | ļ             |

| R2F  |                |           |      |      |                  |                  |      |             |                |                |              |   |          |       |        |       |     |    |               |

Notes: 1. 00 at a hardware reset state.

At a software reset state, bits 7 and 6 are preserved, while the rest are cleared.

2. Semaphore bits to prevent access contention. OWNO-OWN7 and AVLO-AVL7 are related to each other.

3. R/W

Read/write

W1C

Write 1 to clear

R'

Read only

WID

Write ID code to set if 0

RO

Read as 0 only

0

Not used; write invalid; read as 0 only

SCR

Special Control Register

COMMON

Shared register

When the S-DPRAM is in DPRAM mode, its indirect addressing capability allows both internal registers and the on-chip RAM to be accessed using address register PA/BAR0 or PA/BAR1 as an address pointer. The value stored in PA/BAR0 will be used as an indirect address whenever a read or write operation is performed through a port's data register PA/BDR0. Similarly, the value contained in PA/BAR1 will be used as an indirect address whenever a read or write operation is performed through a port's data register PA/BDR1.

Using indirect addressing, it is possible to access from port A the registers belonging to port B, and vice versa. The indirect address values 30-3F are reserved for accessing the opposite port's registers. Table 3 summarizes the direct and indirect address allocation for S-DPRAM's internal registers.

In FIFO mode, the indirect addressing is disabled because the address registers are utilized for FIFO control. The opposite port's registers, therefore, are not accessible in this mode.

Figure 2. Internal Register Configuration

Table 4. Register Map and Address (In DPRAM mode)

| Address  | Port A               | D | 1 | Port B               | D | ı |

|----------|----------------------|---|---|----------------------|---|---|

| 00<br>0F | Control Register (A) | 0 | 0 | Control Register (B) | 0 | 0 |

| 10<br>2F | Parameter Register   | 0 | 0 | Parameter Register   | 0 | 0 |

| 30<br>3F | Control Register (B) | × | 0 | Control Register (A) | × | 0 |

Notes: 1. D: Direct addressing mode

- Accessible

- t: Indirect addressing mode x: Not accessible

<sup>2.</sup> Address inputs A<sub>6</sub>-A<sub>9</sub> are not used for register access. Therefore addresses above 40 are the same as addresses 00-3F.

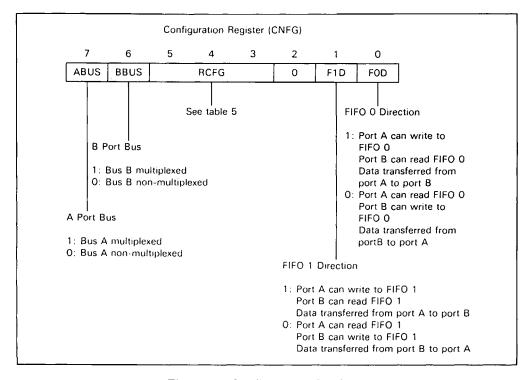

#### Configuration Register (CNFG)

The contents of the CNFG register (figure 3) should be defined after a reset, before any other register is accessed.

The ABUS and BBUS respectively define bus A and bus B to be either non-multiplexed or multiplexed address and data buses. The RCFG field defines the on-chip RAM either as DPRAM or as two FIFOs. The F1D/F0D define

the data transfer direction between FIFO 1 and FIFO 0 and the data ports. F1D/F0D are not used (ineffective) when the S-DPRAM is set in DPRAM mode by the RCFG.

After a reset, both ports are set in DPRAM mode with the I/O bus configured as non-multiplexed (ABUS=0, BBUS=0, RCFG=000). CNFG is a shared register accessible from both ports.

Figure 3. Configuration Register

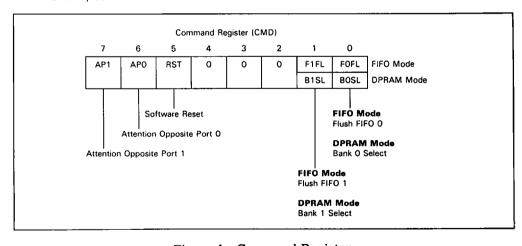

#### Command Register (CMD(A), CMD(B))

Writing to a CMD register (figure 4) causes the commands corresponding to the bits set to 1 to be executed. The previous data in the CMD register does not affect the operation. For example, if the data in a bit is 1, writing a 1 to that bit still accesses the corresponding command.

The AP1 and AP0 bits perform interport communication. Writing a 1 to these bits sets

bits ATT1 or ATT0 of the ISRC register of the opposite port, reporting a transaction request to that port.

The RST bit places the S-DPRAM in the software reset state. The software reset is slightly different from the hardware reset caused by asserting the RESET pin. Refer to "Reset Operation" for details.

The functions of bits 0 and 1 of the CMD register vary depending on the S-DPRAM

operating mode. In FIFO mode, they function as F1FL and F0FL, which initialize the FIFOs. Writing a 1 to F1FL/F0FL causes the following operations:

- Sets F1E/F0E=1 and F1F/F0F=0 in the STS registers of both ports

- Sets F1O/F0O=0 and F1U/F0U=0 in the SCFE registers of both ports

- Sets F1E/F0E=1 in ISRC registers of both ports

- Flushes FIFO 1/0 (initializes FIFO top and bottom pointers)

In DPRAM mode, they function as B1SL and B0SL, which select the upper or lower 512

bytes of RAM. Setting B1SL to 1 selects the upper 512-byte bank (bank 1). This sets B1EN =1 in the STS register. Setting B0SL to 1 selects the lower 512-byte bank (bank 0). This sets B0EN= 1 in the STS register. If an attempt is made to set both B1SL and B0SL to 1, B1SL will be set to 0 and B0SL will be set to 1, selecting the bank 0. These bits are only used for direct addressing with a non-multiplexed I/O bus. In the multiplexed mode, the A9 signal selects the bank instead.

Writing a 0 to any bit of the CMD register clears that bit. Reading the CMD register returns the data that was most recently written into the register.

Table 5. 1024-Byte RAM Operation Mode and FIFO Size

| RCFG |                |   |             | FIFO Size |        |  |

|------|----------------|---|-------------|-----------|--------|--|

| bit5 | oit5 bit4 bit3 |   | RAM Op Mode | FIFO 1    | FIFO 0 |  |

| 0    | 0              | 0 | DPRAM       | -         | _      |  |

| 0    | 0              | 1 | FIFO        | 0         | 1024   |  |

| 0    | 1              | 0 | FIFO        | 1024      | 0      |  |

| 0    | 1              | 1 | FIFO        | 512       | 512    |  |

| 1    | 0              | x | FIFO        | 256       | 768    |  |

| 1    | 1              | х | FIFO        | 768       | 256    |  |

Notes: x: Don't care Unit: bytes

Figure 4. Command Register

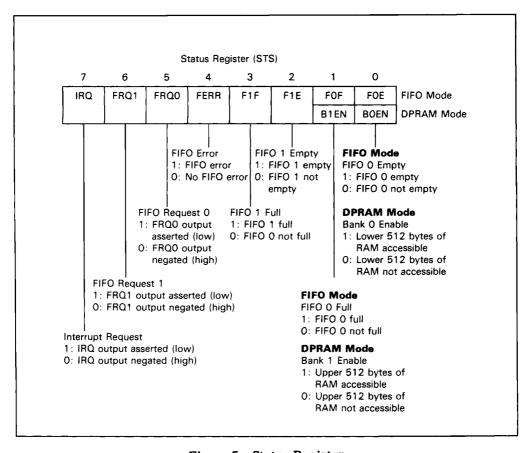

#### Status Register (STS(A), STS(B))

The read-only STS register (figure 5) reports the operational status of the S-DPRAM. The IRQ bit displays the condition of the IRQ output terminal. FRQ1 and FRQ0 display internal signal conditions.

F1E and F0E (FIFO 1/0 empty) are set to 1 at FIFO 1/0 initialization.

FERR (FIFO error) is set when one of F1O, F1U, F0O, or F0U is set in the SCFE register:

FERR = F1O + F1U + F0O + F0U

Figure 5. Status Register

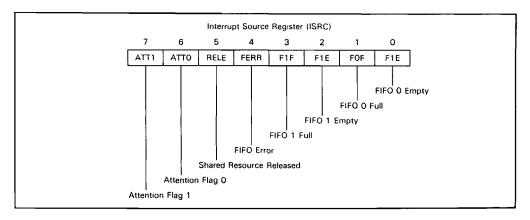

### Interrupt Source Register (ISRC(A), ISRC (B))

The ISRC register (figure 6) stores interrupt source information. The stored information is preserved regardless of FIFO, ATT, and RELE status change until the ISRC register is cleared. The interrupt request output IRQ is asserted when at least one bit of the AND of corresponding bits of IRSC and IEN registers is set to 1.

The ATT1 and ATT0 bits are set to 1 by a transaction request from the opposite port (AP1/AP0 of opposite port set).

RELE = 1 indicates that the shared resource semaphore of the opposite port has been released. This occurs when a bit of the REL register has changed from 0 to 1 due to the opposite port writing a 1 into the AVL bit of the REL register.

The FERR bit indicates a condition such as FIFO overflow or underflow. the F1F, F1E, F0F, and F0E bits, indicate FIFO full and empty conditions. They are set when the corresponding bit in the STS goes from 0 to 1. These bits in the ISRC register retain their state until the register is cleared. In the STS register, they show the current status when they are read.

Writing a 1 into an ISRC register bit clears that bit. Writing a 0 into a bit has no effect.

Figure 6. Interrupt Source Register

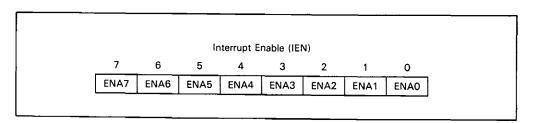

#### Interrupt Enable Register

The IEN register (figure 7) masks interrupt conditions in the ISRC register.

The IRO signal is asserted when the AND of at least one pair of corresponding bits from IEN and ISRC is 1:

IRQ= ATT1·ENA7+ATT0·ENA6+RELE· ENA5+FERR·ENA4+F1F·ENA3+ F1E·ENA2+F0F·ENA1+F0E·ENA0

The IRQ bit of STS is also set when the IRQ signal is asserted.

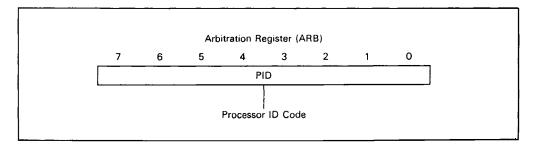

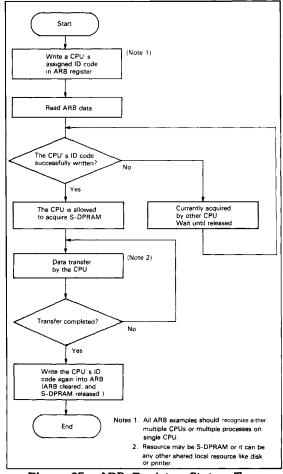

#### Arbitration Register (ARB(A), ARB(B))

The ARB register (figure 8) provides a mechanism for multiple CPUs (or multiple processes on a single CPU) sharing a common port to arbitrate among themselves.

This register has a test-and-set hardware logic circuit, and allows system software to manage access to shared resources, including the S-DPRAM itself.

The ARB register access procedure is:

- The requesting processor writes its ID code into the register.

- The processor reads back the register. If it reads its own ID, its request has been accepted.

- 3. The processor makes the data transfer.

- The processor releases the system resource by writing its ID into the register again.

Write Access: If the PID is 0, then ARB write access is allowed. if the PID is not 0:

- Writing data equal to the PID clears the PID.

- Writing data not equal to the PID does not change the PID.

**Read Access:** If the PID is equal to a processor's ID code, the system resource is owned by that processor. If the PID is not equal to a processor's ID code, the resource is owned by another processor. If the PID equals 0, the resource is free.

Figure 7. Interrupt Enable Register

Figure 8. Arbitration Register

Figure 8A. ARB Status Chart

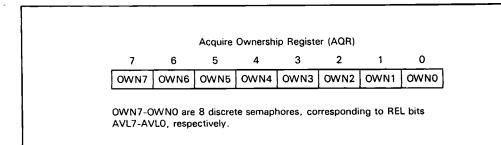

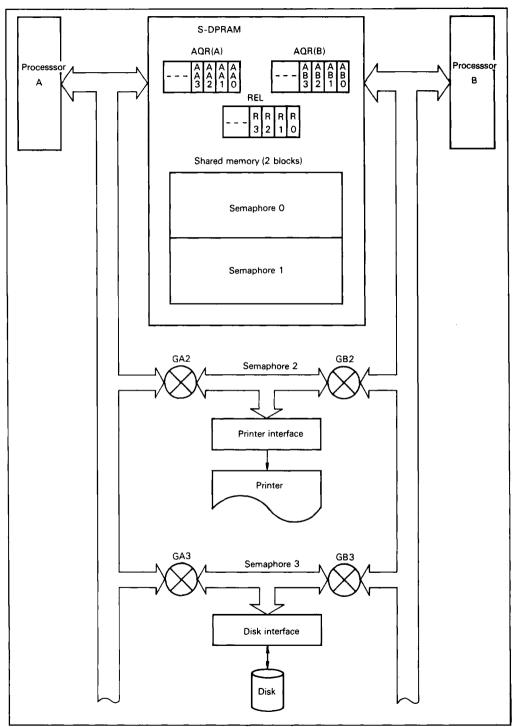

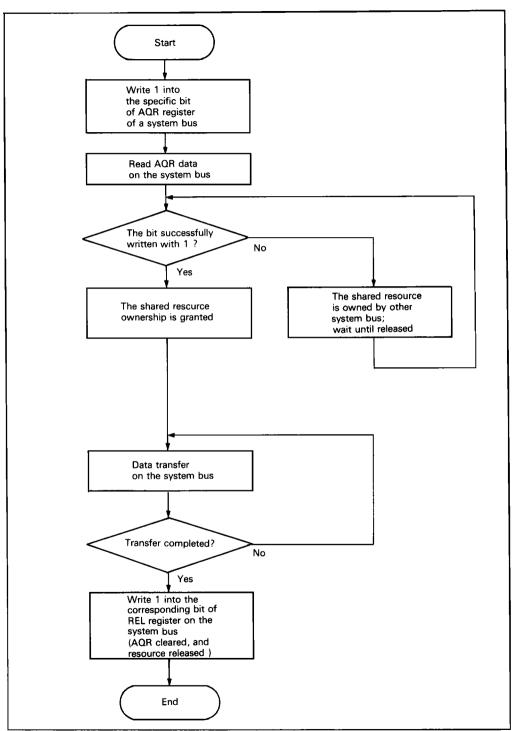

### Acquire Ownership Register (AQR(A), AQR(B))

The AQR register (figure 9) provides 8 semaphores to arbitrate for exclusive ownership of system resources shared between ports A and B. It is used in conjunction with the REL register. Each of the 8 bits, OWN7-OWN0, can represent ownership of a separate system resource. An AQR register is provided for each port.

A resource is acquired as follows:

- The requesting processor attempts to write a 1 into the bit corresponding to the desired shared resource.

- 2. The processor reads the bit back. A 1 indicates that the resource has been successfully acquired. A 0 indicates that the resource has already been acquired by a device on the opposite port.

Successfully writing a 1 to an AQR bit

- simultaneously clears the bit in the same position in the REL register.

- The processor makes the data transfer.

- 4. The processor releases the resource by

writing a 1 to the corresponding bit of the REL register. The OWN bit in the AQR register will be cleared and the shared resource will be released to the system.

Write Access: An unsuccessful attempt to write a 1 to an OWN bit indicates that the opposite port has acquired ownership of the corresponding shared resource. A successful attempt indicates that the resource has been acquired. On acquisition, a 0 is simultaneously written into the corresponding AVL bit in the REL register.

**Read Access:** A read access must be performed after an attempt to write a 1 into a bit. Writing a 1 does not guarantee that the bit will be set. When the bit is read as 1, it indicates that the device connected to this port has acquired ownership of the system resource corresponding to the bit.

Once successfully set, the bit remains set until the corresponding bit in the REL register is set or a reset occurs. When the bit is read as 0, it indicates that the request for ownership has failed.

Figure 9. Acquire Ownership Register

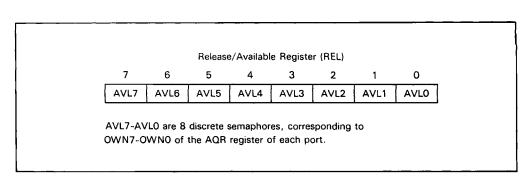

#### Release Available Register (REL)

The REL register (figure 10), in conjunction with a port's AQR register, provides 8 semaphores for interport arbitration of system resources. The register is a bit-mapped summary of available system resources, and a mechanism for either port to release its acquired resources to the system. REL is a shared register accessible from both ports. AVL7-AVL0 correspond to OWN7-OWN0 of the AQR registers of each port.

When a port writes a 1 into a specific bit of the REL register, it releases the corresponding system resource, provided that it is owned by that port. A write access by the opposite port (which doesn't own the resource) causes no action. Successfully writing a 1 into an AVL bit simultaneously writes 0 the OWN bit of the AQR register of the port performing the write.

When the OWN bit is read as 1, it indicates that the corresponding system resource is available. Writing a 1 to an OWN bit of the AQR register simultaneously clears the cor-

responding AVL bit of the REL register.

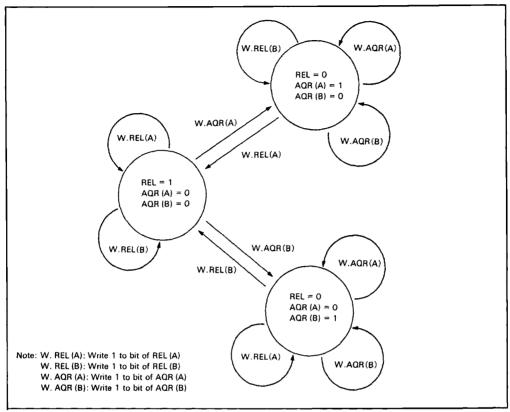

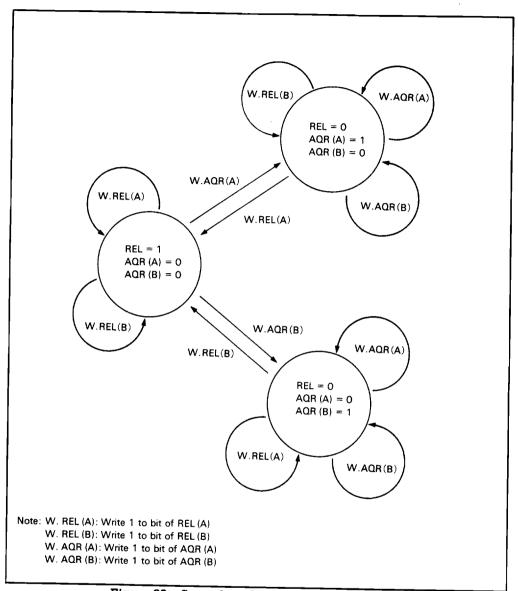

The state transition diagram (figure 11) summarizes the relation between the REL register and the AQR registers of ports A and B.

Write Access: Writing a 1 into a bit releases the corresponding shared resource to the system. A port can set an AVL successfully only if the AOR register of that port has a 1 in the same bit position. A port successfully writing a 1 into an AVL bit clears the corresponding OWN bit in that port's AOR register. Writing a 0 has no effect. A transition from 1 to 0 in any bit of the REL register sets the RELE interrupt bit in the ISRC register.

Read Access: When a bit is read as 1, it indicates that the corresponding shared resource is available. The bit remains set until a 1 is written to the corresponding OWN bit of the AQR register. When a bit is read as 0, it indicates that the system resource has been acquired by either port A or port B.

Figure 10. Release/Available Register

Figure 11. AQR, REL Register State Transition Diagram

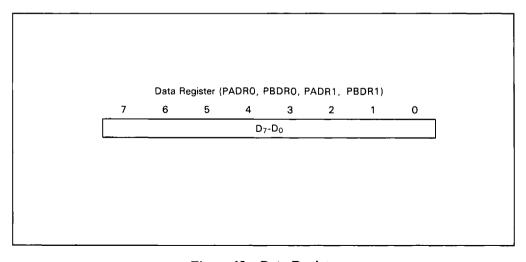

### Data Register (PADR0, PBDR0, PADR1, PBDR1)

Each port of the S-DPRAM has two data registers (figure 12). The data transferred through these registers depends on the S-DPRAM operating mode.

**DPRAM Mode, Indirect Addressing Operation:** An access to a port's data register in DPRAM mode results in an indirect access to the target register or RAM. If PADR0 or PBDR0 is accessed, the address will be supplied by PAAR0 or PBAR0. If PADR1 or PBDR1 is accessed, the address will be supplied by PAAR1 or PBAR1 (table 6).

The opposite port's registers are also accessible in indirect addressing mode. This facilitates system status checking and more efficient data transfer. Also, in this mode the SCFE register can be defined to allow the

address register to increment by 1, decrement by 1, or remain unchanged after each indirect access.

**FIFO Mode:** During FIFO mode, accessing these registers transfers data to and from the two FIFOs. The data transfer direction is defined by bits F1D and F0D in the CNFG register.

PADR0 or PBDR0 transfer data between FIFO 0 and the corresponding port. Similarly PADR1 or PBDR1 transfer data between FIFO 1 and the corresponding port (table 7).

The RAM address for FIFO accesses is internally supplied from the port address registers PAARO, PBARO, PAAR1, and PBAR1 (table 8). The registers are automatically incremented after each transfer. These registers should not be accessed in FIFO mode.

Table 6. Address Register Used as Pointer

| Port   | Accessed Data Register | Pointer Address Register |

|--------|------------------------|--------------------------|

| Port A | PADR O                 | PAAR O                   |

|        | PADR 1                 | PAAR 1                   |

| Port B | PBDR 0                 | PBAR O                   |

|        | PBDR 1                 | PBAR 1                   |

Table 7. FIFO 0/1 and Data Registers

| Port   | FIFO   | Accessed Data Register |

|--------|--------|------------------------|

| Port A | FIFO O | PADR 0                 |

|        | FIFO 1 | PADR 1                 |

| Port B | FIFO O | PBDR 0                 |

|        | FIFO 1 | PBDR 1                 |

Table 8. Address Control in FIFO Mode

| FIFO   | Pointer       | Address Register |  |

|--------|---------------|------------------|--|

| FIFO O | Bottom (read) | PAAR O           |  |

|        | Top (write)   | PBAR O           |  |

| FIFO 1 | Bottom (read) | PAAR 1           |  |

|        | Top (write)   | PBAR 1           |  |

Note: Top = Top of FIFO, address for write transaction Bottom = Bottom of FIFO, address for read transaction

Figure 12. Data Register

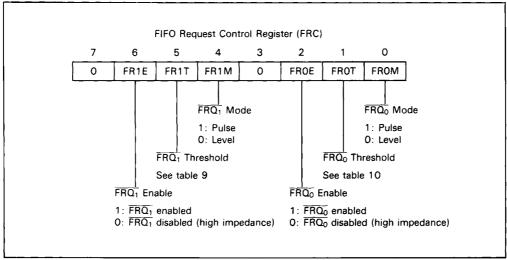

### FIFO Request Control Register (FRC(A), FRC(B))

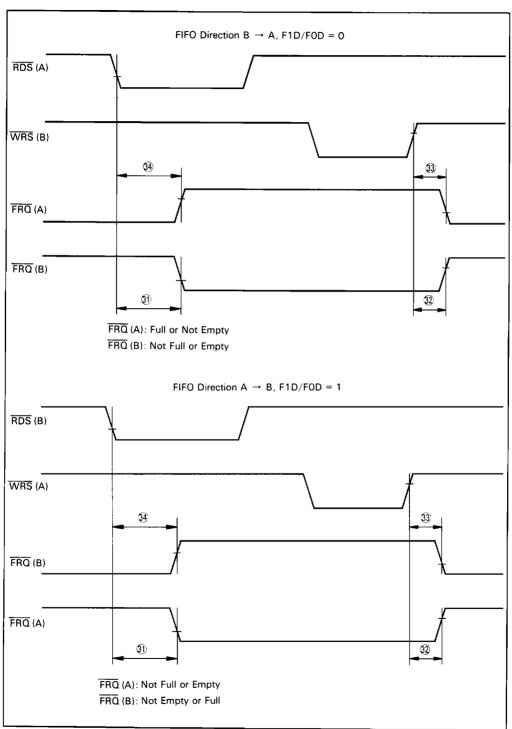

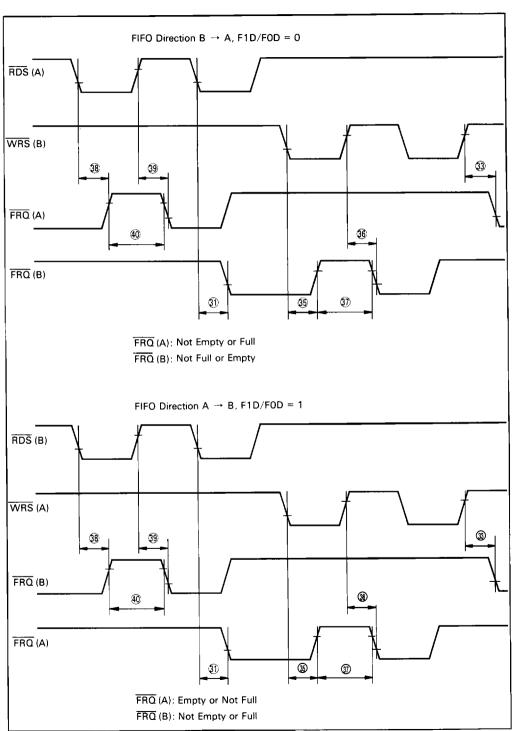

The FRC registers (figure 13) control the FIFO request output signals  $\overline{FRQ}_1$  and  $\overline{FRQ}_0$  in FIFO mode.

The FR1E and FR0E bits enable  $\overline{FRQ_1}$  and  $\overline{FRQ_0}$  outputs, respectively. The FR1T and FR0T bits define the assertion conditions of these signals (tables 9, 10).

The FR1M and FR0M bits specify whether  $\overline{FRQ_1}$  and  $\overline{FRQ_0}$  are asserted as pulse or level outputs. As a pulse output, a  $\overline{FRQ_1}$  or  $\overline{FRQ_0}$  pulse is asserted each time a FIFO bus transaction occurs in the specified direction, and is held for as long as the asserting condition remains true. As a level output,  $\overline{FRQ_1}$  or  $\overline{FRQ_0}$  level is held asserted as long as the asserting condition remains true. (See timing chart for details.)

Table 9. FRQ1 Assertion Condition

|                | Data Access |      | Assertion Condition |                  |  |  |  |  |

|----------------|-------------|------|---------------------|------------------|--|--|--|--|

| F1D (CNFG Reg) |             | FR1T | Port A              | Port B           |  |  |  |  |

| 0              | A: Read     | 1    | FIFO 1 full         | FIFO 1 empty     |  |  |  |  |

|                | B: Write    | 0    | FIFO 1 not empty    | FIFO 1 not full  |  |  |  |  |

| 1              | A: Write    | 1    | FIFO 1 empty        | FIFO 1 full      |  |  |  |  |

|                | B: Read     | 0    | FIFO 1 not full     | FIFO 1 not empty |  |  |  |  |

Table 10. FRO<sub>0</sub> Assertion Condition

|                | Data Access |      | Assertion Condition |                  |  |  |  |  |

|----------------|-------------|------|---------------------|------------------|--|--|--|--|

| FOD (CNFG Reg) |             | FROT | Port A              | Port B           |  |  |  |  |

| 0              | A: Read     | 1    | FIFO O full         | FIFO 0 empty     |  |  |  |  |

|                | B: Write    | 0    | FIFO 0 not empty    | FIFO 0 not full  |  |  |  |  |

| 1              | A: Write    | 1    | FIFO 0 empty        | FIFO O full      |  |  |  |  |

|                | B: Read     | 0    | FIFO O not full     | FIFO 0 not empty |  |  |  |  |

Figure 13. FIFO Request Control Register

# 5

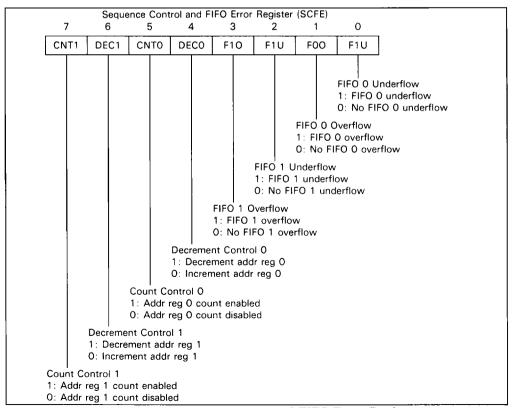

# Sequence Control and FIFO Error Register (SCFE(A), SCFE(B))

The SCFE register (figure 14) has 4 bits for address register control, and 4 bits for FIFO error indication.

The upper 4 bits (CNT1, DEC1, CNT0, DEC0)

control the corresponding address register count. If CNT1/CNT0 = 0, the address register will not change after access to the corresponding data register. If CNT1/CNT0 = 1, the address register will decrement by when DEC1/DEC0 = 1 or increment by 1 when DEC1/DEC0 = 0 (table 11).

Table 11. Address Register Count Control (DPRAM-Indirect Addressing Mode)

| Accessed Data Register | CNTO        |   | ess Regis<br>Countin |   | CNT1 | DEC1 |

|------------------------|-------------|---|----------------------|---|------|------|

| PADR1/PBDR1            | PAAR1/PBAR1 | 0 | ×                    | х | х    | + 0  |

|                        |             | 1 | 0                    | х | x    | + 1  |

|                        |             | 1 | 1                    | x | x    | - 1  |

| PADRO/PBDRO            | PAARO/PBARO | × | x                    | 0 | x    | + 0  |

|                        |             | x | х                    | 1 | 0    | + 1  |

|                        |             | × | x                    | 1 | 1    | - 1  |

|                        |             |   |                      |   |      |      |

Note: x = Don't care

Figure 14. Sequence Control and FIFO Error Register

The lower 4 bits (F10, F1U, F00, F0U) indicate FIFO 1/0 overflow and underflow errors. After these errors are detected, the FIFO must be initialized using the F0FL and F1FL bits of the CMD register. These bits remain set until the FIFO is initialized until a reset occurs.

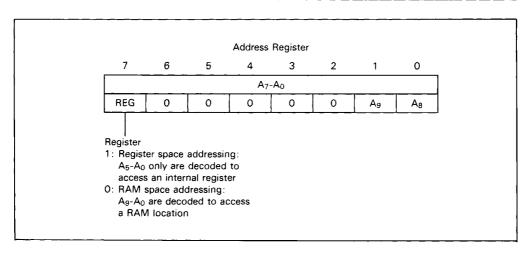

# Address Register (PAAR0, PBAR0, PAAR1, PBAR1)

The S-PDRAM has two address registers (figure 15) for each port. These registers specify the RAM or register address during

indirect addressing in DPRAM mode. The automatic address count is controlled by the CNT1, DEC1, CNT0, and DEC0 bits of the SCFE registers. In FIFO mode, these registers are used as the read/write pointers, and cannot be accessed externally.

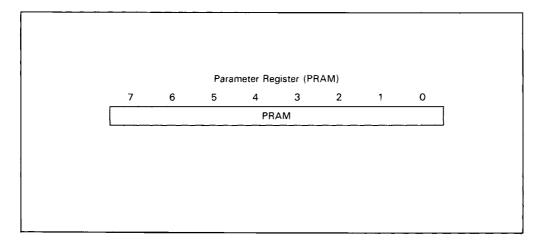

#### Parameter Registers (PRAM31-PRAM0)

The 32-byte PRAM registers PRAM31-PRAM0 (figure 16) are user definable registers. They can be used for passing parameters between ports, or for extra storage space. These registers are shared by both ports.

Figure 15. Address Register

Figure 16. Parameter Register

#### Reset

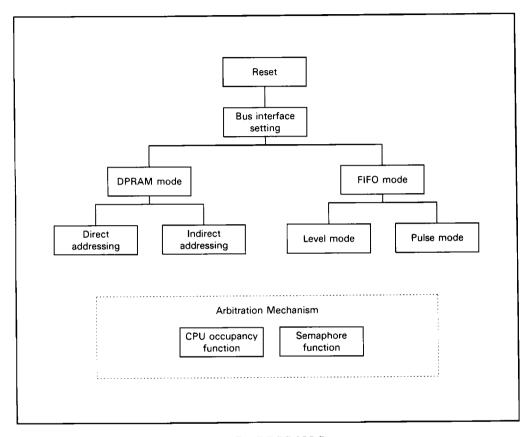

Figures 17 and 18 show the procedure for driving the S-DPRAM after reset.

Figure 17. S-DPRAM Setup

Figure 18. S-DPRAM Driving Procedure

The S-DPRAM performs two types of reset operations: hardware reset due to an external signal assertion and software reset due to a command setting (table 12).

- Hardware reset: Asserting the RESET input places the S-DPRAM into the initial state. Hardware reset is used for system initialization such as power-on reset, and must be performed after applying power.

- Software reset: Writing a 1 into the RST bit of the CMD register of either port initializes the device. Software reset does

not affect the interrupt flags (AP1 and AP0 of CMD register or ATT1 and ATT0 of ISRC register).

Owing to this architecture, the S-DPRAM can recognize an interrupt request from the opposite port even after reset.

The S-DPRAM is set to the status shown intable 12 after initialization, and is therefore operable immediately after reset in a normal interface system.

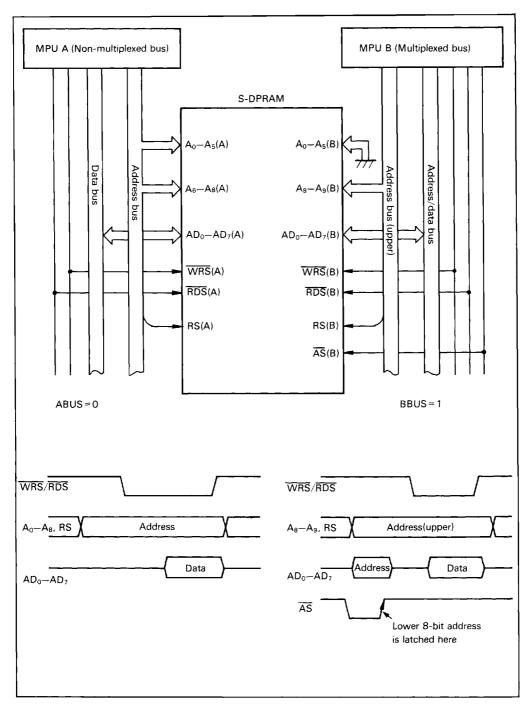

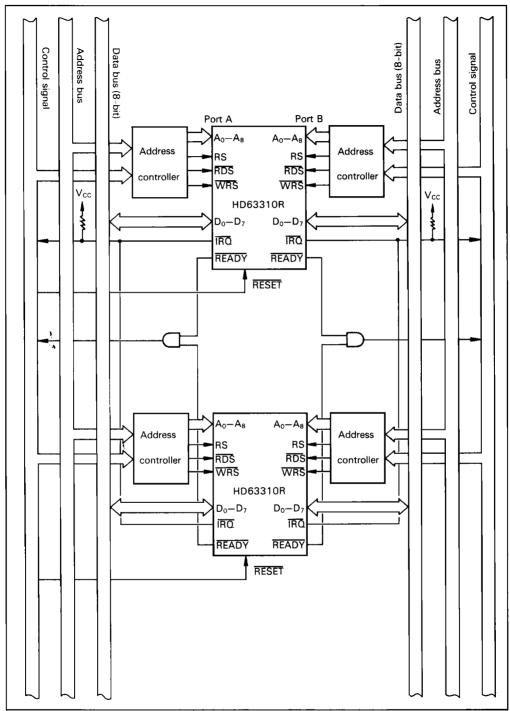

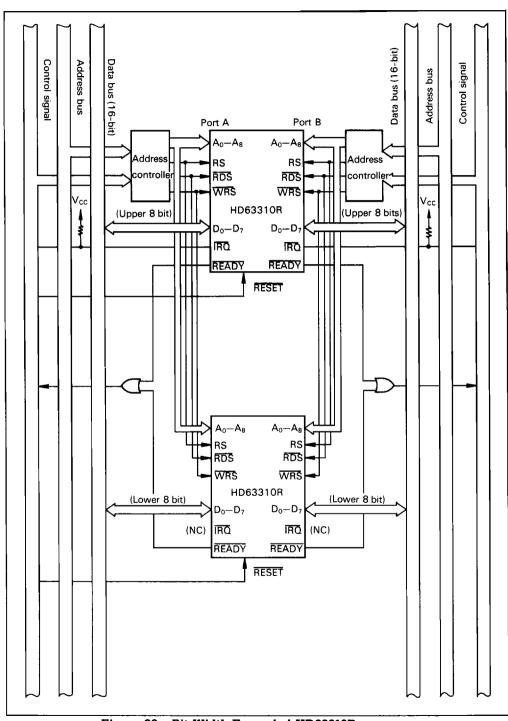

#### **Bus Interface**

Each port's I/O bus can be configured as a non-multiplexed or multiplexed address and data bus. Non-multiplexed mode is selected when ABUS/BBUS bit of the CNFG register is set to 0, and multiplexed mode when it is 1. In the bus connection example of figure 19, port A is configured as a non-multiplexed bus and port B as a multiplexed bus.

In multiplexed mode, the lower address is input via address data pins  $AD_0$ - $AD_7$ . Therefore, address pins  $A_0$ - $A_5$  of  $A_0$ - $A_7$  are left

unused.  $A_6$  and  $A_7$ , which are multipurpose lines, are switched to  $A_8$  and  $A_9$  and used as input pins for the upper address. It should be noted that the unused  $A_0$ - $A_5$  must be connected to GND. Since the S-DPRAM is set to non-multiplexed mode after initialization, the CNFG register must be accessed first to have the I/O bus multiplexed. If  $A_0$ - $A_5$  are set to 0 by connecting them to GND, the CNFG register at register address 00 is automatically selected by asserting  $\overline{WRS}$  or  $\overline{RDS}$ . Therefore, RS must be set high.

Table 12. S-DPRAM Status After Reset

| Item                  | Status                                                                                                                                                                                      |       |      |           |          |               |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------|----------|---------------|--|--|

| Internal register     | Refer to table 3 "Internal Register: Bit Configuration and Operation"  Not affected                                                                                                         |       |      |           |          |               |  |  |

| RAM                   |                                                                                                                                                                                             |       |      |           |          |               |  |  |

| FIFO status flags     |                                                                                                                                                                                             | Empty | Full | Underflow | Overflow |               |  |  |

|                       | FIF01                                                                                                                                                                                       | 0     | 0    | 0         | 0        | Not Empty and |  |  |

|                       | FIF00                                                                                                                                                                                       | 0     | 0    | 0         | 0        | Not Full      |  |  |

| Terminal (both ports) | Multipurpose line $\{1\}$ : $A_6$ , Multipurpose line $\{2\}$ : $A_7$ , Multipurpose line $\{3\}$ : $A_8$ , Data bus $AD_0$ - $AD_7$ : high impedance IRQ: high impedance READY: high level |       |      |           |          |               |  |  |

| Operation mode        | Mode: DPRAM mode Bus interface: non-multiplexed bus Access method: direct addressing method (bank = 0)                                                                                      |       |      |           |          |               |  |  |

Figure 19. Bus Connection Example

#### **Operation Mode**

Two types of operation modes can be programmed in the S-DPRAM: DPRAM mode and FIFO mode. DPRAM mode is selected when the RCFG field of the CNFG register is 000, and FIFO mode when it is other than 000.

(See table 5 "1024-Byte RAM Operation Mode and FIFO Size".) Please note that the registers may have various functions depending on the operation mode. Table 13 shows the bit configuration of registers in each mode.

Table 13. Bit Configuration of Internal Registers

DPRAM mode (RCFG = 000)

| Address Bit configuration |             |                                |      |                  |                        |                  |          |                |                |

|---------------------------|-------------|--------------------------------|------|------------------|------------------------|------------------|----------|----------------|----------------|

| Address                   | name        | 7                              | 6    | 5                | 4                      | 3                | 2        | 1              | 0              |

| R00                       | CNFG        | ABUS                           | BBUS |                  | RCFG                   |                  | 0        | , -            | _              |

| R01                       | CMD         | AP1                            | APO  | RST              | 0                      | 0                | 0        | _              | _              |

|                           |             |                                | ]    |                  |                        |                  |          | B1SL           | BOSL           |

| R02                       | IEN         | ENA7                           | ENA6 | ENA5             | ENA4                   | ENA3             | ENA2     | ENA1           | ENAO           |

| R03                       | ISRC        | ATT1                           | ATTO | RELE             | _                      | _                | _        |                | _              |

| R04                       | STS         | IRQ                            | 0    | 0                | 0                      | 0                | 0        | _              | _              |

|                           |             |                                |      |                  |                        |                  |          | B1EN           | BOEN           |

| R05                       | ARB         |                                |      |                  | Р                      | ID               | h        |                |                |

| R06                       | AQR         | OWN7                           | OWN6 | OWN5             | OWN4                   | оwиз             | OWN2     | OWN1           | OWNO           |

| R07                       | REL         | AVL7                           | AVL6 | AVL5             | AVL4                   | AVL3             | AVL2     | AVL1           | AVLO           |

| R08                       | PA/B DRO    |                                | ·    | D <sub>7</sub> – | D <sub>0</sub> (Indire | ect addres       | ssing)   |                |                |

| R09                       | PA/B DR1    |                                |      | D7-              | D <sub>0</sub> (Indire | ect addres       | ssing)   |                |                |

| ROA                       | FRC         | 0                              | T _  |                  | _                      | 0                | _        | _              | _              |

| ROB                       | SCFE        | CNT1                           | DEC1 | CNTO             | DECO                   | 0                | 0        | 0              | 0              |

| ROC                       | PA/B ARO(L) |                                | ·    |                  | Α7                     | - A <sub>0</sub> | <u> </u> |                | L              |

| ROD                       | PA/B ARO(H) | REG                            | 0    | 0                | 0                      | 0                | 0        | A <sub>9</sub> | A <sub>8</sub> |

| ROE                       | PA/B AR1(L) | A <sub>7</sub> -A <sub>0</sub> |      |                  |                        |                  | L        |                |                |

| ROF                       | PA/B AR1(H) | REG                            | 0    | 0                | 0                      | 0                | 0        | A <sub>9</sub> | A <sub>8</sub> |

| R10                       | PRAM        |                                |      |                  | PR                     | AM               |          | ·              |                |

| :                         |             |                                |      |                  |                        |                  |          |                |                |

| R2F                       | 1           |                                |      |                  |                        |                  |          |                |                |

FIFO mode (RCFG ≠ 000)

| Address | Register    | Bit configuration                                |        |          |                                 |                  |           |          |      |

|---------|-------------|--------------------------------------------------|--------|----------|---------------------------------|------------------|-----------|----------|------|

| Address | name        | 7                                                | 6      | 5        | 4                               | 3                | 2         | 1        | 0    |

| R00     | CNFG        | ABUS                                             | BBUS   |          | RCFG                            |                  | 0         | F1D      | FOD  |

| RO1     | CMD         | AP1                                              | APO    | RST      | 0                               | 0                | 0         | F1FL     | FOFL |

|         |             |                                                  | l      |          | Į                               |                  |           | _        |      |

| R02     | IEN         | ENA7                                             | ENA6   | ENA5     | ENA4                            | ENA3             | ENA2      | ENA1     | ENAO |

| R03     | ISRC        | ATT1                                             | ATTO   | _        | FERR                            | F1F              | F1E       | FOF      | FOE  |

| R04     | STS         | IRQ                                              | FRQ1   | FRQO     | FERR                            | F1F              | F1E       | FOF      | FOE  |

|         |             |                                                  | 1      |          |                                 |                  |           | _        | _    |

| RO5     | ARB         |                                                  |        |          | Р                               | ID               |           |          |      |

| R06     | AQR         | OWN7                                             | OWN6   | OWN5     | OWN4                            | OWN3             | OWN2      | OWN1     | OWNO |

| R07     | REL         | AVL7                                             | AVL6   | AVL5     | AVL4                            | AVL3             | AVL2      | AVL1     | AVLO |

| R08     | PA/B DRO    |                                                  | •      |          | D <sub>7</sub> – D <sub>0</sub> |                  |           |          |      |

| R09     | PA/B DR1    |                                                  |        |          | D <sub>7</sub>                  | - D <sub>0</sub> |           |          |      |

| ROA     | FRC         | 0                                                | FR1E   | FR1T     | FR1M                            | 0                | FROE      | FROT     | FROM |

| ROB     | SCFE        | -                                                | -      | _        | _                               | F10              | F1U       | F00      | FOU  |

| ROC     | PA/B ARO(L) |                                                  | FIFO ( | ): A=Rea | d pointer                       | (L), B=\         | Vrite poi | nter (L) |      |

| ROD     | PA/B ARO(H) | FIFO 0: A=Read pointer (H), B=Write pointer (H)  |        |          |                                 | nter (H)         |           |          |      |

| ROE     | PA/B AR1(L) | L) FIFO 1: A=Read pointer (L), B=Write pointer ( |        |          |                                 | nter (L)         |           |          |      |

| ROF     | PA/B AR1(H) | FIFO 1: A=Read pointer (H), B=Write pointer (H)  |        |          |                                 |                  |           |          |      |

| R10     | PRAM        |                                                  |        |          | PR                              | AM               |           |          |      |

| :       |             | i<br>i                                           |        |          |                                 |                  |           |          |      |

| R2F     |             |                                                  |        |          |                                 |                  |           |          |      |

Note: 0: Write causes no action, and read as 0 only.

-: Invalid in the specified operation mode.

#### **DPRAM Mode**

In DPRAM mode, 1024-byte RAM can be used as shared memory accessible from either port A or B. The address space accessible at a time differs depending on the bus interface configuration: non-multiplexed or multiplexed (table 15).

- Non-multiplexed mode: Up to 512 bytes can be addressed via A<sub>0</sub>-A<sub>8</sub>. All addresses are accessible due to bank switching by B1SL (upper) and B0SL (lower) bits of the CMD register.

- Multiplexed mode: Up to 1024 bytes can be addressed via AD<sub>0</sub>-AD<sub>7</sub>, A<sub>8</sub>, and A<sub>9</sub>. All addresses are accessible.

To increase efficiency in software development, two types of addressing methods are implemented: direct addressing and indirect addressing.

Direct Addressing Mode: In direct addressing mode, the target address is specified by externally supplied address signals and internal bank select bits B1SL and B0SL. When the I/O bus is non-multiplexed, bank select bit information is reflected on A<sub>9</sub>. Table 14 shows how the address space is specified by B1SL and B0SL and how its status is reflected on the B1EN and B0EN bits of the STS register.

Indirect Addressing Mode: In indirect addressing mode, the target address is obtained by accessing the data register. When the data register is accessed, the corresponding address register is referenced, and memory is accessed according to this information. Therefore, the target address must be written into the address register before accessing the data register.

Table 14. Direct Addressing Mode Address Space

| CMD Regis | ster Write |                    | STS Register Read |      |  |

|-----------|------------|--------------------|-------------------|------|--|

| B1SL BOSL |            | Address space      | B1EN              | BOEN |  |

| 0         | 0          | Not affected       | Not affected      | 1    |  |

| 0         | 1          | 000-1FF (lower)    | 0                 | 1    |  |

| 1         | 0          | 200-3FF (upper)    | 1                 | 0    |  |

| 1         | 1          | 000 - 1 FF (lower) | 0                 | 1    |  |

Table 15. DPRAM Mode Table (RCFG=000)

#### Address to be Accessed

| Addressing             | Bus interface   | RS | Address<br>inputs                                                   | Register                          | Associated Register                                                     |  |

|------------------------|-----------------|----|---------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------|--|

| Direct<br>Addressing   | Non-multiplexed | 0  | A <sub>0</sub> -A <sub>5</sub><br>A <sub>6</sub> -A <sub>8</sub>    | STS reg:<br>B1EN,<br>B0EN<br>(A9) | CMD reg: B1SL, B0SL<br>(for bank selection)                             |  |

|                        | Multiplexed     | 0  | AD <sub>0</sub> -AD <sub>7</sub><br>A <sub>8</sub> , A <sub>9</sub> | _                                 | _                                                                       |  |

| Indirect<br>Addressing | Non-multiplexed | 1  | A <sub>0</sub> -A <sub>5</sub><br>P(A/B) DR0<br>P(A/B) DR1          | _                                 | SCFE reg: CNT1, DEC1,<br>SCFE reg: CNT0, DEC0<br>(for address counting) |  |

|                        | Multiplexed     | 1  | AD <sub>0</sub> -AD <sub>5</sub><br>P(A/B) DRO<br>P(A/B) DR1        |                                   | PA/BARO, PA/BAR1 register (for address reference)                       |  |

Note: Refer to table 6 in the data register section for the relation between data register and address register in indirect addressing mode.

In indirect addressing mode, the address can be automatically incremented or decremented after each read/write access of the data register. Either increment, decrement, or no count can be selected by setting the SCFE register. This automatic address count function facilitates sequential memory access. In addition, two memory groups can be separately accessed because there are two channels of address registers for each port.

#### FIFO Mode

In FIFO mode, memory is configured as a buffer with first-in/first-out facilities. This mode is effective for sequential data communications between transmitter and receiver having different data transfer speeds. FIFO mode is selected when the RCFG field of the CNFG register equals any bit pattern from 001 to 111. In this mode, RAM is configured as two FIFOs. The size of each FIFO is determined by the RCFG field code (See table 5).

The FIFO-associated registers are listed in table 16. They are implemented for both ports independently. FIFOs 0 and 1 are separately controlled by these registers. The RCFG field and FERR bit are shared by FIFO 0 and 1, while the others are respectively provided for each FIFO.

Indirect addressing mode is disabled in FIFO mode, since the address registers are used for FIFO read/write pointers. Therefore, the opposite port's registers are not accessible in this mode. Refer to the subsection "Special FIFO Mode Application" for access to the opposite port's registers.

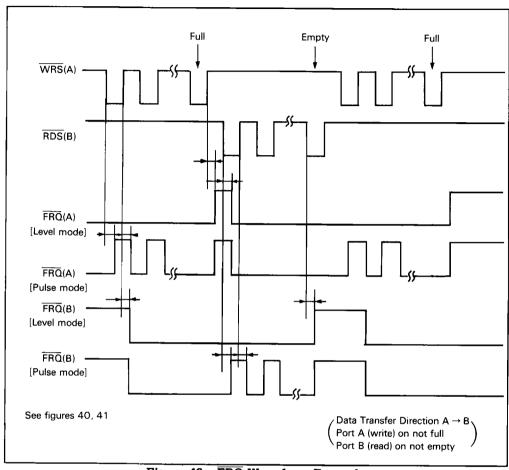

The S-DPRAM  $\overline{FRQ}$  output signal represents FIFO status. The multipurpose line functions as  $\overline{FRQ}$  in FIFO mode. The FRC register controls the following with respect to  $\overline{FRQ}$ : output enabled or disabled, assertion condition, and output waveform mode. In particular, for output waveform mode, either level mode or pulse mode can be selected depending on the system used.

Table 16. FIFO-Associated Registers

#### **Associated Bit**

| Register Name              | FIFO 0                       | FIFO 1                       | Function                                           |  |  |

|----------------------------|------------------------------|------------------------------|----------------------------------------------------|--|--|

| CNFG                       | RCFC                         | 3                            | FIFO configuration (001 – 111)                     |  |  |

|                            | FOD                          | F1D                          | FIFO data transfer direction                       |  |  |

| CMD (A/B)                  | FOFL                         | F1FL                         | FIFO initialization                                |  |  |

| STS (A/B)                  | FRQO                         | FRQ1                         | FRQ <sub>0</sub> & FRQ <sub>1</sub> outputs status |  |  |

|                            | FERF                         | }                            | FIFO error status                                  |  |  |

|                            | FOF, FOE                     | F1F, F1E                     | FIFO full or empty                                 |  |  |

| ISRC (A/B)                 | FERF                         | }                            | FIFO error status                                  |  |  |

|                            | FOF, FOE                     | F1F, F1E                     | FIFO full or empty                                 |  |  |

| FRC (A/B)                  | FROE, FROT, FROM             | FR1E, FR1T, FR1M             | FRQ <sub>0</sub> , FRQ <sub>1</sub> mode setting   |  |  |

| SCFE (A/B)                 | FOO, FOU                     | F10, F1U                     | FIFO overflow or underflow                         |  |  |

| Read/write register        | PADRO (Note)<br>PBDRO (Note) | PADR1 (Note)<br>PBDR1 (Note) | Data register to be accessed                       |  |  |

| Read pointer write pointer | PAARO (Note)<br>PBARO (Note) | PAAR1 (Note)<br>PBAR1 (Note) | Address reg to be referenced                       |  |  |

Note: Register name

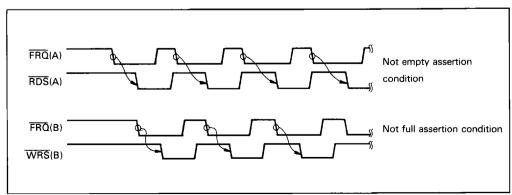

Level Mode: Level mode is selected when the FR1M or FR0M bit of the FRC register is set to 0. In this mode, FRQ is asserted continuously as long as the assertion condition defined by FR1T or FR0T remains true. In level mode, data transfer is allowed if only the detected FRO level is low. Example 1 shows a handshaking protocol realized using this mode.

Example 1:

FIFO partition: FIFO 1 (1024 bytes)

.....RCFG = 010

Data transfer direction: Port A to B  $\cdots F1D = 1$

Output enable: FRQ1 output enabled

$\cdots FR1E = 1$ Waveform mode: Level mode.....FR1M = 0

Threshold:  $A = Empty, B = Full \cdots FR1T = 1$

Port A

- (1) FRO is asserted and FIFO is judged to be empty. (2) CPU writes up to 1024 bytes of

- data into FIFO (3) Wait until the next assertion.

- (1) FRQ is asserted and FIFO is judged to be full.

Port B

(2) CPU reads up to 1024 bytes of data from FIFO

(3) Wait until the next assertion.

Data transfer is carried out by repeating procedures (1) to (3). A different handshaking protocol uses different threshold conditions.

Example 2:

Threshold: A = Not full, B = Not empty $\cdots FR1T = 0$

(Other conditions are the same as those in example 1)

(1) FRO is asserted and FIFO is judged to be not full.

Port A

(2) Write access continues until FRO is negated (until FIFO becomes full)

(1) FRQ is asserted and FIFO is judged to be not empty.

Port B

(2) Read access continues until FRQ is negated (until FIFO becomes empty)

Data transfer is carried out by repeating procedures (1) to (2).

Notes for HD63310R interface: The FRQ signal of the HD63310R is negated after it completes the WRS cycle, and therefore FRO acknowledge timing must be specified after WRS cycle completion. In general, trally, the FRO negation delay time at write access, is 150 ns. Taking the delay due to access contention into account, at least 400 ns of delay is required after WRS negation.

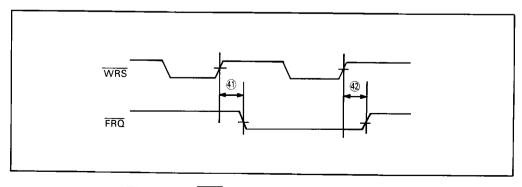

Pulse Mode: Pulse mode is selected when the FR1M or FR0M bit of the FRC register is set to 1. In this mode, FRO is asserted and negated repeatedly each time a data transfer occurs as long as the assertion condition defined by FR1T or FR0T remains true. In pulse mode, handshaking takes place by detecting the falling edge of FRO (figure 20).

Example:

FIFO partition: FIFO 0 (1024 bytes) ..... RCFG = 001 Data transfer direction: Port B to A  $\cdots FOD = 0$ Output enable: FRQ0 output enabled ..... FROE = 1

Figure 20. Pulse Mode Handshaking

Waveform mode: Pulse mode

......FR0M = 1

Threshold: A = Not empty, B = Not full

.....FR0T = 0

Port A— Reads 1-byte of data from FIFO upon each assertion of  $\overline{FRQ}$

Port B— Writes 1-byte of data into FIFO upon each assertion of  $\overline{FRQ}$

In pulse mode, handshaking is performed by detecting the falling edge of  $\overline{FRQ}$ , and therefore special timing is not required. In addition, overrun (excessive write/read access) due to  $\overline{FRQ}$  delay as in level mode cannot occur, since the falling pulse count agrees with the transfer byte count in this mode.

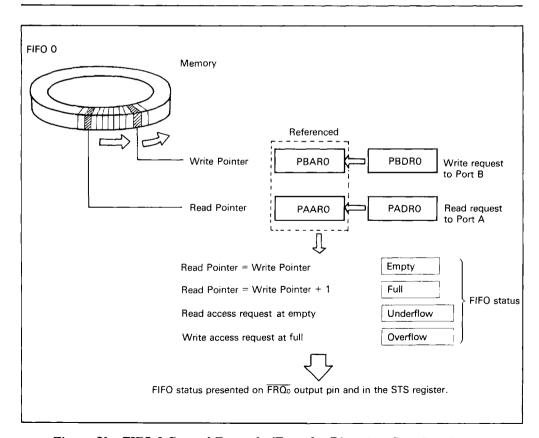

FIFO Operation: Figure 21 illustrates an example of FIFO operation. In FIFO mode,

RAM is configure as two ring-shaped memories. Each memory has read/write pointers and thus can be accessed independently. The PBAR (0/1) and PAAR (0/1) registers, used in indirect addressing DPRAM mode, are assigned here as write pointer and a read pointer, respectively. These pointers are automatically incremented upon each access. During write access, a write pointer is incremented after writing data into the address indicated by the write pointer. In the same way, a read pointer is incremented after reading data from the address indicated by the read pointer. When a write pointer value equals a read pointer value, FIFO memory is considered to be empty. When a write pointer value exceeds a read pointer value by one, FIFO memory is considered to be full. These FIFO statuses are represented by the status bits of internal registers or are output via the FRO line.

Figure 21. FIFO 0 Control Example (Transfer Direction: Port B to Port A)

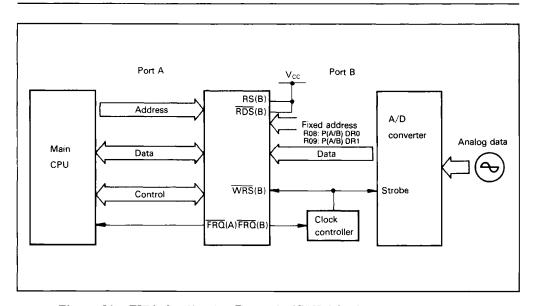

Special FIFO Mode Application: The S-DPRAM has been basically designed as an interface between CPUs. Therefore, there are some limitations when it is used with non-intelligent devices. In particular, when the S-DPRAM is used in FIFO mode, some registers must be set and therefore the S-DPRAM cannot support an interface between non-intelligent devices.

Figure 22 shows an example of an interface between a CPU and non-intelligent device. In this example, the CPU reads sequential digital data that is converted from analog data through synchronous sampling with a clock; the digital data is then stored into FIFO. Moreover, the FIFO status is returned to the A/D converter via the FRQ line. The S-DPRAM performs handshaking by referring to this signal's status.

- Non-intelligent device setting: The address bus must be fixed to the address of the data register of the FIFO being used. RS and RDS must be set to high, and the sampling clock for A/D conversion must be input to WRS. This clock circuit must be controlled using FRQ.

- Register setting: Through the non-intelligent device's port, only the data register is accessible, and therefore each register must be set through the CPU's port. The opposite port's registers can be accessed using the indirect addressing method, but in FIFO mode this method cannot be used. Accordingly, the S-DPRAM must be placed in FIFO mode after the FIFO-associated registers of the opposite port are set using the indirect addressing method in DPRAM mode.

Figure 22. FIFO Application Example (CPU-A/D Converter Interface)

**General Notes for FIFO Mode:** Keep the following in mind when operating in FIFO mode.

- Mode Transition: Switching from DPRAM

or FIFO operation mode does not affect

the contents of registers or RAM. The FIFO

status flag is reset upon transition from

FIFO mode to DPRAM mode. However,

when the address that will result in empty

or full status is stored in DPRAM mode, the

FIFO status flag is not set even if the SDPRAM is switched to FIFO mode.

- 2. Underflow and overflow: Attempting a read access after empty status causes an underflow and invalid data is read out. The read pointer is incremented and the empty flag is reset. In the same way, a write access after full status causes an overflow and data at the bottom of the stack is destroyed. The write pointer is incremented and the full flag is reset.

- 3. Data transfer direction: When data access against the transfer direction specified by CNFG is requested, flags and FIFO operation are not affected except that input and output are replaced by each other. That is, when A to B direction is specified, a write access to port B results in a successful data write to B, and a read access from port A results in a successful data read from A; internal operation is not affected. However, it should be noted that the FRO output condition is reversed.

- FIFO partitioning and addresses: Table 17 shows how memory addresses are allocated corresponding to FIFO partitions.

#### Arbitration

The S-DPRAM arbitration function supports multiprocessor systems. It facilitates effective data communications between multiple CPUs on one system bus or between two system buses. There are two arbitration methods:

Software arbitration by register flag control

Hardware arbitration by an internal arbiter

This section describes the software arbitration control method. Hardware arbitration will be described later in the section about internal operation.

The S-DPRAM incorporates the following

registers for interprocessor arbitration: arbitration register (ARB), acquire ownership register (AQR), and release/available register (REL). These registers only act as flags to control interprocessor arbitration, and are not directly related to S-DPRAM operations. Accordingly, they are designated as a flag register group and clearly distinguished from the special control register (SCR) group and address/data register group.

These registers are used for two types of arbitration: CPU occupancy or semaphore function, depending on the architecture of the multiprocessor system (table 18).

Table 17. FIFO Memory Addresses

| RCFG |            |           | Memory address |             |  |  |

|------|------------|-----------|----------------|-------------|--|--|

| b5   | <b>b</b> 4 | <b>b3</b> | FIFO 1         | FIFO 0      |  |  |

| 0    | 0          | 1         |                | 000-3FF     |  |  |

| 0    | 1          | 0         | 000-3FF        | _           |  |  |

| 0    | 1          | 1         | 200-3FF        | 000 - 1 F F |  |  |

| 1    | 0          | x         | 300-3FF        | 000-2FF     |  |  |

| 1    | 1          | x         | 100-3FF        | 000-0FF     |  |  |

#### **CPU Occupancy Function**

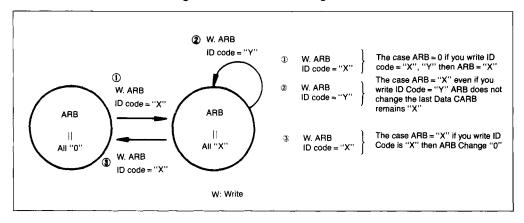

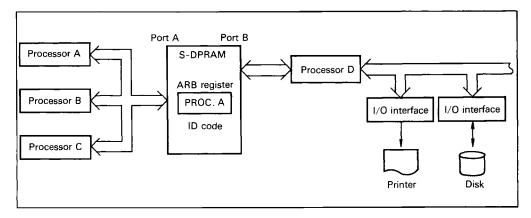

In a system having several processors on one system bus (multimaster bus system), each processor can acquire ownership of the system bus, and thus there may be contention for control of a shared resource (I/O, memory, etc). To avoid this contention, the S-DPRAM uses the ARB register to indicate which processor currently controls the shared resource. Figure 23 shows an example of a multiprocessor system configuration. In this system, processor A, B, and C, on one system bus, are connected with processor D via the S-DPRAM, sharing the I/O devices. For one of processors A, B, and C to drive the I/O controller normally, one processor must occupy the I/O device for a specific period. The following procedure gives processor A control of the printer (figure 24).

Processor A writes its ID code into the ARB register to acquire bus ownership of port

- A. After acquiring the bus ownership, processor A starts to transfer data to processor D dia the S-DPRAM, and then processor D drives the printer.

- Since processor A performs data output on a page basis, there is an interval between one page and another when no data transfer is executed. The system bus is released to the other processors so as not to decrease system throughput.

- However, during this interval, if processor B attempts to write its ID code into ARB, it is rejected because ARB already has the ID code of processor A (figure 25). Thus, this effective arbitration mechanism prevents processor B from using the S-DPRAM.

- 4. Thereafter, the bus ownership is returned to processor A and data transfer is resumed. After finishing a series of processes, processor A clears ARB by writing its ID code into ARB again, and bus ownership is then released.

Table 18. Arbitration Function

|                              | Related<br>Register                                                        | Mode          | Function              | Application                                                                                        |

|------------------------------|----------------------------------------------------------------------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------|

| CPU<br>occupancy<br>function | ARB<br>(Arbitration<br>ownership<br>register)                              | DPRAM<br>FIFO | •                     | Determines which CPU among multiple CPUs on one system bus can acquire the shared resource S-DPRAM |

| Semaphore function           | AQR, REL<br>(Acquire/<br>ownership,<br>release/<br>available<br>registers) | DPRAM         | indicates that the S- | Determines which CPU on<br>which system bus can<br>acquire the shared resource<br>S-DPRAM          |

Figure 23. Multiprocessor System Configuration Example (CPU Occupancy Function)

W. ARB

ID code = "X"

ARB = All 0

W. ARB

ID code = "X"

ARB = "X"

Arbitration between

CPUs on One System Bus

W. ARB

ID code = "Y"

Figure 25. ARB Register Status Transition

# 5

#### Semaphore Function

For a system sharing a resource between two system buses, the S-DPRAM AQR (acquire ownership) and REL (release/available) registers arbitrate access contention in the case of simultaneous requests from both ports. These registers have the following functions and are used as a pair.

- AQR register: Represents ownership of one port against the opposite port

- REL register: Relinquishes the acquired ownership

The AQR register implements "test and set" logic circuit in hardware. "Test" logic checks the current ownership status of a resource, and "set" logic establishes the ownership of a resource before it can be acquired by another requestor.

Each register provides eight semaphores, which can discrete control eight shared resources. For instance, if 1024-byte memory is divided into eight areas, each area can be represented by a corresponding semaphore bit.