# **TPIC82000 Series Tire Pressure Monitoring System TX Module**

# **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Literature Number: SLDS189 May 2012

# **Contents**

| 1 | INTR  | ODUCT    | ION                |                                                    | . <u>6</u> |

|---|-------|----------|--------------------|----------------------------------------------------|------------|

|   | 1.1   | Feature  | s                  |                                                    | . <u>6</u> |

|   | 1.2   |          |                    | n                                                  |            |

| 2 | PIN C | CONFIG   | URATION            | AND DESCRIPTIONS                                   | . <u>8</u> |

|   | 2.1   | Pin Cor  | figuration .       |                                                    | . 8        |

|   | 2.2   | Pin Des  | criptions          |                                                    | . 8        |

|   | 2.3   |          |                    | cuits                                              |            |

| 3 | FUNC  | CTION D  | ESCRIPT            | TON                                                | <u>13</u>  |

|   | 3.1   | Function | nal Block D        | Diagram (Whole Device)                             | <u>13</u>  |

|   | 3.2   | MCU80    | 51 core            |                                                    | <u>13</u>  |

|   |       | 3.2.1    | Memory F           | Resource Map                                       | <u>14</u>  |

|   |       | 3.2.2    | Program            | Code Memory (ROM)                                  | <u>14</u>  |

|   |       | 3.2.3    |                    | Pata Memory (RAM)                                  |            |

|   |       | 3.2.4    |                    | Special Function Registers (ESFR)                  | _          |

|   |       |          | 3.2.4.1            | ESFR Table                                         |            |

|   |       |          | 3.2.4.2            | ESFR Table (Continued)                             |            |

|   |       |          | 3.2.4.3            | ESFR Table (Continued)                             |            |

|   |       | 3.2.5    | -                  | ackup External-RAM (BuRAM)                         | _          |

|   |       |          | 3.2.5.1            | CRC (Cyclic Redundancy Check) Generator Function   | _          |

|   |       |          | 3.2.5.2            | BuRAM with CRC Generator Block Diagram             | _          |

|   |       |          | 3.2.5.3            | 8-bit CRC Polynomial Expression                    |            |

|   |       |          | 3.2.5.4            | Timing Chart of CRC Calculation from Start Address |            |

|   |       |          | 3.2.5.5            | Timing Chart of CRC Calculation at the End Address |            |

|   |       |          | 3.2.5.6            | Battery Backup External-RAM (BuRAM) Control ESFR   |            |

|   |       | 3.2.6    |                    | ile EEPROM                                         | _          |

|   |       |          | 3.2.6.1            | EEPROM Block Diagram                               |            |

|   |       |          | 3.2.6.2            | EEPROM Unit Structure and DATA/ECC Implementation  |            |

|   |       |          | 3.2.6.3            | EEPROM Programming Procedure                       |            |

|   |       | 0.07     | 3.2.6.4            | EEPROM Control ESFR                                |            |

|   |       | 3.2.7    |                    | 1 Registers                                        |            |

|   |       |          | 3.2.7.1<br>3.2.7.2 | MCU8051 Core SFR Map                               |            |

|   |       |          |                    | I/O PORT (P0,P1,P2,P3)                             |            |

|   |       |          | 3.2.7.3<br>3.2.7.4 | Stack Pointer (SP)                                 | _          |

|   |       |          | 3.2.7.4            | Data Pointer (DPTR)                                |            |

|   |       |          | 3.2.7.5            | Timer/Counter Registers                            |            |

|   |       |          | 3.2.7.0            | UART Registers                                     |            |

|   |       |          | 3.2.7.8            | Interrupt Registers                                |            |

|   |       |          | 3.2.7.9            | Program Status Word (PSW)                          |            |

|   |       |          | 3.2.7.10           | Accumulator (ACC)                                  |            |

|   |       |          | 3.2.7.10           | B Register (B)                                     |            |

|   |       | 3.2.8    |                    | n Definitions                                      |            |

|   |       | 0.2.0    | 3.2.8.1            | Addressing Modes                                   | _          |

|   |       |          | 3.2.8.2            | Arithmetic Instructions                            |            |

|   |       |          | 3.2.8.3            | Logic Instructions                                 | _          |

|   |       |          | 3.2.8.4            | Data Transfers                                     |            |

|   |       |          | 3.2.8.5            | Jump Instructions                                  |            |

|   |       |          | 3.2.8.6            | Boolean Instructions                               |            |

|   |       |          | 3.2.8.7            | Flags                                              | _          |

|   |       |          | 3.2.8.8            | Instruction Table                                  |            |

|   | 3.3   | System   |                    | ntroller and Status Monitor                        | _          |

|   | 0.0   | 0,00011  | . 55. 501          |                                                    |            |

www.ti.com

SLDS189 – MAY 2012

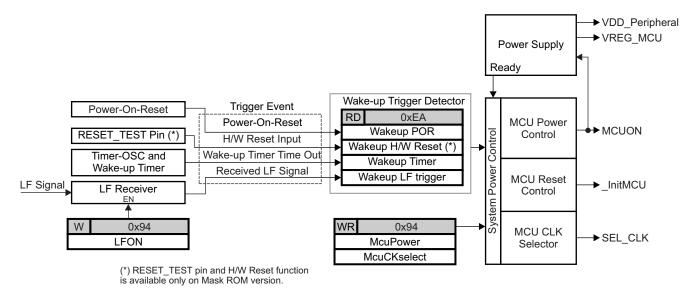

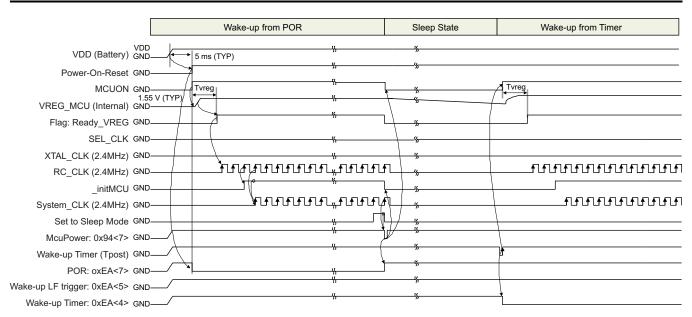

|   |      | 3.3.1    | System Power Block Diagram                                  | <u>43</u> |

|---|------|----------|-------------------------------------------------------------|-----------|

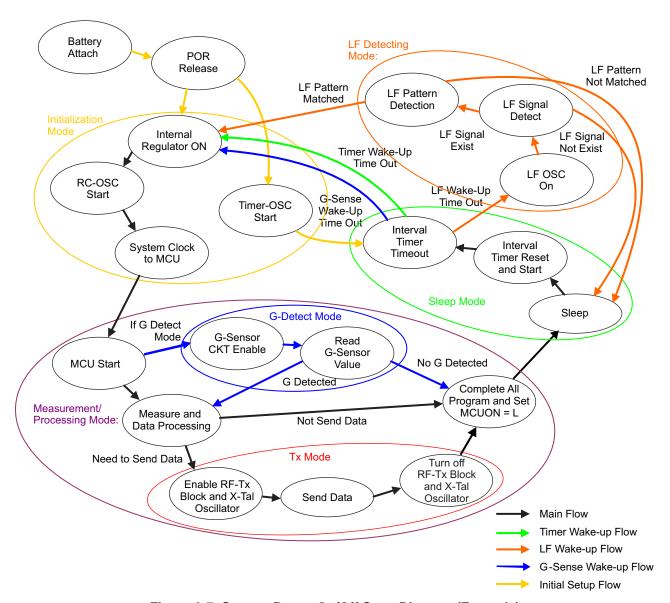

|   |      | 3.3.2    | System Wake-up Operation                                    | <u>43</u> |

|   |      | 3.3.3    | System Power Control ESFR                                   | <u>46</u> |

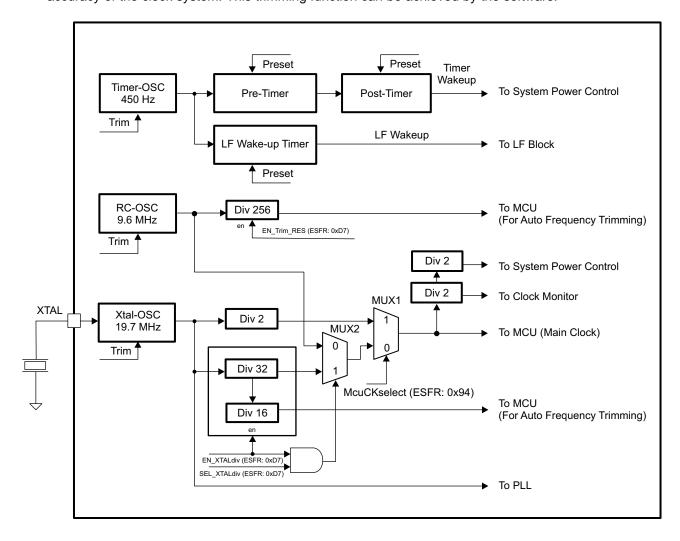

|   | 3.4  | Internal | Clocks System                                               | <u>47</u> |

|   |      | 3.4.1    | Internal Clock System Block Diagram                         | <u>47</u> |

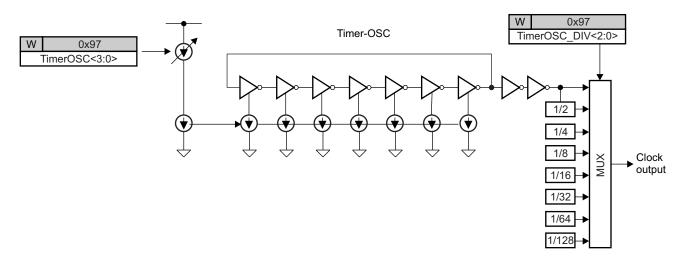

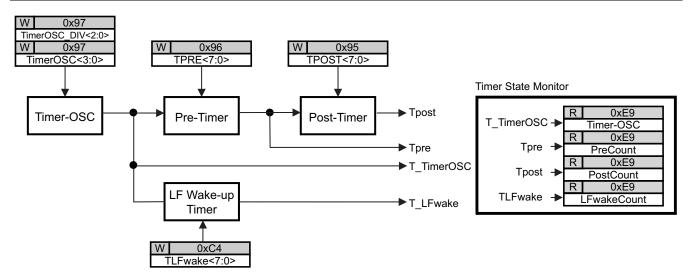

|   |      | 3.4.2    | Timer Oscillator (Timer-OSC)                                | <u>48</u> |

|   |      |          | 3.4.2.1 Interval Timer                                      | <u>49</u> |

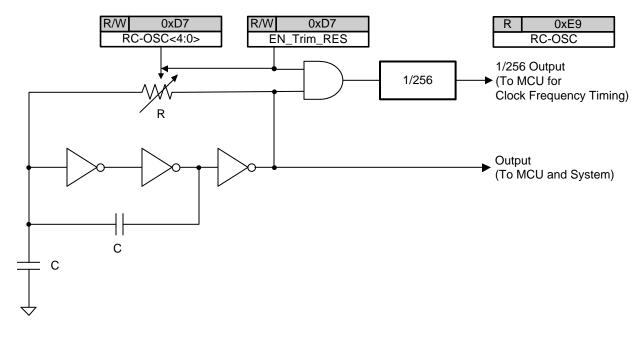

|   |      | 3.4.3    | RC Oscillator (RC-OSC)                                      | <u>51</u> |

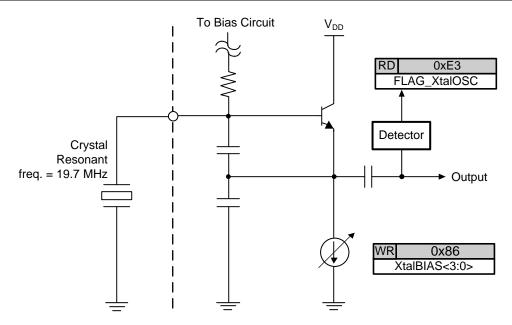

|   |      | 3.4.4    | Crystal Oscillator                                          | <u>52</u> |

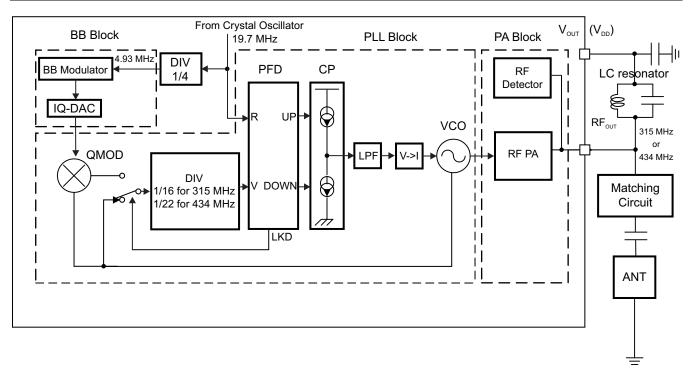

|   | 3.5  | RF Trar  | nsmitter                                                    | <u>53</u> |

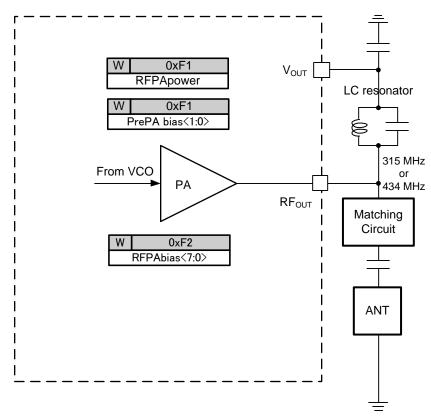

|   |      | 3.5.1    | RF Power Amplifier                                          | <u>54</u> |

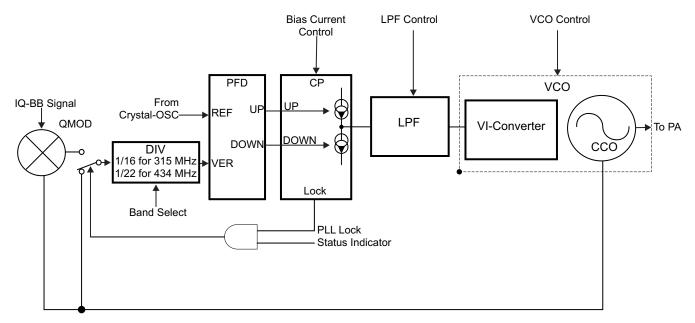

|   |      | 3.5.2    | PLL Block                                                   | 56        |

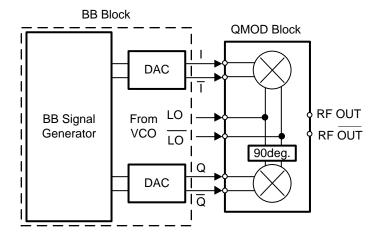

|   |      | 3.5.3    | 315/434MHz Dual-band Quadrature Modulator (QMOD)            | 56        |

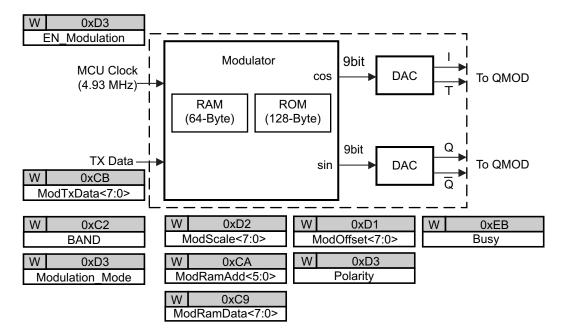

|   |      | 3.5.4    | Baseband Block (BB block)                                   | 57        |

|   | 3.6  | LF Rece  | eiver                                                       | 62        |

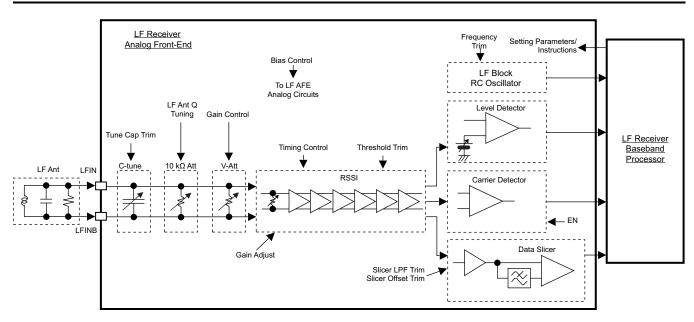

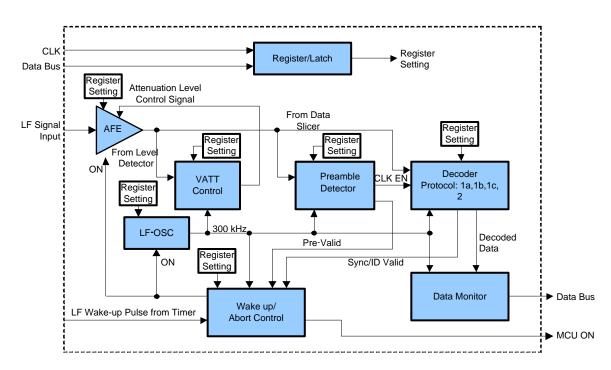

|   |      | 3.6.1    | LF AFE                                                      | 62        |

|   |      | 3.6.2    | LF Baseband Processor                                       | 63        |

|   |      | 3.6.3    | LF Pattern                                                  | 63        |

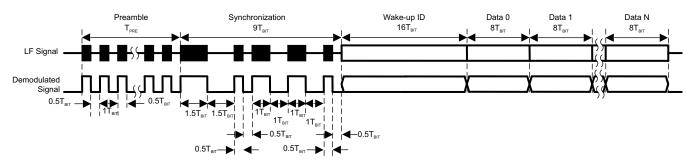

|   |      |          | 3.6.3.1 Protocol 1a                                         |           |

|   |      |          | 3.6.3.2 Protocol 1b                                         | _         |

|   |      |          | 3.6.3.3 Protocol 1c                                         |           |

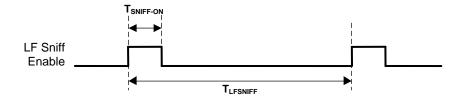

|   |      |          | 3.6.3.4 Protocol 1 Total Sniffing Abort Time                |           |

|   |      |          | 3.6.3.5 Protocol 1 Data Pattern Setting                     |           |

|   |      |          | 3.6.3.6 Protocol 2                                          | _         |

|   | 3.7  | Sensor   |                                                             |           |

|   | 3.8  |          | Mode                                                        |           |

|   |      | 3.8.1    | ESFR                                                        |           |

| 4 | ELEC | TRICAL   | SPECIFICATIONS                                              |           |

|   | 4.1  |          | e Maximum Ratings                                           |           |

|   | 4.2  |          | mended Operating Conditions                                 |           |

| 5 | ELEC |          | _ CHARACTERISTICS                                           |           |

|   | 5.1  |          |                                                             |           |

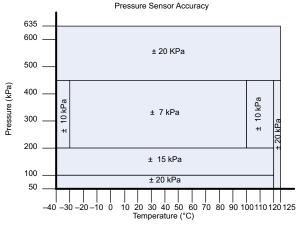

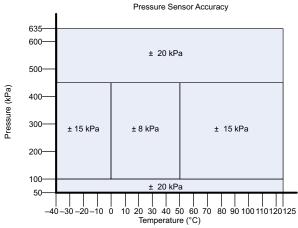

|   |      | 5.1.1    | Pressure Sensor (Selection A) for (50 kPa to 635 kPa Range) |           |

|   |      | 5.1.2    | Pressure Sensor (Selection B) for (50 kPa to 635 kPa Range) |           |

|   |      | 5.1.3    | Temperature / Voltage / Acceleration Sensor                 |           |

|   | 5.2  |          | Supply                                                      | _         |

|   | 5.3  |          | C                                                           |           |

|   | 5.4  |          |                                                             |           |

|   | 5.5  |          | DSC                                                         |           |

|   | 5.6  |          | z RC-OSC                                                    |           |

|   | 5.7  |          | fulator and RF PA                                           | _         |

|   | 5.8  |          | eiver                                                       |           |

|   | 5.9  |          | Regulator (VREG)                                            |           |

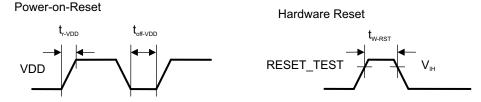

|   | 5.10 | •        | on-Reset and Hardware Reset                                 |           |

|   | 5.11 |          | M                                                           | _         |

|   |      |          |                                                             |           |

# List of Figures

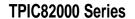

| 2-1  | Top View from Diaphragm                                                           | 8         |

|------|-----------------------------------------------------------------------------------|-----------|

| 3-1  | ESFR Table (Address FF–D8)                                                        | <u>16</u> |

| 3-2  | ESFR Table (Address D7–AC)                                                        | <u>17</u> |

| 3-3  | ESFR Table (Address AB-80)                                                        | 19        |

| 3-4  | CRC Generator 8-bit Polynomial Expression                                         | <u>20</u> |

| 3-5  | System Power Controller and Status Monitor                                        | 43        |

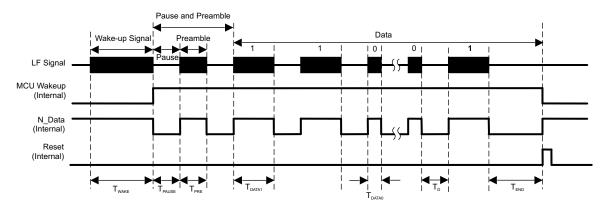

| 3-6  | System Wake-up Timing                                                             | <u>45</u> |

| 3-7  | System Power On/Off State Diagram (Example)                                       | 45        |

| 3-8  | Crystal Oscillator Block Diagram                                                  | <u>53</u> |

| 3-9  | 315/434MHz Transmitter Block Diagram                                              | <u>54</u> |

| 3-10 | RF PA Block                                                                       | <u>55</u> |

| 3-11 | PLL Block                                                                         | <u>56</u> |

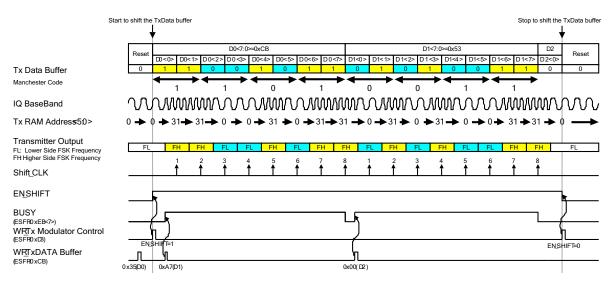

| 3-12 | Timing Diagram of 1-Byte FSK Data Transmission                                    | <u>60</u> |

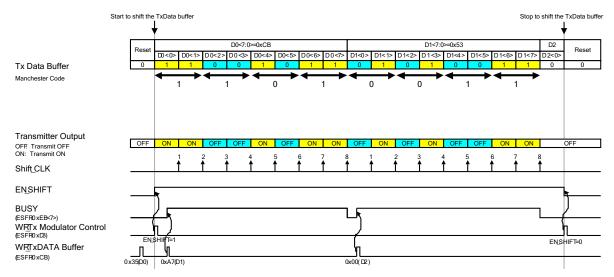

| 3-13 | Timing Diagram of 1-Byte ASK Data Transmission                                    | <u>60</u> |

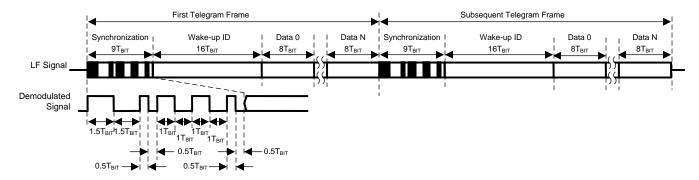

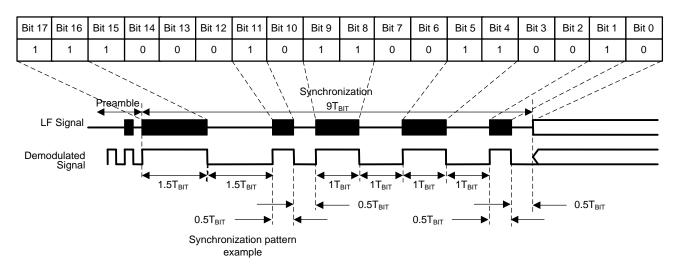

| 3-14 | LF Protocol 1a Pattern Example                                                    | 65        |

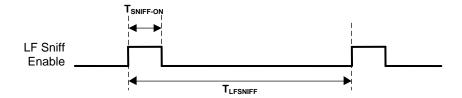

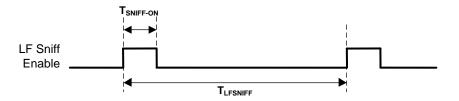

| 3-15 | LF Sniffing Timing                                                                | <u>65</u> |

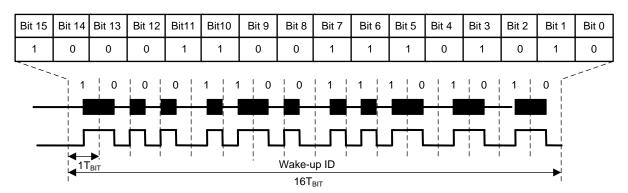

| 3-16 | Protocol 1b Pattern Example                                                       | 66        |

| 3-17 | LF Sniffing Timing                                                                | 66        |

| 3-18 | Protocol 1c Pattern Example                                                       | <u>67</u> |

| 3-19 | LF Sniffing Timing                                                                | <u>67</u> |

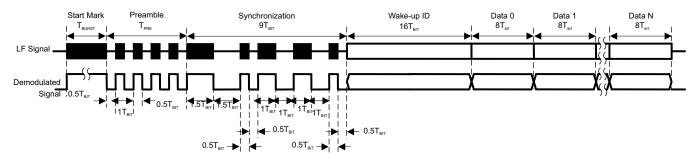

| 3-20 | Synchronization Pattern Example                                                   | 68        |

| 3-21 | Wake-up ID Pattern Example                                                        | <u>69</u> |

| 3-22 | Protocol 2 Example                                                                | <u>69</u> |

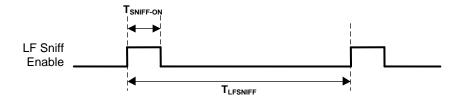

| 3-23 | LF Sniffing Timing                                                                | <u>70</u> |

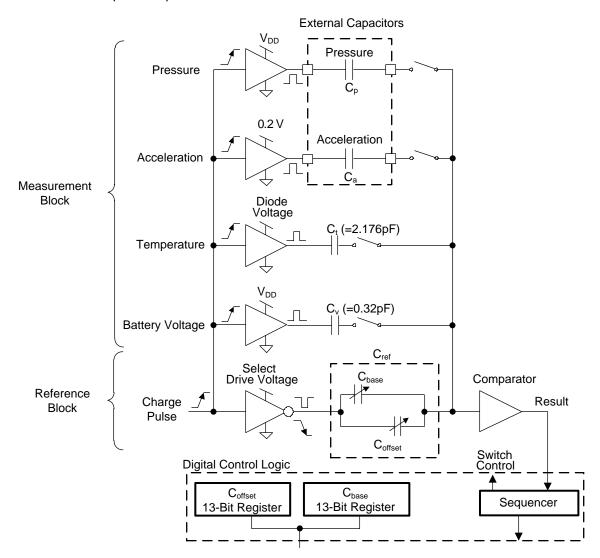

| 3-24 | 13-bit SAR-ADC Sensor Block Diagram                                               | <u>77</u> |

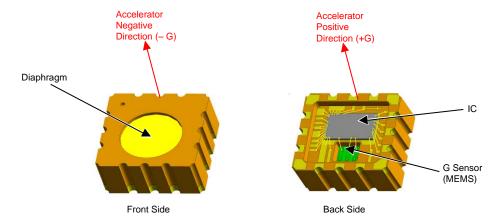

| 4-1  | Relationship Between Package Diaphragm Side and Accelerator Measurement Direction | 84        |

| 5-3  | Power-on-Reset and Hardware Reset                                                 | 89        |

# **List of Tables**

| 3-1 | Flags Instructions                             | 39 |

|-----|------------------------------------------------|----|

| 3-2 | Instruction Table                              | 40 |

| 3-3 | Protocol 1a (Manchester Coding) Timing Example | 6  |

| 3-4 | Protocol 1b (Manchester Coding) Timing Example | 6  |

| 3-5 | Protocol 1c (Manchester Coding) Timing Example | 68 |

| 3-6 | Protocol 2 (PWM) Timing Example                | 70 |

# **Tire Pressure Monitoring System TX Module**

Check for Samples: TPIC82000 Series

#### 1 INTRODUCTION

#### 1.1 Features

- Operating Voltage Range: 1.5 V to 3.5 V (315 MHz), 1.75 V to 3.5 V (434 MHz)

- Operating Temperature Range: –40°C to 125°C

- Low Current Consumption to Support a Coin Size Lithium Battery Operation

- In Package Pressure Sensor (Operation Range: 50 kPa to 635 kPa)

- In Package Accelerometer

- On Chip Temperature Sensor

- On Chip Battery Voltage Sensor

- 13-bit ADC for Sensors

- Dual Band 315/434 MHz Transmitter With One Crystal Oscillator

- Fully Integrated PLL Synthesizer

- ASK/FSK Baseband Modulator for 10K bits/s Manchester/BiPhase Coding, Capable up to 20K bits/s for FSK

- Dual Band Quadrature Modulator for Transmit Frequency Tuning (~ ±700 kHz)

- 125 kHz LF ASK Receiver (4K bits/s Manchester/BiPhase Code)

- LF Antenna Q Tuning Function

- Selectable LF Format

- 8051 Compatible Microcontroller

- 16KB ROM (for Program Code)

- 43 Words (7-bit x 43 Word) EEPROM

- 128-byte Battery Backed up RAM (BuRAM) (Uninitialized RAM at MCU Sleep Mode)

- 8-bit CRC Generator for BuRAM

- 16 PIN Ceramic Package with Diaphragm for Pressure Sensor (Shielded for EMI Protection)

#### 1.2 General Description

The TPIC82000 series integrates the functions required for a transmit (TX) module in Tire Pressure Monitoring System (TPMS) into a single ceramic package. The functions required for TPMS applications such as measurement functions (tire pressure, tire temperature, tire acceleration, battery voltage), RF data transmission, and LF command receiving functions are integrated in one device. The device consists of a ceramic package with diaphragm for pressure sensing, an accelerometer, and an LSI. The LSI integrates an 8051 microcontroller, RF transmitter, LF receiver, and Analog Front-End (AFE) with a 13-bit ADC for sensor measurements.

To minimize the power consumption and maximize the battery life of the system, the device can wake up periodically for measurements and RF transmissions using an internal ultra low power programmable timer or the 125 kHz LF trigger signal detector. Also, to support maximum usage of battery energy, the device can operate over the wide power supply range from 3.5 V to 1.5 V. (For 434 MHz RF transmission, the minimum voltage is 1.75 V)

The LF receiver enables control of this device remotely using a 125 kHz LF signal.

The 315 and/or 434 MHz local carrier signal is generated by the internal PLL synthesizer with one external crystal resonator.

The RF transmit frequency tuning is achieved using a baseband signal generator and a quadrature modulator. The baseband signal generator can control the baseband frequency up to 700 kHz.

The device supports automotive temperature range (-40°C to 125°C) and quality.

In the TPIC82000 series, the accelerometer is an optional component, and for the pressure sensor there are two selections: A and B at TI-TEST factory. For the RF transmission characteristic of 315 and 434 MHz band, one of the RF bands is tested at TI-TEST factory. The device names are defined below.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

| Device Name |   | Accelerometer Type / Pressure Sensor Selection A and B |                                |  |

|-------------|---|--------------------------------------------------------|--------------------------------|--|

| TPIC820X00  | Х | 0: No Accelerometer                                    | 1: 1-Axis (Z) Accelerometer    |  |

| TPIC8200Y0  | Υ | 0: Passenger car (Selection A)                         | 2: Passenger Car (Selection B) |  |

| TPIC82000Z  | Z | 3: 315 MHz                                             | 4: 434 MHz                     |  |

### 2 PIN CONFIGURATION AND DESCRIPTIONS

# 2.1 Pin Configuration

Figure 2-1. Top View from Diaphragm

# 2.2 Pin Descriptions

| PIN                         |     |                     | PULL UP-  | DECODINE                                                                       |  |  |

|-----------------------------|-----|---------------------|-----------|--------------------------------------------------------------------------------|--|--|

| NAME                        | NO. | TYPE                | DOWN      | DESCRIPTION                                                                    |  |  |

| CK                          | 1   | I                   | Pull down | SPI CK input terminal                                                          |  |  |

| LFIN                        | 2   | I                   |           | LF receiver input terminal 1                                                   |  |  |

| LFINB                       | 3   | I                   |           | LF receiver input terminal 2                                                   |  |  |

| RESET_ TEST                 | 4   | I                   | Pull down | H/W reset and Test Mode input terminal                                         |  |  |

| DI                          | 5   | 1                   | Pull up   | SPI DATA input terminal at EN_UART = 0 UART RXD output terminal at EN_UART = 1 |  |  |

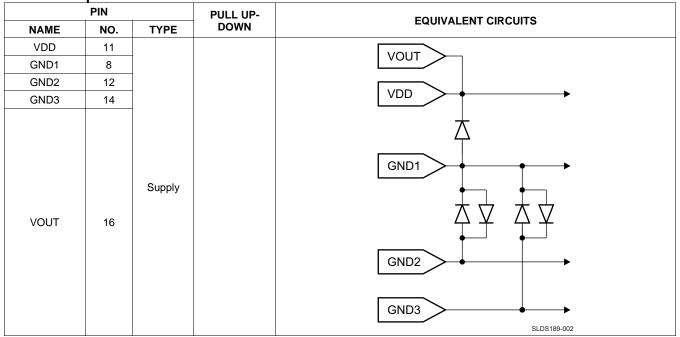

| TVO 6 O TVO output terminal |     | TVO output terminal |           |                                                                                |  |  |

| XTAL                        | 7   | I                   |           | XTAL component connection terminal                                             |  |  |

| GND1                        | 8   | GND                 |           | GND (Common GND)                                                               |  |  |

**NSTRUMENTS**

|               | PIN |        |           | DESCRIPTION                                                                                                                                                                   |  |  |

|---------------|-----|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. TYPE |     | DOWN   |           |                                                                                                                                                                               |  |  |

| DO            | 9   | 0      |           | SPI DO output terminal at EN_UART = 0 UART TXD output terminal at EN_UART = 1                                                                                                 |  |  |

| VREG          | 10  | 0      |           | Internal voltage regulator output A decoupling capacitor (0.1 $\mu$ F) needs to be connected between this terminal and GND. VREG should not be used to supply external loads. |  |  |

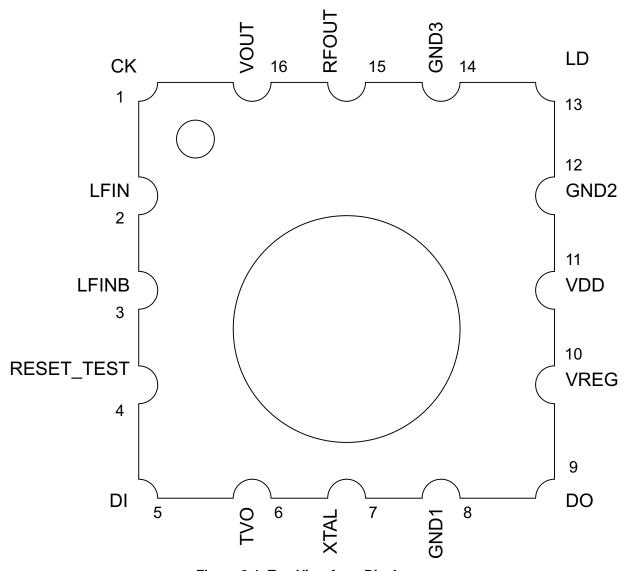

| VDD           | 11  | Supply |           | Battery supply voltage                                                                                                                                                        |  |  |

| GND2          | 12  | GND    |           | GND (RF block except PA)                                                                                                                                                      |  |  |

| LD            | 13  | ı      | Pull down | SPI CS input terminal                                                                                                                                                         |  |  |

| GND3          | 14  | GND    |           | GND (RF PA)                                                                                                                                                                   |  |  |

| RFOUT         | 15  | 0      |           | RF PA output terminal                                                                                                                                                         |  |  |

| VOUT          | 16  | 0      |           | V <sub>DD</sub> for load of PA (connected to V <sub>DD</sub> internally)                                                                                                      |  |  |

## 2.3 Pin Equivalent Circuits

TEXAS INSTRUMENTS

SLDS189 –MAY 2012 www.ti.com

|               | PIN |   | PULL UP-  |                                             |

|---------------|-----|---|-----------|---------------------------------------------|

| NAME NO. TYPE |     |   | DOWN      | EQUIVALENT CIRCUITS                         |

| VREG          | 10  | O |           | VREG  SLDS189-003                           |

| RESET_ TEST   | 4   | I | Pull down | RESET_TEST  VDD  VDD  VDD  VDD  SLDS189-004 |

| СК            | 1   | I | Pull down | CK SLDS189-005                              |

| LD            | 13  | I | Pull down | UD SLDS189-006                              |

|       | PIN |      | PULL UP- |                                |

|-------|-----|------|----------|--------------------------------|

| NAME  | NO. | TYPE | DOWN     | EQUIVALENT CIRCUITS            |

| DI    | 5   | I    | Pull up  | DI SLDS189-007                 |

| DO    | 9   | 0    |          | DO SLDS189-008                 |

| XTAL  | 7   | I    |          | XTAL VDD VDD GND SLDS 189-009  |

| RFOUT | 15  | O    |          | RFOUT  GND1  GND3  SLDS189-010 |

TEXAS INSTRUMENTS

SLDS189 –MAY 2012 www.ti.com

#### 3 FUNCTION DESCRIPTION

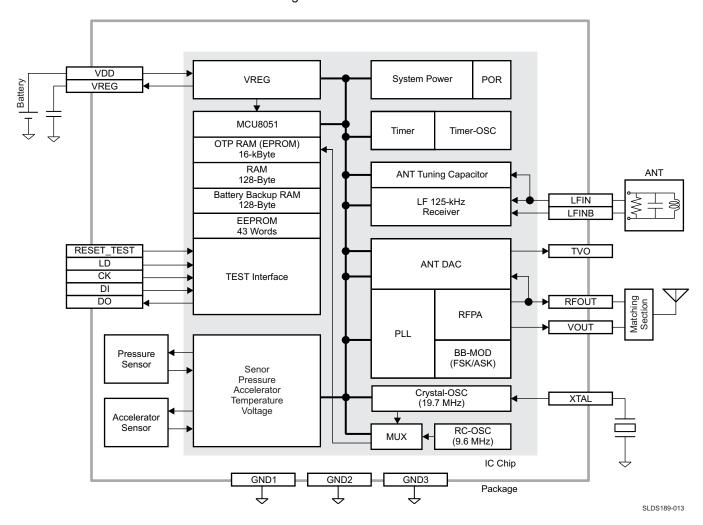

#### 3.1 Functional Block Diagram (Whole Device)

The block diagram below shows the overview of the whole TPIC82000 device.

The TPIC82000 consists of a pressure sensor which is structured within the ceramic package, an accelerometer for motion sensing, and a mixed signal LSI. The LSI integrates the 8051 microcontroller, a voltage regulator for internal block operation, an Analog Front-End for the sensor signal conditioning, clock generators for processor and internal blocks, an RF transmitter, and an LF signal receiver. The details of each block are described in the following sections.

#### 3.2 MCU8051 core

The TPIC82000 integrates a high performance version 8-bit microcontroller that is software compatible with the industry standard 8051. The MCU8051 core uses an internal RC oscillator (about 9.6 MHz) or an external crystal (about 19.7 MHz) as the clock source. It uses a two-clock period machine cycle to realize faster operation.

Submit Documentation Feedback

Product Folder Link(s): TPIC82000 Series

The MCU can address up to 16K bytes of program memory (ROM) and up to 128 bytes of internal data memory (RAM). The MCU can also access the integrated External Special Function Registers (ESFR) space up to 128 bytes. The control registers for built-in peripheral analog/logic circuit control, non-volatile EEPROM memory control and the Battery Backup External-RAM memory control are allocated in this ESFR space. The 43-word EEPROM (7bit x 43word) is prepared as a non-volatile data storage for the various variable parameters such as device ID and calibration parameters. The Battery Backup External-RAM is a volatile memory but the contents of the memory can be kept by the internal regulator when the device is in sleep mode.

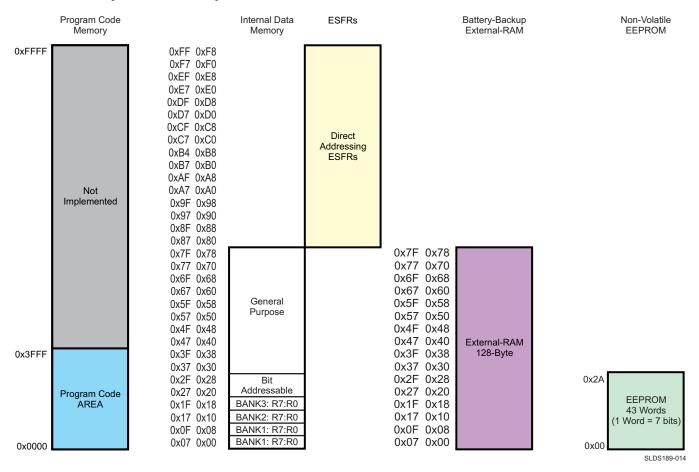

#### 3.2.1 Memory Resource Map

#### 3.2.2 Program Code Memory (ROM)

The 16K byte program code memory is located in the address space from 0x0000 to 0x3FFF. This portion is configured by Mask ROM, which is locked by a hardware disabling the SPI DO output as default to protect the ROM code.

#### **NOTE**

If using the built-in firmware prepared by TI, the program code area for the application software becomes smaller than 16K bytes (Typically around half of 16K bytes are available for application software).

#### 3.2.3 Internal Data Memory (RAM)

The 128-bytes of RAM are available as the volatile data storage for standard 8051 application program. During MCU sleep mode, the RAM is powered off and their contents are lost. Right after the Power-On-Reset or the Power-up of the MCU, the RAM data is not initialized.

#### 3.2.4 External Special Function Registers (ESFR)

The ESFRs are mapped on physical memory spaces 0x80 to 0xFF on the MCU8051 core to control and monitor the built-in peripherals. Figure 3-1, Figure 3-2, and Figure 3-3 show the register allocations.

#### 3.2.4.1 ESFR Table

| FOFD            | Write F             | Register  |           | Read Register       |           |           |  |

|-----------------|---------------------|-----------|-----------|---------------------|-----------|-----------|--|

| ESFR<br>Address | N                   | Reset (   | Note 1)   | Reset               |           | ( Note 1) |  |

| Address         | Name                | Power on  | Timer     | Name                | Power on  | Timer     |  |

| FF              | -                   |           |           | -                   |           |           |  |

| FE              | -                   |           |           | -                   |           |           |  |

| FD              | -                   |           |           | -                   |           |           |  |

| FC              | -                   |           |           | -                   |           |           |  |

| FB              | -                   |           |           |                     |           |           |  |

| FA              | -                   |           |           |                     |           |           |  |

| F9              | EEprom CONT         | X011 1111 | X011 1111 |                     |           |           |  |

| F8              | IP1 ( Not Usable )  | 0000 0000 | 0000 0000 | IP1 (Not Usable)    | 0000 0000 | 0000 0000 |  |

| F7              |                     |           |           |                     |           |           |  |

| F6              | -                   |           |           | -                   |           |           |  |

| F5              | •                   |           |           | •                   |           |           |  |

| F4              | -                   |           |           | -                   |           |           |  |

| F3              | AntDac              | 0000 0000 | 0000 0000 |                     |           |           |  |

| F2              | RFbias              | 0000 0000 | 0000 0000 |                     |           |           |  |

| F1              | RFpower             | 0000 0000 | 0000 0000 |                     |           |           |  |

| F0              | В                   | 0000 0000 | 0000 0000 | В                   | 0000 0000 | 0000 0000 |  |

| EF              | -                   |           |           | -                   |           |           |  |

| EE              | -                   |           |           | -                   |           |           |  |

| ED              | SLoffset            | XXXU UUUU | XXXS SSSS | -                   |           |           |  |

| EC              | LFcont              | บบบบ บบบบ | SSSS SSSS | LFdataCount         | 0000 0000 | DDDD DDDD |  |

| EB              |                     |           |           | ModState            | U1XX XXXX | U1XX XXXX |  |

| EA              |                     |           |           | SystemState         | 0X11 1110 | 1XDD 1DD0 |  |

| E9              |                     |           |           | Timer state         | 00XX 1110 | 00XX DDDD |  |

| E8              | IE1 ( Not Usable )  | 0000 0000 | 0000 0000 | IE1 ( Not Usable )  | 0000 0000 | 0000 0000 |  |

| E7              | -                   |           |           | -                   |           |           |  |

| <b>E</b> 6      | -                   |           |           | -                   |           |           |  |

| E5              | •                   |           |           | -                   |           |           |  |

| E4              | •                   |           |           | -                   |           |           |  |

| E3              |                     |           |           | LocalState          | XXX0 00U0 | XXX0 00D0 |  |

| E2              |                     |           |           | LFrxData            | 0000 0000 | DDDD DDDD |  |

| E1              |                     |           |           | LFanalogFE          | UUUU UUUU | DDDD DDDD |  |

| E0              | ACC                 | 0000 0000 | 0000 0000 | ACC                 | 0000 0000 | 0000 0000 |  |

| DF              | BuRAM_CRC_Start_Adr | X000 0000 | X000 0000 | BuRAM_CRC_Start_Adr | X000 0000 | X000 0000 |  |

| DE              | BuRAM_CRC_End_Adr   | 0000 0000 | 0000 0000 | BuRAM_CRC_End_Adr   | 0000 0000 | 0000 0000 |  |

| DD              | LFCarrierDet        | XXX0 0000 | XXXD DDDD | BuRAM_CRC_Status    | 0XXX XXXX | 0XXX XXX  |  |

| DC              | Lfabort             | 0000 0000 | DDDD DDDD | BuRAM_CRC_Result    | 1111 1111 | 1111 1111 |  |

| DB              |                     |           |           | •                   |           |           |  |

| DA              |                     |           |           | •                   |           |           |  |

| D9              |                     |           |           | •                   |           |           |  |

| D8              |                     |           |           |                     |           |           |  |

|                 |                     |           |           |                     |           |           |  |

| Note 1<br>Note 2 | Power on<br>Timer | Initial value from Power-On-Reset<br>Initial value from WAKEUP-EVENT (Timer / LF trigger / RF trigger) |

|------------------|-------------------|--------------------------------------------------------------------------------------------------------|

|                  | 0                 | DATA 0                                                                                                 |

|                  | 1                 | DATA 1                                                                                                 |

|                  | D                 | DATA 0 or DATA 1, depend on the EVENT/State                                                            |

|                  | U                 | Unknown, or DATA loss in MCU sleep state                                                               |

|                  | X                 | Notimplemented                                                                                         |

|                  | S                 | DATA kept during SLEEP state                                                                           |

|                  |                   | Accessible ESFR on TPIC82000                                                                           |

|                  | -                 | Reserved (Not Used)                                                                                    |

|                  |                   | Reserved ( by MCU Core )                                                                               |

|                  |                   | Reserved (for FW & Internal use)                                                                       |

Figure 3-1. ESFR Table (Address FF-D8)

# 3.2.4.2 ESFR Table (Continued)

| FOFD    | Write           | Register        |           | Read Register |                |           |  |

|---------|-----------------|-----------------|-----------|---------------|----------------|-----------|--|

| ESFR    | N.              | Reset ( Note 1) |           |               | Reset( Note 1) |           |  |

| Address | Name            | Power on        | Timer     | Name          | Power on       | Timer     |  |

| D7      | RC-OSC (Note 2) | 0000 1110       | 000S SSSS | RC-OSC        | 0000 1110      | 000S SSSS |  |

| D6      | -               |                 |           |               |                |           |  |

| D5      | -               |                 |           | -             |                |           |  |

| D4      | -               |                 |           | •             |                |           |  |

| D3      | ModCONT         | 0X00 0000       | 0X00 0000 | -             |                |           |  |

| D2      | ModScale        | UUUU UUUU       | UUUU UUUU | -             |                |           |  |

| D1      | ModOffset       | UUUU UUUU       | UUUU UUUU | -             |                |           |  |

| D0      | PSW             | 0000 0000       | 0000 0000 | PSW           | 0000 0000      | 0000 0000 |  |

| CF      | -               |                 |           |               |                |           |  |

| CE      |                 |                 |           | -             |                |           |  |

| CD      | LFwake1H        | UUUU UUUU       | SSSS SSSS | •             |                |           |  |

| CC      | LFwake1L        | UUUU UUUU       |           | •             |                |           |  |

| СВ      | ModTxData       | UUUU UUUU       |           | -             |                |           |  |

| CA      | ModRamAdd       | XXUU UUUU       | XXUU UUUU | •             |                |           |  |

| C9      | ModRamData      | UUUU UUUU       | UUUU UUUU | -             |                |           |  |

| C8      |                 |                 |           | LFstate       | 0000 0000      | DDDD DDDD |  |

| C7      | LFmodeRSSI      | 0UUU UUXX       | 0SSS SSXX | •             |                |           |  |

| C6      | LFagcSET        | XXUU UUUU       | XXSS SSSS | LFagcSET      | XX00 0000      | XXDD DDDD |  |

| C5      | LFdataC         | UUUU UUUU       | SSSS SSSS | •             |                |           |  |

| C4      | TimerLFwake     | 1111 1111       | SSSS SSSS | •             |                |           |  |

| C3      |                 |                 |           | TESTvector    | DD00 0000      | DD00 0000 |  |

| C2      | PLLIocalOSC     | 1000 0000       | 1000 0000 | -             |                |           |  |

| C1      | BuRAM_DATA      | UUUU UUUU       | SSSS SSSS | BuRAM_DATA    | UUUU UUUU      | SSSS SSSS |  |

| C0      |                 |                 |           | SensorState   | 00UX XXXX      | 00UX XXXX |  |

| BF      | SensorDC6       | 0000 0000       | 0000 0000 | •             |                |           |  |

| BE      | SensorDC5       | X000 0000       | X000 0000 | •             |                |           |  |

| BD      | SensorDC4       | X000 0000       | X000 0000 | •             |                |           |  |

| BC      | SensorDC3       | X000 0000       | X000 0000 | •             |                |           |  |

| BB      | SensorDC2       | X000 0000       | X000 0000 | •             |                |           |  |

| BA      | SensorDC1       | X000 0000       | X000 0000 | -             |                |           |  |

| B9      | SensorDC0       | X000 0000       | X000 0000 | •             |                |           |  |

| B8      | IP              | 1111 1111       | 1111 1111 | IP            | 1111 1111      | 1111 1111 |  |

| B7      | SensorBaseH     | XXX0 0000       | XXX0 0000 | •             |                |           |  |

| B6      | SensorBaseL     | 0000 0000       | 0000 0000 | •             |                |           |  |

| B5      | SensorOffsetH   | XX00 0000       | XX00 0000 | •             |                |           |  |

| B4      | SensorOffsetL   | 0000 0000       | 0000 0000 | •             |                |           |  |

| B3      | SensorCONT      | 0000 0000       | 0000 0000 | •             |                |           |  |

| B2      | LFANT           | UUUU UUUU       | SSSS SSSS | •             |                |           |  |

| B1      | LFwake0H        | UUUU UUUU       | SSSS SSSS | -<br>D2       | 4444 4444      | 4444 4444 |  |

| B0      | P3              | 1111 1111       | 1111 1111 | P3            | 1111 1111      | 1111 1111 |  |

| AF      | LFwake0L        | UUUU UUUU       | SSSS SSSS | -             |                |           |  |

| AE      | LFsync1         | XUUU UUUU       | XSSS SSSS | -             |                |           |  |

| AD      | LFsync0         | UUUU UUUU       | SSSS SSSS | •             |                |           |  |

| AC      | LFpLT           | UUUU UUUU       | SSSS SSSS | •             |                |           |  |

| Note 1 | Power on | Initial value from Power-On-Reset                                 |  |  |  |  |

|--------|----------|-------------------------------------------------------------------|--|--|--|--|

| Note 2 | Timer    | Initial value from WAKEUP-EVENT (Timer / LF trigger / RF trigger) |  |  |  |  |

|        |          |                                                                   |  |  |  |  |

|        | 0        | DATA 0                                                            |  |  |  |  |

|        | 1        | DATA 1                                                            |  |  |  |  |

|        | D        | DATA 0 or DATA 1, depend on the EVENT/State                       |  |  |  |  |

|        | U        | Unknown, or DATA loss in MCU sleep state                          |  |  |  |  |

|        | X        | Not implemented                                                   |  |  |  |  |

|        | S        | DATA kept during SLEEP state                                      |  |  |  |  |

|        |          | Accessible ESFR on TPIC82000                                      |  |  |  |  |

|        | •        | Reserved (Not Used)                                               |  |  |  |  |

|        |          | Reserved (by MCU Core)                                            |  |  |  |  |

|        |          | Reserved (for FW & Internal use)                                  |  |  |  |  |

Figure 3-2. ESFR Table (Address D7-AC)

Note

# 3.2.4.3 ESFR Table (Continued)

| FOFD    | Write F           | Register  |           | Read Register     |                       |                       |  |

|---------|-------------------|-----------|-----------|-------------------|-----------------------|-----------------------|--|

| ESFR    |                   | Reset(    | Note 1)   |                   |                       | Note 1)               |  |

| Address | Name              | Power on  | Timer     | Name              | Power on              | Timer                 |  |

| AB      | LFpUT             | UUUU UUUU | SSSS SSSS | -                 |                       |                       |  |

| AA      | LFrssiVT          | UUUU UUUU | SSSS SSSS | -                 |                       |                       |  |

| A9      | -                 |           |           | -                 |                       |                       |  |

| A8      | IE                | 0000 0000 | 0000 0000 | IE                | 0000 0000             | 0000 0000             |  |

| A7      | LFOSC             | UUUU UUUU | SSSS SSSS | -                 |                       |                       |  |

| A6      | LFdelay           | UUUU UUUU | SSSS SSSS | -                 |                       |                       |  |

| A5      | LFbias            | UUUU UUUU | SSSS SSSS | -                 |                       |                       |  |

| A4      | LFmode            | 0000 0000 | 0SSS SSSS | -                 |                       |                       |  |

| А3      | EEpromData        | ×000 0000 | ×000 0000 | EEpromData        | 0UUU UUUU<br>(E2prom) | 0SSS SSSS<br>(E2prom) |  |

| A2      | RFdetCONT         | 000X XXXU | UUUX XXXU | •                 |                       |                       |  |

| A1      | BuRAM_ADDR        | 0000 0000 | 0000 0000 | BuRAM_ADDR        | 0000 0000             | 0000 0000             |  |

| A0      | P2 ( Not Usable ) | 1111 1111 | 1111 1111 | P2 ( Not Usable ) | 1111 1111             | 1111 1111             |  |

| 9F      | -                 |           |           | -                 |                       |                       |  |

| 9E      | •                 |           |           | -                 |                       |                       |  |

| 9D      | •                 |           |           | -                 |                       |                       |  |

| 9C      | -                 |           |           | -                 |                       |                       |  |

| 9B      | -                 |           |           | -                 |                       |                       |  |

| 9A      | -                 |           |           | -                 |                       |                       |  |

| 99      | SBUF              | 0000 0000 | 0000 0000 | SBUF              | 0000 0000             | 0000 0000             |  |

| 98      | SCON              | 0000 0000 | 0000 0000 | SCON              | 0000 0000             | 0000 0000             |  |

| 97      | TimerOSC          | 0000 0000 | 0SSS SSSS | -                 |                       |                       |  |

| 96      | TimerPre          | 1111 1111 | SSSS SSSS | -                 |                       |                       |  |

| 95      | TimerPost         | 1111 1111 | SSSS SSSS | TimerPost         | 1111 1111             | DDDD DDDD             |  |

| 94      | SystemPower       | 100X XXXX | 100X XXXX | -                 |                       |                       |  |

| 93      | BPL               | 0000 0000 | 0000 0000 | -                 |                       |                       |  |

| 92      | BPU               | XX00 0000 | XX00 0000 | -                 |                       |                       |  |

| 91      | TESTvector        | 0000 0000 | 0000 0000 | -                 |                       |                       |  |

| 90      | P1 ( Not Usable ) | 1111 1111 | 1111 1111 | P1 (Not Usable )  | 1111 1111             | 1111 1111             |  |

| 8F      | -                 |           |           | -                 |                       |                       |  |

| 8E      | -                 |           |           | -                 |                       |                       |  |

| 8D      | TH1               | 0000 0000 | 0000 0000 | TH1               | 0000 0000             | 0000 0000             |  |

| 8C      | TH0               | 0000 0000 | 0000 0000 | TH0               | 0000 0000             | 0000 0000             |  |

| 8B      | TL1               | 0000 0000 | 0000 0000 | TL1               | 0000 0000             | 0000 0000             |  |

| 8A      | TL0               | 0000 0000 | 0000 0000 | TL0               | 0000 0000             | 0000 0000             |  |

| 89      | TMOD              | 0000 0000 | 0000 0000 | TMOD              | 0000 0000             | 0000 0000             |  |

| 88      | TCON              | 0000 0000 | 0000 0000 | TCON              | 0000 0000             | 0000 0000             |  |

| 87      | PCON              | 0000 0000 | 0000 0000 | PCON              | 0000 0000             | 0000 0000             |  |

| 86      | XtalBias          | XXXX 0000 | XXXX 0000 | -                 |                       |                       |  |

| 85      | TESTmux1          | 0000 0000 | 0000 0000 | •                 |                       |                       |  |

| 84      | TESTmux0          | 0000 0000 | 0000 0000 | •                 |                       |                       |  |

| 83      | DPH               | 0000 0000 | 0000 0000 | DPH               | 0000 0000             | 0000 0000             |  |

| 82      | DPL               | 0000 0000 | 0000 0000 | DPL               | 0000 0000             | 0000 0000             |  |

| 81      | SP                | 0000 0000 | 0000 0000 | SP                | 0000 0000             | 0000 0000             |  |

| 80      | P0 ( Not Usable ) | 1111 1111 | 1111 1111 | P0 (Not Usable)   | 1111 1111             | 1111 1111             |  |

| Note 1 | Power on | Initial value from Power-On-Reset                                |  |  |  |  |  |

|--------|----------|------------------------------------------------------------------|--|--|--|--|--|

| Note 2 | Timer    | Initial value from WAKEUP-EVENT (Timer / LF trigger / RF trigger |  |  |  |  |  |

|        |          |                                                                  |  |  |  |  |  |

|        | 0        | DATA 0                                                           |  |  |  |  |  |

|        | 1        | DATA 1                                                           |  |  |  |  |  |

|        | D        | DATA 0 or DATA 1, depend on the EVENT/State                      |  |  |  |  |  |

|        | U        | Unknown, or DATA loss in MCU sleep state                         |  |  |  |  |  |

|        | X        | Not implemented                                                  |  |  |  |  |  |

|        | S        | DATA kept during SLEEP state                                     |  |  |  |  |  |

|        |          | Accessible ESFR on TPIC82000                                     |  |  |  |  |  |

|        | -        | Reserved (Not Used)                                              |  |  |  |  |  |

|        |          | Reserved ( by MCU Core )                                         |  |  |  |  |  |

|        |          | Reserved (for FW & Internal use)                                 |  |  |  |  |  |

Figure 3-3. ESFR Table (Address AB-80)

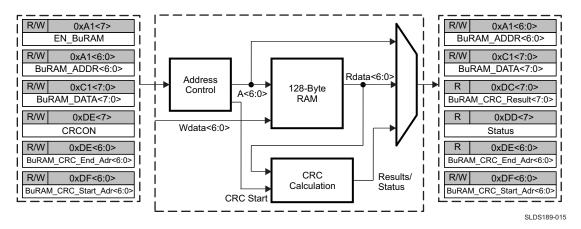

#### 3.2.5 Battery Backup External-RAM (BuRAM)

On the TPIC82000 device, the 128-byte RAM area is prepared as the Battery Backup External-RAM on the device and can be used to store status parameters for TPMS applications while the device is in sleep mode. The BuRAM area is structured as the volatile memory but is backed up by internal regulator voltage while in sleep mode. Right after Power-on-Reset, the data contents of RAM are not initialized.

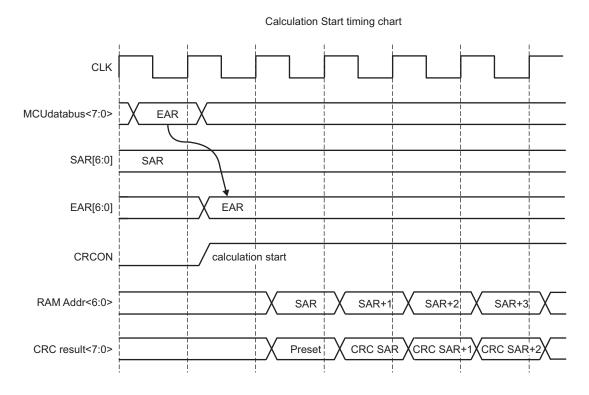

#### 3.2.5.1 CRC (Cyclic Redundancy Check) Generator Function

BuRAM has an 8-bit CRC generator of BuRAM memory, which is shown in Section 3.2.5.2.

The CRC calculation is done through the following steps:

- 1. Set the CRC calculation start address (SAR) of BuRAM memory.

- 2. Set the CRC calculation end address (EAR) of BuRAM memory with CRCON = 1.

- When CRCON is set to 1, CRC calculation starts from SAR to EAR data of the BuRAM memory.

- Each CRC calculation is done by every system clock cycle.

- CRC initial value is 0xFF.

- If SAR and EAR are the same, the CRC calculation result is one address calculation.

- If SAR > EAR, calculation starts from SAR to 127 and continuously calculates 0 to EAR.

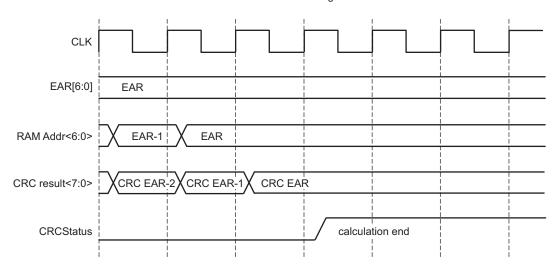

- 3. When CRC calculation is done, the status bit (**BuRAM\_CRC\_Status** [7]) turns to 1. This flag is cleared by setting CRCON bit to 0.

- 4. The CRC calculation result appears in the BuRAM\_CRC\_Result register.

#### 3.2.5.2 BuRAM with CRC Generator Block Diagram

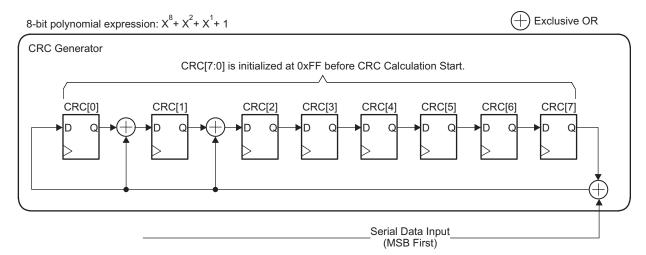

#### 3.2.5.3 8-bit CRC Polynomial Expression

The CRC generator uses the following 8-bit polynomial expression shown in Figure 3-4

Figure 3-4. CRC Generator 8-bit Polynomial Expression

#### 3.2.5.4 Timing Chart of CRC Calculation from Start Address

#### 3.2.5.5 Timing Chart of CRC Calculation at the End Address

Calculation End timing chart

#### 3.2.5.6 Battery Backup External-RAM (BuRAM) Control ESFR

■ Battery backup RAM Read/Write Address Control

Not Bit Addressable

ESFR: 0xA1

BuRAM\_ADDR

|                                          | BIT 7    | BIT 6                               | BIT 5           | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |

|------------------------------------------|----------|-------------------------------------|-----------------|-------|-------|-------|-------|-------|--|--|

|                                          | EN_BuRAM |                                     | BuRAM_ADDR<6:0> |       |       |       |       |       |  |  |

| Access                                   | r/w      | r/w                                 | r/w             | r/w   | r/w   | r/w   | r/w   | r/w   |  |  |

| At Power on reset                        | 0        | 0                                   | 0               | 0     | 0     | 0     | 0     | 0     |  |  |

| At Timer reset                           | 0        | 0                                   | 0               | 0     | 0     | 0     | 0     | 0     |  |  |

| EN_BuRam                                 |          | BuRAM Read/Write access control bit |                 |       |       |       |       |       |  |  |

|                                          |          | 1 = Access Er<br>0 = Access Di      |                 |       |       |       |       |       |  |  |

| BuRAM_ADDR<6:0> BuRAM Read/Write Address |          |                                     |                 |       |       |       |       |       |  |  |

■ Battery backup RAM Read/Write DATA Register

Not Bit Addressable

ESFR: 0xC1

BuRAM\_DATA

|                   | BIT 7                 | BIT 6           | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |

|-------------------|-----------------------|-----------------|-------|-------|-------|-------|-------|-------|--|--|

|                   |                       | BuRAM_DATA<7:0> |       |       |       |       |       |       |  |  |

| Access            | r/w                   | r/w             | r/w   | r/w   | r/w   | r/w   | r/w   | r/w   |  |  |

| At Power on reset | U                     | U               | U     | U     | U     | U     | U     | U     |  |  |

| At Timer reset    | S                     | S               | S     | S     | S     | S     | S     | S     |  |  |

| BuRAM_DATA<7:0>   | BuRAM Read/Write DATA |                 |       |       |       |       |       |       |  |  |

■ Battery backup RAM CRC Start Address Register

Not Bit Addressable

ESFR: 0xDF

BuRAM\_CRC\_Start\_Adr

|                   | BIT 7    | BIT 6                         | BIT 5                    | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |

|-------------------|----------|-------------------------------|--------------------------|-------|-------|-------|-------|-------|--|--|

|                   | -        |                               | BuRAM CRC Start Adr<6:0> |       |       |       |       |       |  |  |

| Access            | _        | r/w                           | r/w                      | r/w   | r/w   | r/w   | r/w   | r/w   |  |  |

| At Power on reset | Х        | 0                             | 0                        | 0     | 0     | 0     | 0     | 0     |  |  |

| At Timer reset    | Х        | 0                             | 0 0 0 0                  |       |       |       |       | 0     |  |  |

| BuRAM CRC Start   | Adr<6:0> | CRC calculation start address |                          |       |       |       |       |       |  |  |

| ■ Battery backup F           | RAM CRC End                                    | Address Regist    | er No          | ot Bit Addressab | ole   |       |       |       |

|------------------------------|------------------------------------------------|-------------------|----------------|------------------|-------|-------|-------|-------|

| ESFR: 0xDE                   |                                                | BuRAM_CRC_End_Adr |                |                  |       |       |       |       |

|                              | BIT 7                                          | BIT 6             | BIT 5          | BIT 4            | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| CRCON BuRAM CRC End Adr<6:0> |                                                |                   |                |                  |       |       |       |       |

| Access                       | r/w                                            | r/w               | r/w            | r/w              | r/w   | r/w   | r/w   | r/w   |

| At Power on reset            | 0                                              | 0                 | 0              | 0                | 0     | 0     | 0     | 0     |

| At Timer reset               | 0                                              | 0                 | 0              | 0                | 0     | 0     | 0     | 0     |

| CRCON                        |                                                | CRC calculati     | on: (1), Norma | I mode: (0)      |       |       |       |       |

| BuRAM_CRC_End_               | BuRAM_CRC_End_Adr<6:0> CRC calculation end add |                   |                |                  |       |       |       |       |

|                              |                                                |                   |                |                  |       |       |       |       |

| ■ Battery backup F           | RAM CRC Stat                                   | us Register       | No             | ot Bit Addressab | ole   |       |       |       |

ESFR: 0xDD BuRAM\_CRC\_Status

|                   | BIT 7  | BIT 6 | BIT 5                            | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|--------|-------|----------------------------------|-------|-------|-------|-------|-------|

|                   | Status |       |                                  |       | _     |       |       |       |

| Access            | r      | _     | _                                | _     | _     | _     | _     | -     |

| At Power on reset | 0      | x     | x                                | x     | x     | x     | x     | х     |

| At Timer reset    | 0      | x     | x                                | x     | x     | x     | x     | X     |

| Status            |        |       | on: Done: (1), I<br>when CRCON = |       |       |       |       |       |

■ Battery backup RAM CRC Result Register

Not Bit Addressable

ESFR: 0xDC BuRAM\_CRC\_Result

|                                              | BIT 7                  | BIT 6 | BIT 5                 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |  |

|----------------------------------------------|------------------------|-------|-----------------------|-------|-------|-------|-------|-------|--|--|--|

|                                              |                        |       | BuRAM CRC Result<7:0> |       |       |       |       |       |  |  |  |

| Access                                       | r                      | r     | r                     | r     | r     | r     | r     | r     |  |  |  |

| At Power on reset                            | 1                      | 1     | 1                     | 1     | 1     | 1     | 1     | 1     |  |  |  |

| At Timer reset                               | er reset 1 1 1 1 1 1 1 |       |                       |       |       |       | 1     | 1     |  |  |  |

| BuRAM_CRC_Result<7:0> CRC calculation Result |                        |       |                       |       |       |       |       |       |  |  |  |

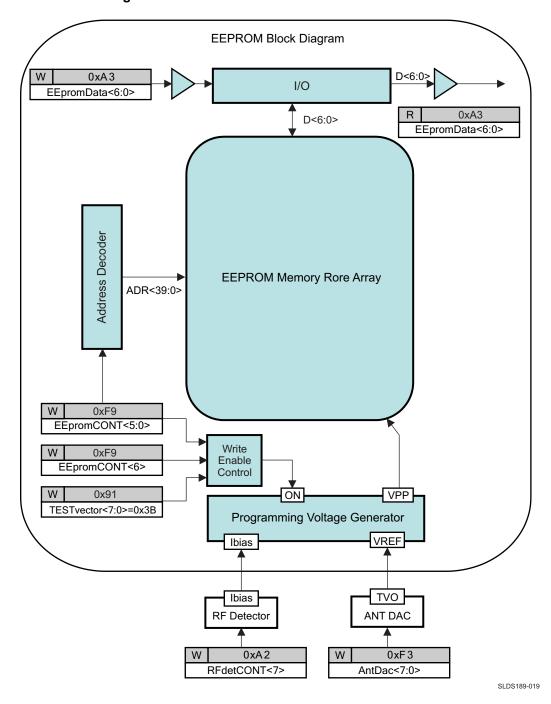

#### 3.2.6 Non-volatile EEPROM

In the TPIC82000 device, the 7-bits x 43-words of EEPROM are available as non-volatile data storage for the various variable parameters. All 7-bits can be used for data storage or the register can be configured for 3-bits Error Correction Code (ECC) + 4-bits of Data.

#### **NOTE**

This EEPROM area is also used for the trimming/calibration parameter storage by TI and firmware. Therefore, the actual accessible area for the user is limited for address 0x02 to 0x0F. The interface board and Support Software are prepared to support the EEPROM programming.

#### 3.2.6.1 EEPROM Block Diagram

<u>SLDS189 – MAY 2012</u> **www.ti.com**

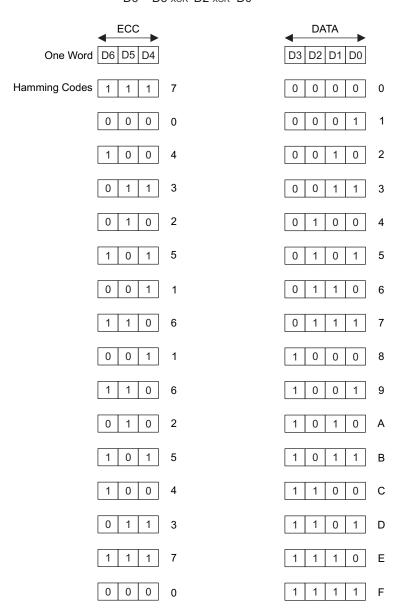

#### 3.2.6.2 EEPROM Unit Structure and DATA/ECC Implementation

EEPROM is mapped on the ESFR space. It has a 43 words memory unit. Each unit has 7 bits (D6:D0). The upper three bits (D6:D4) are allocated for Error Correcting Code (ECC) and the lower four bits (D3:D0) are for data. The ECC contains Hamming codes. Hamming codes can detect up to two simultaneous bit errors, and correct single-bit errors. The Hamming codes are calculated by the following equations:

| D4 = | D2 xor | D1 xor | D0 |

|------|--------|--------|----|

| D5 = | D3 xor | D1 xor | D0 |

| D6 = | D3 xor | D2 xor | D0 |

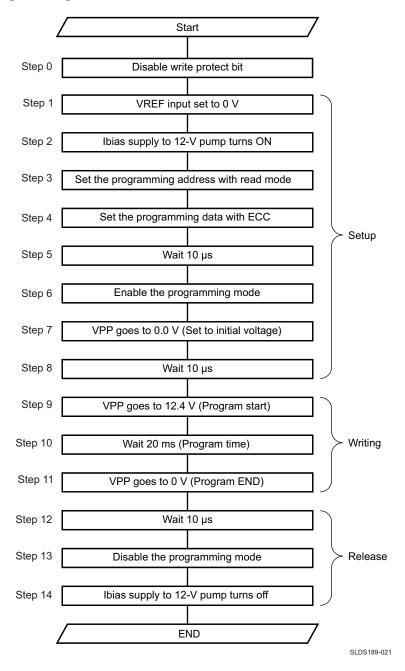

#### 3.2.6.3 EEPROM Programming Procedure

| Step             | Register    |      | Setting Values                                    | Operation                                                    |  |  |

|------------------|-------------|------|---------------------------------------------------|--------------------------------------------------------------|--|--|

| 0                | TestVector  | 0x91 | 0X3B                                              | Disable write protect                                        |  |  |

| 1                | AntDac      | 0xF3 | 0X00 (OFF)                                        | VREF input set to 0 V                                        |  |  |

| 2                | RFdetCONT   | 0xA2 | 0X80 (ON)                                         | Ibias supply to 12 V PUMP turns on                           |  |  |

| 3                | EEprom CONT | 0xF9 | 0x00-0x2A (Write address) + 0x00 (Read mode) (1)  | Set the programming address with read mode                   |  |  |

| 4                | EEprom Data | 0xA3 | 0x00-0x7F (Write data)                            | Set the programming data with ECC                            |  |  |

| 5                |             |      |                                                   | Wait 10 µs                                                   |  |  |

| 6                | EEprom CONT | 0xF9 | 0x00-0x2A (Write address) + 0x40 (Write mode) (1) | Enable the programming mode                                  |  |  |

| 7 <sup>(2)</sup> | AntDac      | 0xF3 | 0x00 (OFF) → 0xC0 (ON)                            | VPP goes to the initial voltage (0 V)                        |  |  |

| 8                |             |      |                                                   | Wait 10 µs                                                   |  |  |

| 9                | AntDac      | 0xF3 | 0x17 (1.24 V) + 0xC0 (ON)                         | VPP goes to 12.4 V (Programming voltage)                     |  |  |

| 10               |             |      |                                                   | Programming time 20 ms at typical is controlled by firmware. |  |  |

| 11               | AntDac      | 0xF3 | 0x00 (OFF)                                        | VPP goes to 0 V (Forced to GND)                              |  |  |

| 12               |             |      |                                                   | Wait 10 µs                                                   |  |  |

| 13               | EEprom CONT | 0xF9 | 0x00-0x2A (Write address) + 0x00 (Read mode)      | Disable the programming mode                                 |  |  |

| 14               | RFdet CONT  | 0xA2 | 0x00 (OFF)                                        | Ibias supply to 12 V PUMP turns off                          |  |  |

The user areas of EEPROM are assigned from 0x02 to 0x0F. The other areas are reserved for TI internal use and are not usable. For steps 7–9: The AntDac register should be set to the value of 0xC0 to define the initial voltage of TVO to 0 V. After the register setting, wait about 10 µs. Then the AntDac register is set to the value of 0xD7 to bias the TVO voltage to 1.24 V. The programming voltage generator generates 12.4 V by using the TVO voltage of 1.24 V at typical condition, and the programming voltage can be changed by using the AntDac register. For step 10: programming time is set to 20 ms.

#### 3.2.6.4 EEPROM Control ESFR

| ■ E | <b>Eprom</b> | Write | Address | Register |  |

|-----|--------------|-------|---------|----------|--|

|-----|--------------|-------|---------|----------|--|

Not Bit Addressable

| ESFR: 0xF9 |       | EEpromCONT |  |  |

|------------|-------|------------|--|--|

|            | BIT 7 | BIT 6      |  |  |

|                   | BIT 7 | BIT 6                               | BIT 5                   | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|-------|-------------------------------------|-------------------------|-------|-------|-------|-------|-------|

|                   | ı     | EEpromWrite                         | mWrite EEpromWRadd<5:0> |       |       |       |       |       |

| Access            | _     | W                                   | W                       | w     | w     | W     | w     | W     |

| At Power on reset | Х     | 0                                   | 1                       | 1     | 1     | 1     | 1     | 1     |

| At Timer reset    | х     | 0                                   | 1                       | 1     | 1     | 1     | 1     | 1     |

| EEpromWrite       |       | ON: (1), OFF: (0)                   |                         |       |       |       |       |       |

| FF WD 11 50       |       | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                         |       |       |       |       |       |

EEpromWRadd<5:0> **EEprom Write address**

#### ■ EEprom DATA Register

Not Bit Addressable

ESFR: 0xA3 EEpromData

|                   | BIT 7 | BIT 6      | BIT 5           | BIT 4 | BIT 3         | BIT 2           | BIT 1          | BIT 0   |  |  |

|-------------------|-------|------------|-----------------|-------|---------------|-----------------|----------------|---------|--|--|

|                   | -     |            | EEpromData<6:0> |       |               |                 |                |         |  |  |

| Access            | _     | w          | w               | w     | w             | w               | w              | w       |  |  |

| At Power on reset | x     | 0          | 0               | 0     | 0             | 0               | 0              | 0       |  |  |

| At Timer reset    | х     | 0          | 0               | 0     | 0             | 0               | 0              | 0       |  |  |

| EEpromData<6:0>   |       | EEprom DAT | 4               |       | Note: This Re | gister is commo | on to RFdetThr | es<7:0> |  |  |

#### ■ EEprom DATA Register

Not Bit Addressable

ESFR: 0xA3

EEpromData

|                   | BIT 7   | BIT 6                                                       | BIT 5           | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0   |  |  |

|-------------------|---------|-------------------------------------------------------------|-----------------|-------|-------|-------|-------|---------|--|--|

|                   | Testout |                                                             | EEpromData<6:0> |       |       |       |       |         |  |  |

| Access            | r       | r                                                           | r               | r     | r     | r     | r     | r       |  |  |

| At Power on reset | 0       | U                                                           | U               | U     | U     | U     | U     | U       |  |  |

| At Timer reset    | 0       | S                                                           | S               | S     | S     | S     | S     | S       |  |  |

| Testout           |         | Test output                                                 |                 |       |       |       |       |         |  |  |

| EEpromData<6:0>   |         | EEprom DATA Note: This Register is common to RFdetThres<7:0 |                 |       |       |       |       | es<7:0> |  |  |

■ Test Mode Control

Not Bit Addressable

ESFR: 0x91 **TESTvector**

|                   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3   | BIT 2    | BIT 1 | BIT 0 |

|-------------------|-------|-------|-------|-------|---------|----------|-------|-------|

|                   | _     | _     |       |       | TestVec | tor<5:0> |       |       |

| Access            | w     | w     | w     | w     | w       | w        | w     | w     |

| At Power on reset | 0     | 0     | 0     | 0     | 0       | 0        | 0     | 0     |

| At Timer reset    | 0     | 0     | 0     | 0     | 0       | 0        | 0     | 0     |

|                   |       |       |       |       |         |          |       |       |

TestVector<5:0> Test Vector Setting;

TestVector<5:0> = 0x3B; Enable to Write access of the EEprom (Upper address: 0x10 to 0x27)

#### ■ RF Detector Control

Not Bit Addressable

ESFR: 0xA2 **RFdetCONT**

Copyright © 2012, Texas Instruments Incorporated

|                   | BIT 7      | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|------------|-------|-------|-------|-------|-------|-------|-------|

|                   | RFdetPower | -     | _     | _     | _     | _     | _     | _     |

| Access            | W          | W     | w     | -     | _     | _     | _     | W     |

| At Power on reset | 0          | 0     | 0     | x     | x     | x     | x     | U     |

| At Timer reset    | U          | U     | U     | х     | х     | Х     | X     | U     |

RFdetPower

**EEPROM Bias Power Control**

Note: This bit is consolidated with RF Detector Power Control.

**FUNCTION DESCRIPTION**

1 = Power On, 0 = Power Off

TX ANT-Tuning DAC control

Not Bit Addressable

ESFR: 0xF3 AntDac

| LOI IX. OXI O                                                                                          |                                                                                   | rindao                              |           |       |       |                                                                              |       |       |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------|-----------|-------|-------|------------------------------------------------------------------------------|-------|-------|

|                                                                                                        | BIT 7                                                                             | BIT 6                               | BIT 5     | BIT 4 | BIT 3 | BIT 2                                                                        | BIT 1 | BIT 0 |

|                                                                                                        | ANTdacPower                                                                       | SEL_PumpCk                          |           |       | ANT   | TDAC<5:0>                                                                    |       |       |

| Access                                                                                                 | w                                                                                 | W                                   | W         | w     | w     | W                                                                            | w     | w     |

| At Power on reset                                                                                      | 0                                                                                 | 0                                   | 0         | 0     | 0     | 0                                                                            | 0     | 0     |

| At Timer reset                                                                                         | U                                                                                 | U                                   | U         | U     | U     | U                                                                            | U     | U     |

| ANTdacPower Control the EEPROM programming voltage generator power On/Off  0 = Power Off, 1 = Power ON |                                                                                   |                                     |           |       |       |                                                                              |       |       |

| SEL_PumpCK                                                                                             | Charge Pump (<br>Always keep                                                      | Clock select:<br>to 1 (Internal Osc | cillator) |       |       | Note: These Register bits are commonly used with Antenna Tuning DAC Control. |       |       |

| ANTDAC<5:0>                                                                                            | EEPROM Programming Voltage Control  Set to 0x17 (= 1.24 V) for EEPROM programming |                                     |           |       |       |                                                                              |       |       |

#### 3.2.7 MCU8051 Registers

This section describes the internal registers used in the MCU. All I/O, timer/counter and UART operations for the MCU 8051 core are accessed via specific ESFRs. These registers occupy the direct internal data memory spaces of 0x80 to 0xFF.

#### 3.2.7.1 MCU8051 Core SFR Map

| Description                                  | Label | Address | Reset Value | Bit Addressable |

|----------------------------------------------|-------|---------|-------------|-----------------|

| Port0 <sup>(1)</sup>                         | P0    | 0x80    | 0xFF        | 0               |

| Stack Pointer                                | SP    | 0x81    | 0x07        |                 |

| Data Pointer Low Byte                        | DPL   | 0x82    | 0x00        |                 |

| Data Pointer High Byte                       | DPH   | 0x83    | 0x00        |                 |

| Power Control Register (1)                   | PCON  | 0x87    | 0x00        |                 |

| Timer / Counter Control (1)                  | TCON  | 0x88    | 0x00        | 0               |

| Timer / Counter Mode Control                 | TMOD  | 0x89    | 0x00        |                 |

| Timer / Counter 0 Low Byte                   | TL0   | 0x8A    | 0x00        |                 |

| Timer / Counter 1 Low Byte                   | TL1   | 0x8B    | 0x00        |                 |

| Timer / Counter 0 High Byte                  | TH0   | 0x8C    | 0x00        |                 |

| Timer / Counter 1 High Byte                  | TH1   | 0x8D    | 0x00        |                 |

| Port1 (1)                                    | P1    | 0x90    | 0xFF        | 0               |

| Serial Control Register                      | SCON  | 0x98    | 0x00        | 0               |

| Serial Data Buffer                           | SBUF  | 0x99    | 0x00        |                 |

| Port2 <sup>(1)</sup>                         | P2    | 0xA0    | 0xFF        | 0               |

| Interrupt Enable Register 0 <sup>(1)</sup>   | IE    | 0xA8    | 0x00        | 0               |

| Port3 (1)                                    | P3    | 0xB0    | 0xFF        | 0               |

| Interrupt Priority Register 0 <sup>(1)</sup> | IP    | 0xB8    | 0xFF        | 0               |

| Program Status Word                          | PSW   | 0xD0    | 0x00        | 0               |

| Accumulator                                  | А     | 0xE0    | 0x00        | 0               |

- (1) The following functions and/or registers are not implemented on this device instead the standard 8051 core has:

- Port 0 (0x80), Port 1 (0x98), Port 2 (0xA8) are not connected physically or usable.

- Bit 2 to bit 6 of Port 3 are not physically connected or usable as a general I/O port.

- Extended functions assigned on Port 3 at bit 3 (NINT1), bit 4 (TO), bit 5 (T1) are not connected or usable.

- External Interrupt functions for IE1 and Extended Interrupt functions IE5 through IE13 are not supported or usable.

- Based on 4), the Internal Enable Register 1 (IE1) (0xE8) is not configured or usable.

- Based on 4), the Interrupt Priority Register 1 (IP1) (0xF8) is not configured or usable.

- Based on 4), the control bits of External Interrupt 1 and 5 related functions on the Interrupt Enable Register 0 (IE) (0xA8), bit 2 (EX1) and bit 5 (EI5) are not configured or usable.

- Based on 4), the control bits of External Interrupt 1 and 5 related functions on the Interrupt Priority Register 0 (IP) (0xB8), bit 2 (PX1) and bit 5 (PI5) are not configured or usable.

- Based on 4), the related control bits of IE1 control on Timer/Counter Register (TCON), bit 2 (IT 1) and bit 3 (IE1) are not configured or usable.

FUNCTION DESCRIPTION

www.ti.com \_\_\_\_\_\_\_ SLDS189 – MAY 2012

| Description                                  | Label | Address | Reset Value | Bit Addressable |

|----------------------------------------------|-------|---------|-------------|-----------------|

| Interrupt Enable Register 1 (1)              | IE1   | 0xE8    | 0x00        | 0               |

| B Register                                   | В     | 0xF0    | 0x00        | 0               |

| Interrupt Priority Register 1 <sup>(1)</sup> | IP1   | 0xF8    | 0x00        | 0               |

#### 3.2.7.2 I/O PORT (P0,P1,P2,P3)

On the 8051 MCU, P0, P1, P2 and P3 are assigned as the 32 quasi-bi-directional I/O lines. However, on the TPIC82000 device, only the ports P3<1:0> can be used for a general purpose I/O (GPIO), the others are not configured or usable.

| ■ I/O PORTS(P0,P      | 1,P2,P3) <sup>(1)</sup> |                | Bit                         |                 |                |                  |            |       |  |

|-----------------------|-------------------------|----------------|-----------------------------|-----------------|----------------|------------------|------------|-------|--|

| ESFR: 0xB0            |                         | P3             |                             |                 |                |                  |            |       |  |