## Dual Channel 8-Bit Resolution CMOS ADC

AD9281

#### **FEATURES**

Complete Dual Matching ADC

Low Power Dissipation: 225 mW (+3 V Supply)

Single Supply: 2.7 V to 5.5 V

Differential Nonlinearity Error: 0.1 LSB

On-Chip Analog Input Buffers

On-Chip Reference

Signal-to-Noise Ratio: 49.2 dB

Over Seven Effective Bits

Spurious-Free Dynamic Range: -65 dB

No Missing Codes Guaranteed

### PRODUCT DESCRIPTION

28-Lead SSOP

The AD9281 is a complete dual channel, 28 MSPS, 8-bit CMOS ADC. The AD9281 is optimized specifically for applications where close matching between two ADCs is required (e.g., I/Q channels in communications applications). The 28 MHz sampling rate and wide input bandwidth will cover both narrowband and spread-spectrum channels. The AD9281 integrates two 8-bit, 28 MSPS ADCs, two input buffer amplifiers, an internal voltage reference and multiplexed digital output buffers.

Each ADC incorporates a simultaneous sampling sample-and-hold amplifier at its input. The analog inputs are buffered; no external input buffer op amp will be required in most applications. The ADCs are implemented using a multistage pipeline architecture that offers accurate performance and guarantees no missing codes. The outputs of the ADCs are ported to a multiplexed digital output buffer.

The AD9281 is manufactured on an advanced low cost CMOS process, operates from a single supply from 2.7 V to 5.5 V, and consumes 225 mW of power (on 3 V supply). The AD9281 input structure accepts either single-ended or differential signals, providing excellent dynamic performance up to and beyond 14 MHz Nyquist input frequencies.

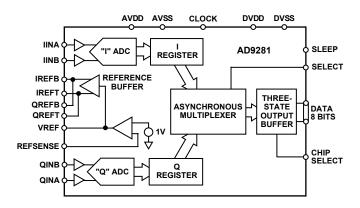

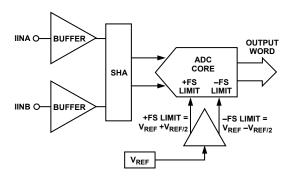

### **FUNCTIONAL BLOCK DIAGRAM**

### **PRODUCT HIGHLIGHTS**

- Dual 8-Bit, 28 MSPS ADC

A pair of high performance 28 MSPS ADCs that are optimized for spurious free dynamic performance are provided for encoding of I and Q or diversity channel information.

- Low Power

Complete CMOS Dual ADC function consumes a low

225 mW on a single supply (on 3 V supply). The AD9281 operates on supply voltages from 2.7 V to 5.5 V.

- On-Chip Voltage Reference

The AD9281 includes an on-chip compensated bandgap voltage reference pin programmable for 1 V or 2 V.

- 4. On-chip analog input buffers eliminate the need for external op amps in most applications.

- Single 8-Bit Digital Output Bus

The AD9281 ADC outputs are interleaved onto a single output bus saving board space and digital pin count.

- Small Package

The AD9281 offers the complete integrated function in a compact 28-lead SSOP package.

- 7. Product Family

The AD9281 dual ADC is pin compatible with a dual 10-bit ADC (AD9201).

# $\textbf{AD9281-SPECIFICATIONS} \quad \text{(AVDD} = +3 \text{ V, DVDD} = +3 \text{ V, F}_{\text{SAMPLE}} = 28 \text{ MSPS, VREF} = 2 \text{ V, INB} = 0.5 \text{ V, T}_{\text{MIN}} \text{ to T}_{\text{MAX}} \quad \text{unless otherwise noted)}$

| Parameter                                                                                                                                                                                                                                                                                                                                       | Symbol                                                                                                            | Min                  | Typ                                                                                 | Max                          | Units                                                    | Condition                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|

| RESOLUTION                                                                                                                                                                                                                                                                                                                                      |                                                                                                                   |                      | 8                                                                                   |                              | Bits                                                     |                                                                                 |

| CONVERSION RATE                                                                                                                                                                                                                                                                                                                                 | F <sub>S</sub>                                                                                                    |                      | 28                                                                                  |                              | MHz                                                      | (32 MHz at +25°C)                                                               |

| DC ACCURACY Differential Nonlinearity Integral Nonlinearity Differential Nonlinearity (SE) <sup>1</sup> Integral Nonlinearity (SE) <sup>1</sup> Zero-Scale Error, Offset Error Full-Scale Error, Gain Error Gain Match Offset Match                                                                                                             | DNL<br>INL<br>DNL<br>INL<br>E <sub>ZS</sub><br>E <sub>FS</sub>                                                    |                      | $\pm 0.1$ $\pm 0.25$ $\pm 0.2$ $\pm 0.3$ $\pm 1$ $\pm 1.2$ $\pm 0.2$ $\pm 1.2$      | ±1.0<br>±1.5<br>±3.2<br>±5.4 | LSB<br>LSB<br>LSB<br>% FS<br>% FS<br>LSB<br>LSB          | REFT = 1.0 V, REFB = 0.0 V<br>REFT = 1.0 V, REFB = 0.0 V                        |

| ANALOG INPUT Input Voltage Range Input Capacitance Aperture Delay Aperture Uncertainty (Jitter) Aperture Delay Match Input Bandwidth (-3 dB) Small Signal (-20 dB) Full Power (0 dB)                                                                                                                                                            | $\begin{array}{c} \text{AIN} \\ \text{C}_{\text{IN}} \\ \text{t}_{\text{AP}} \\ \text{t}_{\text{AJ}} \end{array}$ | -0.5                 | AVDE<br>2<br>4<br>2<br>2<br>2<br>240<br>245                                         | 0/2                          | V<br>pF<br>ns<br>ps<br>ps<br>MHz<br>MHz                  |                                                                                 |

| INTERNAL REFERENCE Output Voltage (1 V Mode) Output Voltage Tolerance (1 V Mode) Output Voltage (2 V Mode) Output Voltage Tolerance (2 V Mode) Load Regulation (1 V Mode) Load Regulation (2 V Mode)                                                                                                                                            | VREF<br>VREF<br>VREF                                                                                              |                      | $ \begin{array}{c} 1 \\ \pm 10 \\ 2 \\ \pm 15 \\ \pm 10 \\ \pm 15 \end{array} $     | ±35                          | V<br>mV<br>V<br>mV<br>mV                                 | REFSENSE = VREF REFSENSE = GND  1 mA Load Current 1 mA Load Current             |

| POWER SUPPLY Operating Voltage  Supply Current  Power Consumption Power-Down Power Supply Rejection                                                                                                                                                                                                                                             | AVDD<br>DVDD<br>I <sub>AVDD</sub><br>I <sub>DVDD</sub><br>P <sub>D</sub><br>PSR                                   | 2.7<br>2.7           | 3<br>3<br>75<br>0.1<br>225<br>16<br>0.15                                            | 5.5<br>5.5<br>260<br>0.75    | V<br>V<br>mA<br>mA<br>mW<br>mW                           | STBY = AVDD, Clock Low                                                          |

| DYNAMIC PERFORMANCE <sup>2</sup> Signal-to-Noise and Distortion f = 3.58 MHz f = 14 MHz Signal-to-Noise f = 3.58 MHz f = 14 MHz Total Harmonic Distortion f = 3.58 MHz f = 14 MHz Spurious Free Dynamic Range f = 3.58 MHz f = 14 MHz Two-Tone Intermodulation Distortion <sup>3</sup> Differential Phase Differential Gain Crosstalk Rejection | SINAD  SNR  THD  SFDR  IMD  DP  DG                                                                                | 46.4<br>47.8<br>49.6 | 49.1<br>48<br>49.2<br>48.5<br>-67.5<br>-60<br>65<br>56<br>-58<br>0.2<br>0.08<br>-62 | -49.5                        | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB | f = 44.9 MHz and 45.52 MHz<br>NTSC 40 IRE Mod Ramp<br>F <sub>S</sub> = 14.3 MHz |

-2- REV. F

| Parameter                             | Symbol            | Min  | Typ   | Max | Units  | Condition                      |

|---------------------------------------|-------------------|------|-------|-----|--------|--------------------------------|

| DYNAMIC PERFORMANCE (SE) <sup>1</sup> |                   |      |       |     |        |                                |

| Signal-to-Noise and Distortion        | SINAD             |      |       |     |        |                                |

| f = 3.58  MHz                         |                   |      | 47.2  |     | dB     |                                |

| Signal-to-Noise                       | SNR               |      |       |     |        |                                |

| f = 3.58  MHz                         |                   |      | 48    |     | dB     |                                |

| Total Harmonic Distortion             | THD               |      |       |     |        |                                |

| f = 3.58  MHz                         |                   |      | -55   |     | dB     |                                |

| Spurious Free Dynamic Range           | SFDR              |      |       |     |        |                                |

| f = 3.58 MHz                          |                   |      | -58   |     | dB     |                                |

| DIGITAL INPUTS                        |                   |      |       |     |        |                                |

| High Input Voltage                    | $V_{\mathrm{IH}}$ | 2.4  |       |     | V      |                                |

| Low Input Voltage                     | $V_{IL}$          |      |       | 0.3 | V      |                                |

| DC Leakage Current                    | $I_{IN}$          |      | ±6    |     | μA     |                                |

| Input Capacitance                     | $C_{IN}$          |      | 2     |     | pF     |                                |

| LOGIC OUTPUT (with DVDD = 3 V)        |                   |      |       |     |        |                                |

| High Level Output Voltage             |                   |      |       |     |        |                                |

| $(I_{OH} = 50 \mu A)$                 | V <sub>OH</sub>   |      | 2.88  |     | V      |                                |

| Low Level Output Voltage              | On                |      |       |     |        |                                |

| $(I_{OL} = 1.5 \text{ mA})$           | $V_{OL}$          |      | 0.095 |     | V      |                                |

| LOGIC OUTPUT (with DVDD = 5 V)        |                   |      |       |     |        |                                |

| High Level Output Voltage             |                   |      |       |     |        |                                |

| $(I_{OH} = 50 \mu\text{A})$           | V <sub>OH</sub>   |      | 4.5   |     | V      |                                |

| Low Level Output Voltage              | ·OH               |      | 1.5   |     | ,      |                                |

| $(I_{OL} = 1.5 \text{ mA})$           | $V_{OL}$          |      | 0.4   |     | V      |                                |

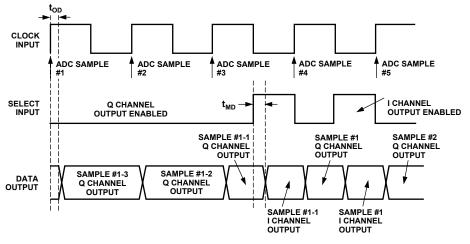

| Data Valid Delay                      | t <sub>OD</sub>   |      | 11    |     | ns     |                                |

| MUX Select Delay                      | t <sub>MD</sub>   |      | 7     |     | ns     |                                |

| Data Enable Delay                     | t <sub>ED</sub>   |      | 13    |     | ns     | $C_L = 20$ pF. Output Level to |

|                                       |                   |      |       |     |        | 90% of Final Value             |

| Data High-Z Delay                     | t <sub>DHZ</sub>  |      | 13    |     | ns     |                                |

| CLOCKING                              |                   |      |       |     |        |                                |

| Clock Pulsewidth High                 | t <sub>CH</sub>   | 16.9 |       |     | ns     |                                |

| Clock Pulsewidth Low                  | $t_{\mathrm{CL}}$ | 16.9 |       |     | ns     |                                |

| Pipeline Latency                      |                   |      | 3.0   |     | Cycles |                                |

### NOTES

Specifications subject to change without notice.

Figure 1. ADC Timing

$<sup>^{1}</sup>$ SE is single ended input, REFT = 1.5 V, REFB = -0.5 V.

$<sup>^{2}</sup>$ AIN differential 2 V p-p, REFT = 1.5 V, REFB = -0.5 V.

<sup>&</sup>lt;sup>3</sup>IMD referred to larger of two input signals.

### **ABSOLUTE MAXIMUM RATINGS\***

|                      | With<br>Respect |      |            |       |

|----------------------|-----------------|------|------------|-------|

| Parameter            | to              | Min  | Max        | Units |

| AVDD                 | AVSS            | -0.3 | +6.5       | V     |

| DVDD                 | DVSS            | -0.3 | +6.5       | V     |

| AVSS                 | DVSS            | -0.3 | +0.3       | V     |

| AVDD                 | DVDD            | -6.5 | +6.5       | V     |

| CLK                  | AVSS            | -0.3 | AVDD + 0.3 | V     |

| Digital Outputs      | DVSS            | -0.3 | DVDD + 0.3 | V     |

| AINA, AINB           | AVSS            | -1.0 | AVDD + 0.3 | V     |

| VREF                 | AVSS            | -0.3 | AVDD + 0.3 | V     |

| REFSENSE             | AVSS            | -0.3 | AVDD + 0.3 | V     |

| REFT, REFB           | AVSS            | -0.3 | AVDD + 0.3 | V     |

| Junction Temperature |                 |      | +150       | °C    |

| Storage Temperature  |                 | -65  | +150       | °C    |

| Lead Temperature     |                 |      |            |       |

| 10 sec               |                 |      | +300       | °C    |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

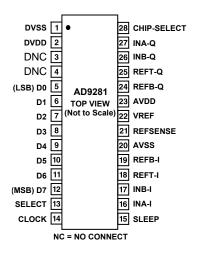

### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| D:         |             |                                        |

|------------|-------------|----------------------------------------|

| Pin<br>No. | Name        | Description                            |

| 1          | DVSS        | Digital Ground                         |

| 2          | DVDD        | Digital Supply                         |

| 3          | DNC         | Do not connect                         |

| 4          | DNC         | Do not connect                         |

| 5          | D0          | Bit 0 (LSB)                            |

| 6          | D1          | Bit 1                                  |

| 7          | D2          | Bit 2                                  |

| 8          | D3          | Bit 3                                  |

| 9          | D4          | Bit 4                                  |

| 10         | D5          | Bit 5                                  |

| 11         | D6          | Bit 6                                  |

| 12         | D7          | Bit 7 (MSB)                            |

| 13         | SELECT      | Hi I Channel Out, Lo Q Channel Out     |

| 14         | CLOCK       | Clock                                  |

| 15         | SLEEP       | Hi Power Down, Lo Normal Operation     |

| 16         | INA-I       | I Channel, A Input                     |

| 17         | INB-I       | I Channel, B Input                     |

| 18         | REFT-I      | Top Reference Decoupling, I Channel    |

| 19         | REFB-I      | Bottom Reference Decoupling, I Channel |

| 20         | AVSS        | Analog Ground                          |

| 21         | REFSENSE    | Reference Select                       |

| 22         | VREF        | Internal Reference Output              |

| 23         | AVDD        | Analog Supply                          |

| 24         | REFB-Q      | Bottom Reference Decoupling, Q Channel |

| 25         | REFT-Q      | Top Reference Decoupling, Q Channel    |

| 26         | INB-Q       | Q Channel B Input                      |

| 27         | INA-Q       | Q Channel A Input                      |

| 28         | CHIP-SELECT | Hi-High Impedance, Lo-Normal Operation |

## DEFINITIONS OF SPECIFICATIONS INTEGRAL NONLINEARITY (INL)

Integral nonlinearity refers to the deviation of each individual code from a line drawn from "zero" through "full scale." The point used as "zero" occurs 1/2 LSB before the first code transition. "Full scale" is defined as a level 1 1/2 LSBs beyond the last code transition. The deviation is measured from the center of each particular code to the true straight line.

## DIFFERENTIAL NONLINEARITY (DNL, NO MISSING CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. It is often specified in terms of the resolution for which no missing codes (NMC) are guaranteed.

### CAUTION -

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9281 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

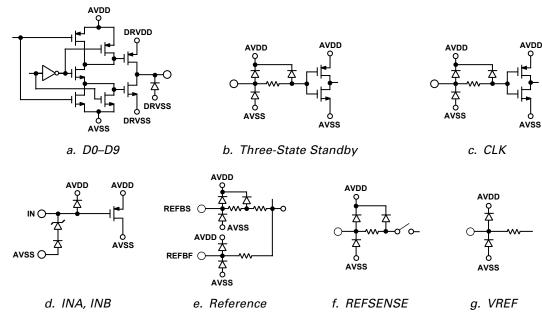

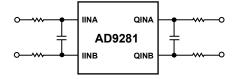

Figure 2. Equivalent Circuits

### **OFFSET ERROR**

The first transition should occur at a level 1 LSB above "zero." Offset is defined as the deviation of the actual first code transition from that point.

### **OFFSET MATCH**

The change in offset error between I and Q channels.

### **EFFECTIVE NUMBER OF BITS (ENOB)**

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula,

$$N = (SINAD - 1.76)/6.02$$

It is possible to get a measure of performance expressed as N, the effective number of bits.

Thus, effective number of bits for a device for sine wave inputs at a given input frequency can be calculated directly from its measured SINAD.

### TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

### SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. The value for SNR is expressed in decibels.

### SPURIOUS FREE DYNAMIC RANGE (SFDR)

The difference in dB between the rms amplitude of the input signal and the peak spurious signal.

#### **GAIN ERROR**

The first code transition should occur for an analog value 1 LSB above nominal negative full scale. The last transition should occur for an analog value 1 LSB below the nominal positive full

scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between the first and last code transitions.

#### **GAIN MATCH**

The change in gain error between I and Q channels.

### PIPELINE DELAY (LATENCY)

The number of clock cycles between conversion initiation and the associated output data being made available. New output data is provided every rising clock edge.

### MUX SELECT DELAY

The delay between the change in SELECT pin data level and valid data on output pins.

### POWER SUPPLY REJECTION

The specification shows the maximum change in full scale from the value with the supply at the minimum limit to the value with the supply at its maximum limit.

### **APERTURE JITTER**

Aperture jitter is the variation in aperture delay for successive samples and is manifested as noise on the input to the A/D.

### APERTURE DELAY

Aperture delay is a measure of the Sample-and-Hold Amplifier (SHA) performance and is measured from the rising edge of the clock input to when the input signal is held for conversion.

## SIGNAL-TO-NOISE AND DISTORTION (S/N+D, SINAD) RATIO

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

REV. F \_5\_

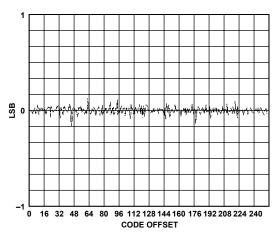

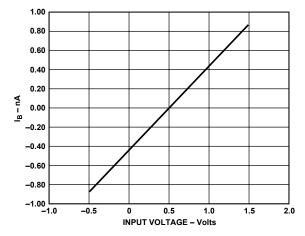

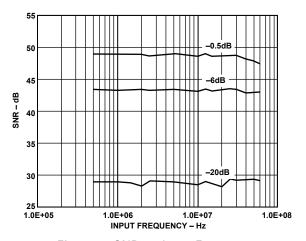

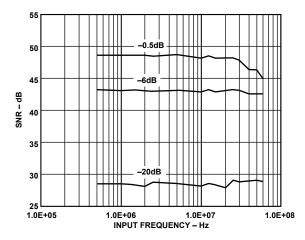

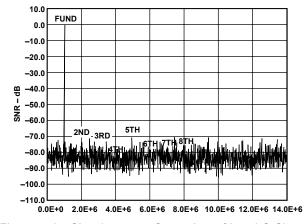

## **AD9281-Typical Characteristic Curves**

$(AVDD = +3 V, DVDD = +3 V, F_S = 28 MHz (50\% duty cycle), 2 V input span from -0.5 V to +1.5 V, 2 V internal reference unless otherwise noted)$

-6-

Figure 3. Typical INL

Figure 4. Typical DNL

Figure 5. Input Bias Current vs. Input Voltage

Figure 6. SNR vs. Input Frequency

Figure 7. SINAD vs. Input Frequency

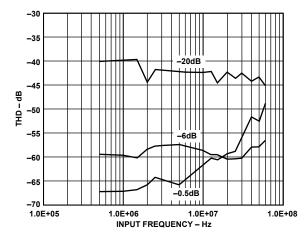

Figure 8. THD vs. Input Frequency

REV. F

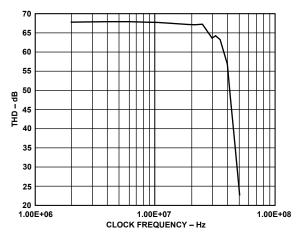

Figure 9. THD vs. Clock Frequency

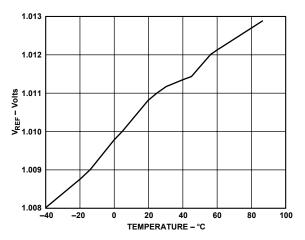

Figure 10. Voltage Reference Error vs. Temperature

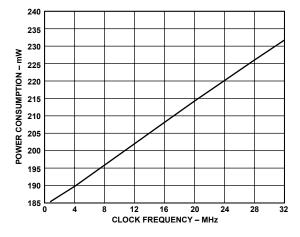

Figure 11. Power Consumption vs. Clock Frequency

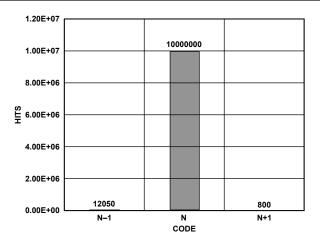

Figure 12. Grounded Input Histogram

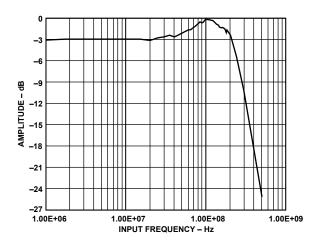

Figure 13. Full Power Bandwidth

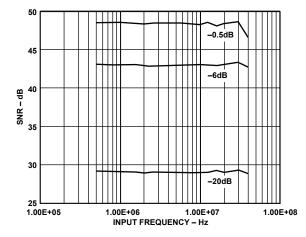

Figure 14. SNR vs. Input Frequency (Single-Ended)

REV. F \_\_7\_

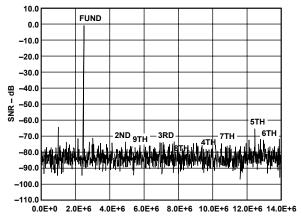

Figure 15a. Simultaneous Operation of I and Q Channels

Figure 15b. Simultaneous Operation of I and Q Channels

### THEORY OF OPERATION

The AD9281 integrates two A/D converters, two analog input buffers, an internal reference and reference buffer, and an output multiplexer. For clarity, this data sheet refers to the two converters as "I" and "O." The two A/D converters simultaneously sample their respective inputs on the rising edge of the input clock. The two converters distribute the conversion operation over several smaller A/D sub-blocks, refining the conversion with progressively higher accuracy as it passes the result from stage to stage. As a consequence of the distributed conversion, each converter requires a small fraction of the 256 comparators used in a traditional flash-type 8-bit ADC. A sample-and-hold function within each of the stages permits the first stage to operate on a new input sample while the following stages continue to process previous samples. This results in a "pipeline processing" latency of three clock periods between when an input sample is taken and when the corresponding ADC output is updated into the output registers.

The AD9281 integrates input buffer amplifiers to drive the analog inputs of the converters. In most applications, these input amplifiers eliminate the need for external op amps for the input signals. The input structure is fully differential, but the SHA common-mode response has been designed to allow the

converter to readily accommodate either single-ended or differential input signals. This differential structure makes the part capable of accommodating a wide range of input signals.

The AD9281 also includes an on-chip bandgap reference and reference buffer. The reference buffer shifts the ground-referred reference to levels more suitable for use by the internal circuits of the converter. Both converters share the same reference and reference buffer. This scheme provides for the best possible gain match between the converters while simultaneously minimizing the channel-to-channel crosstalk.

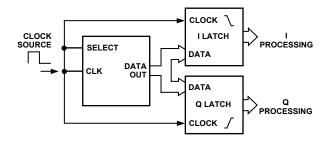

Each A/D converter has its own output latch, which updates on the rising edge of the input clock. A logic multiplexer, controlled through the SELECT pin, determines which channel is passed to the digital output pins. The output drivers have their own supply, allowing the part to be interfaced to a variety of logic families. The outputs can be placed in a high impedance state using the CHIP SELECT pin.

The AD9281 has great flexibility in its supply voltage. The analog and digital supplies may be operated from 2.7 V to 5.5 V, independently of one another.

### **ANALOG INPUT**

Figure 16 shows an equivalent circuit structure for the analog input of one of the A/D converters. PMOS source-followers buffer the analog input pins from the charge kickback problems normally associated with switched capacitor ADC input structures. This produces a very high input impedance on the part, allowing it to be effectively driven from high impedance sources. This means that the AD9281 could even be driven directly by a passive antialias filter.

Figure 16. Equivalent Circuit for AD9281 Analog Inputs

The source followers inside the buffers also provide a level-shift function of approximately 1 V, allowing the AD9281 to accept inputs at or below ground. One consequence of this structure is that distortion will result if the analog input comes within 1.4 V of the positive supply. For optimum high frequency distortion performance, the analog input signal should be centered according to Figure 27.

The capacitance load of the analog input pin is 4 pF to the analog supplies (AVSS, AVDD).

Full-scale setpoints may be calculated according to the following algorithm ( $V_{REF}$  may be internally or externally generated):

$$\begin{aligned} -F_S &= V_{REF} - (V_{REF}/2) \\ +F_S &= V_{REF} + (V_{REF}/2) \\ V_{SPAN} &= V_{REF} \end{aligned}$$

\_8\_ REV. F

The AD9281 can accommodate a variety of input spans between 1 V and 2 V. For spans of less than 1 V, expect a proportionate degradation in SNR. Use of a 2 V span will provide the best noise performance. 1 V spans will provide lower distortion when using a 3 V analog supply. Users wishing to run with larger full-scales are encouraged to use a 5 V analog supply (AVDD).

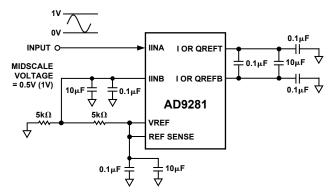

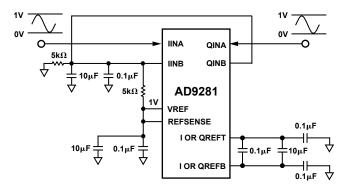

**Single-Ended Inputs:** For single-ended input signals, the signal is applied to one input pin and the other input pin is tied to a midscale voltage. This midscale voltage defines the center of the full-scale span for the input signal.

EXAMPLE: For a single-ended input range from 0 V to 1 V applied to IINA, we would configure the converter for a 1 V reference (see Figure 17) and apply 0.5 V to IINB.

Figure 17. Example Configuration for 0 V–1 V Single-Ended Input Signal

Note that since the inputs are high impedance, this reference level can easily be generated with an external resistive divider with large resistance values (to minimize power dissipation). A decoupling capacitor is recommended on this input to minimize the high frequency noise-coupling onto this pin. Decoupling should occur close to the ADC.

### **Differential Inputs**

Use of differential input signals can provide greater flexibility in input ranges and bias points, as well as offering improvements in distortion performance, particularly for high frequency input signals. Users with differential input signals will probably want to take advantage of the differential input structure of the AD9281. Performance is still very good for single-ended inputs. Converting a single-ended input to a differential signal for application to the converter is probably only worth considering for very high frequency input signals.

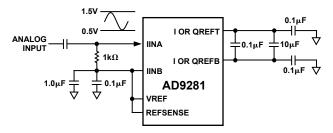

#### **AC-Coupled Inputs**

If the signal of interest has no dc component, ac coupling can be easily used to define an optimum bias point. Figure 18 illustrates one recommended configuration. The voltage chosen for the dc bias point (in this case the 1 V reference) is applied to both IINA and IINB pins through 1 k $\Omega$  resistors (R1 and R2). IINA is coupled to the input signal through Capacitor C1, while IINB is decoupled to ground through Capacitor C2.

Figure 18. Example Configuration for 0.5 V-1.5 V ac Coupled Single-Ended Inputs

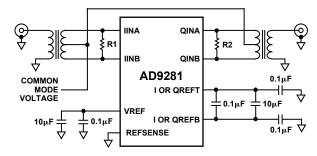

### **Transformer Coupled Inputs**

Another option for input ac coupling is to use a transformer. This not only provides dc rejection, but also allows truly differential drive of the AD9281's analog inputs, which will provide the optimal distortion performance. Figure 19 shows a recommended transformer input drive configuration. Resistors R1 and R2 define the termination impedance of the transformer coupling. The center tap of the transformer secondary is tied to the common-mode voltage, establishing the dc bias point for the analog inputs.

Figure 19. Example Configuration for Transformer Coupled Inputs

Crosstalk: The internal layout of the AD9281, as well as its pinout, was configured to minimize the crosstalk between the two input signals. Users wishing to minimize high frequency crosstalk should take care to provide the best possible decoupling for input pins (see Figure 20). R and C values will make a pole dependant on antialiasing requirements. Decoupling is also required on reference pins and power supplies (see Figure 21).

Figure 20. Input Loading

Figure 21. Reference and Power Supply Decoupling

### REFERENCE AND REFERENCE BUFFER

The reference and buffer circuitry on the AD9281 is configured for maximum convenience and flexibility. An illustration of the equivalent reference circuit is show in Figure 26. The user can select from five different reference modes through appropriate pin-strapping (see Table I below). These pin strapping options cause the internal circuitry to reconfigure itself for the appropriate operating mode.

Table I. Table of Modes

| Mode         | Input Span     | REFSENSE Pin | Figure |

|--------------|----------------|--------------|--------|

| 1 V          | 1 V            | VREF         | 22     |

| 2 V          | 2 V            | AGND         | 23     |

| Programmable |                | See Figure   | 24     |

| External     | = External Ref | AVDD         | 25     |

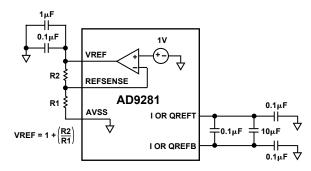

**1 V Mode (Figure 22)**—provides a 1 V reference and 1 V input full scale. Recommended for applications wishing to optimize high frequency performance, or any circuit on a supply voltage of less than 4 V. The part is placed in this mode by shorting the REFSENSE pin to the VREF pin.

Figure 22. 0 V to 1 V Input

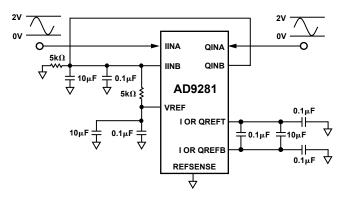

**2 V Mode (Figure 23)**—provides a 2 V reference and 2 V input full scale. Recommended for noise sensitive applications on 5 V supplies. The part is placed in 2 V reference mode by grounding (shorting to AVSS) the REFSENSE pin.

Figure 23. 0 V to 2 V Input

Externally Set Voltage Mode (Figure 24)—this mode uses the on-chip reference, but scales the exact reference level though the use of an external resistor divider network. VREF is wired to the top of the network, with the REFSENSE wired to the tap point in the resistor divider. The reference level (and input full scale) will be equal to  $1 \text{ V} \times (R1 + R2)/R1$ . This method can be used for voltage levels from 0.7 V to 2.5 V.

Figure 24. Programmable Reference

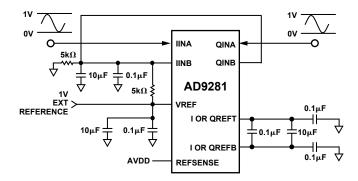

**External Reference Mode (Figure 25)**—in this mode, the onchip reference is disabled, and an external reference applied to the VREF pin. This mode is achieved by tying the REFSENSE pin to AVDD.

Figure 25. External Reference

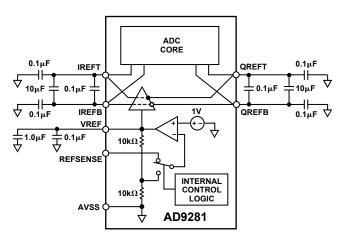

Reference Buffer—The reference buffer structure takes the voltage on the VREF pin and level-shifts and buffers it for use by various sub-blocks within the two A/D converters. The two converters share the same reference buffer amplifier to maintain the best possible gain match between the two converters. In the interests of minimizing high frequency crosstalk, the buffered references for the two converters are separately decoupled on the IREFB, IREFT, QREFB and QREFT pins, as illustrated in Figure 26.

\_10\_ REV. F

Figure 26. Reference Buffer Equivalent Circuit and External Decoupling Recommendation

For best results in both noise suppression and robustness against crosstalk, the 4-capacitor buffer decoupling arrangement shown in Figure 26 is recommended. This decoupling should

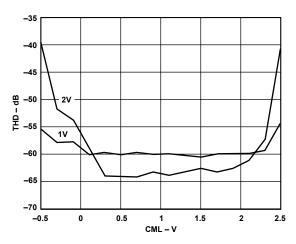

a. Differential Input, 3 V Supplies

b. Differential Input, 5 V Supplies

feature chip capacitors located close to the converter IC. The capacitors are connected to either IREFT/IREFB or QREFT/QREFB. A connection to both sides is not required.

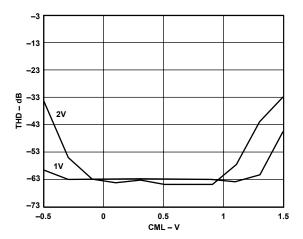

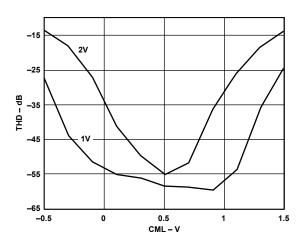

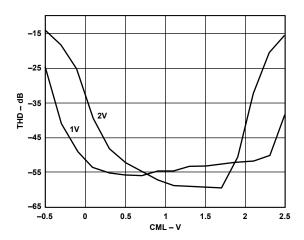

### **COMMON-MODE PERFORMANCE**

Attention to the common-mode point of the analog input voltage can improve the performance of the AD9281. Figure 27 illustrates THD as a function of common-mode voltage (center point of the analog input span) and power supply.

Inspection of the curves will yield the following conclusions:

- 1. An AD9281 running with AVDD = 5 V is the easiest to drive

- 2. Differential inputs are the most insensitive to common-mode voltage.

- An AD9281 powered by AVDD = 3 V and a single ended input, should have a 1 V span with a common-mode voltage of 0.75 V.

c. Single-Ended Input, 3 V Supplies

d. Single-Ended Input, 5 V Supplies

Figure 27. THD vs. CML Input Span and Power Supply (Analog Input = 1 MHz)

REV. F \_\_11\_

### DIGITAL INPUTS AND OUTPUTS

Each of the AD9281 digital control inputs, CHIP SELECT, CLOCK, SELECT and SLEEP are referenced to AVDD and AVSS. Switching thresholds will be AVDD/2.

The format of the digital output is straight binary. A low power mode feature is provided such that for STBY = HIGH and the clock disabled, the static power of the AD9281 will drop below 22 mW.

#### **CLOCK INPUT**

The AD9281 clock input is internally buffered with an inverter powered from the AVDD pin. This feature allows the AD9281 to accommodate either +5 V or +3.3 V CMOS logic input signal swings with the input threshold for the CLK pin nominally at AVDD/2.

The pipelined architecture of the AD9281 operates on both rising and falling edges of the input clock. To minimize duty cycle variations the logic family recommended to drive the clock input is high speed or advanced CMOS (HC/HCT, AC/ACT) logic. CMOS logic provides both symmetrical voltage threshold levels and sufficient rise and fall times to support 28 MSPS operation. Running the part at slightly faster clock rates may be possible, although at reduced performance levels. Conversely, some slight performance improvements might be realized by clocking the AD9281 at slower clock rates.

The power dissipated by the output buffers is largely proportional to the clock frequency; running at reduced clock rates provides a reduction in power consumption.

### **DIGITAL OUTPUTS**

Each of the on-chip buffers for the AD9281 output bits (D0–D9) is powered from the DVDD supply pin, separate from AVDD. The output drivers are sized to handle a variety of logic families while minimizing the amount of glitch energy generated. In all cases, a fan-out of one is recommended to keep the capacitive load on the output data bits below the specified 20 pF level.

For DVDD = 5 V, the AD9281 output signal swing is compatible with both high speed CMOS and TTL logic families. For TTL, the AD9281 on-chip, output drivers were designed to support several of the high speed TTL families (F, AS, S). For applications where the clock rate is below 28 MSPS, other TTL families may be appropriate. For interfacing with lower voltage CMOS logic, the AD9281 sustains 28 MSPS operation with DVDD = 3 V. In all cases, check your logic family data sheets for compatibility with the AD9281's Specification table.

A 2 ns reduction in output delays can be achieved by limiting the logic load to 5 pF per output line.

### THREE-STATE OUTPUTS

The digital outputs of the AD9281 can be placed in a high impedance state by setting the CHIP SELECT pin to HIGH. This feature is provided to facilitate in-circuit testing or evaluation.

#### **SELECT**

When the select pin is held LOW, the output word will present the "Q" level. When the select pin is held HIGH, the "I" level will be presented to the output word (see Figure 1).

The AD9281's select and clock pins may be driven by a common signal source. The data will change in 5 ns to 11 ns after the edges of the input pulse. The user must make sure the interface latches have sufficient hold time for the AD9281's delays (see Figure 28).

Figure 28. Typical De-Mux Connection

### **APPLICATIONS**

### USING THE AD9281 FOR QAM DEMODULATION

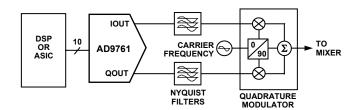

QAM is one of the most widely used digital modulation schemes in digital communication systems. This modulation technique can be found in both FDMA as well as spread spectrum (i.e., CDMA) based systems. A QAM signal is a carrier frequency which is both modulated in amplitude (i.e., AM modulation) and in phase (i.e., PM modulation). At the transmitter, it can be generated by independently modulating two carriers of identical frequency but with a 90° phase difference. This results in an inphase (I) carrier component and a quadrature (Q) carrier component at a 90° phase shift with respect to the I component. The I and O components are then summed to provide a OAM signal at the specified carrier or IF frequency. Figure 29 shows a typical analog implementation of a QAM modulator using a dual 10-bit DAC with 2× interpolation, the AD9761. A QAM signal can also be synthesized in the digital domain thus requiring a single DAC to reconstruct the OAM signal. The AD9853 is an example of a complete (i.e., DAC included) digital OAM modulator.

Figure 29. Typical Analog QAM Modulator Architecture

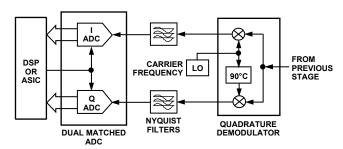

At the receiver, the demodulation of a QAM signal back into its separate I and Q components is essentially the modulation process explain above but in the reverse order. A common and traditional implementation of a QAM demodulator is shown in Figure 30. In this example, the demodulation is performed in the analog domain using a dual, matched ADC and a quadrature demodulator to recover and digitize the I and O baseband signals. The quadrature demodulator is typically a single IC containing two mixers and the appropriate circuitry to generate the necessary 90° phase shift between the I and Q mixers' local oscillators. Before being digitized by the ADCs, the mixed down baseband I and Q signals are filtered using matched analog filters. These filters, often referred to as Nyquist or Pulse-Shaping filters, remove images-from the mixing process and any out-of-band. The characteristics of the matching Nyquist filters are well defined to provide optimum signal-to-noise (SNR) performance while minimizing intersymbol interference. The ADC's are typically simultaneously sampling their respective inputs at the OAM symbol rate or, most often, at a multiple of it if a digital filter follows the ADC. Oversampling and the use of digital filtering eases the implementation and complexity of the analog filter. It also allows for enhanced digital processing for both carrier and symbol recovery and tuning purposes. The use of a dual ADC such as the AD9281 ensures excellent gain, offset, and phase matching between the I and Q channels.

Figure 30. Typical Analog QAM Demodulator

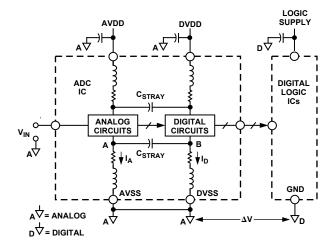

### **GROUNDING AND LAYOUT RULES**

As is the case for any high performance device, proper grounding and layout techniques are essential in achieving optimal performance. The analog and digital grounds on the AD9281 have been separated to optimize the management of return currents in a system. Grounds should be connected near the ADC. It is recommended that a printed circuit board (PCB) of at least four layers, employing a ground plane and power planes, be used with the AD9281. The use of ground and power planes offers distinct advantages:

- 1. The minimization of the loop area encompassed by a signal and its return path.

- 2. The minimization of the impedance associated with ground and power paths.

- 3. The inherent distributed capacitor formed by the power plane, PCB insulation and ground plane.

Figure 31. Ground and Power Consideration

These characteristics result in both a reduction of electromagnetic interference (EMI) and an overall improvement in performance.

It is important to design a layout that prevents noise from coupling onto the input signal. Digital signals should not be run in parallel with the input signal traces and should be routed away from the input circuitry. Separate analog and digital grounds should be joined together directly under the AD9281 in a solid ground plane. The power and ground return currents must be carefully managed. A general rule of thumb for mixed signal layouts dictates that the return currents from digital circuitry should not pass through critical analog circuitry.

Transients between AVSS and DVSS will seriously degrade performance of the ADC.

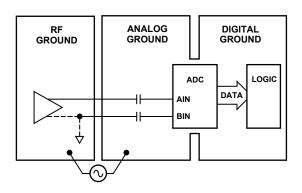

If the user cannot tie analog ground and digital ground together at the ADC, he should consider the configuration in Figure 32.

Another input and ground technique is shown in Figure 32. A separate ground plane has been split for RF or hard to manage signals. These signals can be routed to the ADC differentially or single ended (i.e., both can either be connected to the driver or RF ground). The ADC will perform well with several hundred mV of noise or signals between the RF and ADC analog ground.

Figure 32. RF Ground Scheme

REV. F –13–

### **REVISION HISTORY**

1/11—Rev. E to Rev. F

| Updated Format                             | Universal |

|--------------------------------------------|-----------|

| Changes to Pin Configuration Diagram       | 4         |

| Changes to Pin Function Descriptions Table | 4         |

| Removed Evaluation Boards; Renumbered      |           |

| Sequentially                               | 14 to 18  |

| Changes to Ordering Guide                  | 15        |

8/99—Rev. D to Rev. E

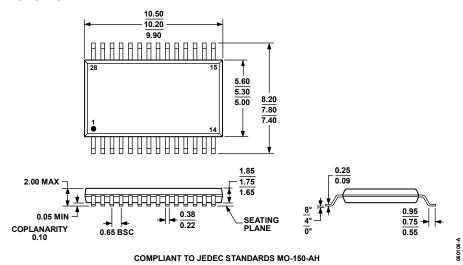

### **OUTLINE DIMENSIONS**

Figure 33. 28-Lead Shrink Small Outline Package [SSOP] (RS-28) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description | Package Option |

|-----------------------|-------------------|---------------------|----------------|

| AD9281ARS             | −40°C to +85°C    | 28-Lead SSOP        | RS-28          |

| AD9281ARSRL           | -40°C to +85°C    | 28-Lead SSOP        | RS-28          |

| AD9281ARSZ            | -40°C to +85°C    | 28-Lead SSOP        | RS-28          |

| AD9281ARSZRL          | -40°C to +85°C    | 28-Lead SSOP        | RS-28          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

<sup>&</sup>lt;sup>2</sup> RS = Shrink Small Outline.