**PRODUCTION DATA SHEET**

#### **DESCRIPTION**

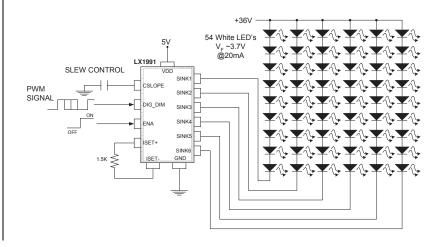

**LED Display Driver:** This six channel current sink driver is ideal for controlling brightness and hue of high quality dimmable LED displays. High accuracy, dual mode dimming, and controlled current switching time provides consistent color hue, at brightness ratios of up to 1000:1, and keeps electro magnetic emissions in check.

Its wide compliance voltage range combined with 43 volt breakdown capability make the LX1991 ideal for automotive in-dash displays.

**Precision current control**: Precision current mirror circuitry sets all channels to the same current with a single programming input. Sinking current value can be programmed up to 30 mA per channel with a single resistor or potentiometer from  $I_{\text{SET-}}$ . Channel to channel matching is typically within  $\pm 1$  percent of channel mean at the rated output current.

**Dual Mode Dimming:** Display dimming can be achieved by controlling either current amplitude or duty cycle, and both methods can be employed at the same time.

**1000:1 Dimming Range:** The DIG\_DIM input accepts a TTL or CMOS logic signal that controls duty cycle of the output currents.

Independent Channels: The six channels feature independent regulation with respect to output voltage, so one does not affect the others. Any one or more outputs can be left unloaded without affecting current regulation of the other channels. Multiple channels can also be connected together to sink more current in a single load.

**EMI Control:** Rise and fall time of sink currents are precisely controlled by placing a capacitor on the SLOPE\_C pin. Special control circuitry maintains symmetrical rise and fall times, preserving the LX1991's ability to provide accurate output current response to very narrow input pulses on the DIG DIM pin.

**Power Handling:** The LX1991 is supplied in a 4x4 MLPQ package capable of 1.5 watts dissipation. Logic Enable: A separate input puts the LX1991 to sleep at less than 1 uA I<sub>DD</sub>.

$\textbf{IMPORTANT:} \ For \ the \ most \ current \ data, \ consult \ \textit{MICROSEMI'} \ s \ website: \ \textbf{http://www.microsemi.com}$

## **KEY FEATURES**

- Six precision independent current sink channels

- Simultaneous Analog and Digital Dimming Modes

- Precision programming of current rise & fall times

- 1% band gap reference

- 40 volt rated output stages

- 3V / 5V logic input compatible

- 1.5 watt power dissipation

- On-chip thermal shutdown

- 16 Pin 4 x 4 MLPQ Package

#### **BENEFITS**

- Consistent LED color hue results from high current accuracy

- 1000:1 dimming ratio with digital dimming

- Lowered emissions with current slope programming

- Reduced component count for compact designs

- Drive up to 108 colored LED's per IC (6 x 18 @ 2.1 volts)

- Drive up to 60 white or blue LED's per IC (6 x 10 @ 3.8 volts)

## PRODUCT HIGHLIGHT

| Bill of Materials |             |  |  |  |  |

|-------------------|-------------|--|--|--|--|

| 1                 | LX1991      |  |  |  |  |

| 1                 | Cap         |  |  |  |  |

| 1                 | Resistor    |  |  |  |  |

| 54                | White LEDs  |  |  |  |  |

| 57                | Total Count |  |  |  |  |

####

Note: Available in Tape & Reel. Append the letters "TR" to the part number. (i.e. LX1991ILQ-TR)

#### **PRODUCTION DATA SHEET**

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (VDD )                                           | 0.3v to 6V     |

|-----------------------------------------------------------------|----------------|

| Analog Output Voltage (SINK <sub>1</sub> to SINK <sub>6</sub> ) | 0.3V to 43V    |

| Analog Inputs (I <sub>SET</sub> )0.3                            | V to VDD +0.5V |

| Digital Inputs (ENABLE, DIG_DIM)0.3                             | V to VDD +0.5V |

| Operating Temperature Range                                     | 40°C – 85°C    |

| Storage Temperature Range                                       | 65°C – 150°C   |

| Maximum Junction Temperature                                    | 150°C          |

| Peak Package Solder Reflow Temp. (40 seconds max. exposure)     |                |

Note: Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of specified terminal.

### THERMAL DATA

LQ Plastic 4x4 MLPQ 16-Pin

| THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{\text{JC}}$ | 2.2°C/W |

|--------------------------------------------------------------|---------|

| THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{JA}$        | 36°C/W  |

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/ 4 layer pc-

board system. All of the above assume no ambient airflow.

The  $\theta_{\text{JA}}$  numbers are to MIL-STD-883D Method 1012.1

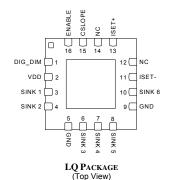

### PACKAGE PIN OUT

MSC 1991 xxxx

LQ PACKAGE MARKING xxxx Denotes Date Code / Lot Code

RoHS / Pb-free 100% Matte Tin Lead Finish

#### FUNCTIONAL PIN DESCRIPTION PIN NAME DESCRIPTION **GND** Ground Voltage Input, 4.5 to 5.5V input range. V<sub>DD</sub> is internally switched (see ENABLE) to remove power from chip. $V_{DD}$ SINK<sub>1</sub> -Current sink channels one through six. Each output sinks the programmed current from the V<sub>IFD</sub> supply to SINK<sub>6</sub> ground. Compliance voltage is from 1 volt minimum to the V<sub>LED</sub> supply maximum. A logic input that duty cycle modulates the output currents. All output currents are turned on at the programmed DIG DIM current value when DIG DIM is high and turned off when it is low. Compatible with both 3V and 5V logic. Chip Enable Input. If logic high, all functions are enabled. If logic low, internal power is disconnected from the **ENABLE** V<sub>DD</sub> pin, disabling all functions. Logic threshold is 1.6 ± 0.8V maximum over supply and temperature range. Maximum current into VDD when ENABLE < 0.4V is 1 µA. Current programming resistor pins. Output current in each channel is 24 times the current that flows from I<sub>SET+</sub> to I<sub>SET+</sub> I<sub>SET</sub>. I<sub>SET</sub> current is 1.26V / R<sub>SET</sub>. Connect resistor between I<sub>SET</sub>+ and I<sub>SET</sub>-I<sub>SET</sub>-Current rise and fall time programming capacitor. Rise and fall times increase in direct proportion to capacitor CSLOPE value. $C = 450\mu A * T_R \text{ or } T_F \text{ in microseconds, } C \text{ in picofarads.}$

#### **PRODUCTION DATA SHEET**

## RECOMMENDED OPERATING CONDITIONS

| Parameter                                                     | LX1991 |     |          | Units  |

|---------------------------------------------------------------|--------|-----|----------|--------|

| Faianietei                                                    | Min    | Тур | Max      | Ullits |

| Supply Voltage (V <sub>DD</sub> )                             | 4.5    |     | 5.5      | V      |

| ENABLE Input Voltage                                          | 0      |     | $V_{DD}$ | V      |

| DIG_DIM Input Voltage                                         | 0      |     | $V_{DD}$ | V      |

| C <sub>SLOPE</sub> Capacitance Range                          |        |     |          |        |

| I <sub>SET</sub> Voltage                                      | 0      |     | 1.26     | V      |

| R <sub>SET</sub> Current Programming Resistor Range           | 1      |     | 40       | ΚΩ     |

| SINK <sub>1</sub> To SINK <sub>6</sub> Output Voltage Range   | 0.5    | 3   | 40*      | V      |

| SINK <sub>1</sub> To SINK <sub>6</sub> Maximum Output Current |        |     | 30       | mA     |

<sup>\*</sup>At output voltages greater than 5V total power dissipation when using all six outputs at maximum current will exceed power rating of package and ambient of 85°C.

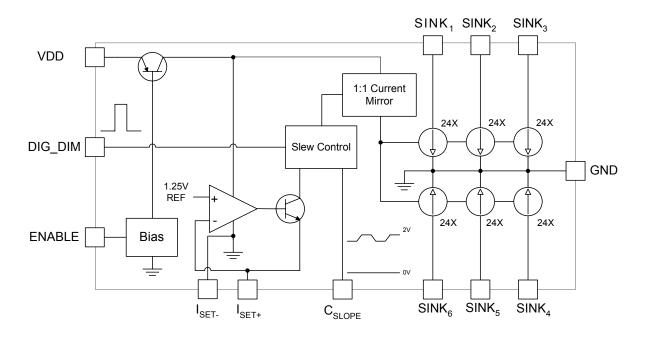

## SIMPLIFIED BLOCK DIAGRAM

Figure 1 – Simplified Block Diagram

#### **PRODUCTION DATA SHEET**

| and with the following test conditions: $V_{DD} =$                   |                          |                                                                   | _    | LX1991 |          | T                                                |

|----------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------|------|--------|----------|--------------------------------------------------|

| Parameter                                                            | Symbol                   | Test Conditions                                                   | Min  | Тур    |          |                                                  |

| POWER                                                                |                          |                                                                   | •    |        |          |                                                  |

| Power Supply Input Voltage                                           | $V_{DD}$                 |                                                                   | 4.5  | 5      | 5.5      | V                                                |

| Quiescent current                                                    | I <sub>DD ON</sub>       | VDD = 5V, ENABLE ≥ 2.4V; DIG_DIM ≥ 2.4V                           |      | 10     | 16       | mA                                               |

| Quiescent current                                                    | I <sub>DD OFF</sub>      | VDD = 5V, ENABLE ≥ 2.4V; DIG_DIM ≤ 0.8V                           |      | 3.6    | 6        | mA                                               |

| Sleep Current <sup>1</sup>                                           | I <sub>DD SLEEP</sub>    | VDD = 5V, V <sub>OUT</sub> = 40V, ENABLE ≤ 0.4V                   |      | 0.08   | 1        | μA                                               |

| ENABLE INPUT                                                         | DD_GEEE!                 | - 7 001 - 7                                                       |      |        | <u>I</u> | <u> </u>                                         |

| ENABLE Logic Threshold                                               | $V_{TH\_EN}$             |                                                                   | 0.8  | 1.6    | 2.4      | V                                                |

| Input Current                                                        | I <sub>IH ENABLE</sub>   | $V_{\text{ENABLE}} = V_{\text{DD}}$                               | 0.0  | 4.0    | 10       | μA                                               |

| Input Current                                                        | I <sub>IL ENABLE</sub>   | V <sub>ENABLE</sub> = 0V                                          |      | 0.4    | 1        | μΑ                                               |

| OUTPUT CURRENT                                                       | 'IL ENABLE               | V ENABLE 0                                                        |      | 1 0.1  | <u> </u> | _ μ, ι                                           |

| SINK x 30mA                                                          | SINK 30                  | VDD = 5V, SINK <sub>X</sub> = 3V, $R_{SFT}$ = 1.02K $\Omega$      | 28.4 | 30     | 31.6     | mA                                               |

| SINK x 20mA                                                          | SINK 20                  | VDD = 5V, SINK <sub>X</sub> = 3V, R <sub>SET</sub> = 1.54KΩ       | 19   | 20     | 21       | mA                                               |

| SINK x 10mA                                                          | SINK 10                  | VDD = 5V, SINK <sub>X</sub> = 3V, R <sub>SET</sub> = 3.09KΩ       | 9    | 10     | 11       | 1                                                |

| SINK x 5mA                                                           | SINK <sub>05</sub>       | $VDD = 5V$ , $SINK_X = 3V$ , $R_{SET} = 6.19KΩ$                   | 4    | 5      | 6        | mA<br>mA                                         |

| SINK x Current Matching <sup>2</sup>                                 | SINK X_MATCH             | VDD = 5V, SINK <sub>X</sub> = 1V to 5V; R <sub>SET</sub> = 1.54KΩ | 7    | ±1     | ±2.5     | %                                                |

| I <sub>SET</sub> to SINK <sub>X</sub> Current Ratio                  | SINK X RATIO             | VDD = 5V, SINK <sub>X</sub> /I <sub>SET</sub>                     |      | 24.5   | 12.0     | <del>                                     </del> |

| Output Current I <sub>SET</sub> = 0µA                                | SINK <sub>SET0</sub>     | I <sub>SET</sub> = 0μA                                            |      | 10     | 100      | μA <sub>D</sub>                                  |

| Output Current DIG_DIM ≤ 0.8V                                        | SINK <sub>DIG_DIM0</sub> | $R_{SET} = 1.02K\Omega$ ; DIG_DIM $\leq 0.8V$                     |      | 10     | 100      | μA <sub>D</sub>                                  |

| Dropout Voltage <sup>3</sup>                                         | V <sub>DROPOUT</sub>     | $SINK_X = 10mA$                                                   |      | 200    | 800      | mV                                               |

| Dropout Voltage <sup>3</sup>                                         | V <sub>DROPOUT</sub>     | SINK x = 30mA                                                     |      | 600    | 1000     | mV                                               |

| Maximum Output Current, I <sub>SET</sub> Shorted To Gnd. Each Output | SINK ISETSC              | $V_{ISET}$ = Zero Volts; VDD=5V; SINK <sub>X</sub> = 5V           |      | 50     |          | mA <sub>D</sub>                                  |

| Output Off State Current                                             | SINK X OFF               | ENA $\leq$ 0.4V, $V_{OUT} = 40V$                                  |      | 1      | 3        | μA <sub>D</sub>                                  |

| DIG_DIM INPUT                                                        |                          |                                                                   |      |        |          |                                                  |

| DIG_DIM Logic Threshold                                              | $V_{TH\_DD}$             |                                                                   | 0.8  | 1.6    | 2.4      | V                                                |

| Input Current, high state                                            | I <sub>IH DIG_DIM</sub>  | $V_{DIG\_DINM} = V_{DD}$                                          |      | 50     |          | μA                                               |

| Input Current, low state                                             | I <sub>IL DIG_DIM</sub>  | $V_{DIG\_DIM} = 0V$                                               |      | 0.1    |          | μA                                               |

| DIG_DIM to SINK x Pulse Response                                     | T <sub>D(ON)</sub>       | C <sub>SLOPE</sub> ≤ 20pF                                         |      | 340    |          | nS                                               |

| DIG_DIM to SINK x Pulse Response                                     | $T_{D(OFF)}$             | C <sub>SLOPE</sub> ≤ 20pF                                         |      | 230    |          | nS                                               |

| Minimum SINK x Pulse Width                                           | SINK X PWMMIN            | $C_{SLOPE} \le 20pF, DIG_DIM \le 5uS$                             |      | 5      |          | μS                                               |

| CURRENT ON / OFF SLOPE                                               |                          |                                                                   |      |        |          |                                                  |

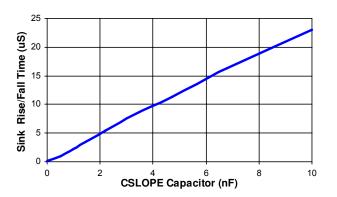

| Current On rise time                                                 | T <sub>RISE</sub>        | C <sub>SLOPE</sub> = 10 nF                                        | 15   | 22     | 29       | μSe                                              |

| Current On fall time                                                 | $T_{FALL}$               | C <sub>SLOPE</sub> = 10 nF                                        | 15   | 24     | 29       | μSe                                              |

| Current on / off delay time                                          | T <sub>delay</sub>       | $C_{SLOPE}$ = 10 nF, $T_A$ = 25°C                                 |      | 50     |          | μSe                                              |

| RSET PIN                                                             |                          |                                                                   |      |        |          |                                                  |

| Voltage at Pin R <sub>SET</sub>                                      | $V_{RSET}$               | R <sub>SET+</sub> = 1.50K to I <sub>SET-</sub>                    | 1.24 | 1.26   | 1.28     | V                                                |

| Pin R <sub>SET</sub> Max Source Current                              | I <sub>MAX RSET</sub>    |                                                                   |      | 4.5    |          | mA                                               |

<sup>&</sup>lt;sup>1</sup> At enable voltages greater than 0.4V but less than 0.8V the outputs will remain off but the sleep current may be greater than 1µA.

<sup>&</sup>lt;sup>2</sup> SINK <sub>X</sub> current matching is greatest percentage delta between output currents with respect to the mean, with V<sub>SINK X</sub> both at 1V and 5V and  $R_{SET} = 1.54K\Omega$ .

<sup>&</sup>lt;sup>3</sup> Dropout is defined as the SINK<sub>X</sub> to GND voltage at which the output current sink drops 10% from the nominal value.

#### **PRODUCTION DATA SHEET**

### THEORY OF OPERATION / APPLICATION NOTE

#### FUNCTIONAL DESCRIPTION

The LX1991 is designed to drive LED's used in display illumination and signaling applications such as cellular telephones, PDA's automotive dashboard lighting, panel illumination etc. With a single 5V supply, the six independently regulated constant current outputs can drive 6 white LED's ( $V_F < 4.0V$ ), or 12 green or amber LED's ( $V_F < 2.0V$  each) arranged as 6 parallel x 2 in series. With a separate high voltage LED supply (up to 40V) a large matrix of LED's (>100) can be driven.

The LX1991 features resistor settable output current. Connecting a resistor between  $I_{\rm SET+}$  and  $I_{\rm SET-}$  pins generates a current that is mirrored into each of the outputs with a gain ratio of about 24. This ratio remains linear for output currents from 3 to 30mA, at output current less than 3mA the ratio increases somewhat. Output current can be varied in an analog fashion by varying  $R_{\rm SET}$  resistor, typically this resistor shall be chosen in the range of 1K to 40K.

Duty cycle dimming with a fixed current amplitude is accomplished by driving the DIG\_DIM input. The switching frequency can exceed 100 KHz, making it practical to use a PWM output channel from popular micro controllers. The upper limit on frequency correlates to the minimum DIG\_DIM sink pulse width which is typically about  $5\mu S$ .

To use the LX1991 at the maximum usable frequency, or minimum pulse width the CSLOPE pin must be open. The CSLOPE pin allows precise control of the sink current rise and fall time. As the value of the CSLOPE capacitor is increased the slope of the rise and fall time will change correspondingly along with some delay to output. Special control circuitry maintains symmetrical rise and fall times, preserving the LX1991's ability to provide accurate output current response to very narrow input pulses on the DIG\_DIM pin.

The ENABLE input is TTL compatible with a turn on threshold of about 1.6V with about 150mV of hysteresis. Below 0.8V the chip is disabled and the sink outputs are off. However ENABLE must be driven below 0.4 volts to insure the minimum sleep current from  $V_{\rm DD}$  and output off current.

All inputs and outputs are ESD and short circuit protected making the LX1991 an exceptionally robust component. The device also includes thermal shutdown however it is not recommended to short the  $I_{\rm SET+}$  and  $I_{\rm SET-}$  inputs together while shorting the outputs to 40V as the power dissipation under these conditions is the greatest.

#### APPLICATION NOTES

POWER CONSIDERATIONS

Each output has an independent current sink, however each must be held above about 600-800mV (typically) to perform properly and maintain the specified current regulation accuracy. The device is designed however to allow one or more of the outputs to be unused (open) without affecting the other channels Or conversely if more than 30mA is needed the outputs can be combined for higher total currents

Package power dissipation can be calculated from the following equation:

$$P_{D} = (n \times I_{OUT}) \times (V_{LOAD} - V_{LED})$$

$\begin{array}{lll} n & = & \text{Number of outputs used} \\ I_{OUT} & = & \text{Current from each output} \\ V_{LOAD} & = & \text{Output Supply Voltage} \\ V_{LED} & = & \text{Minimum LED forward voltage} \\ P_{D} & = & \text{Power Dissipated in mW} \end{array}$

Care should be exercised not to exceed the power dissipation of the package or the maximum junction temperature of the die. Proper mounting of the package with thermal vias (see PCB Land Guidelines and Thermal Pad Design section) enhances power dissipation capability. As an example to drive 24 white LED's, 4 per channel from a 18V  $V_{\rm LED}$  supply @ 25mA per LED string, we will assume the minimum LED forward voltage to be 3.5V with an maximum operating ambient of 50°C.

$$P_D = (6 \times 25 \text{mA}) \times (18 \text{V} - (4 \times 3.5 \text{V})) = 15 \times 4 \text{V} = 0.6 \text{W}$$

This represents a 21.6°C temperature rise (36°C/W \*0.6W) for a die temperature of about 72°C, ignoring device drain current power dissipation that only represents about a 3°C rise worst case. This is well under the die junction temperature maximum rating of 150°C, and within the 85°C electrical specifications.

#### DIMMING

Dimming can be accomplished both with current amplitude control (changing the  $R_{\rm SET}$  resistor value) with a PWM signal (toggling the DIG\_DIM input) or both. Current between the  $I_{\rm SET+}$  and  $I_{\rm SET-}$  pins may be varied for current amplitude dimming. If a mechanical input is needed, a rheostat in series with a resistor connected from  $I_{\rm SET+}$  to  $I_{\rm SET-}$  can be used.:

Page 6

## Six Output Programmable LED Current Sink

**PRODUCTION DATA SHEET**

### **APPLICATION NOTE - CONTINUED**

The range of the  $R_{SET}$  resistor can vary between 1K and 40K Ohms. The resistor in series with the rheostat will set the maximum current and should be a least  $1K\Omega$  in value. If a fixed sink current is desired its easy to find the RSET resistor value. As an example, suppose the desired output current is 25mA per sink channel. The  $R_{SET}$  resistor can be calculated as follows:

$R_{SET(K\Omega)} = Current \ ratio / Output \ current(mA) \times VR_{SET}$

$$R_{SET(K\Omega)} = 24.5 / 25 \times 1.26 = 1.23 K\Omega$$

Once the maximum sink current is set the rheostat will increase the RSET value thus dimming the LED by reducing the sinking current.

Wide range dimming can be accomplished by using the DIG\_DIM input pin to pulse the output sink current. The DIG\_DIM pin may be driven with a TTL compatible logic PWM signal to dim the LED's. The recommended PWM frequency for dimming is between 100 Hz and 100 KHz. Below 100 Hz flicker may be observed. Above 100 KHz duty cycle accuracy and minimum pulse width is reduced due to delay times and the current slew rate. To obtain the maximum dim range and still make use of the slope control function ( see CSLOPE pin below) it is advisable to use a lower frequency on the DIG\_DIM input.

If PWM dimming is used, use of separate power and ground lines directly from the power source point will help to prevent noise generated from the LED current transients from entering video or audio subsystems on the same supply rails. Additional power supply filtering may be needed in PWM dimming applications. Care should be exercised in the PCB layout to prevent coupling from the SINK outputs to the DIG DIM pin.

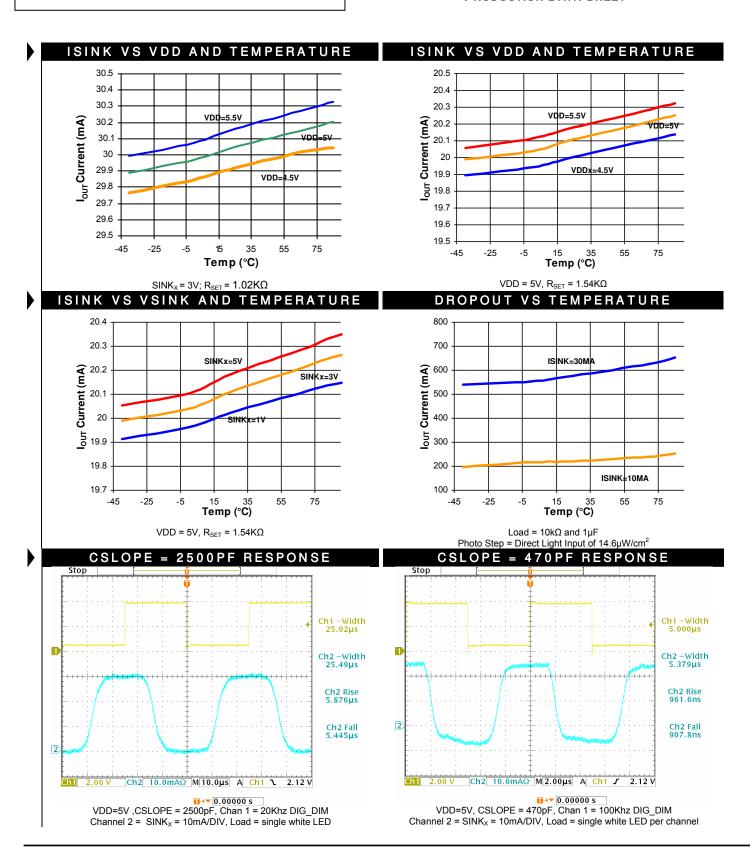

## CSLOPE PIN

The CSLOPE pin is available to control the rise and fall times of the SINK outputs during pulse dimming. With the CSLOPE pin open a minimum rise and fall time of about 120 to 200nS will be present on the output waveforms along with a delay time (DIG\_DIM to SINKx) of about 200nS. As the CSLOPE capacitor is increases in value so will the corresponding rise and fall times and delay to output. The calculation for the CSLOPE value is approximately  $450\mu A$  \*  $T_R$  or  $T_F$  in microseconds, C in picofarads. So for a 5uS rise and fall time 0.00045 \* 5 = 2250pF or about a typical .0022uF capacitor value. For typical slope rise and fall times see the follow chart

## **Typical CSLOPE vs Slope Times**

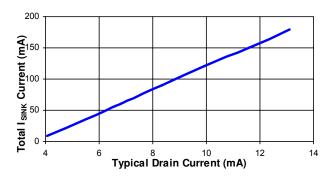

#### DRAIN CURRENT

The chart below illustrates the correlation between the IC's drain current and the total sink output current. The drain current will also increase slightly if one or more the SINKx pins are left floating or when the SINK outputs are near dropout, however in both of these circumstances the increased drain current will be small and controlled and is a feature of the design.

## LX1991 Typical Drain Current Vs Sink Current

#### **PRODUCTION DATA SHEET**

#### **PRODUCTION DATA SHEET**

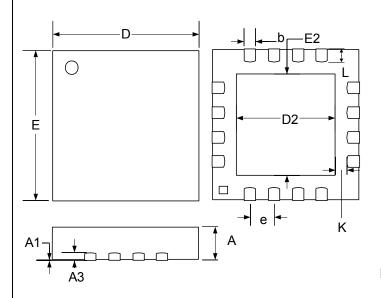

## MECHANICAL DRAWING

# LQ 16-Pin MLPQ Plastic (4x4mm EP)

| Dim   |          | ETERS | INCHES    |       |  |

|-------|----------|-------|-----------|-------|--|

| Dilli | MIN      | MAX   | MIN       | MAX   |  |

| Α     | 0.80     | 1.00  | 0.031     | 0.039 |  |

| A1    | 0        | 0.05  | 0         | 0.002 |  |

| A3    | 0.18     | 0.30  | 0.007     | 0.012 |  |

| b     | 0.23     | 0.38  | 0.009     | 0.015 |  |

| D     | 4.00 BSC |       | 0.157 BSC |       |  |

| Е     | 4.00 BSC |       | 0.157 BSC |       |  |

| е     | 0.65 BSC |       | 0.026 BSC |       |  |

| D2    | 2.55     | 2.80  | 0.100     | 0.110 |  |

| E2    | 2.55     | 2.80  | 0.100     | 0.110 |  |

| K     | 0.20     | -     | 0.008     |       |  |

| L     | 0.30     | 0.50  | 0.012     | 0.020 |  |

### Note:

Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm(.006") on any side. Lead dimension shall not include solder coverage.

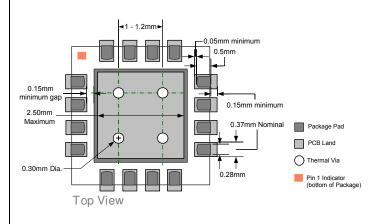

## 16-Pin PCB Land Guidelines and Thermal Pad Design

The typical land pattern shown includes thermal vias in the exposed die attach pad for improved thermal performance. Vias should be about 0.3mm in diameter, with the via plated to about 1.0 ounce copper. Vias should be plugged to prevent voids being formed due to capillary action. This can be avoided by tenting the via during the solder mask process. In addition, to reduce solder paste volume on the thermal land, it is recommended that an array of small apertures in the solder mask be used instead of one large aperture, with the goal of 50 – 80% solder paste coverage. Please review IPC / EIA J-Std-001C Section 9.2.6.4 "Bottom Only Termination" for solder joint requirements.

LX1991

## **Six Output Programmable LED Current Sink**

PRODUCTION DATA SHEET

NOTES

PRODUCTION DATA – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.