ISL6553

NOT RECOMMENDED FOR NEW DESIGNS NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

**DATASHEET**

FN4931 Rev 1.00 August 2004

Microprocessor CORE Voltage Regulator Multi-Phase Buck PWM Controller

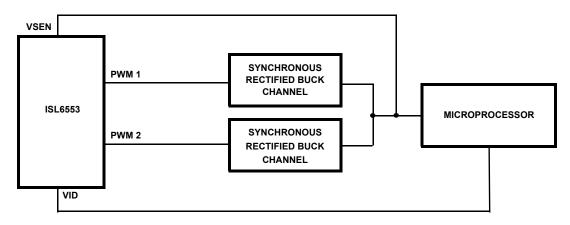

The ISL6553 multi-phase PWM control IC together with its companion gate drivers, the HIP6601, HIP6602 or HIP6603 provides a precision voltage regulation system for advanced microprocessors. Multi-phase power conversion is a marked departure from earlier single phase converter configurations previously employed to satisfy the ever increasing current demands of modern microprocessors. Multi-phase converters, by distributing the power and load current results in smaller and lower cost transistors with fewer input and output capacitors. These reductions accrue from the higher effective conversion frequency with higher frequency ripple current due to the phase interleaving process of this topology. For example, a two phase converter operating at 350kHz will have a ripple frequency of 700kHz. Moreover, greater converter bandwidth of this design results in faster response to load transients.

Outstanding features of this controller IC include programmable VID codes from the microprocessor that range from 1.05V to 1.825V with a system accuracy of  $\pm 1\%$ . Pull up currents on these VID pins eliminates the need for external pull up resistors. In addition "droop" compensation, used to reduce the overshoot or undershoot of the CORE voltage, is easily programmed with a single resistor.

Another feature of this controller IC is the PGOOD monitor circuit which is held low until the CORE voltage increases, during its Soft-Start sequence, to within 10% of the programmed voltage. Over-voltage, 15% above programmed CORE voltage, results in the converter shutting down and turning the lower MOSFETs ON to clamp and protect the microprocessor. Under voltage is also detected and results in PGOOD low if the CORE voltage falls 10% below the programmed level. Over-current protection reduces the regulator RMS output current to 41% of the programmed over-current trip value. These features provide monitoring and protection for the microprocessor and power system.

#### **Features**

- Multi-Phase Power Conversion

- · Precision Channel Current Sharing

- Loss Less Current Sampling Uses rDS(ON)

- · Precision CORE Voltage Regulation

- ±1% System Accuracy Over Temperature

- Microprocessor Voltage Identification Input

- 5-Bit VID Input

- 1.05V to 1.825V in 25mV Steps

- Programmable "Droop" Voltage

- · Fast Transient Recovery Time

- Over Current Protection

- · Pb-free available

#### Related Literature

Technical Brief TB363 "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

# Ordering Information

| PART NUMBER       | TEMP. (°C)     | PACKAGE                 | PKG. DWG.<br># |

|-------------------|----------------|-------------------------|----------------|

| ISL6553CB         | 0 to 70        | 16 Ld SOIC              | M16.15         |

| ISL6553CBZ (Note) | 0 to 70        | 16 Ld SOIC<br>(Pb-free) | M16.15         |

| ISL6553EVAL1      | Evaluation Pla | atform                  |                |

<sup>\*</sup>Add "-T" suffix to part number for tape and reel packaging.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

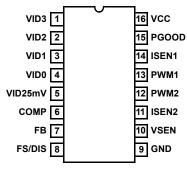

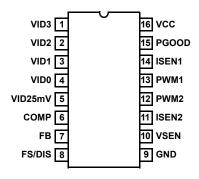

## **Pinout**

ISL6553 (SOIC) TOP VIEW

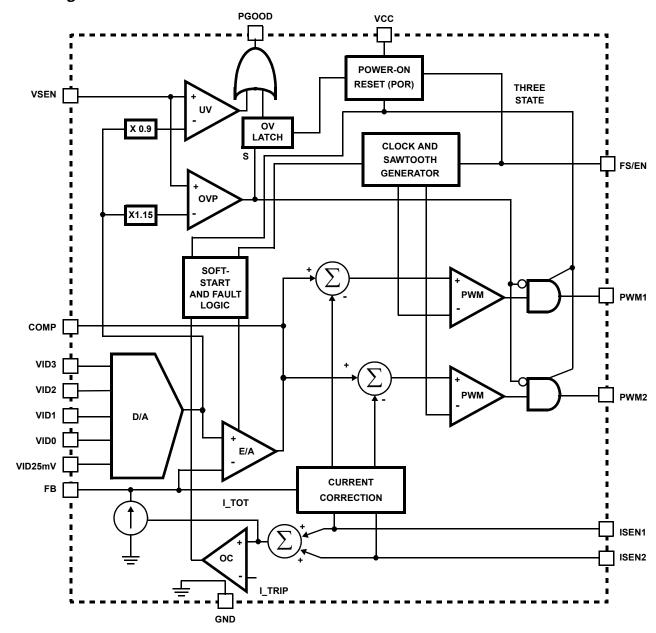

# **Block Diagram**

# Simplified Power System Diagram

## Functional Pin Description

# VID3 (Pin 1), VID2 (Pin 2), VID1 (Pin 3), VID0 (Pin 4) and VID25mV (Pin 5)

Voltage Identification inputs from microprocessor. These pins respond to TTL and 3.3V logic signals. The ISL6553 decodes VID bits to establish the output voltage. See Table 1.

#### COMP (Pin 6)

Output of the internal error amplifier. Connect this pin to the external feedback and compensation network.

#### FB (Pin 7)

Inverting input of the internal error amplifier.

## FS/DIS (Pin 8)

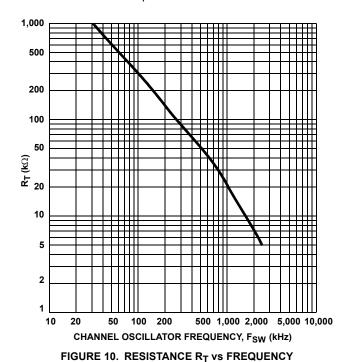

Channel frequency,  $F_{SW}$ , select and disable. A resistor from this pin to ground sets the switching frequency of the converter. Pulling this pin to ground disables the converter and three states the PWM outputs. See Figure 10.

#### GND (Pin 9)

Bias and reference ground. All signals are referenced to this pin.

#### VSEN (Pin 10)

Power good monitor input. Connect to the microprocessor-CORE voltage.

## ISEN2 (Pin 11) and ISEN1 (Pin 14)

Current sense inputs from the individual converter channel's phase nodes.

## PWM2 (Pin 12) and PWM1 (Pin 13)

PWM outputs for each driven channel in use. Connect these pins to the PWM input of a HIP6601/2/3 driver.

#### PGOOD (Pin 15)

Power good. This pin provides a logic-high signal when the microprocessor CORE voltage (VSEN pin) is within specified limits and Soft-Start has timed out.

## VCC (Pin 16)

Bias supply. Connect this pin to a 5V supply.

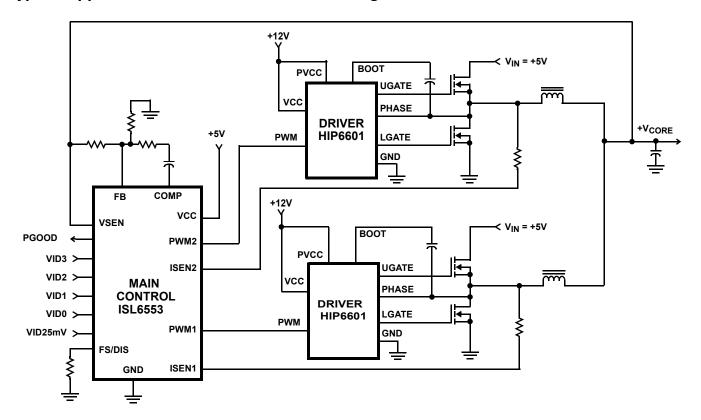

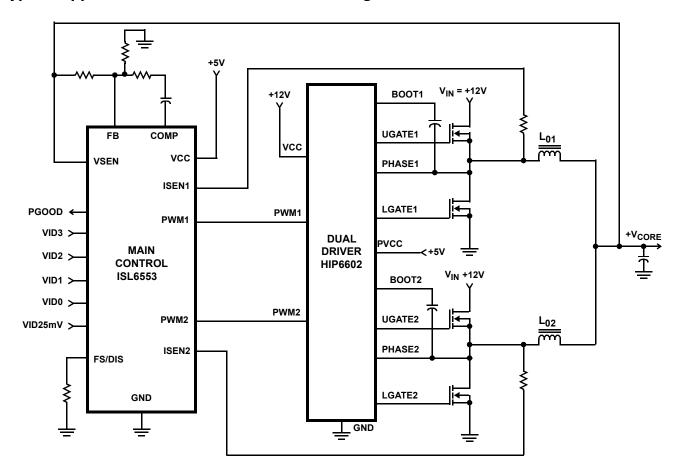

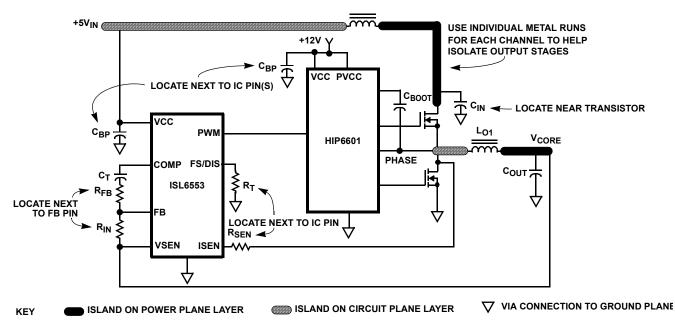

# Typical Application - Two Phase Converter Using HIP6601 Gate Drivers

# Typical Application - Two Phase Converter Using an HIP6602 Gate Driver

## **Absolute Maximum Ratings**

| Supply Voltage, VCC           | +7V                                  |

|-------------------------------|--------------------------------------|

| Input, Output, or I/O Voltage | GND -0.3V to V <sub>VCC</sub> + 0.3V |

| ESD Classification            | Class TBD                            |

## **Recommended Operating Conditions**

| Supply Voltage      | <br>+5V ±5%     |

|---------------------|-----------------|

| Ambient Temperature | <br>0°C to 70°C |

## **Thermal Information**

| Thermal Resistance (Typical, Note 1)                             | $\theta_{JA}$ (oC/W)                 |

|------------------------------------------------------------------|--------------------------------------|

| SOIC Package                                                     | 106                                  |

| Maximum Junction Temperature                                     |                                      |

| Maximum Storage Temperature Range65                              | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s) (SOIC - Lead Tips Only) | 300°C                                |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

**Electrical Specifications** Operating Conditions: VCC = 5V, T<sub>A</sub> = 0°C to 70°C, Unless Otherwise Specified

| PARAMETER                            | TEST CONDITIONS                                                            | MIN  | TYP  | MAX  | UNITS            |

|--------------------------------------|----------------------------------------------------------------------------|------|------|------|------------------|

| INPUT SUPPLY POWER                   |                                                                            |      | ı    | Į.   | II.              |

| Input Supply Current                 | $R_T = 100k\Omega$ , Active and Disabled Maximum Limit                     | -    | 10   | 15   | mA               |

| POR (Power-On Reset) Threshold       | VCC Rising                                                                 | 4.25 | 4.38 | 4.5  | V                |

|                                      | VCC Falling                                                                | 3.75 | 3.88 | 4.00 | V                |

| REFERENCE AND DAC                    |                                                                            |      |      |      |                  |

| DAC Voltage Accuracy                 |                                                                            | -1   | -    | 1    | %                |

| DAC Pin Input Low Voltage Threshold  |                                                                            | -    | -    | 0.8  | ٧                |

| DAC Pin Input High Voltage Threshold |                                                                            | 2.0  | -    | -    | ٧                |

| VID Pull-Up                          | VIDx = 0V or VIDx = 3V                                                     | 10   | 20   | 40   | μА               |

| OSCILLATOR                           |                                                                            | 1    | I.   |      |                  |

| Frequency, F <sub>SW</sub>           | $R_T = 100 k\Omega, \pm 1\%$                                               | 245  | 275  | 305  | kHz              |

| Adjustment Range                     | See Figure 10                                                              | 0.05 | -    | 1.5  | MHz              |

| Disable Voltage                      | Maximum Voltage at FS/DIS to Disable Controller. I <sub>FS/DIS</sub> = 1mA | -    | -    | 1.0  | ٧                |

| ERROR AMPLIFIER                      |                                                                            | 1    | I.   |      |                  |

| DC Gain                              | R <sub>L</sub> = 10K to GND                                                | -    | 72   | -    | dB               |

| Gain-Bandwidth Product               | C <sub>L</sub> = 100pF, R <sub>L</sub> = 10K to GND                        | -    | 18   | -    | MHz              |

| Slew Rate                            | $C_L$ = 100pF, Load = $\pm 400\mu A$                                       | -    | 5.3  | -    | V/μs             |

| Maximum Output Voltage               | R <sub>L</sub> = 10K to GND, Load = 400μA                                  | 3.6  | 4.1  | -    | V                |

| Minimum Output Voltage               | R <sub>L</sub> = 10K to GND, Load = -400μA                                 | -    | 0.16 | 0.5  | V                |

| ISEN                                 |                                                                            |      |      |      |                  |

| Full Scale Input Current             |                                                                            | -    | 50   | -    | μА               |

| Over-Current Trip Level              |                                                                            | -    | 82.5 | -    | μА               |

| POWER GOOD MONITOR                   |                                                                            | 1    | I.   |      |                  |

| Under-Voltage Threshold              | VSEN Rising                                                                | -    | 0.92 | -    | $V_{DAC}$        |

| Under-Voltage Threshold              | VSEN Falling                                                               | -    | 0.90 | -    | V <sub>DAC</sub> |

| PGOOD Low Output Voltage             | I <sub>PGOOD</sub> = 4mA                                                   | -    | 0.18 | 0.4  | ٧                |

| PROTECTION                           |                                                                            | 1    | l    | I    | 1                |

| Over-Voltage Threshold               | VSEN Rising                                                                | 1.12 | 1.15 | 1.2  | V <sub>DAC</sub> |

| Percent Over-Voltage Hysteresis      | VSEN Falling after Over-Voltage                                            | -    | 2    | -    | %                |

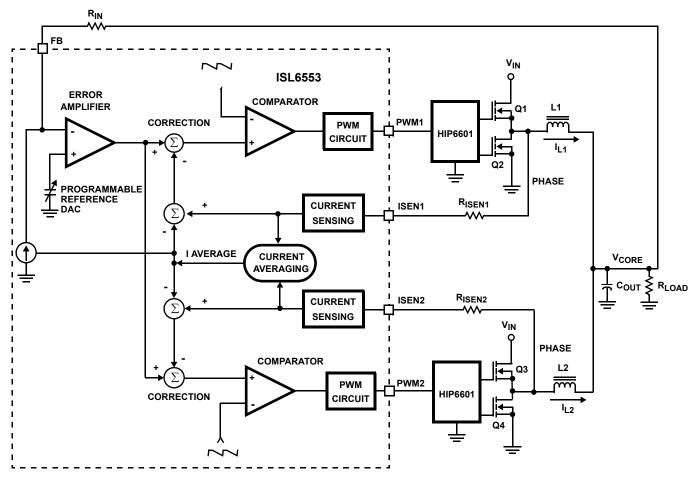

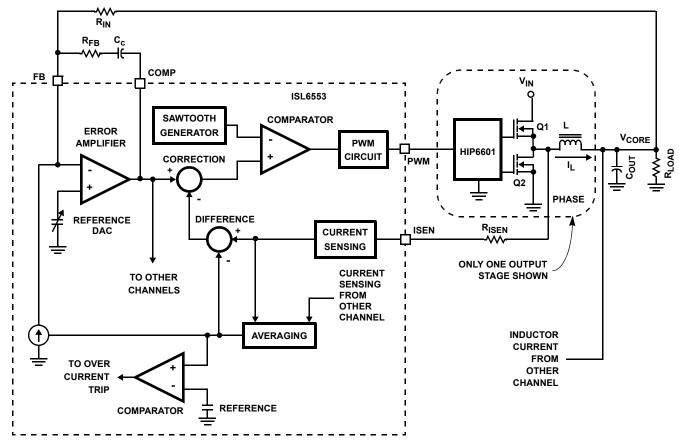

FIGURE 1. SIMPLIFIED BLOCK DIAGRAM OF THE ISL6553 VOLTAGE AND CURRENT CONTROL LOOPS FOR A TWO POWER CHANNEL REGULATOR

## Operation

Figure 1 shows a simplified diagram of the voltage regulation and current control loops. Both voltage and current feedback are used to precisely regulate voltage and tightly control output currents,  $I_{L\,1}$  and  $I_{L\,2}$ , of the two power channels. The voltage loop comprises the Error Amplifier, Comparators, gate drivers and output MOSFETs. The Error Amplifier is essentially connected as a voltage follower that has as an input, the Programmable Reference DAC and an output that is the CORE voltage.

## Voltage Loop

Feedback from the CORE voltage is applied via resistor  $R_{IN}$  to the inverting input of the error amplifier. This signal can drive the error amplifier output either high or low, depending upon the CORE voltage. Low CORE voltage makes the amplifier output move towards a higher output voltage level. Amplifier output voltage is applied to the positive inputs of the comparators via the correction summing networks. Out-of-phase sawtooth signals are applied to the two comparators inverting inputs. Increasing error amplifier voltage results in

increased comparator output duty cycle. This increased duty cycle signal is passed through the PWM circuit with no phase reversal and on to the HIP6601, again with no phase reversal for gate drive to the upper MOSFETs, Q1 and Q3. Increased duty cycle or ON time for the MOSFET transistors results in increased output voltage to compensate for the low output voltage sensed.

#### Current Loop

The current control loop works in a similar fashion to the voltage control loop, but with current control information applied individually to each channel's comparator. The information used for this control is the voltage that is developed across r<sub>DS(ON)</sub> of each lower MOSFET, Q2 and Q4, when they are conducting. A single resistor converts and scales the voltage across the MOSFETs to a current that is applied to the current sensing circuit within the ISL6553. Output from these sensing circuits is applied to the current averaging circuit. Each PWM channel receives the difference current signal from the summing circuit that compares the average sensed current to the individual channel current. When a power channel's current is greater than the average current, the signal applied via the

summing correction circuit to the comparator, reduces the output pulse width of the comparator to compensate for the detected "above average" current in that channel.

#### **Droop Compensation**

In addition to control of each power channel's output current, the average channel current is also used to provide CORE voltage "droop" compensation. Average full channel current is defined as  $50\mu A$ . By selecting an input resistor,  $R_{IN}$ , the amount of voltage droop required at full load current can be programmed. The average current driven into the FB pin results in a voltage increase across resistor  $R_{IN}$  that is in the direction to make the error amplifier "see" a higher voltage at the inverting input, resulting in the error amplifier adjusting the output voltage lower. The voltage developed across  $R_{IN}$  is equal to the "droop" voltage. See the "Current Sensing and Balancing" section for more details.

## Applications and Converter Start-Up

Each PWM power channel's current is regulated. This enables the PWM channels to accurately share the load current for enhanced reliability. The HIP6601, HIP6602 or HIP6603 MOSFET driver interfaces with the ISL6553. For more information, see the HIP6601, HIP6602 or HIP6603 data sheets [1] [2].

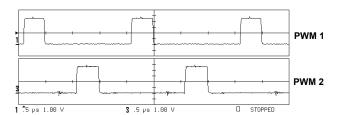

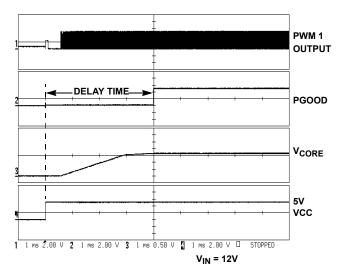

The ISL6553 controls the two PWM power channels 180 degrees out of phase. Figure 2 shows the out of phase relationship between the two PWM channels.

FIGURE 2. TWO PHASE PWM OUTPUT AT 500kHz

Power supply ripple frequency is determined by the channel frequency,  $F_{SW}$ , multiplied by the number of active channels. For example, if the channel frequency is set to 250kHz, the ripple frequency is 500kHz.

The IC monitors and precisely regulates the CORE voltage of a microprocessor. After initial start-up, the controller also provides protection for the load and the power supply. The following section discusses these features.

#### Initialization

The ISL6553 usually operates from an ATX power supply. Many functions are initiated by the rising supply voltage to the VCC pin of the ISL6553. Oscillator, sawtooth generator, soft-start and other functions are initialized during this interval. These circuits are controlled by POR, Power-On Reset. During this interval, the PWM outputs are driven to a three state

condition that makes these outputs essentially open. This state results in no gate drive to the output MOSFETs.

Once the VCC voltage reaches 4.375V ( $\pm 125$ mV), a voltage level to insure proper internal function, the PWM outputs are enabled and the soft-start sequence is initiated. If for any reason, the VCC voltage drops below 3.875V ( $\pm 125$ mV). The POR circuit shuts the converter down and again three states the PWM outputs.

#### Soft-Start

After the POR function is completed with VCC reaching 4.375V, the soft-start sequence is initiated. Soft-Start, by its slow rise in CORE voltage from zero, avoids an over-current condition by slowly charging the discharged output capacitors. This voltage rise is initiated by an internal DAC that slowly raises the reference voltage to the error amplifier input. The voltage rise is controlled by the oscillator frequency and the DAC within the ISL6553, therefore, the output voltage is effectively regulated as it rises to the final programmed CORE voltage value.

For the first 32 PWM switching cycles, the DAC output remains inhibited and the PWM outputs remain three stated. From the 33rd cycle and for another, approximately 150 cycles the PWM output remains low, clamping the lower output MOSFETs to ground, see Figure 3. The time variability is due to the error amplifier, sawtooth generator and comparators moving into their active regions. After this short interval, the PWM outputs are enabled and increment the PWM pulse width from zero duty cycle to operational pulse width, thus allowing the output voltage to slowly reach the CORE voltage. The CORE voltage will reach its programmed value before the 2048 cycles, but the PGOOD output will not be initiated until the 2048th PWM switching cycle.

The Soft-Start time or delay time, DT =  $2048/F_{SW}$ . For an oscillator frequency,  $F_{SW}$ , of 200kHz, the first 32 cycles or  $160\mu s$ , the PWM outputs are held in a three state level as explained above. After this period and a short interval described above, the PWM outputs are initiated and the voltage rises in 10.08ms, for a total delay time DT of 10.24ms.

Figure 3 shows the start-up sequence as initiated by a fast rising 5V supply, VCC, applied to the ISL6553. Note the short rise to the three state level in PWM 1 output during first 32 PWM cycles.

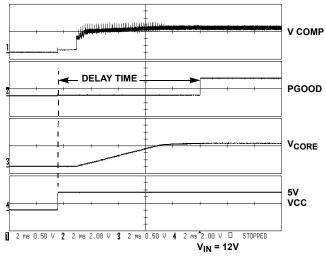

Figure 4 shows the waveforms when the regulator is operating at 200kHz. Note that the Soft-Start duration is a function of the channel frequency as explained previously. Also note the pulses on the COMP terminal. These pulses are the current correction signal feeding into the comparator input (see the **Block Diagram**).

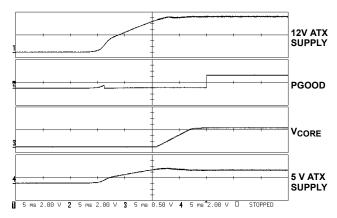

Figure 5 shows the regulator operating from an ATX supply. In this figure, note the slight rise in PGOOD as the 5V supply rises. The PGOOD output stage is made up of NMOS and PMOS transistors. On the rising VCC, the PMOS device

becomes active slightly before the NMOS transistor pulls "down", generating the slight rise in the PGOOD voltage.

Note that Figure 5 shows the 12V gate driver voltage available before the 5V supply to the ISL6553 has reached its threshold level. If conditions were reversed and the 5V supply was to rise first, the start-up sequence would be different. In this case the ISL6553 will sense an over-current condition due to charging the output capacitors. The supply will then restart and go through the normal Soft-Start cycle.

FIGURE 3. START-UP OF 4 PHASE SYSTEM OPERATING AT 500kHz

FIGURE 4. START-UP OF 4 PHASE SYSTEM OPERATING AT 200kHz

V<sub>IN</sub> = 5V, CORE LOAD CURRENT = 31A FREQUENCY 200kHz ATX SUPPLY ACTIVATED BY ATX "PS-ON PIN"

FIGURE 5. SUPPLY POWERED BY ATX SUPPLY

## **Fault Protection**

The ISL6553 protects the microprocessor and the entire power system from damaging stress levels. Within the ISL6553 both over-voltage and over-current circuits are incorporated to protect the load and regulator.

#### Over-Voltage

The VSEN pin is connected to the microprocessor CORE voltage. A CORE over-voltage condition is detected when the VSEN pin goes more than 15% above the programmed VID level.

The over-voltage condition is latched, disabling normal PWM operation, and causing PGOOD to go low. The latch can only be reset by lowering and returning VCC high to initiate a POR and Soft-Start sequence.

During a latched over-voltage, the PWM outputs will be driven either low or three state, depending upon the VSEN input. PWM outputs are driven low when the VSEN pin detects that the CORE voltage is 15% above the programmed VID level. This condition drives the PWM outputs low, resulting in the lower or synchronous rectifier MOSFETs to conduct and shunt the CORE voltage to ground to protect the load.

If after this event, the CORE voltage falls below the overvoltage limit (plus some hysteresis), the PWM outputs will three state. The HIP6601 family drivers pass the three state information along, and shuts off both upper and lower MOSFETs. This prevents "dumping" of the output capacitors back through the lower MOSFETs, avoiding a possibly destructive ringing of the capacitors and output inductors. If the conditions that caused the over-voltage still persist, the PWM outputs will be cycled between three state and VCORE clamped to ground, as a hysteretic shunt regulator.

## Under-Voltage

The VSEN pin also detects when the CORE voltage falls more than 10% below the VID programmed level. This causes PGOOD to go low, but has no other effect on operation and is not latched. There is also hysteresis in this detection point.

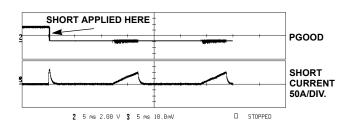

#### Over-Current

In the event of an over-current condition, the over-current protection circuit reduces the RMS current delivered to 41% of the current limit. When an over-current condition is detected, the controller forces all PWM outputs into a three state mode. This condition results in the gate driver removing drive to the output stages. The ISL6553 goes into a wait delay timing cycle that is equal to the Soft-Start ramp time. PGOOD also goes "low" during this time due to VSEN going below its threshold voltage. To lower the average output dissipation, the Soft-Start initial wait time is increased from 32 to 2048 cycles, then the Soft-Start ramp is initiated. At a PWM frequency of 200kHz, for instance, an over-current detection would cause a dead time of 10.24ms, then a ramp of 10.08ms.

At the end of the delay, PWM outputs are restarted and the Soft-Start ramp is initiated. If a short is present at that time, the cycle is repeated. This is the hiccup mode.

Figure 6 shows the supply shorted under operation and the hiccup operating mode described above. Note that due to the high short circuit current, over-current is detected before completion of the start-up sequence so the delay is not quite as long as the normal Soft-Start cycle.

HICCUP MODE. SUPPLY POWERED BY ATX SUPPLY CORE LOAD CURRENT = 31A, 5V LOAD = 5A SUPPLY FREQUENCY = 200kHz, V IN = 12V ATX SUPPLY ACTIVATED BY ATX "PS-ON PIN"

FIGURE 6. SHORT APPLIED TO SUPPLY AFTER POWER-UP

# CORE Voltage Programming

The voltage identification pins (VID25mV, VID0, VID1, VID2 and VID3) set the CORE output voltage. Each VID pin is pulled to VCC by an internal  $20\mu A$  current source and accepts open-collector/open-drain/open-switch-to-ground or standard low-voltage TTL or CMOS signals.

Table 1 shows the nominal DAC voltage as a function of the VID codes. The power supply system is  $\pm 1\%$  accurate over the operating temperature and voltage range.

**TABLE 1. VOLTAGE IDENTIFICATION CODES**

| VOLTAGE IDENTIFICATION CODE AT PROCESSOR PINS |      |      |      |      | VCC <sub>(CORE)</sub> |

|-----------------------------------------------|------|------|------|------|-----------------------|

| VID25mV                                       | VID3 | VID2 | VID1 | VID0 | (VDC)                 |

| 0                                             | 0    | 1    | 0    | 0    | 1.05                  |

| 1                                             | 0    | 1    | 0    | 0    | 1.075                 |

| 0                                             | 0    | 0    | 1    | 1    | 1.10                  |

| 1                                             | 0    | 0    | 1    | 1    | 1.125                 |

| 0                                             | 0    | 0    | 1    | 0    | 1.15                  |

| 1                                             | 0    | 0    | 1    | 0    | 1.175                 |

| 0                                             | 0    | 0    | 0    | 1    | 1.20                  |

| 1                                             | 0    | 0    | 0    | 1    | 1.225                 |

| 0                                             | 0    | 0    | 0    | 0    | 1.25                  |

| 1                                             | 0    | 0    | 0    | 0    | 1.275                 |

| 0                                             | 1    | 1    | 1    | 1    | 1.30                  |

| 1                                             | 1    | 1    | 1    | 1    | 1.325                 |

| 0                                             | 1    | 1    | 1    | 0    | 1.35                  |

| 1                                             | 1    | 1    | 1    | 0    | 1.375                 |

| 0                                             | 1    | 1    | 0    | 1    | 1.40                  |

| 1                                             | 1    | 1    | 0    | 1    | 1.425                 |

| 0                                             | 1    | 1    | 0    | 0    | 1.45                  |

| 1                                             | 1    | 1    | 0    | 0    | 1.475                 |

| 0                                             | 1    | 0    | 1    | 1    | 1.50                  |

| 1                                             | 1    | 0    | 1    | 1    | 1.525                 |

| 0                                             | 1    | 0    | 1    | 0    | 1.55                  |

| 1                                             | 1    | 0    | 1    | 0    | 1.575                 |

| 0                                             | 1    | 0    | 0    | 1    | 1.60                  |

| 1                                             | 1    | 0    | 0    | 1    | 1.625                 |

| 0                                             | 1    | 0    | 0    | 0    | 1.65                  |

| 1                                             | 1    | 0    | 0    | 0    | 1.675                 |

| 0                                             | 0    | 1    | 1    | 1    | 1.70                  |

| 1                                             | 0    | 1    | 1    | 1    | 1.725                 |

| 0                                             | 0    | 1    | 1    | 0    | 1.75                  |

| 1                                             | 0    | 1    | 1    | 0    | 1.775                 |

| 0                                             | 0    | 1    | 0    | 1    | 1.80                  |

| 1                                             | 0    | 1    | 0    | 1    | 1.825                 |

FIGURE 7. SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM SHOWING CURRENT AND VOLTAGE SAMPLING

# Current Sensing and Balancing

#### Overview

The ISL6553 samples the on-state voltage drop across each synchronous rectifier FET, Q2, as an indication of the inductor current in that phase, see Figure 7. Neglecting AC effects (to be discussed later), the voltage drop across Q2 is simply  $r_{DS(ON)}(Q2)$  x inductor current (I<sub>L</sub>). Note that I<sub>L</sub>, the inductor current, is 1/2 of the total current (I<sub>LT</sub>).

The voltage at Q2's drain, the PHASE node, is applied to the  $R_{ISEN}$  resistor to develop the  $I_{ISEN}$  current to the ISL6553 ISEN pin. This pin is held at virtual ground, so the current through  $R_{ISEN}$  is  $I_L \times r_{DS(ON)}(Q2) / R_{ISEN}$ .

The I<sub>ISEN</sub> current provides information to perform the following functions:

- 1. Detection of an over-current condition

- Reduce the regulator output voltage with increasing load current (droop)

- 3. Balance the  $I_L$  currents in the two phases

## Over-Current, Selecting RISEN

The current detected through the R<sub>ISEN</sub> resistor is averaged with the current detected in the other channel. The averaged

current is compared with a trimmed, internally generated current, and used to detect an over-current condition.

The nominal current through the R<sub>ISEN</sub> resistor should be  $50\mu A$  at full output load current, and the nominal trip point for over-current detection is 165% of that value, or  $82.5\mu A$ . Therefore, R<sub>ISEN</sub> = I<sub>L</sub> x r<sub>DS(ON)</sub> (Q2) /  $50\mu A$ .

For a full load of 25A per phase, and an  $r_{DS(ON)}$  (Q2) of  $4m\Omega,$   $R_{ISEN}$  =  $2k\Omega$  .

The over-current trip point would be 165% of 25A, or  $\sim$  41A per phase. The R<sub>ISEN</sub> value can be adjusted to change the over-current trip point, but it is suggested to stay within  $\pm 25\%$  of nominal.

## Droop, Selection of R<sub>IN</sub>

The average of the currents detected through the  $R_{ISEN}$  resistors is also steered to the FB pin. There is no DC return path connected to the FB pin except for  $R_{IN}$ , so the average current creates a voltage drop across  $R_{IN}$ . This drop increases the apparent  $V_{CORE}$  voltage with increasing load current, causing the system to decrease  $V_{CORE}$  to maintain balance at the FB pin. This is the desired "droop" voltage used to maintain  $V_{CORE}$  within limits under transient conditions.

With a high dv/dt load transient, typical of high performance microprocessors, the largest deviations in output voltage occur

at the leading and trailing edges of the load transient. In order to fully utilize the output-voltage tolerance range, the output voltage is positioned in the upper half of the range when the output is unloaded and in the lower half of the range when the controller is under full load. This droop compensation allows larger transient voltage deviations and thus reduces the size and cost of the output filter components.

$R_{IN}$  should be selected to give the desired "droop" voltage at the normal full load current  $50\mu A$  applied through the  $R_{ISEN}$  resistor (or at a different full load current if adjusted as under "Over-current, Selecting  $R_{ISEN}$ " above).

$R_{IN} = V_{DROOP} / 50 \mu A$

For a  $V_{DROOP}$  of 80mV,  $R_{IN} = 1.6k\Omega$

The AC feedback components,  $R_{FB}$  and Cc, are scaled in relation to  $R_{IN}$ .

#### **Current Balancing**

The detected currents are also used to balance the phase currents.

Each phase's current is compared to the average of the two phase currents, and the difference is used to create an offset in that phase's PWM comparator. The offset is in a direction to reduce the imbalance.

The balancing circuit can not make up for a difference in  $r_{DS(ON)}$  between synchronous rectifiers. If a FET has a higher  $r_{DS(ON)}$ , the current through that phase will be reduced.

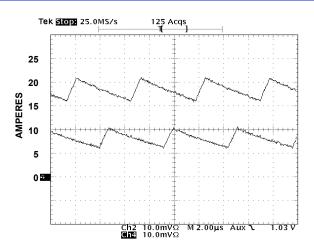

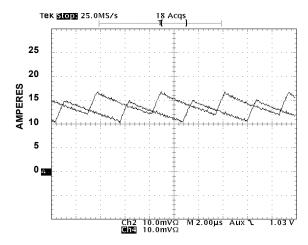

Figures 8 and 9 show the inductor current of a two phase system without and with current balancing.

#### **Inductor Current**

The inductor current in each phase of a multi-phase Buck converter has two components. There is a current equal to the load current divided by the number of phases ( $I_{LT}/n$ ), and a sawtooth current, ( $i_{PK-PK}$ ) resulting from switching. The sawtooth component is dependent on the size of the inductors, the switching frequency of each phase, and the values of the input and output voltage. Ignoring secondary effects, such as series resistance, the peak to peak value of the sawtooth current can be described by:

$i_{PK-PK} = (V_{IN} \times V_{CORE} - V_{CORE}^2) / (L \times F_{SW} \times V_{IN})$

Where:  $V_{CORE} = DC$  value of the output or  $V_{ID}$  voltage

$V_{IN}$  = DC value of the input or supply voltage

L = value of the inductor

F<sub>SW</sub> = switching frequency

Example: For  $V_{CORE} = 1.6V$ ,

$V_{IN} = 12V$ ,

$L = 1.3 \mu H$

$F_{SW} = 250kHz,$

Then  $i_{PK-PK} = 4.3A$

FIGURE 8. TWO CHANNEL multi-phase SYSTEM WITH CURRENT BALANCING DISABLED

FIGURE 9. TWO CHANNEL multi-phase SYSTEM WITH CURRENT BALANCING ENABLED

The inductor, or load current, flows alternately from  $V_{IN}$  through Q1 and from ground through Q2. The ISL6553 samples the on-state voltage drop across each Q2 transistor to indicate the inductor current in that phase. The voltage drop is sampled 1/3 of a switching period, 1/F<sub>SW</sub>, after Q1 is turned OFF and Q2 is turned on. Because of the sawtooth current component, the sampled current is different from the average current per phase. Neglecting secondary effects, the sampled current ( $I_{SAMPLE}$ ) can be related to the load current ( $I_{LT}$ ) by:

$I_{SAMPLE} = I_{LT} / n + (V_{IN}V_{CORE} - 3V_{CORE}^2) / (6L \times F_{SW} \times V_{IN})$

Where: I<sub>LT</sub> = total load current

n = the number of channels

Example: Using the previously given conditions, and For  $I_{LT} = 50A$ ,

n 0

n = 2

Then I<sub>SAMPLE</sub> = 25.49A

As discussed previously, the voltage drop across each Q2 transistor at the point in time when current is sampled is  $r_{DSON}$  (Q2) x  $I_{SAMPLE}$ . The voltage at Q2's drain, the PHASE node, is applied through the  $R_{ISEN}$  resistor to the ISL6553 ISEN pin. This pin is held at virtual ground, so the current into ISEN is:

$I_{SENSE} = I_{SAMPLE} \times r_{DS(ON)} (Q2) / R_{ISEN}$  $R_{ISEN} = I_{SAMPLE} \times r_{DS(ON)} (Q2) / 50\mu A$

Example: From the previous conditions,

where  $I_{LT}$  = 50A,  $I_{SAMPLE}$  = 25.49A,  $r_{DS(ON)}$  (Q2) = 4m $\Omega$

Then:  $R_{ISEN} = 2.04K$  and

$I_{\text{CURRENT TRIP}} = 165\%$ Short circuit  $I_{\text{LT}} = 82.5A$ .

## Channel Frequency Oscillator

The channel oscillator frequency is set by placing a resistor,  $R_T$ , to ground from the FS/DIS pin. Figure 10 is a curve showing the relationship between frequency,  $F_{SW}$ , and resistor  $R_T$ . To avoid pickup by the FS/DIS pin, it is important to place this resistor next to the pin. If this pin is also used to disable the converter, it is also important to locate the pull-down device next to this pin.

## Layout Considerations

MOSFETs switch very fast and efficiently. The speed with which the current transitions from one device to another causes voltage spikes across the interconnecting impedances

and parasitic circuit elements. These voltage spikes can degrade efficiency, radiate noise into the circuit and lead to device over-voltage stress. Careful component layout and printed circuit design minimizes the voltage spikes in the converter. Consider, as an example, the turnoff transition of the upper PWM MOSFET. Prior to turnoff, the upper MOSFET was carrying channel current. During the turnoff, current stops flowing in the upper MOSFET and is picked up by the lower MOSFET. Any inductance in the switched current path generates a large voltage spike during the switching interval. Careful component selection, tight layout of the critical components, and short, wide circuit traces minimize the magnitude of voltage spikes. Contact Intersil for evaluation board drawings of the component placement and printed circuit board.

There are two sets of critical components in a DC-DC converter using a ISL6553 controller and a HIP6601 gate driver. The power components are the most critical because they switch large amounts of energy. Next are small signal components that connect to sensitive nodes or supply critical bypassing current and signal coupling.

The power components should be placed first. Locate the input capacitors close to the power switches. Minimize the length of the connections between the input capacitors,  $C_{IN}$ , and the power switches. Locate the output inductors and output capacitors between the MOSFETs and the load. Locate the gate driver close to the MOSFETs.

The critical small components include the bypass capacitors for VCC and PVCC on the gate driver ICs. Locate the bypass capacitor,  $C_{BP}$ , for the ISL6553 controller close to the device. It is especially important to locate the resistors associated with the input to the amplifiers close to their respective pins, since they represent the input to feedback amplifiers. Resistor  $R_{T}$ , that sets the oscillator frequency should also be located next to the associated pin. It is especially important to place the  $R_{SEN}$  resistors at the respective terminals of the ISL6553.

A multi-layer printed circuit board is recommended. Figure 11 shows the connections of the critical components for one output channel of the converter. Note that capacitors  $C_{IN}$  and  $C_{OUT}$  could each represent numerous physical capacitors. Dedicate one solid layer, usually the middle layer of the PC board, for a ground plane and make all critical component ground connections with vias to this layer. Dedicate another solid layer as a power plane and break this plane into smaller islands of common voltage levels. Keep the metal runs from the PHASE terminal to output inductor short. The power plane should support the input power and output power nodes. Use copper filled polygons on the top and bottom circuit layers for the phase nodes. Use the remaining printed circuit layers for small signal wiring. The wiring traces from the driver IC to the MOSFET gate and source should be sized to carry at least 1A of current.

## Component Selection Guidelines

#### **Output Capacitor Selection**

The output capacitor is selected to meet both the dynamic load requirements and the voltage ripple requirements. The load transient for the microprocessor CORE is characterized by high slew rate (di/dt) current demands. In general, multiple high quality capacitors of different size and dielectric are paralleled to meet the design constraints.

Modern microprocessors produce severe transient load rates. High frequency capacitors supply the initially transient current and slow the load rate-of-change seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (effective series resistance) and voltage rating requirements rather than actual capacitance requirements.

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements.

Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR determines the output ripple voltage and the initial voltage drop following a high slew-rate transient's edge. In most cases, multiple capacitors of small case size perform better than a single large case capacitor.

Bulk capacitor choices include aluminum electrolytic, OS-Con, Tantalum and even ceramic dielectrics. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes. However, the equivalent series inductance (ESL) of these capacitors

increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Unfortunately, ESL is not a specified parameter. Consult the capacitor manufacturer and measure the capacitor's impedance with frequency to select a suitable component.

#### **Output Inductor Selection**

One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Small inductors in a multi-phase converter reduces the response time without significant increases in total ripple current.

The output inductor of each power channel controls the ripple current. The control IC is stable for channel ripple current (peak-to-peak) up to twice the average current. A single channel's ripple current is approximately:

$$\Delta I = \frac{V_{IN} - V_{OUT}}{F_{SW}xL} \times \frac{V_{OUT}}{V_{IN}}$$

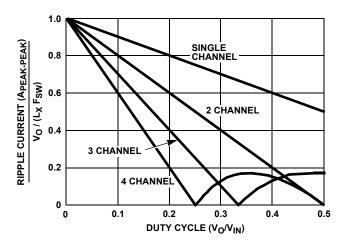

The current from multiple channels tend to cancel each other and reduce the total ripple current. Figure 12 gives the total ripple current as a function of duty cycle, normalized to the parameter  $(\text{Vo})/(\text{L}\cdot\text{F}_{\text{S}})$  at zero duty cycle. To determine the total ripple current from the number of channels and the duty cycle, multiply the y-axis value by  $(\text{Vo})/(\text{LxF}_{\text{SW}})$ .

Small values of output inductance can cause excessive power dissipation. The ISL6553 is designed for stable operation for ripple currents up to twice the load current. However, for this condition, the RMS current is 115% above the value shown in the following MOSFET Selection and Considerations section. With all else fixed, decreasing the inductance could increase the power dissipated in the MOSFETs by 30%.

FIGURE 11. PRINTED CIRCUIT BOARD POWER PLANES AND ISLANDS

FIGURE 12. RIPPLE CURRENT vs DUTY CYCLE

#### Input Capacitor Selection

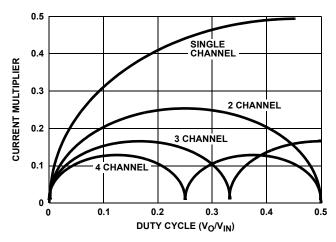

The important parameters for the bulk input capacitors are the voltage rating and the RMS current rating. For reliable operation, select bulk input capacitors with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and a voltage rating of 1.5 times is a conservative guideline. The RMS current required for a multiphase converter can be approximated with the aid of Figure 13.

FIGURE 13. CURRENT MULTIPLIER vs DUTY CYCLE

First determine the operating duty ratio as the ratio of the output voltage divided by the input voltage. Find the Current Multiplier from the curve with the appropriate power channels. Multiply the current multiplier by the full load output current. The resulting value is the RMS current rating required by the input capacitor.

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use ceramic capacitance for the high frequency decoupling and bulk capacitors to supply the RMS current. Small ceramic capacitors should be placed very close to the drain of the upper MOSFET to suppress the voltage induced in the parasitic circuit impedances.

For bulk capacitance, several electrolytic capacitors (Panasonic HFQ series or Nichicon PL series or Sanyo MV-GX or equivalent) may be needed. For surface mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge-current at power-up. The TPS series available from AVX, and the 593D series from Sprague are both surge current tested.

## **MOSFET Selection and Considerations**

In high-current PWM applications, the MOSFET power dissipation, package selection and heatsink are the dominant design factors. The power dissipation includes two loss components; conduction loss and switching loss. These losses are distributed between the upper and lower MOSFETs according to duty factor (see the following equations). The conduction losses are the main component of power dissipation for the lower MOSFETs, Q2 and Q4 of Figure 1. Only the upper MOSFETs, Q1 and Q3 have significant switching losses, since the lower device turns on and off into near zero voltage.

The equations assume linear voltage-current transitions and do not model power loss due to the reverse-recovery of the lower MOSFETs body diode. The gate-charge losses are dissipated by the Driver IC and don't heat the MOSFETs. However, large gate-charge increases the switching time, t<sub>SW</sub> which increases the upper MOSFET switching losses. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

$$\begin{aligned} & P_{UPPER} = \frac{{I_{O}}^2 \times r_{DS(ON)} \times V_{OUT}}{V_{IN}} + \frac{{I_{O} \times V_{IN} \times t_{SW} \times F_{SW}}}{2} \\ & P_{LOWER} = \frac{{I_{O}}^2 \times r_{DS(ON)} \times (V_{IN} - V_{OUT})}{V_{IN}} \end{aligned}$$

A diode, anode to ground, may be placed across Q2 and Q4 of Figure 1. These diodes function as a clamp that catches the negative inductor swing during the dead time between the turn off of the lower MOSFETs and the turn on of the upper MOSFETs. The diodes must be a Schottky type to prevent the lossy parasitic MOSFET body diode from conducting. It is usually acceptable to omit the diodes and let the body diodes of the lower MOSFETs clamp the negative inductor swing, but efficiency could drop one or two percent as a result. The diode's rated reverse breakdown voltage must be greater than the maximum input voltage.

## References

Intersil documents are available on the web at www.intersil.com/

- [1] HIP6601/HIP6603 Data Sheet, Intersil Corporation, File No. 4819

- [2] HIP6602 Data Sheet, Intersil Corporation, File No. 4838

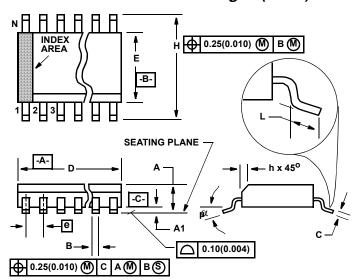

# Small Outline Plastic Packages (SOIC)

M16.15 (JEDEC MS-012-AC ISSUE C)

16 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES    |       | MILLIMETERS |       |       |

|--------|-----------|-------|-------------|-------|-------|

| SYMBOL | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α      | 0.053     | 0.069 | 1.35        | 1.75  | -     |

| A1     | 0.004     | 0.010 | 0.10        | 0.25  | -     |

| В      | 0.014     | 0.019 | 0.35        | 0.49  | 9     |

| С      | 0.007     | 0.010 | 0.19        | 0.25  | -     |

| D      | 0.386     | 0.394 | 9.80        | 10.00 | 3     |

| Е      | 0.150     | 0.157 | 3.80        | 4.00  | 4     |

| е      | 0.050 BSC |       | 1.27 BSC    |       | -     |

| Н      | 0.228     | 0.244 | 5.80        | 6.20  | -     |

| h      | 0.010     | 0.020 | 0.25        | 0.50  | 5     |

| L      | 0.016     | 0.050 | 0.40        | 1.27  | 6     |

| N      | 16        |       | 1           | 6     | 7     |

| α      | 0°        | 8º    | 0°          | 8º    | -     |

Rev. 1 02/02

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

© Copyright Intersil Americas LLC 2000-2004. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>