# ACPL-P340/ACPL-W340

1.0 Amp Output Current IGBT Gate Drive Optocoupler with Rail-to-Rail Output Voltage in Stretched SO6

# **Data Sheet**

# Description

The ACPL-P340/W340 contains an AlGaAs LED, which is optically coupled to an integrated circuit with a power output stage. This optocoupler is ideally suited for driving power IGBTs and MOSFETs used in motor control inverter applications. The high operating voltage range of the output stage provides the drive voltages required by gate controlled devices. The voltage and high peak output current supplied by this optocoupler make it ideally suited for direct driving IGBT with ratings up to 1200V/50A. For IGBTs with higher ratings, this optocoupler can be used to drive a discrete power stage which drives the IGBT gate. The ACPL-P340 and ACPL-W340 have the highest insulation voltage of V<sub>IORM</sub> = 891V<sub>peak</sub> and V<sub>IORM</sub> = 1140V<sub>peak</sub> respectively in the IEC/EN/DIN EN 60747-5-5.

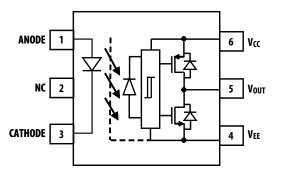

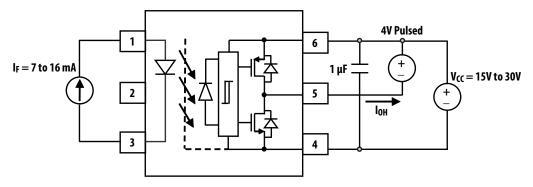

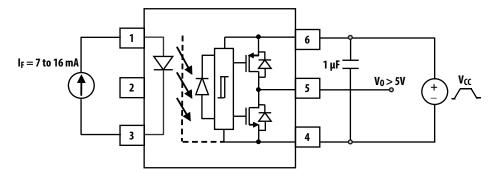

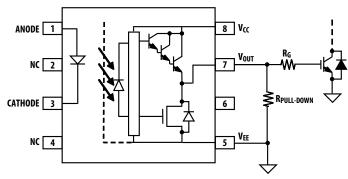

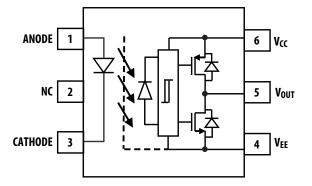

# **Functional Diagram**

Note: A 1  $\mu$ F bypass capacitor must be connected between pins V<sub>CC</sub> and V<sub>EE</sub>.

## Features

- 1.0A maximum peak output current

- 0.8A minimum peak output current

- Rail-to-rail output voltage

- 200 ns maximum propagation delay

- 100 ns maximum propagation delay difference

- LED current input with hysteresis

- 35 kV/ $\mu$ s minimum Common Mode Rejection (CMR) at V<sub>CM</sub> = 1500V

- I<sub>CC</sub> = 3.0 mA maximum supply current

- Under Voltage Lock-Out protection (UVLO) with hysteresis

- Wide operating V<sub>CC</sub> Range: 15V to 30V

- Industrial temperature range: -40°C to +105°C

- Safety Approval:

- UL Recognized 3750V/5000V<sub>RMS</sub> for 1 min.

- CSA

- IEC/EN/DIN EN 60747-5-5 V<sub>IORM</sub> = 891V/1140V<sub>peak</sub>

## **Applications**

- IGBT/MOSFET gate drive

- AC and Brushless DC motor drives

- Renewable energy inverters

- Industrial inverters

- Switching power supplies

**CAUTION:** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD. The components featured in this data sheet are not to be used in military or aerospace applications or environments.

## **Truth Table**

| LED | V <sub>CC</sub> – V <sub>EE</sub><br>POSITIVE GOING<br>(TURN-ON) | V <sub>CC</sub> – V <sub>EE</sub><br>NEGATIVE GOING<br>(TURN-OFF) | vo         |

|-----|------------------------------------------------------------------|-------------------------------------------------------------------|------------|

| OFF | 0 – 30 V                                                         | 0 – 30 V                                                          | LOW        |

| ON  | 0 – 12.1 V                                                       | 0 – 11.1 V                                                        | LOW        |

| ON  | 12.1 – 13.5 V                                                    | 11.1 – 12.4 V                                                     | TRANSITION |

| ON  | 13.5 – 30 V                                                      | 12.4 – 30 V                                                       | HIGH       |

# **Ordering Information**

ACPL-P340 is UL Recognized with  $3750V_{RMS}$  for 1 minute per UL1577. ACPL-W340 is UL Recognized with  $5000V_{RMS}$  for 1 minute per UL1577.

| Davit Number | Option                | Dackago   | Surface | Tana and Paol | IEC/EN/DIN EN | Quantity      |  |

|--------------|-----------------------|-----------|---------|---------------|---------------|---------------|--|

| Part Number  | <b>RoHS</b> Compliant | Package   | Mount   | Tape and Reel | 60747-5-5     | Quantity      |  |

| ACPL-P340    | -000E                 | Stretched | Х       |               |               | 100 per tube  |  |

| ACPL-W340    | -500E                 | SO6       | Х       | X             |               | 1000 per reel |  |

|              | -060E                 |           | Х       |               | Х             | 100 per tube  |  |

|              | -560E                 |           | Х       | X             | Х             | 1000 per reel |  |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

Example 1:

ACPL-P340-560E to order product of Stretched SO6 Surface Mount package in Tape and Reel packaging with IEC/EN/DIN EN 60747-5-5 Safety Approval in RoHS compliant.

Example 2:

ACPL-W340-000E to order product of Stretched SO6 Surface Mount package in Tube packaging and RoHS compliant.

Option data sheets are available. Contact your Broadcom sales representative or authorized distributor for information.

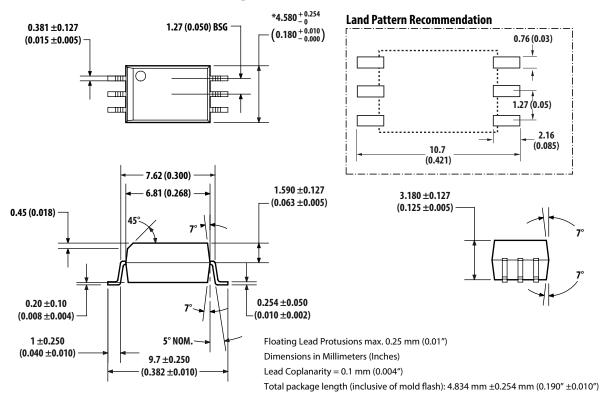

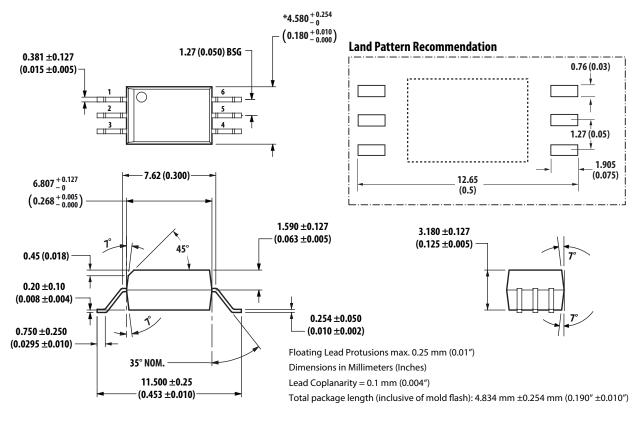

## Package Outline Drawing

## ACPL-P340 Stretched SO6 Package (7 mm Clearance)

### ACPL-W340 Stretched SO6 Package (8 mm Clearance)

### **Recommended Pb-Free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision). Non-Halide Flux should be used.

### **Regulatory Information**

The ACPL-P340/W340 is approved by the following organizations:

| UL                | Recognized under UL 1577, component recognition program up to $V_{ISO} = 3750V_{RMS}$ (ACPL-P340) and $V_{ISO} = 5000V_{RMS}$ (ACPL-W340). |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| CSA               | CSA Component Acceptance Notice #5, File CA 88324                                                                                          |

| IEC/EN/DIN        | Maximum Working Insulation Voltage $V_{IORM} = 891V_{peak}$ (ACPL-P340) and $V_{IORM} = 1140V_{peak}$ (ACPL-                               |

| EN 60747-5-5      | W340)                                                                                                                                      |

| (Option 060 Only) |                                                                                                                                            |

## IEC/EN/DIN EN 60747-5-5 Insulation Characteristics\* (Option 060)

| Description                                                                                                                                                                                                                                                                                | Symbol                | ACPL-<br>P340<br>Option<br>060      | ACPL-<br>W340<br>Option<br>060                 | Unit              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------|------------------------------------------------|-------------------|

| Installation classification per DIN VDE 0110/39, Table 1<br>for rated mains voltage $\leq 150V_{RMS}$<br>for rated mains voltage $\leq 300V_{RMS}$<br>for rated mains voltage $\leq 450V_{RMS}$<br>for rated mains voltage $\leq 600V_{RMS}$<br>for rated mains voltage $\leq 1000V_{RMS}$ |                       | –  V<br>  –  V<br>  –  I <br>  –  I | I – IV<br>I – IV<br>I – IV<br>I – IV<br>I – II |                   |

| Climatic Classification                                                                                                                                                                                                                                                                    |                       | 40/105/21                           | 40/105/21                                      |                   |

| Pollution Degree (DIN VDE 0110/39)                                                                                                                                                                                                                                                         |                       | 2                                   | 2                                              |                   |

| Maximum Working Insulation Voltage                                                                                                                                                                                                                                                         | VIORM                 | 891                                 | 1,140                                          | V <sub>peak</sub> |

| Input to Output Test Voltage, Method b*<br>V <sub>IORM</sub> $\times$ 1.875 = V <sub>PR</sub> , 100% Production Test with t <sub>m</sub> =1 sec, Partial discharge < 5 pC                                                                                                                  | V <sub>PR</sub>       | 1,671                               | 2,137                                          | V <sub>peak</sub> |

| Input to Output Test Voltage, Method a*<br>V <sub>IORM</sub> × 1.6 = V <sub>PR</sub> , Type and Sample Test, t <sub>m</sub> =10 sec, Partial discharge < 5 pC                                                                                                                              | V <sub>PR</sub>       | 1,426                               | 1,824                                          | V <sub>peak</sub> |

| Highest Allowable Overvoltage*<br>(Transient Overvoltage t <sub>ini</sub> = 60 sec)                                                                                                                                                                                                        | V <sub>IOTM</sub>     | 6,000                               | 8,000                                          | V <sub>peak</sub> |

| Safety-limiting values – maximum values allowed in the event of a failure                                                                                                                                                                                                                  |                       |                                     |                                                |                   |

| Case Temperature                                                                                                                                                                                                                                                                           | Ts                    | 175                                 | 175                                            | °C                |

| Input Current                                                                                                                                                                                                                                                                              | I <sub>S, INPUT</sub> | 230                                 | 230                                            | mA                |

| Output Power                                                                                                                                                                                                                                                                               | Ps, output            | 600                                 | 600                                            | mW                |

| Insulation Resistance at $T_S$ , $V_{IO} = 500V$                                                                                                                                                                                                                                           | Rs                    | >10 <sup>9</sup>                    | >10 <sup>9</sup>                               | Ω                 |

\*Refer to IEC/EN/DIN EN 60747-5-5 Optoisolator Safety Standard section of the Broadcom Regulatory Guide to Isolation Circuits, AV02-2041EN for a detailed description of Method a and Method b partial discharge test profiles.

Note: These optocouplers are suitable for "safe electrical isolation" only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits. Surface mount classification is Class A in accordance with CECC 00802.

# Insulation and Safety Related Specifications

| Parameter                                               | Symbol | ACPL-<br>P340 | ACPL-<br>W340 | Unit | Conditions                                                                                                                         |

|---------------------------------------------------------|--------|---------------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External<br>Air Gap (Clearance)                 | L(101) | 7.0           | 8.0           | mm   | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External<br>Tracking (Creepage)                 | L(102) | 8.0           | 8.0           | mm   | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal<br>Plastic Gap<br>(Internal Clearance) |        | 0.08          | 0.08          | mm   | Through insulation distance conductor to conductor, usually the straight line distance thickness between the emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking<br>Index)  | CTI    | >175          | >175          | V    | DIN IEC 112/VDE 0303 Part 1                                                                                                        |

| Isolation Group                                         |        | Illa          | Illa          |      | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                       |

Note: All Broadcom data sheets report the creepage and clearance inherent to the optocoupler component itself. These dimensions are needed as a starting point for the equipment designer when determining the circuit insulation requirements. However, once mounted on a printed circuit board, minimum creepage and clearance requirements must be met as specified for individual equipment standards. For creepage, the shortest distance path along the surface of a printed circuit board between the solder fillets of the input and output leads must be considered (the recommended Land Pattern does not necessarily meet the minimum creepage of the device). There are recommended techniques such as grooves and ribs which may be used on a printed circuit board to achieve desired creepage and clearances. Creepage and clearance distances will also change depending on factors such as pollution degree and insulation level.

## **Absolute Maximum Ratings**

| Parameter                                                 | Symbol                                        | Min. | Max.            | Unit | Note |  |

|-----------------------------------------------------------|-----------------------------------------------|------|-----------------|------|------|--|

| Storage Temperature                                       | Ts                                            | -55  | +125            | °C   |      |  |

| Operating Temperature                                     | T <sub>A</sub>                                | -40  | +105            | °C   |      |  |

| Output IC Junction Temperature                            | Tj                                            |      | 125             | °C   |      |  |

| Average Input Current                                     | I <sub>F(AVG)</sub>                           |      | 25              | mA   | 1    |  |

| Peak Transient Input Current (<1 µs pulse width, 300 pps) | I <sub>F(TRAN)</sub>                          |      | 1               | A    |      |  |

| Reverse Input Voltage                                     | V <sub>R</sub>                                |      | 5               | V    |      |  |

| High Peak Output Current                                  | I <sub>OH(PEAK)</sub>                         |      | 1.0             | A    | 2    |  |

| Low Peak Output Current                                   | I <sub>OL(PEAK)</sub>                         |      | 1.0             | A    | 2    |  |

| Total Output Supply Voltage                               | (V <sub>CC</sub> – V <sub>EE</sub> )          | 0    | 35              | V    |      |  |

| Input Current (Rise/Fall Time)                            | t <sub>r(IN)</sub> /t <sub>f(IN)</sub>        |      | 500             | ns   |      |  |

| Output Voltage                                            | V <sub>O(PEAK)</sub>                          | -0.5 | V <sub>CC</sub> | V    |      |  |

| Output IC Power Dissipation                               | Po                                            |      | 700             | mW   | 3    |  |

| Total Power Dissipation                                   | PT                                            |      | 745             | mW   | 4    |  |

| Lead Solder Temperature                                   | 260°C for 10 sec., 1.6 mm below seating plane |      |                 |      |      |  |

# **Recommended Operating Conditions**

| Parameter             | Symbol                               | Min. | Max. | Unit | Note |

|-----------------------|--------------------------------------|------|------|------|------|

| Operating Temperature | T <sub>A</sub>                       | -40  | +105 | °C   |      |

| Output Supply Voltage | (V <sub>CC</sub> – V <sub>EE</sub> ) | 15   | 30   | V    |      |

| Input Current (ON)    | I <sub>F(ON)</sub>                   | 7    | 16   | mA   |      |

| Input Voltage (OFF)   | V <sub>F(OFF)</sub>                  | -3.6 | +0.8 | V    |      |

# **Electrical Specifications (DC)**

All typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC} - V_{EE} = 30$ V,  $V_{EE} =$ Ground. All minimum and maximum specifications are at recommended operating conditions ( $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $I_{F(ON)} = 7$  mA to +16 mA,  $V_{F(OFF)} = -3.6$ V to +0.8V,  $V_{EE} =$  Ground,  $V_{CC} = 15$ V to 30V), unless otherwise noted.

| Parameter                                           | Symbol                    | Min.                  | Тур.                  | Max. | Unit  | Test Conditions                                                     | Fig.    | Note |

|-----------------------------------------------------|---------------------------|-----------------------|-----------------------|------|-------|---------------------------------------------------------------------|---------|------|

| High Level Peak Output Current                      | Іон                       | -0.3                  |                       |      | A     | $V_{O} = V_{CC} - 4V$                                               | 14      | 5    |

|                                                     |                           | -0.8                  |                       |      | A     | $V_{CC} - V_O \le 15V$                                              |         | 6    |

| Low Level Peak Output                               | I <sub>OL</sub>           | 0.3                   |                       |      | A     | $V_{O} = V_{EE} + 2.5V$                                             | 15      | 5    |

| Current                                             |                           | 0.8                   |                       |      | A     | $V_O - V_{EE} \le 15V$                                              |         | 7    |

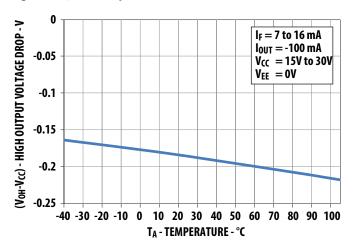

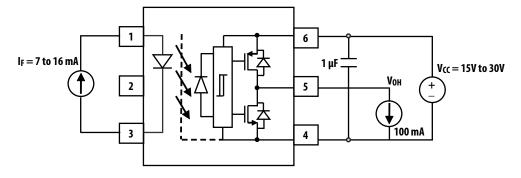

| High Level Output Voltage                           | V <sub>OH</sub>           | V <sub>CC</sub> – 0.3 | V <sub>CC</sub> – 0.2 |      | V     | $I_0 = -100 \text{ mA}$                                             | 2, 16   | 8, 9 |

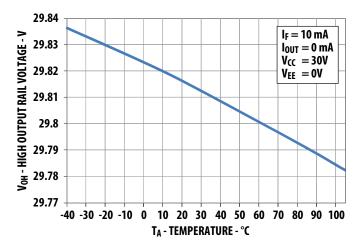

| High Level Output Voltage                           | V <sub>OH</sub>           |                       | V <sub>CC</sub>       |      | V     | $I_0 = 0 \text{ mA}, I_F = 10 \text{ mA}$                           | 1       |      |

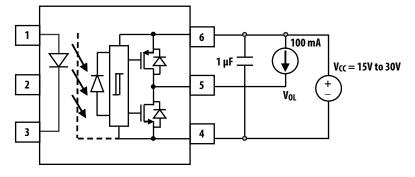

| Low Level Output Voltage                            | V <sub>OL</sub>           |                       | 0.1                   | 0.2  | V     | I <sub>O</sub> = 100 mA                                             | 5, 17   |      |

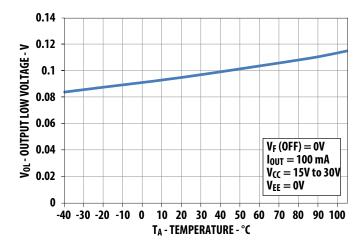

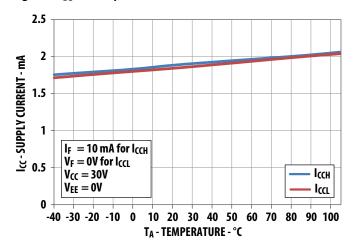

| High Level Supply Current                           | Іссн                      |                       | 1.9                   | 3.0  | mA    | $R_g = 10\Omega$ ,<br>$C_g = 25 \text{ nF}$ , $I_F = 10 \text{ mA}$ | 4, 5    |      |

| Low Level Supply Current                            | I <sub>CCL</sub>          |                       | 1.9                   | 3.0  | mA    | $R_g = 10\Omega$ ,<br>$C_g = 25$ nF, V <sub>F</sub> = 0V            |         |      |

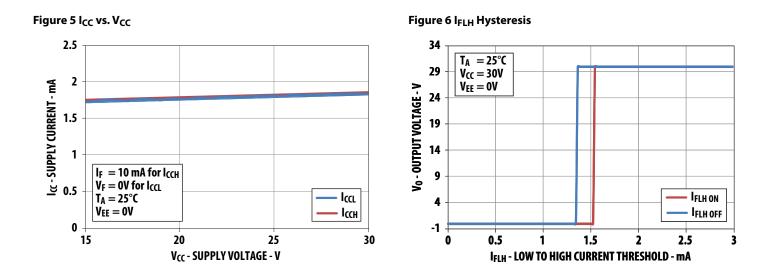

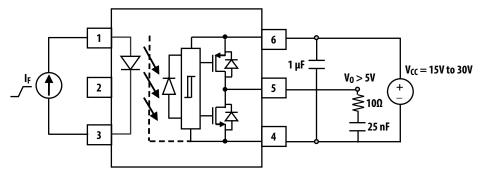

| Threshold Input Current<br>Low to High              | I <sub>FLH</sub>          |                       | 1.5                   | 4.0  | mA    | $R_g = 10\Omega,$<br>$C_g = 25 \text{ nF}, V_O > 5V$                | 6, 7, 8 |      |

| Threshold Input Voltage<br>High to Low              | V <sub>FHL</sub>          | 0.8                   |                       |      | V     |                                                                     |         |      |

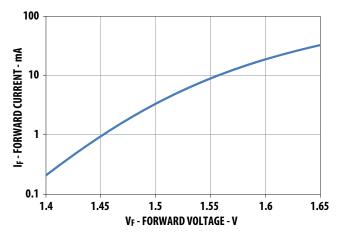

| Input Forward Voltage                               | VF                        | 1.2                   | 1.55                  | 1.95 | V     | I <sub>F</sub> = 10 mA                                              | 13      |      |

| Temperature Coefficient<br>of Input Forward Voltage | $\Delta V_F / \Delta T_A$ |                       | -1.7                  |      | mV/°C | l <sub>F</sub> = 10 mA                                              |         |      |

| Input Reverse Breakdown Voltage                     | BV <sub>R</sub>           | 5                     |                       |      | V     | I <sub>R</sub> = 100 μA                                             |         |      |

| Input Capacitance                                   | C <sub>IN</sub>           |                       | 70                    |      | pF    | $f = 1 MHz, V_F = 0V$                                               |         |      |

| UVLO Threshold                                      | V <sub>UVLO+</sub>        | 12.1                  | 12.8                  | 13.5 | V     | $V_{O} > 5V, I_{F} = 10 \text{ mA}$                                 | 19      |      |

|                                                     | V <sub>UVLO-</sub>        | 11.1                  | 11.8                  | 12.4 | ]     |                                                                     |         |      |

| UVLO Hysteresis                                     | UVLO <sub>HYS</sub>       |                       | 1.0                   |      | V     |                                                                     |         |      |

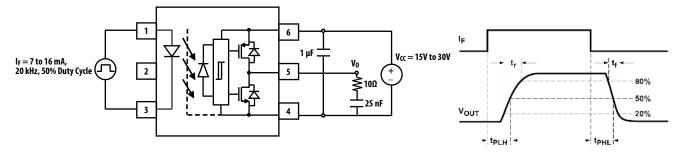

# Switching Specifications (AC)

Unless otherwise noted, all typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC} - V_{EE} = 30$ V,  $V_{EE} =$ Ground; all minimum and maximum specifications are at recommended operating conditions ( $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C,  $I_F(ON) = 7$  mA to 16 mA,  $V_F(OFF) = -3.6$ V to +0.8V,  $V_{EE} =$  Ground,  $V_{CC} = 15$ V to 30V).

| Parameter                                             | Symbol                                        | Min. | Тур. | Max. | Unit  | Test Conditions                                                                                                                   | Fig.             | Note   |

|-------------------------------------------------------|-----------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|--------|

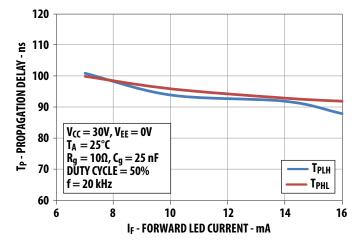

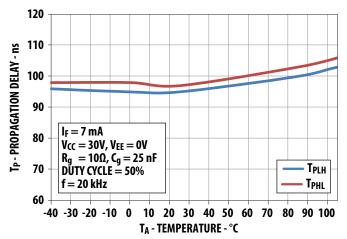

| Propagation Delay Time to<br>High Output Level        | t <sub>PLH</sub>                              | 50   | 98   | 200  | ns    | $R_{g} = 10\Omega, C_{g} = 25 \text{ nF},$ $f = 20 \text{ kHz},$                                                                  | 8, 9,<br>10, 11, |        |

| Propagation Delay Time to<br>Low Output Level         | t <sub>PHL</sub>                              | 50   | 95   | 200  | ns    | Duty Cycle = 50%,<br>$I_F = 7 \text{ mA to } 16 \text{ mA},$<br>$V_{CC} = 15V \text{ to } 30V$                                    | 12, 20           |        |

| Pulse Width Distortion                                | PWD                                           |      | 22   | 70   | ns    | VCC - 13V to 30V                                                                                                                  |                  | 10     |

| Propagation Delay Difference<br>Between Any Two Parts | PDD<br>(t <sub>PHL</sub> – t <sub>PLH</sub> ) | -100 |      | +100 | ns    |                                                                                                                                   | 27, 28           | 11     |

| Rise Time                                             | t <sub>R</sub>                                |      | 43   |      | ns    | Vcc = 30 V                                                                                                                        | 20               |        |

| Fall Time                                             | t <sub>F</sub>                                |      | 40   |      | ns    |                                                                                                                                   |                  |        |

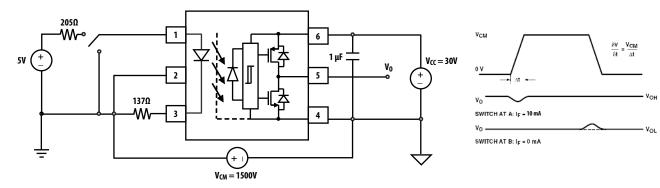

| Output High Level Common<br>Mode Transient Immunity   | CM <sub>H</sub>                               | 35   | 50   |      | kV/μs | $T_A = 25^{\circ}C, I_F = 10 \text{ mA},$<br>$V_{CC} = 30V, V_{CM} = 1500V \text{ with}$<br>split resistors                       | 21               | 12, 13 |

| Output Low Level Common<br>Mode Transient Immunity    | CML                                           | 35   | 50   |      | kV/µs | $T_A = 25^{\circ}\text{C}, V_F = 0\text{V}, \\ V_{CC} = 30\text{V}, V_{CM} = 1500\text{V} \text{ with} \\ \text{split resistors}$ |                  | 12, 14 |

# Package Characteristics

All typical values are at  $T_A = 25^{\circ}$ C. All minimum/maximum specifications are at recommended operating conditions, unless otherwise noted.

| Parameter                                    | Symbol           | Device    | Min. | Тур.  | Max. | Unit             | Test Conditions                                | Fig. | Note  |

|----------------------------------------------|------------------|-----------|------|-------|------|------------------|------------------------------------------------|------|-------|

| Input-Output Momentary<br>Withstand Voltage* | V <sub>ISO</sub> | ACPL-P340 | 3750 |       |      | V <sub>RMS</sub> | RH < 50%,<br>t = 1 min., T <sub>A</sub> = 25°C |      | 15,17 |

|                                              |                  | ACPL-W340 | 5000 |       |      | V <sub>RMS</sub> | RH < 50%,<br>t = 1 min., T <sub>A</sub> = 25°C |      | 16,17 |

| Input-Output Resistance                      | R <sub>I-O</sub> |           |      | >5012 |      | Ω                | $V_{I-O} = 500V_{DC}$                          |      | 17    |

| Input-Output Capacitance                     | C <sub>I-O</sub> |           |      | 0.6   |      | pF               | f=1 MHz                                        |      |       |

| LED-to-Ambient<br>Thermal Resistance         | R <sub>11</sub>  |           |      | 135   |      | °C/W             |                                                |      | 18    |

| LED-to-Detector<br>Thermal Resistance        | R <sub>12</sub>  |           |      | 27    |      |                  |                                                |      |       |

| Detector-to-LED<br>Thermal Resistance        | R <sub>21</sub>  |           |      | 39    |      |                  |                                                |      |       |

| Detector-to-Ambient<br>Thermal Resistance    | R <sub>22</sub>  |           |      | 47    |      |                  |                                                |      |       |

\*The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating, refer to your equipment level safety specification or Broadcom Application Note 1074 entitled "Optocoupler Input-Output Endurance Voltage."

#### Notes:

- 1. Derate linearly above 70°C free-air temperature at a rate of 0.3 mA/°C.

- 2. Maximum pulse width = 10 μs. This value is intended to allow for component tolerances for designs with I<sub>O</sub> peak minimum = 0.8A. See applications section for additional details on limiting I<sub>OH</sub> peak.

- 3. Derate linearly above 85°C free-air temperature at a rate of 16.9 mW/°C.

- 4. Derate linearly above 85°C free-air temperature at a rate of 15.3 mW/°C. The maximum LED junction temperature should not exceed 125°C.

- 5. Maximum pulse width = 50  $\mu$ s.

- 6. Output is sourced at -0.8A with a maximum pulse width = 10  $\mu$ s. V<sub>CC</sub> V<sub>O</sub> is measured to ensure 15V or below.

- 7. Output is sourced at 0.8A with a maximum pulse width =  $10 \mu s$ .  $V_0 V_{EE}$  is measured to ensure 15V or below.

- 8. In this test V<sub>OH</sub> is measured with a DC load current. When driving capacitive loads, V<sub>OH</sub> will approach V<sub>CC</sub> as I<sub>OH</sub> approaches zero amps.

- 9. Maximum pulse width = 1 ms.

- 10. Pulse Width Distortion (PWD) is defined as  $|t_{PHL}-t_{PLH}|$  for any given device.

- 11. The difference between t<sub>PHL</sub> and t<sub>PLH</sub> between any two ACPL-P340 parts under the same test condition.

- 12. Pin 2 needs to be connected to LED common.

- 13. Common mode transient immunity in the high state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to assure that the output will remain in the high state (meaning,  $V_0 > 15.0V$ ).

- 14. Common mode transient immunity in a low state is the maximum tolerable dV<sub>CM</sub>/dt of the common mode pulse, V<sub>CM</sub>, to assure that the output will remain in a low state (meaning, V<sub>O</sub> < 1.0V).

- 15. In accordance with UL1577, each optocoupler is proof tested by applying an insulation test voltage  $\leq$  4500V<sub>RMS</sub> for 1 second (leakage detection current limit,  $I_{I-O} < 5 \ \mu$ A).

- 16. In accordance with UL1577, each optocoupler is proof tested by applying an insulation test voltage  $\leq$  6000V<sub>RMS</sub> for 1 second (leakage detection current limit,  $I_{I-O} < 5 \ \mu$ A).

- 17. Device considered a two-terminal device: pins 1, 2, and 3 shorted together and pins 4, 5, and 6 shorted together.

- 18. The device was mounted on a high conductivity test board as per JEDEC 51-7.

## **Typical Performance Plots**

#### Figure 1 High Output Rail Voltage vs. Temperature

Figure 2 V<sub>OH</sub> vs. Temperature

Figure 3 V<sub>OL</sub> vs. Temperature

Figure 4 I<sub>CC</sub> vs. Temperature

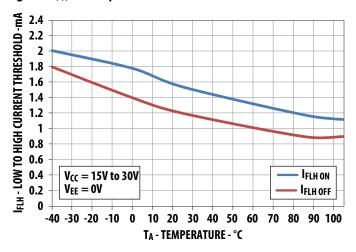

#### Figure 7 I<sub>FH</sub> vs. Temperature

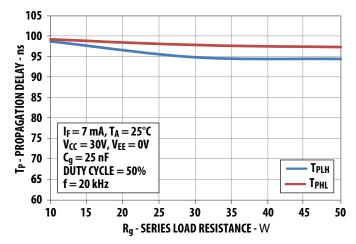

120 110 TP - PROPAGATION DELAY - ns 100 90  $I_F = 7 \text{ mA}$ 80  $T_A = 25^{\circ}C$  $R_g = 10\Omega, C_g = 25 \text{ nF}$ 70 TPLH DUTY CYCLE = 50% f = 20 kHzTPHL 60 15 20 25 30 Vcc - SUPPLY VOLTAGE - V

Figure 9 Propagation Delay vs. IF

Figure 10 Propagation Delay vs. Temperature

Figure 8 Propagation Delay vs. V<sub>CC</sub>

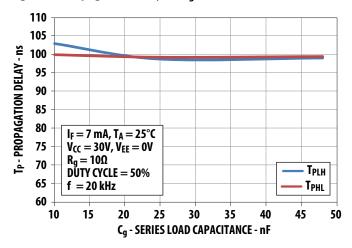

Figure 12 Propagation Delay vs. Cg

#### Figure 13 Input Current vs. Forward Voltage

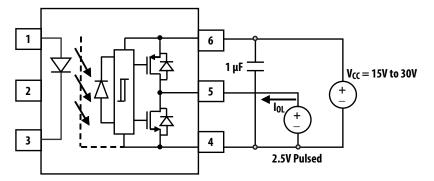

### Figure 14 I<sub>OH</sub> Test Circuit

#### Figure 15 I<sub>OL</sub> Test Circuit

#### Figure 16 V<sub>OH</sub> Test Circuit

Figure 17 V<sub>OL</sub> Test Circuit

### Figure 18 I<sub>FLH</sub> Test Circuit

#### Figure 19 UVLO Test Circuit

#### Figure 20 t<sub>PHL</sub>, t<sub>PHL</sub>, t<sub>r</sub>, and t<sub>f</sub> Test Circuit and Waveforms

#### Figure 21 CMR Test Circuit with Split Resistors Network and Waveforms

# **Application Information**

## **Product Overview Description**

The ACPL-P340/W340 is an optically isolated power output stage capable of driving IGBTs of up to 50A and 1200V. Based on BCDMOS technology, this gate drive optocoupler delivers higher peak output current, better rail-to-rail output voltage performance, and two times faster speed than the previous generation products.

The high-peak output current and short propagation delay are needed for fast IGBT switching to reduce dead time and improve system overall efficiency. Rail-to-rail output voltage ensures that the IGBT's gate voltage is driven to the optimum intended level with no power loss across IGBT. This helps the designer lower the system power which is suitable for bootstrap power supply operation.

It has very high CMR(common mode rejection) rating which allows the microcontroller and the IGBT to operate at very large common mode noise found in industrial motor drives and other power switching applications. The input is driven by direct LED current and has a hysteresis that prevents output oscillation if insufficient LED driving current is applied. This will eliminates the need of additional Schmitt trigger circuit at the input LED.

The stretched SO6 package which is up to 50% smaller than conventional DIP package facilitates smaller more compact design. These stretched packages are compliant to many industrial safety standards such as IEC/EN/DIN EN 60747-5-5, UL 1577 and CSA.

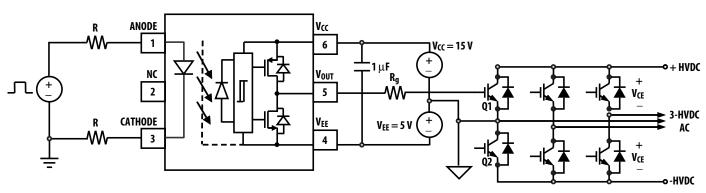

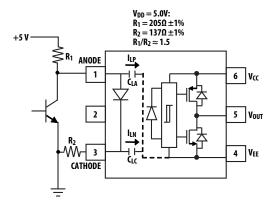

### Figure 22 Recommended Application Circuit with Split Resistors LED

# **Recommended Application Circuit**

The recommended application circuit shown in Figure 22 illustrates a typical gate drive implementation using the ACPL-P340. The following describes about driving IGBT. However, it is also applicable to MOSFET. Designers will need to adjust the V<sub>CC</sub> supply voltage, depending on the MOSFET or IGBT gate threshold requirements (Recommended VCC = 15V for IGBT and 12V for MOSFET).

The supply bypass capacitors (1  $\mu$ F) provide the large transient currents necessary during a switching transition. Because of the transient nature of the charging currents, a low current (3.0 mA) power supply will be enough to power the device. The split resistors (in the ratio of 1.5:1) across the LED will provide a high CMR response by providing a balanced resistance network across the LED.

The gate resistor RG serves to limit gate charge current and controls the IGBT collector voltage rise and fall times.

In PC board design, care should be taken to avoid routing the IGBT collector or emitter traces close to the ACPL-P340 input as this can result in unwanted coupling of transient signals into ACPL-P340 and degrade performance.

## **Rail-to-Rail Output**

Figure 23 shows a typical gate driver's high current output stage with 3 bipolar transistors in darlington configuration. During the output high transition, the output voltage rises rapidly to within 3 diode drops of V<sub>CC</sub>. To ensure the V<sub>OUT</sub> is at V<sub>CC</sub> in order to achieve IGBT rated V<sub>CE(ON)</sub> voltage. The level of V<sub>CC</sub> will be need to be raised to beyond V<sub>CC</sub>+3(V<sub>BE</sub>) to account for the diode drops. And to limit the output voltage to V<sub>CC</sub>, a pull-down resistor, R<sub>PULL-DOWN</sub> between the output and V<sub>EE</sub> is recommended to sink a static current while the output is high.

# Figure 23 Typical Gate Driver with Output Stage in Darlington Configuration

Figure 24 PMOS and NMOS Output Stage for Rail-to-Rail Output Voltage

ACPL-P340 uses a power PMOS to deliver the large current and pull it to  $V_{CC}$  to achieve rail-to-rail output voltage as shown in Figure 24. This ensures that the IGBT's gate voltage is driven to the optimum intended level with no power loss across IGBT even when an unstable power supply is used.

## Selecting the Gate Resistor (Rg)

**Step 1:** Calculate Rg minimum from the I<sub>OL</sub> peak specification. The IGBT and Rg in Figure 22 can be analyzed as a simple RC circuit with a voltage supplied by ACPL-P340/W340.

$$R_{g} \ge \frac{V_{CC} - V_{EE} - V_{OL}}{I_{OLPEAK}}$$

$$= \frac{15V + 5V - 0.6V}{1A}$$

$$= 19.4\Omega \approx 20\Omega$$

**Step 1:** Check the ACPL-P340/W340 power dissipation and increase Rg if necessary. The ACPL-P340/W340 total power dissipation ( $P_T$ ) is equal to the sum of the emitter power ( $P_E$ ) and the output power ( $P_O$ ).

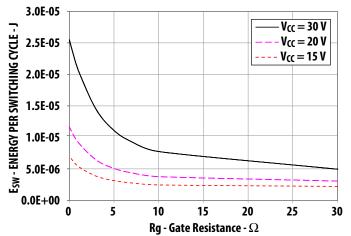

$$\begin{split} P_T &= P_E + P_O \\ P_E &= I_F \times V_F \times \text{Duty Cycle} \\ P_O &= P_{O(BIAS)} + P_{O(SWITCHING)} \\ &= I_{CC} \times (V_{CC} - V_{EE}) + E_{SW}(Rg;Cg) \times f \end{split}$$

Using  $I_F$ (worst case) = 16 mA,  $R_g = 20\Omega$ , Max Duty Cycle = 80%, Cg = 25 nF, f = 25 kHz and  $T_A$  max = 85°C:

$P_E = 16 \text{ mA} \times 1.95 \text{V} \times 0.8 = 25 \text{ mW}$

$P_0 = 3 \text{ mA} \times 20\text{V} + 3.5 \,\mu\text{J} \cdot 25 \,\text{kHz}$

- = 60 mW + 87.5 mW

- = 147.5 mW < 700 mW (P<sub>O(MAX)</sub> at 85°C)

The value of 3 mA for  $I_{CC}$  in the previous equation is the maximum  $I_{CC}$  over the entire operating temperature range.

Since  $P_O$  is less than  $P_{O(MAX)}\text{, }Rg=20\Omega$  is alright for the power dissipation.

# LED Drive Circuit Considerations for High CMR Performance

Figure 26 shows the recommended drive circuit for the ACPL-P340/W340 that gives optimum common-mode rejection. The two current setting resistors balance the common mode impedances at the LED's anode and cathode. Common-mode transients can be capacitive coupled from the LED anode, through  $C_{LA}$  (or cathode through  $C_{LC}$ ) to the output-side ground causing current to be shunted away from the LED (which is not wanted when the LED should be on) or conversely cause current to be injected into the LED (which is not wanted when the LED should be off).

Table 8 shows the directions of  $I_{LP}$  and  $I_{LN}$  depend on the polarity of the common-mode transient. For transients occurring when the LED is on, common-mode rejection (CM<sub>H</sub>, since the output is at "high" state) depends on LED current ( $I_F$ ). For conditions where  $I_F$  is close to the switching threshold ( $I_{FLH}$ ), CM<sub>H</sub> also depends on the extent to which  $I_{LP}$  and  $I_{LN}$  balance each other. In other words, any condition where a common-mode transient causes a momentary decrease in  $I_F$  (meaning when  $dV_{CM}/dt > 0$  and  $|I_{LP}| > |I_{LN}|$ , referring to Table 8) will cause a common-mode failure for transients which are fast enough.

Likewise for a common-mode transient that occurs when the LED is off (meaning  $CM_L$ , since the output is at "low" state), if an imbalance between  $I_{LP}$  and  $I_{LN}$  results in a transient  $I_F$  equal to or greater than the switching threshold of the optocoupler, the transient "signal" may cause the output to spike above 1 V, which constitutes a  $CM_L$  failure. The balanced  $I_{LED}$ -setting resistors help equalize the common mode voltage change at the anode and cathode. The shunt drive input circuit will also help to achieve high  $CM_L$  performance by shunting the LED in the off state.

#### Figure 26 Recommended High-CMR Drive Circuit

## **Common Mode Pulse Polarity and LED Current Transients**

| dV <sub>CM</sub> /dt | I <sub>LP</sub> Direction            | I <sub>LP</sub> Direction              | lf  I <sub>LP</sub>   <  I <sub>LN</sub>  ,<br>I <sub>F</sub> is momentarily | If  I <sub>LP</sub>   >  I <sub>LN</sub>  ,<br>I <sub>F</sub> is momentarily |

|----------------------|--------------------------------------|----------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Positive (>0)        | Away from LED anode through $C_{LA}$ | Away from LED cathode through $C_{LC}$ | Increase                                                                     | Decrease                                                                     |

| Negative(<0)         | Toward LED anode through $C_{LA}$    | Toward LED cathode through $C_{LC}$    | Decrease                                                                     | Increase                                                                     |

# **Dead Time and Propagation Delay Specifications**

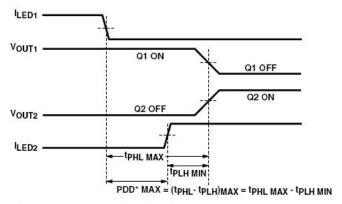

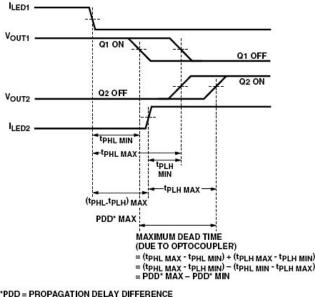

The ACPL-P340/W340 includes a Propagation Delay Difference (PDD) specification intended to help designers minimize "dead time" in their power inverter designs. Dead time is the time period during which both the high and low side power transistors (Q1 and Q2 in Figure 22) are off. Any overlap in Q1 and Q2 conduction will result in large currents flowing through the power devices between the high and low voltage motor rails.

To minimize dead time in a given design, the turn on of LED2 should be delayed (relative to the turn off of LED1) so that under worst-case conditions, transistor Q1 has just turned off when transistor Q2 turns on, as shown in Figure 24. The amount of delay necessary to achieve this condition is equal to the maximum value of the propagation delay difference specification, PDD<sub>MAX</sub>, which is specified to be 100 ns over the operating temperature range of -40°C to 105°C.

Delaying the LED signal by the maximum propagation delay difference ensures that the minimum dead time is zero, but it does not tell a designer what the maximum dead time will be. The maximum dead time is equivalent to the difference between the maximum and minimum propagation delay difference specifications as shown in Figure 25. The maximum dead time for the ACPL-P340/W340 is 100 ns (= 50 ns - (-50 ns)) over an operating temperature range of -40°C to 105°C.

Note that the propagation delays used to calculate PDD and dead time are taken at equal temperatures and test conditions since the optocouplers under consideration are typically mounted in close proximity to each other and are switching identical MOSFETs.

#### Figure 27 Minimum LED Skew for Zero Dead Time

\*PDD = PROPAGATION DELAY DIFFERENCE NOTE: FOR PDD CALCULATIONS THE PROPAGATION DELAYS ARE TAKEN AT THE SAME TEMPERATURE AND TEST CONDITIONS.

#### **Figure 28 Waveforms for Dead Time**

NOTE: FOR DEAD TIME AND PDD CALCULATIONS ALL PROPAGATION DELAYS ARE TAKEN AT THE SAME TEMPERATURE AND TEST CONDITIONS.

# **LED Current Input with Hysteresis**

The detector has optical receiver input stage with built in Schmitt trigger to provide logic compatible waveforms, eliminating the need for additional wave shaping. The hysteresis (Figure 12) provides differential mode noise immunity and minimizes the potential for output signal chatter.

# **Under Voltage Lockout**

The ACPL-P340/W340 Under Voltage Lockout (UVLO) feature is designed to prevent the application of insufficient gate voltage to the IGBT by forcing the ACPL-P340/W340 output low during power-up. IGBTs typically require gate voltages of 15V to achieve their rated V<sub>CE(ON)</sub> voltage. At gate voltages below 13V typically, the V<sub>CE(ON)</sub> voltage increases dramatically, especially at higher currents. At very low gate voltages (below 10V), the IGBT may operate in the linear region and quickly overheat. The UVLO function causes the output to be clamped whenever insufficient operating supply (V<sub>CC</sub>) is applied. Once V<sub>CC</sub> exceeds V<sub>UVLO+</sub> (the positive-going UVLO threshold), the UVLO clamp is released to allow the device output to turn on in response to input signals.

## Thermal Model for ACPL-P340/W340 Stretched SO6 Package Optocoupler

## Definitions

- R<sub>11</sub>: Junction to Ambient Thermal Resistance of LED due to heating of LED

- R<sub>12</sub>: Junction to Ambient Thermal Resistance of LED due to heating of Detector (Output IC)

- R<sub>21</sub>: Junction to Ambient Thermal Resistance of Detector (Output IC) due to heating of LED.

- R<sub>22</sub>: Junction to Ambient Thermal Resistance of Detector (Output IC) due to heating of Detector (Output IC).

- P<sub>1</sub>: Power dissipation of LED (W).

- P<sub>2</sub>: Power dissipation of Detector / Output IC (W).

- T<sub>1</sub>: Junction temperature of LED (°C).

- T<sub>2</sub>: Junction temperature of Detector (°C).

- Ta: Ambient temperature.

Ambient Temperature: Junction to Ambient Thermal

| Resistances were measured approximately 1.25 cm above |

|-------------------------------------------------------|

| optocoupler at ~23°C in still air.                    |

| Thermal Resistance | °C/W |

|--------------------|------|

| R <sub>11</sub>    | 135  |

| R <sub>12</sub>    | 27   |

| R <sub>21</sub>    | 39   |

| R <sub>22</sub>    | 47   |

This thermal model assumes that an 6-pin single-channel plastic package optocoupler is soldered into a 7.62 cm  $\times$  7.62 cm printed circuit board (PCB) per JEDEC standards. The temperature at the LED and Detector junctions of the opto-coupler can be calculated using the equations below.

$$T_1 = (R_{11} \times P_1 + R_{12} \times P_2) + Ta - (1)$$

$T_2 = (R_{21} \times P_1 + R_{22} \times P_2) + Ta - (2)$

Using the given thermal resistances and thermal model formula in this datasheet, we can calculate the junction temperature for both LED and the output detector. Both junction temperatures should be within the absolute maximum rating.

For example, given  $P_1 = 17 \text{ mW}$ ,  $P_2 = 124 \text{ mW}$ ,  $Ta = 85^{\circ}\text{C}$ :

LED junction temperature,

$T_1 = (R_{11} \times P_1 + R_{12} \times P_2) + Ta$ = (135 × 0.017 + 27 × 0.124) + 85 = 90.7°C

Output IC junction temperature,

$$T_2 = (R_{21} \times P_1 + R_{22} \times P_2) + T_a$$

= (39 × 0.017 + 47 × 0.124) + 85

= 91.5°C

$T_1$  and  $T_2$  should be limited to 125  $^\circ C$  based on the board layout and part placement.

# **Related Documents**

| AV02-0421EN | Application Note 5336 | Gate Drive Optocoupler Basic Design for IGBT/MOSFET        |

|-------------|-----------------------|------------------------------------------------------------|

| AV02-3698EN | Application Note 1043 | Common-Mode Noise: Sources and Solutions                   |

| AV02-0310EN | Reliability Data      | Plastics Optocouplers Product ESD and Moisture Sensitivity |

For product information and a complete list of distributors, please go to our web site: <u>www.broadcom.com</u>.

Broadcom, the pulse logo, Connecting everything, Avago Technologies, Avago, the A logo, and R<sup>2</sup>Coupler are among the trademarks of Broadcom and/or its affiliates in the United States, certain other countries and/or the EU.

Broadcom Proprietary and Confidential. Copyright © 2017 Broadcom. All Rights Reserved. The term "Broadcom" refers to Broadcom Limited and/or its subsidiaries.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. AV02-2930EN – May 8, 2017