ADC128S102

SNAS298G -AUGUST 2005-REVISED JANUARY 2015

# ADC128S102 8-Channel, 500-ksps to 1-Msps, 12-Bit A/D Converter

## **Features**

- Eight Input Channels

- Variable Power Management

- Independent Analog and Digital Supplies

- SPI/QSPI™/MICROWIRE™/DSP Compatible

- Packaged in 16-Lead TSSOP

- **Key Specifications**

- Conversion Rate 500 ksps to 1 MSPS

- DNL ( $V_A = V_D = 5.0 \text{ V}$ ) +1.5 / -0.9

- LSB (maximum) INL  $(V_A = V_D = 5.0 \text{ V}) \pm 1.2$ LSB (maximum)

- Power Consumption

- 3V Supply 2.3 mW (typical)

- 5V Supply 10.7 mW (typical)

## 2 Applications

- **Automotive Navigation**

- Portable Systems

- Medical Instruments

- Mobile Communications

- Instrumentation and Control Systems

## 3 Description

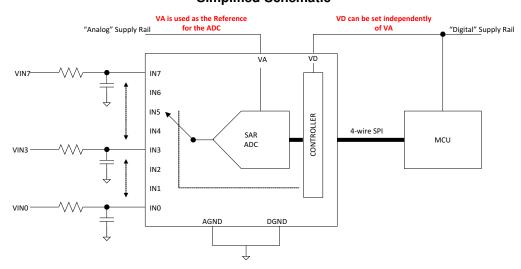

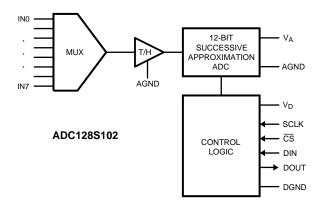

The ADC128S102 is a low-power, eight-channel CMOS 12-bit analog-to-digital converter specified for conversion throughput rates of 500 ksps to 1 MSPS. converter is based on a successiveapproximation register architecture with an internal track-and-hold circuit. It can be configured to accept up to eight input signals at inputs IN0 through IN7.

The output serial data is straight binary and is compatible with several standards, such as SPI, QSPI, MICROWIRE, and many common DSP serial interfaces.

The ADC128S102 may be operated with independent analog and digital supplies. The analog supply (V<sub>A</sub>) can range from +2.7 V to +5.25 V, and the digital supply  $(V_D)$  can range from +2.7 V to  $V_A$ . Normal power consumption using a +3-V or +5-V supply is 2.3 mW and 10.7 mW, respectively. The power-down feature reduces the power consumption to 0.06 μW using a +3-V supply and 0.25  $\mu$ W using a +5-V supply.

The ADC128S102 is packaged in a 16-lead TSSOP package. Operation over the extended industrial temperature range of -40°C to +105°C is ensured.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |

|-------------|------------|-------------------|--|--|

| ADC128S102  | TSSOP (16) | 5.00 mm x 4.40 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

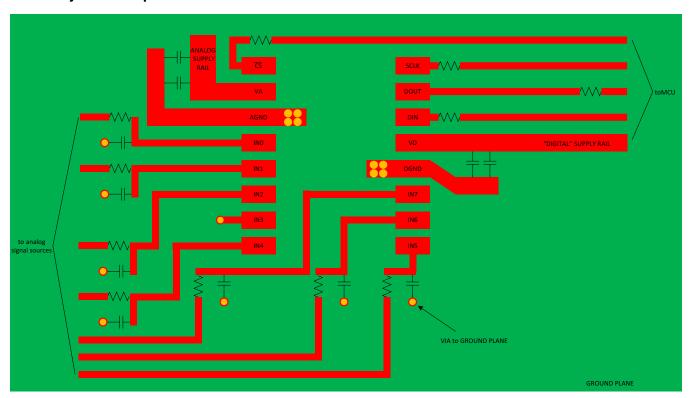

## Simplified Schematic

### **Table of Contents**

| 1 | Features 1                           |    | 7.4 Device Functional Modes                      | 10 |

|---|--------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                       |    | 7.5 Programming                                  | 10 |

| 3 | Description 1                        | 8  | Application and Implementation                   | 18 |

| 4 | Revision History2                    |    | 8.1 Application Information                      | 18 |

| 5 | Pin Configuration and Functions3     |    | 8.2 Typical Application                          | 18 |

| 6 | Specifications4                      | 9  | Power Supply Recommendations                     | 20 |

| • | 6.1 Absolute Maximum Ratings         |    | 9.1 Power Supply Sequence                        | 20 |

|   | 6.2 ESD Ratings                      |    | 9.2 Power Supply Noise Considerations            | 20 |

|   | 6.3 Recommended Operating Conditions | 10 | Layout                                           | 20 |

|   | 6.4 Thermal Information              |    | 10.1 Layout Guidelines                           | 20 |

|   | 6.5 Electrical Characteristics       |    | 10.2 Layout Example                              | 2  |

|   | 6.6 Timing Specifications 7          | 11 | Device and Documentation Support                 | 22 |

|   | 6.7 Typical Characteristics          |    | 11.1 Device Support                              | 2  |

| 7 | Detailed Description 14              |    | 11.2 Trademarks                                  | 2  |

| - | 7.1 Overview                         |    | 11.3 Electrostatic Discharge Caution             | 23 |

|   | 7.2 Functional Block Diagram         |    | 11.4 Glossary                                    | 23 |

|   | 7.3 Feature Description              | 12 | Mechanical, Packaging, and Orderable Information | 23 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision F (May 2013) to Revision G

**Page**

## Changes from Revision D (March 2013) to Revision E

Page

# 5 Pin Configuration and Functions

### **Pin Functions**

| PIN                                                                                     |                | 1/0                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                                                                                     | NAME           | I/O                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                   |

| 3                                                                                       | AGND           | Supply                                                                                                            | The ground return for the analog supply and signals.                                                                                                                                                                                                          |

| 1                                                                                       | CS             | IN                                                                                                                | Chip select. On the falling edge of $\overline{CS}$ , a conversion process begins. Conversions continue as long as $\overline{CS}$ is held low.                                                                                                               |

| 12                                                                                      | DGND           | Supply                                                                                                            | The ground return for the digital supply and signals.                                                                                                                                                                                                         |

| 14 DIN IN Digital data input. The ADC128S102's Control Register is loaded the SCLK pin. |                | Digital data input. The ADC128S102's Control Register is loaded through this pin on rising edges of the SCLK pin. |                                                                                                                                                                                                                                                               |

| 15                                                                                      | DOUT           | OUT                                                                                                               | Digital data output. The output samples are clocked out of this pin on the falling edges of the SCLK pin.                                                                                                                                                     |

| 4 - 11                                                                                  | IN0 to IN7     | IN                                                                                                                | Analog inputs. These signals can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                         |

| 16                                                                                      | SCLK           | IN                                                                                                                | Digital clock input. The ensured performance range of frequencies for this input is 8 MHz to 16 MHz. This clock directly controls the conversion and readout processes.                                                                                       |

| 2                                                                                       | V <sub>A</sub> | Supply                                                                                                            | Positive analog supply pin. This voltage is also used as the reference voltage. This pin should be connected to a quiet +2.7-V to +5.25-V source and bypassed to GND with 1-μF and 0.1-μF monolithic ceramic capacitors located within 1 cm of the power pin. |

| 13                                                                                      | V <sub>D</sub> | Supply                                                                                                            | Positive digital supply pin. This pin should be connected to a $+2.7$ V to $V_A$ supply, and bypassed to GND with a $0.1$ - $\mu$ F monolithic ceramic capacitor located within 1 cm of the power pin.                                                        |

Copyright © 2005–2015, Texas Instruments Incorporated

## 6 Specifications

### 6.1 Absolute Maximum Ratings

See (1)(2).

|                                                                            | MIN  | MAX                   | UNIT |  |  |  |

|----------------------------------------------------------------------------|------|-----------------------|------|--|--|--|

| Analog Supply Voltage V <sub>A</sub>                                       | -0.3 | 6.5                   | V    |  |  |  |

| Digital Supply Voltage V <sub>D</sub>                                      | -0.3 | $V_A + 0.3$ , max 6.5 | ٧    |  |  |  |

| Voltage on Any Pin to GND                                                  | -0.3 | V <sub>A</sub> +0.3   | V    |  |  |  |

| Input Current at Any Pin (3)                                               | -10  | 10                    | mA   |  |  |  |

| Package Input Current <sup>(3)</sup>                                       | -20  | 20                    | mA   |  |  |  |

| Power Dissipation at T <sub>A</sub> = 25°C                                 |      | See (4)               |      |  |  |  |

| Junction Temperature                                                       |      | 150                   | °C   |  |  |  |

| Storage temperature, T <sub>stg</sub>                                      | -65  | 150                   | °C   |  |  |  |

| For soldering specifications: see product folder at www.ti.com and SNOA549 |      |                       |      |  |  |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

## 6.2 ESD Ratings

|                    |                         |                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Flootrostatio discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2500 | V    |

|                    | Electrostatic discharge | Machine model (MM)                                     | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                                       | MIN | MAX     | UNIT |

|---------------------------------------|-----|---------|------|

| Operating Temperature, T <sub>A</sub> | -40 | 105     | °C   |

| V <sub>A</sub> Supply Voltage         | 2.7 | 5.25    | V    |

| V <sub>D</sub> Supply Voltage         | 2.7 | $V_{A}$ | V    |

| Digital Input Voltage                 | 0   | $V_{A}$ | V    |

| Analog Input Voltage                  | 0   | $V_A$   | V    |

| Clock Frequency                       | 8   | 16      | MHz  |

(1) All voltages are measured with respect to GND = 0V, unless otherwise specified.

<sup>(3)</sup> When the input voltage at any pin exceeds the power supplies (that is, V<sub>IN</sub> < AGND or V<sub>IN</sub> > V<sub>A</sub> or V<sub>D</sub>), the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two.

<sup>(4)</sup> The absolute maximum junction temperature (T<sub>J</sub>max) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>J</sub>max, the junction-to-ambient thermal resistance (θ<sub>JA</sub>), and the ambient temperature (T<sub>A</sub>), and can be calculated using the formula P<sub>D</sub>MAX = (T<sub>J</sub>max - T<sub>A</sub>)/θ<sub>JA</sub>. In the 16-pin TSSOP, θ<sub>JA</sub> is 96°C/W, so P<sub>D</sub>MAX = 1,200 mW at 25°C and 625 mW at the maximum operating ambient temperature of 105°C. Note that the power consumption of this device under normal operation is a maximum of 12 mW. The values for maximum power dissipation listed above will be reached only when the ADC128S102 is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Obviously, such conditions should always be avoided.

### 6.4 Thermal Information

|                      |                                              | ADC128S102 |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PW         | UNIT |

|                      |                                              | 16 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 110        |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 42         |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 56         | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 5          |      |

| ΨЈВ                  | Junction-to-board characterization parameter | 55         |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

The following specifications apply for  $T_A$  = 25°C, AGND = DGND = 0 V,  $f_{SCLK}$  = 8 MHz to 16 MHz,  $f_{SAMPLE}$  = 500 ksps to 1 MSPS,  $C_L$  = 50pF, unless otherwise noted. MIN and MAX limits apply for  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ .

|                  | PARAMETER                         | TEST CONDITIONS                                                             | MIN  | TYP  | MAX <sup>(2)</sup> | UNIT |

|------------------|-----------------------------------|-----------------------------------------------------------------------------|------|------|--------------------|------|

| STATIC           | CONVERTER CHARACTERISTICS         |                                                                             | Ti.  |      | ,                  |      |

|                  | Resolution with No Missing Codes  |                                                                             |      |      | 12                 | Bits |

| INII             | Integral Non-Linearity (End Point | $V_A = V_D = +3.0V$                                                         | -1   | ±0.4 | 1                  | LSB  |

| INL              | Method)                           | $V_A = V_D = +5.0V$                                                         | -1.2 | ±0.5 | 1.2                | LSB  |

|                  |                                   | $V_{\Delta} = V_{D} = +3.0V$                                                |      | +0.4 | 0.9                | LSB  |

| DNL              | Differential Non-Linearity        | VA = VD = +3.0V                                                             | -0.7 | -0.2 |                    | LSB  |

| DINL             | Differential Non-Linearity        | $V_{A} = V_{D} = +5.0V$                                                     |      | +0.7 | 1.5                | LSB  |

|                  |                                   | VA - VD - +3.0V                                                             | -0.9 | -0.4 |                    | LSB  |

| V <sub>OFF</sub> | Offset Error                      | $V_A = V_D = +3.0V$                                                         | -2.3 | +0.8 | 2.3                | LSB  |

| VOFF             | Oliset Elloi                      | $V_A = V_D = +5.0V$                                                         | -2.3 | +1.1 | 2.3                | LSB  |

| OEM              | Offset Error Match                | $V_A = V_D = +3.0V$                                                         | -1.5 | ±0.1 | 1.5                | LSB  |

| OLIVI            |                                   | $V_A = V_D = +5.0V$                                                         | -1.5 | ±0.3 | 1.5                | LSB  |

| FSE              | Full Scale Error                  | $V_A = V_D = +3.0V$                                                         | -2.0 | +0.8 | 2.0                | LSB  |

| 1 JL             | Tuli Scale Lift                   | $V_A = V_D = +5.0V$                                                         | -2.0 | +0.3 | 2.0                | LSB  |

| FSEM             | Full Scale Error Match            | $V_A = V_D = +3.0V$                                                         | -1.5 | ±0.1 | 1.5                | LSB  |

| 1 OLIVI          | Tuli Scale Lifti Match            | $V_A = V_D = +5.0V$                                                         | -1.5 | ±0.3 | 1.5                | LSB  |

| DYNAMI           | IC CONVERTER CHARACTERISTIC       | cs                                                                          |      |      |                    |      |

| FPBW             | Full Power Bandwidth (-3dB)       | $V_A = V_D = +3.0V$                                                         |      | 8    |                    | MHz  |

| I I DVV          | Tull Tower Ballawidth ( 3db)      | $V_A = V_D = +5.0V$                                                         |      | 11   |                    | MHz  |

| SINAD            | Signal-to-Noise Plus Distortion   | $V_A = V_D = +3.0V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , $-0.02 \text{ dBFS}$ | 70   | 73   |                    | dB   |

| SINAD            | Ratio                             | $V_A = V_D = +5.0V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , $-0.02 \text{ dBFS}$ | 70   | 73   |                    | dB   |

| SNR              | Signal to Naigo Patia             | $V_A = V_D = +3.0V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , $-0.02 \text{ dBFS}$ | 70.8 | 73   |                    | dB   |

| SINK             | Signal-to-Noise Ratio             | $V_A = V_D = +5.0V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , $-0.02 \text{ dBFS}$ | 70.8 | 73   |                    | dB   |

| THD              | Total Harmonic Distortion         | $V_A = V_D = +3.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$     |      | -88  | -74                | dB   |

| וחט              | Total Harmonic Distortion         | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$     |      | -90  | -74                | dB   |

<sup>(1)</sup> Data sheet min/max specification limits are ensured by design, test, or statistical analysis.

Copyright © 2005–2015, Texas Instruments Incorporated

<sup>(2)</sup> Tested limits are specified to TI's AOQL (Average Outgoing Quality Level).

# **Electrical Characteristics (continued)**

The following specifications apply for  $T_A$  = 25°C, AGND = DGND = 0 V,  $f_{SCLK}$  = 8 MHz to 16 MHz,  $f_{SAMPLE}$  = 500 ksps to 1 MSPS,  $C_L$  = 50pF, unless otherwise noted. MIN and MAX limits apply for  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ .

|                                     | PARAMETER                                         | TEST CONDITIONS  TEST CONDITIONS                                                               | MIN                  | TYP                 | MAX <sup>(2)</sup> | UNIT |

|-------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------|---------------------|--------------------|------|

| SFDR                                |                                                   | $V_A = V_D = +3.0V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , $-0.02 \text{ dBFS}$                    | 75                   | 91                  |                    | dB   |

| SFDN                                | Spurious-Free Dynamic Range                       | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$                        | 75                   | 92                  |                    | dB   |

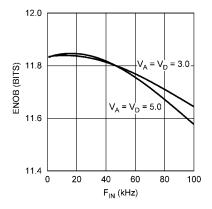

| ENOB                                | Effective Number of Bits                          | $\begin{split} V_A &= V_D = +3.0V, \\ f_{IN} &= 40.2 \text{ kHz} \end{split}$                  | 11.3                 | 11.8                |                    | Bits |

| LNOB                                | Ellective Number of Bits                          | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$                        | 11.3                 | 11.8                |                    | Bits |

| ISO                                 | Channel-to-Channel Isolation                      | $\begin{split} V_A &= V_D = +3.0V, \\ f_{IN} &= 20 \text{ kHz} \end{split}$                    |                      | 82                  |                    | dB   |

| 130                                 | Charmer-to-Charmer isolation                      | $V_A = V_D = +5.0V$ ,<br>$f_{IN} = 20 \text{ kHz}$ , $-0.02 \text{ dBFS}$                      |                      | 84                  |                    | dB   |

|                                     | Intermodulation Distortion,                       | $V_A = V_D = +3.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$                       |                      | -89                 |                    | dB   |

| IMD                                 | Second Order Terms                                | $V_A = V_D = +5.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$                       |                      | -91                 |                    | dB   |

| INID                                | Intermodulation Distortion, Third Order Terms     | $V_A = V_D = +3.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$                       |                      | -88                 |                    | dB   |

|                                     |                                                   | $V_A = V_D = +5.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$                       |                      | -88                 |                    | dB   |

| ANALOG                              | INPUT CHARACTERISTICS                             | -                                                                                              |                      |                     |                    |      |

| $V_{IN}$                            | Input Range                                       |                                                                                                |                      | 0 to $V_{\text{A}}$ |                    | V    |

| $I_{DCL}$                           | DC Leakage Current                                |                                                                                                | -1                   |                     | 1                  | μΑ   |

| C <sub>INA</sub> Input Capacitance  |                                                   | Track Mode                                                                                     |                      | 33                  |                    | pF   |

|                                     |                                                   | Hold Mode                                                                                      |                      | 3                   |                    | pF   |

| DIGITAL                             | INPUT CHARACTERISTICS                             |                                                                                                | ·                    |                     | · ·                |      |

| M                                   | Innut I ligh Voltage                              | $V_A = V_D = +2.7V \text{ to } +3.6V$                                                          | 2.1                  |                     |                    | V    |

| $V_{IH}$                            | Input High Voltage                                | $V_A = V_D = +4.75V \text{ to } +5.25V$                                                        | 2.4                  |                     |                    | V    |

| V <sub>IL</sub>                     | Input Low Voltage                                 | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                         |                      |                     | 8.0                | V    |

| I <sub>IN</sub>                     | Input Current                                     | $V_{IN} = 0V \text{ or } V_D$                                                                  | -1                   | ±0.01               | 1                  | μΑ   |

| C <sub>IND</sub>                    | Digital Input Capacitance                         |                                                                                                |                      | 2                   | 4                  | pF   |

| DIGITAL                             | OUTPUT CHARACTERISTICS                            |                                                                                                | •                    |                     | · ·                |      |

| V <sub>OH</sub>                     | Output High Voltage                               | $I_{SOURCE} = 200 \ \mu A, \ V_A = V_D = +2.7 V \ to \ +5.25 V$                                | V <sub>D</sub> - 0.5 |                     |                    | V    |

| V <sub>OL</sub>                     | Output Low Voltage                                | $I_{SINK} = 200 \mu A \text{ to } 1.0 \text{ mA},$<br>$V_A = V_D = +2.7 V \text{ to } +5.25 V$ |                      |                     | 0.4                | V    |

| I <sub>OZH</sub> , I <sub>OZL</sub> | Hi-Impedance Output Leakage<br>Current            | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                         | -1                   |                     | 1                  | μΑ   |

| C <sub>OUT</sub>                    | Hi-Impedance Output<br>Capacitance <sup>(1)</sup> |                                                                                                |                      | 2                   | 4                  | pF   |

|                                     | Output Coding                                     |                                                                                                | Stra                 | ight (Natura        | al) Binary         |      |

| POWER S                             | SUPPLY CHARACTERISTICS (C <sub>L</sub>            | = 10 pF)                                                                                       |                      |                     |                    |      |

| $V_A, V_D$                          | Analog and Digital Supply<br>Voltages             | $V_A \ge V_D$                                                                                  | 2.7                  |                     | 5.25               | V    |

Submit Documentation Feedback

Copyright © 2005–2015, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

The following specifications apply for  $T_A$  = 25°C, AGND = DGND = 0 V,  $f_{SCLK}$  = 8 MHz to 16 MHz,  $f_{SAMPLE}$  = 500 ksps to 1 MSPS,  $C_L$  = 50pF, unless otherwise noted. MIN and MAX limits apply for  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ .

|                                 | PARAMETER                                    | TEST CONDITIONS                                                                                  | MIN | TYP  | MAX <sup>(2)</sup> | UNIT        |

|---------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|--------------------|-------------|

|                                 | Total Supply Current                         | $V_A = V_D = +2.7V \text{ to } +3.6V,$<br>$f_{SAMPLE} = 1 \text{ MSPS}, f_{IN} = 40 \text{ kHz}$ |     | 0.76 | 1.5                | mA          |

| I <sub>A</sub> + I <sub>D</sub> | Normal Mode ( CS low)                        | $V_A = V_D = +4.75V$ to +5.25V,<br>$f_{SAMPLE} = 1$ MSPS, $f_{IN} = 40$ kHz                      |     | 2.13 | 3.1                | mA          |

| ıA + ıD                         | Total Supply Current                         | $V_A = V_D = +2.7V$ to $+3.6V$ , $f_{SCLK} = 0$ ksps                                             |     | 20   |                    | nA          |

|                                 | Shutdown Mode (CS high)                      | $V_A = V_D = +4.75V$ to +5.25V, $f_{SCLK} = 0$ ksps                                              |     | 50   |                    | nA          |

|                                 | Power Consumption                            | $V_A = V_D = +3.0V$<br>$f_{SAMPLE} = 1$ MSPS, $f_{IN} = 40$ kHz                                  |     | 2.3  | 4.5                | mW          |

| P <sub>C</sub>                  | Normal Mode ( $\overline{\text{CS}}$ low)    | $V_A = V_D = +5.0V$<br>$f_{SAMPLE} = 1$ MSPS, $f_{IN} = 40$ kHz                                  |     | 10.7 | 15.5               | mW          |

| r.C                             | Power Consumption<br>Shutdown Mode (CS high) | $V_A = V_D = +3.0V$<br>$f_{SCLK} = 0$ ksps                                                       |     | 0.06 |                    | μW          |

|                                 |                                              | $V_A = V_D = +5.0V$<br>$f_{SCLK} = 0$ ksps                                                       |     | 0.25 |                    | μW          |

| AC ELEC                         | TRICAL CHARACTERISTICS                       |                                                                                                  |     |      |                    |             |

| f <sub>SCLK</sub> MIN           | Minimum Clock Frequency                      | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           | 8   | 0.8  |                    | MHz         |

| f <sub>SCLK</sub>               | Maximum Clock Frequency                      | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           |     |      | 16                 | MHz         |

|                                 | Sample Rate                                  | V V 0.7V 5.05V                                                                                   | 500 | 50   |                    | ksps        |

| $f_S$                           | Continuous Mode                              | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           |     |      | 1                  | MSPS        |

| t <sub>CONVERT</sub>            | Conversion (Hold) Time                       | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           |     |      | 13                 | SCLK cycles |

| DC                              | CCLK Duty Cycle                              | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           | 40% | 30   |                    |             |

| DC                              | SCLK Duty Cycle                              | $V_A = V_D = +2.7 V (0.+3.23 V)$                                                                 |     | 70   | 60%                |             |

| t <sub>ACQ</sub>                | Acquisition (Track) Time                     | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           |     |      | 3                  | SCLK cycles |

|                                 | Throughput Time                              | Acquisition Time + Conversion Time $V_A = V_D = +2.7V$ to $+5.25V$                               |     |      | 16                 | SCLK cycles |

| t <sub>AD</sub>                 | Aperture Delay                               | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                           |     | 4    |                    | ns          |

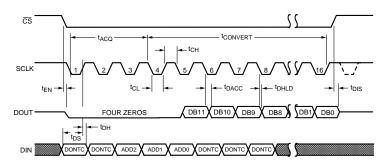

## 6.6 Timing Specifications

The following specifications apply for  $T_A$  = 25°C,  $V_A$  =  $V_D$  = +2.7V to +5.25V, AGND = DGND = 0V,  $f_{SCLK}$  = 8 MHz to 16 MHz,  $f_{SAMPLE}$  = 500 ksps to 1 MSPS, and  $C_L$  = 50pF. MIN and MAX apply for  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ .

|                   | PARAMETER                                | TEST CONDITIONS | MIN                        | TYP | MAX <sup>(1)</sup> | UNIT |

|-------------------|------------------------------------------|-----------------|----------------------------|-----|--------------------|------|

| t <sub>CSH</sub>  | CS Hold Time after SCLK Rising Edge      |                 | 10                         | 0   |                    | ns   |

| t <sub>CSS</sub>  | CS Setup Time prior to SCLK Rising Edge  |                 | 10                         | 4.5 |                    | ns   |

| t <sub>EN</sub>   | CS Falling Edge to DOUT enabled          |                 |                            | 5   | 30                 | ns   |

| t <sub>DACC</sub> | DOUT Access Time after SCLK Falling Edge |                 |                            | 17  | 27                 | ns   |

| t <sub>DHLD</sub> | DOUT Hold Time after SCLK Falling Edge   |                 |                            | 4   |                    | ns   |

| t <sub>DS</sub>   | DIN Setup Time prior to SCLK Rising Edge |                 | 10                         | 3   |                    | ns   |

| $t_{DH}$          | DIN Hold Time after SCLK Rising Edge     |                 | 10                         | 3   |                    | ns   |

| t <sub>CH</sub>   | SCLK High Time                           |                 | 0.4 x<br>t <sub>SCLK</sub> |     |                    | ns   |

| t <sub>CL</sub>   | SCLK Low Time                            |                 | 0.4 x<br>t <sub>SCLK</sub> |     |                    | ns   |

|                   | CC Diging Edge to DOLIT High Impedance   | DOUT falling    |                            | 2.4 | 20                 | ns   |

| t <sub>DIS</sub>  | CS Rising Edge to DOUT High-Impedance    | DOUT rising     |                            | 0.9 | 20                 | ns   |

<sup>(1)</sup> Tested limits are specified to TI's AOQL (Average Outgoing Quality Level).

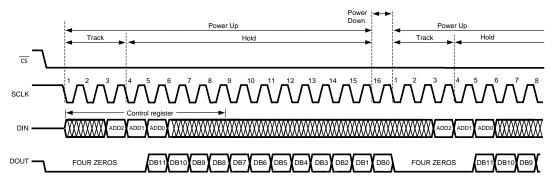

Figure 1. ADC128S102 Operational Timing Diagram

Figure 2. ADC128S102 Serial Timing Diagram

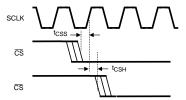

Figure 3. SCLK and CS Timing Parameters

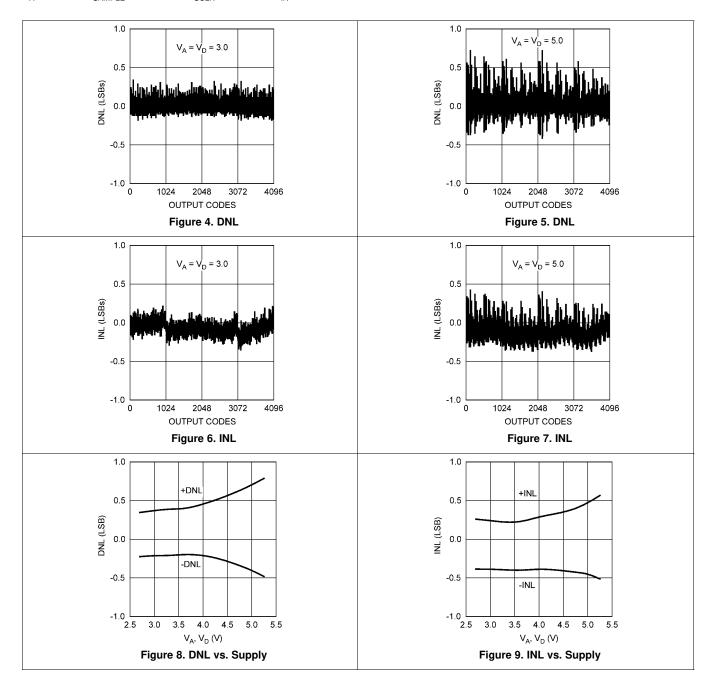

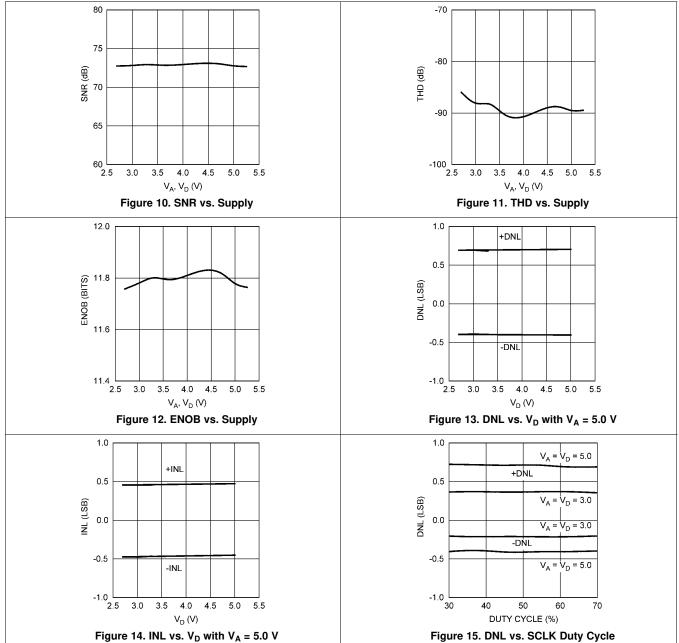

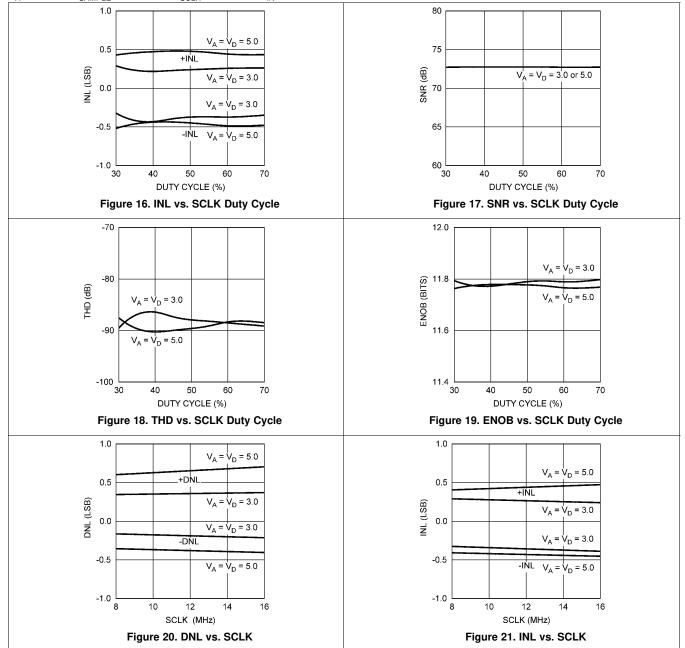

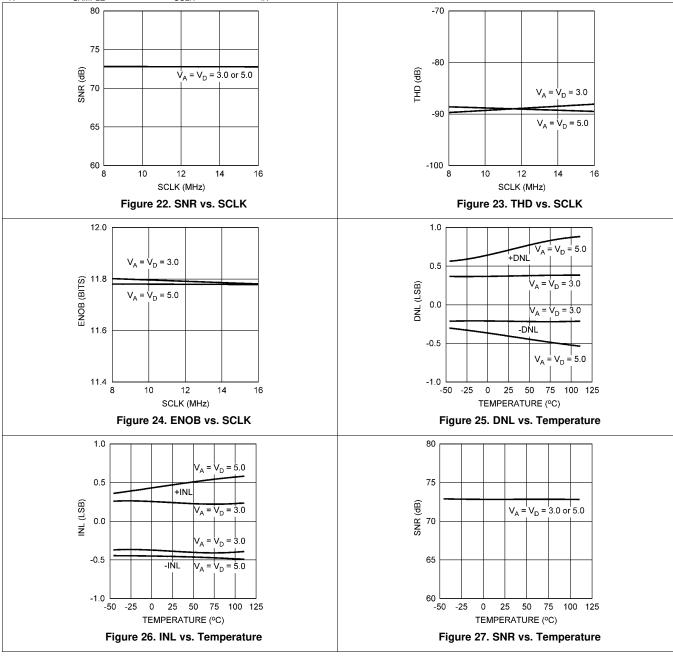

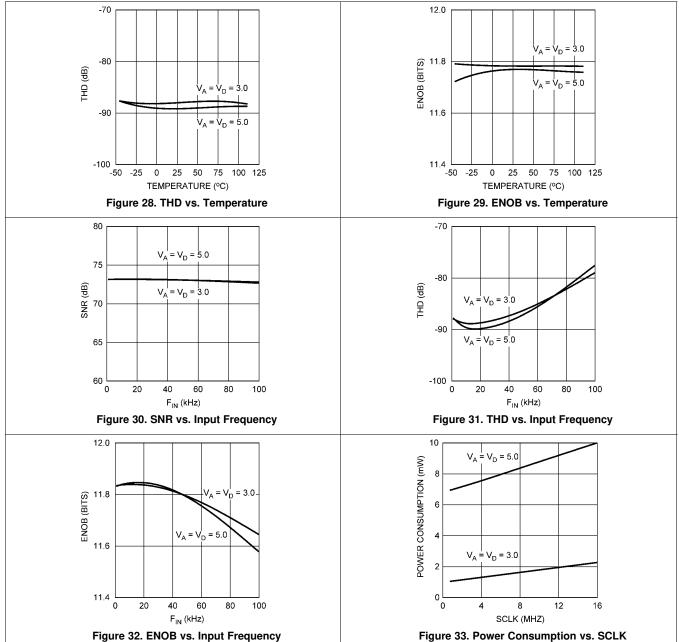

## 6.7 Typical Characteristics

$T_A$  = +25°C,  $f_{SAMPLE}$  = 1 MSPS,  $f_{SCLK}$  = 16 MHz,  $f_{IN}$  = 40.2 kHz unless otherwise stated.

## 7 Detailed Description

#### 7.1 Overview

The ADC128S102 is a successive-approximation analog-to-digital converter designed around a charge-redistribution digital-to-analog converter.

## 7.2 Functional Block Diagram

### 7.3 Feature Description

## 7.3.1 ADC128S102 Operation

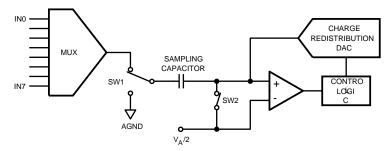

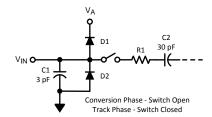

Simplified schematics of the ADC128S102 in both track and hold operation are shown in Figure 34 and Figure 35 respectively. In Figure 34, the ADC128S102 is in track mode: switch SW1 connects the sampling capacitor to one of eight analog input channels through the multiplexer, and SW2 balances the comparator inputs. The ADC128S102 is in this state for the first three SCLK cycles after  $\overline{\text{CS}}$  is brought low.

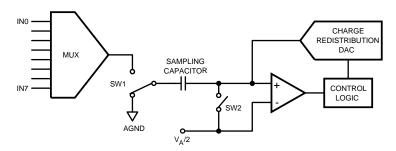

Figure 35 shows the ADC128S102 in hold mode: switch SW1 connects the sampling capacitor to ground, maintaining the sampled voltage, and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge to or from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is the digital representation of the analog input voltage. The ADC128S102 is in this state for the last thirteen SCLK cycles after  $\overline{\text{CS}}$  is brought low.

Figure 34. ADC128S102 in Track Mode

### Feature Description (continued)

Figure 35. ADC128S102 in Hold Mode

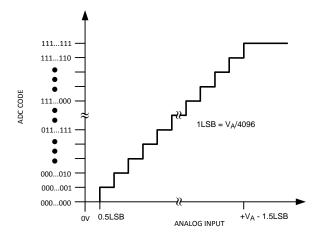

#### 7.3.2 ADC128S102 Transfer Function

The output format of the ADC128S102 is straight binary. Code transitions occur midway between successive integer LSB values. The LSB width for the ADC128S102 is V<sub>A</sub> / 4096. The ideal transfer characteristic is shown in Figure 36. The transition from an output code of 0000 0000 0000 to a code of 0000 0000 0001 is at 1/2 LSB, or a voltage of V<sub>A</sub> / 8192. Other code transitions occur at steps of one LSB.

Figure 36. Ideal Transfer Characteristic

#### 7.3.3 Analog Inputs

An equivalent circuit for one of the ADC128S102's input channels is shown in Figure 37. Diodes D1 and D2 provide ESD protection for the analog inputs. The operating range for the analog inputs is 0 V to V<sub>A</sub>. Going beyond this range will cause the ESD diodes to conduct and result in erratic operation.

The capacitor C1 in Figure 37 has a typical value of 3 pF and is mainly the package pin capacitance. Resistor R1 is the on resistance of the multiplexer and track / hold switch and is typically 500 ohms. Capacitor C2 is the ADC128S102 sampling capacitor, and is typically 30 pF. The ADC128S102 will deliver best performance when driven by a low-impedance source (less than 100 ohms). This is especially important when using the ADC128S102 to sample dynamic signals. Also important when sampling dynamic signals is a band-pass or lowpass filter which reduces harmonics and noise in the input. These filters are often referred to as anti-aliasing filters.

Copyright © 2005-2015, Texas Instruments Incorporated Submit Documentation Feedback

## Feature Description (continued)

Figure 37. Equivalent Input Circuit

## 7.3.4 Digital Inputs and Outputs

The ADC128S102's digital inputs (SCLK,  $\overline{CS}$ , and DIN) have an operating range of 0 V to V<sub>A</sub>. They are not prone to latch-up and may be asserted before the digital supply (V<sub>D</sub>) without any risk. The digital output (DOUT) operating range is controlled by V<sub>D</sub>. The output high voltage is V<sub>D</sub> - 0.5V (min) while the output low voltage is 0.4V (max).

#### 7.4 Device Functional Modes

The ADC128S102 is fully powered-up whenever  $\overline{CS}$  is low and fully powered-down whenever  $\overline{CS}$  is high, with one exception. If operating in continuous conversion mode, the ADC128S102 automatically enters power-down mode between SCLK's 16th falling edge of a conversion and SCLK's 1st falling edge of the subsequent conversion (see Figure 1).

In continuous conversion mode, the ADC128S102 can perform multiple conversions back to back. Each conversion requires 16 SCLK cycles and the ADC128S102 will perform conversions continuously as long as  $\overline{\text{CS}}$  is held low. Continuous mode offers maximum throughput.

In burst mode, the user may trade off throughput for power consumption by performing fewer conversions per unit time. This means spending more time in power-down mode and less time in normal mode. By utilizing this technique, the user can achieve very low sample rates while still utilizing an SCLK frequency within the electrical specifications. The Power Consumption vs. SCLK curve in the *Typical Characteristics* section shows the typical power consumption of the ADC128S102. To calculate the power consumption ( $P_C$ ), simply multiply the fraction of time spent in the normal mode ( $P_C$ ) by the normal mode power consumption ( $P_C$ ), and add the fraction of time spent in shutdown mode ( $P_C$ ) multiplied by the shutdown mode power consumption ( $P_C$ ) as shown in Equation 1.

$$P_{C} = \frac{t_{N}}{t_{N} + t_{S}} \times P_{N} + \frac{t_{S}}{t_{N} + t_{S}} \times P_{S}$$

(1)

### 7.5 Programming

## 7.5.1 Serial Interface

An operational timing diagram and a serial interface timing diagram for the ADC128S102 are shown in the *Timing Specifications* section. CS, chip select, initiates conversions and frames the serial data transfers. SCLK (serial clock) controls both the conversion process and the timing of serial data. DOUT is the serial data output pin, where a conversion result is sent as a serial data stream, MSB first. Data to be written to the ADC128S102's Control Register is placed on DIN, the serial data input pin. New data is written to DIN with each conversion.

A serial frame is initiated on the falling edge of  $\overline{CS}$  and ends on the rising edge of  $\overline{CS}$ . Each frame must contain an integer multiple of 16 rising SCLK edges. The ADC's DOUT pin is in a high impedance state when  $\overline{CS}$  is high and is active when  $\overline{CS}$  is low. Thus,  $\overline{CS}$  acts as an output enable. Similarly, SCLK is internally gated off when  $\overline{CS}$  is brought high.

## Programming (continued)

During the first 3 cycles of SCLK, the ADC is in the track mode, acquiring the input voltage. For the next 13 SCLK cycles the conversion is accomplished and the data is clocked out. SCLK falling edges 1 through 4 clock out leading zeros while falling edges 5 through 16 clock out the conversion result, MSB first. If there is more than one conversion in a frame (continuous conversion mode), the ADC will re-enter the track mode on the falling edge of SCLK after the N\*16th rising edge of SCLK and re-enter the hold/convert mode on the N\*16+4th falling edge of SCLK. "N" is an integer value.

The ADC128S102 enters track mode under three different conditions. In Figure 1,  $\overline{CS}$  goes low with SCLK high and the ADC enters track mode on the first falling edge of SCLK. In the second condition,  $\overline{CS}$  goes low with SCLK low. Under this condition, the ADC automatically enters track mode and the falling edge of  $\overline{CS}$  is seen as the first falling edge of SCLK. In the third condition,  $\overline{CS}$  and SCLK go low simultaneously and the ADC enters track mode. While there is no timing restriction with respect to the rising edges of  $\overline{CS}$  and SCLK, see Figure 3 for setup and hold time requirements for the falling edge of  $\overline{CS}$  with respect to the rising edge of SCLK.

While a conversion is in progress, the address of the next input for conversion is clocked into a control register through the DIN pin on the first 8 rising edges of SCLK after the fall of  $\overline{CS}$ . See Table 1, Table 2, and Table 3.

There is no need to incorporate a power-up delay or dummy conversions as the ADC128S102 is able to acquire the input signal to full resolution in the first conversion immediately following power-up. The first conversion result after power-up will be that of IN0.

**Table 1. Control Register Bits**

| Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| DONTC       | DONTC | ADD2  | ADD1  | ADD0  | DONTC | DONTC | DONTC |

### **Table 2. Control Register Bit Descriptions**

| Bit No:       | Symbol: | Description                                                                              |

|---------------|---------|------------------------------------------------------------------------------------------|

| 7, 6, 2, 1, 0 | DONTC   | Don't care. The values of these bits do not affect the device.                           |

| 5             | ADD2    | These three bits determine which input channel will be sampled and converted at the next |

| 4             | ADD1    | conversion cycle. The mapping between codes and channels is shown in Table 3.            |

| 3             | ADD0    |                                                                                          |

#### **Table 3. Input Channel Selection**

| ADD2 | ADD1 | ADD0 | Input Channel |

|------|------|------|---------------|

| 0    | 0    | 0    | IN0 (Default) |

| 0    | 0    | 1    | IN1           |

| 0    | 1    | 0    | IN2           |

| 0    | 1    | 1    | IN3           |

| 1    | 0    | 0    | IN4           |

| 1    | 0    | 1    | IN5           |

| 1    | 1    | 0    | IN6           |

| 1    | 1    | 1    | IN7           |

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

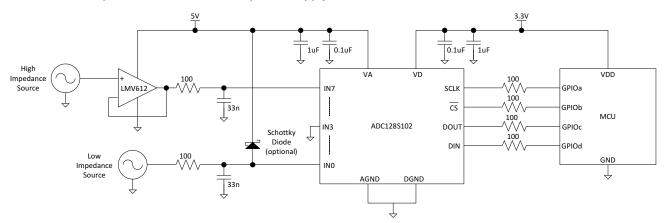

The ADC128S102 is a successive-approximation analog-to-digital converter designed around a charge-redistribution digital-to-analog converter. Since the ADC128S102 integrates an 8 to 1 MUX on the front end, the device is typically used in applications where multiple voltages need to be monitored. In addition to having 8 input channels, the ADC128S102 can operate at sampling rates up to 1 MSPS. As a result, the ADC128S102 is typically run in burst fashion where a voltage is sampled for several times and then the ADC128S102 can be powered-down. This is a common technique for applications that are power limited. Due to the high bandwidth and sampling rate, the ADC128S102 is suitable for monitoring AC waveforms as well as DC inputs. The following example shows a common configuration for monitoring AC inputs.

## 8.2 Typical Application

The following sections outline the design principles of data acquisition system based on the ADC128S102.

A typical application is shown in Figure 38. The analog supply is bypassed with a capacitor network located close to the ADC128S102. The ADC128S102 uses the analog supply  $(V_A)$  as its reference voltage, so it is very important that  $V_A$  be kept as clean as possible. Due to the low power requirements of the ADC128S102, it is also possible to use a precision reference as a power supply.

Figure 38. Typical Application Circuit

#### 8.2.1 Design Requirements

A positive supply only data acquisition system capable of digitizing signals ranging 0 to 5 V, BW = 10 kHz, and a throughput of 125 kSPS.

The ADC128S102 has to interface to an MCU whose supply is set at 3.3 V.

## 8.2.2 Detailed Design Procedure

The signal range requirement forces the design to use 5-V analog supply at VA, analog supply. This follows from the fact that VA is also a reference potential for the ADC.

The requirement of interfacing to the MCU which is powered by 3.3-V supply, forces the choice of 3.3-V as a VD supply.

Sampling is in fact a modulation process which may result in aliasing of the input signal, if the input signal is not adequately band limited. The maximum sampling rate of the ADC128S102 when all channels are enabled is, Fs:

## Typical Application (continued)

$$F_s = \frac{F_{SCLK}}{16 \times 8} \tag{2}$$

Note that faster sampling rates can be achieved when fewer channels are sampled. Single channel can be sampled at the maximum rate of:

$$F_{s\_single} = \frac{F_{SCLK}}{16} \tag{3}$$

In order to avoid the aliasing the Nyquist criterion has to be met:

$$BW_{signal} < \frac{F_s}{2} \tag{4}$$

Therefore it is necessary to place anti-aliasing filters at all inputs of the ADC. These filters may be single pole low pass filters whose pole location has to satisfy, assuming all channels sampled in sequence:

$$\frac{1}{\pi \times R \times C} < \frac{F_{\text{SCLK}}}{16 \times 8} \tag{5}$$

$$R \times C \ge \frac{128}{\pi \times F_{SCLK}} \tag{6}$$

With Fsclk = 16 MHz, a good choice for the single pole filter is:

- R = 100

- C = 33 nF

This reduces the input BW<sub>signal</sub> = 48 kHz. The capacitor at the INx input of the device provides not only the filtering of the input signal, but it also absorbs the charge kick-back from the ADC. The kick-back is the result of the internal switches opening at the end of the acquisition period.

The VA and VD sources are already separated in this example, due to the design requirements. This also benefits the overall performance of the ADC, as the potentially noisy VD supply does not contaminate the VA. In the same vain, further consideration could be given to the SPI interface, especially when the master MCU is capable of producing fast rising edges on the digital bus signals. Inserting small resistances in the digital signal path may help in reducing the ground bounce, and thus improve the overall noise performance of the system.

Care should be taken when the signal source is capable of producing voltages beyond VA. In such instances the internal ESD diodes may start conducting. The ESD diodes are not intended as input signal clamps. To provide the desired clamping action use Schottky diodes as shown in Figure 38.

#### 8.2.3 Application Curve

Figure 39. Typical Performance

Copyright © 2005-2015, Texas Instruments Incorporated

Product Folder Links: ADC128S102

## 9 Power Supply Recommendations

There are three major power supply concerns with this product: power supply sequencing, power management, and the effect of digital supply noise on the analog supply.

### 9.1 Power Supply Sequence

The ADC128S102 is a dual-supply device. The two supply pins share ESD resources, so care must be exercised to ensure that the power is applied in the correct sequence. To avoid turning on the ESD diodes, the digital supply  $(V_D)$  cannot exceed the analog supply  $(V_A)$  by more than 300 mV. Therefore,  $V_A$  must ramp up before or concurrently with  $V_D$ .

## 9.2 Power Supply Noise Considerations

The charging of any output load capacitance requires current from the digital supply,  $V_D$ . The current pulses required from the supply to charge the output capacitance will cause voltage variations on the digital supply. If these variations are large enough, they could degrade SNR and SINAD performance of the ADC. Furthermore, if the analog and digital supplies are tied directly together, the noise on the digital supply will be coupled directly into the analog supply, causing greater performance degradation than would noise on the digital supply alone. Similarly, discharging the output capacitance when the digital output goes from a logic high to a logic low will dump current into the die substrate, which is resistive. Load discharge currents will cause "ground bounce" noise in the substrate that will degrade noise performance if that current is large enough. The larger the output capacitance, the more current flows through the die substrate and the greater the noise coupled into the analog channel.

The first solution to keeping digital noise out of the analog supply is to decouple the analog and digital supplies from each other or use separate supplies for them. To keep noise out of the digital supply, keep the output load capacitance as small as practical. If the load capacitance is greater than 50 pF, use a 100  $\Omega$  series resistor at the ADC output, located as close to the ADC output pin as practical. This will limit the charge and discharge current of the output capacitance and improve noise performance. Since the series resistor and the load capacitance form a low frequency pole, verify signal integrity once the series resistor has been added.

### 10 Layout

## 10.1 Layout Guidelines

Capacitive coupling between the noisy digital circuitry and the sensitive analog circuitry can lead to poor performance. The solution is to keep the analog circuitry separated from the digital circuitry and the clock line as short as possible.

Digital circuits create substantial supply and ground current transients. The logic noise generated could have significant impact upon system noise performance. To avoid performance degradation of the ADC128S102 due to supply noise, do not use the same supply for the ADC128S102 that is used for digital logic.

Generally, analog and digital lines should cross each other at 90° to avoid crosstalk. However, to maximize accuracy in high resolution systems, avoid crossing analog and digital lines altogether. It is important to keep clock lines as short as possible and isolated from ALL other lines, including other digital lines. In addition, the clock line should also be treated as a transmission line and be properly terminated.

The analog input should be isolated from noisy signal traces to avoid coupling of spurious signals into the input. Any external component (e.g., a filter capacitor) connected between the converter's input pins and ground or to the reference input pin and ground should be connected to a very clean point in the ground plane.

We recommend the use of a single, uniform ground plane and the use of split power planes. The power planes should be located within the same board layer. All analog circuitry (input amplifiers, filters, reference components, etc.) should be placed over the analog power plane. All digital circuitry and I/O lines should be placed over the digital power plane. Furthermore, all components in the reference circuitry and the input signal chain that are connected to ground should be connected together with short traces and enter the analog ground plane at a single, quiet point.

Submit Documentation Feedback

Copyright © 2005–2015, Texas Instruments Incorporated

# 10.2 Layout Example

Figure 40. Layout Schematic

(7)

## 11 Device and Documentation Support

## 11.1 Device Support

### 11.1.1 Specification Definitions

- **ACQUISITION TIME** is the time required for the ADC to acquire the input voltage. During this time, the hold capacitor is charged by the input voltage.

- **APERTURE DELAY** is the time between the fourth falling edge of SCLK and the time when the input signal is internally acquired or held for conversion.

- **CONVERSION TIME** is the time required, after the input voltage is acquired, for the ADC to convert the input voltage to a digital word.

- **CHANNEL-TO-CHANNEL ISOLATION** is resistance to coupling of energy from one channel into another channel.

- **CROSSTALK** is the coupling of energy from one channel into another channel. This is similar to Channel-to-Channel Isolation, except for the sign of the data.

- **DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

- **DUTY CYCLE** is the ratio of the time that a repetitive digital waveform is high to the total time of one period. The specification here refers to the SCLK.

- **EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion or SINAD. ENOB is defined as (SINAD 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

- **FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

- **FULL SCALE ERROR (FSE)** is a measure of how far the last code transition is from the ideal  $1\frac{1}{2}$  LSB below  $V_{REF}^+$  and is defined as:

$$V_{FSE} = V_{max} + 1.5 LSB - V_{REF}$$

where

- V<sub>max</sub> is the voltage at which the transition to the maximum code occurs.

- · FSE can be expressed in Volts, LSB or percent of full scale range.

**GAIN ERROR** is the deviation of the last code transition (111...110) to (111...111) from the ideal (V<sub>REF</sub> - 1.5 LSB), after adjusting for offset error.

- INTEGRAL NON-LINEARITY (INL) is a measure of the deviation of each individual code from a line drawn from negative full scale (½ LSB below the first code transition) through positive full scale (½ LSB above the last code transition). The deviation of any given code from this straight line is measured from the center of that code value.

- **INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to an individual ADC input at the same time. It is defined as the ratio of the power in both the second or the third order intermodulation products to the power in one of the original frequencies. Second order products are  $f_a \pm f_b$ , where  $f_a$  and  $f_b$  are the two sine wave input frequencies. Third order products are  $(2f_a \pm f_b)$  and  $(f_a \pm 2f_b)$ . IMD is usually expressed in dB.

- **MISSING CODES** are those output codes that will never appear at the ADC outputs. These codes cannot be reached with any input value. The ADC128S102 is ensured not to have any missing codes.

- **OFFSET ERROR** is the deviation of the first code transition (000...000) to (000...001) from the ideal (i.e. GND + 0.5 LSB).

- **SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

22

## **Device Support (continued)**

- **SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including d.c. or the harmonics included in THD.

- **SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the desired signal amplitude to the amplitude of the peak spurious spectral component, where a spurious spectral component is any signal present in the output spectrum that is not present at the input and may or may not be a harmonic.

- **THROUGHPUT TIME** is the minimum time required between the start of two successive conversions. It is the acquisition time plus the conversion and read out times. In the case of the ADC128S102, this is 16 SCLK periods.

- **TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dBc, of the rms total of the first five harmonic components at the output to the rms level of the input signal frequency as seen at the output. THD is calculated as:

THD = 20 •

$$\log_{10} \sqrt{\frac{A_{f2}^2 + \dots + A_{f10}^2}{A_{f1}^2}}$$

where

- · A<sub>f1</sub> is the RMS power of the input frequency at the output

- A<sub>f2</sub> through A<sub>f10</sub> are the RMS power in the first 9 harmonic frequencies

#### 11.2 Trademarks

MICROWIRE is a trademark of Texas Instruments.

QSPI is a trademark of Motorola, Inc..

All other trademarks are the property of their respective owners.

### 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Documentation Feedback

(8)

www.ti.com 30-Sep-2021

#### PACKAGING INFORMATION

| Orderable Device     | Status | Package Type | _       | Pins | Package | Eco Plan            | Lead finish/  | MSL Peak Temp      | Op Temp (°C) | Device Marking  | Samples |

|----------------------|--------|--------------|---------|------|---------|---------------------|---------------|--------------------|--------------|-----------------|---------|

|                      | (1)    |              | Drawing |      | Qty     | (2)                 | Ball material | (3)                |              | (4/5)           |         |

|                      |        |              |         |      |         |                     | (6)           |                    |              |                 |         |

| ADC128S102CIMT       | NRND   | TSSOP        | PW      | 16   | 92      | Non-RoHS<br>& Green | Call TI       | Level-1-260C-UNLIM | -40 to 105   | 128S102<br>CIMT |         |

| ADC128S102CIMT/NOPB  | ACTIVE | TSSOP        | PW      | 16   | 92      | RoHS & Green        | SN            | Level-1-260C-UNLIM | -40 to 105   | 128S102<br>CIMT | Samples |

| ADC128S102CIMTX/NOPB | ACTIVE | TSSOP        | PW      | 16   | 2500    | RoHS & Green        | SN            | Level-1-260C-UNLIM | -40 to 105   | 128S102<br>CIMT | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- <sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 30-Sep-2021

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

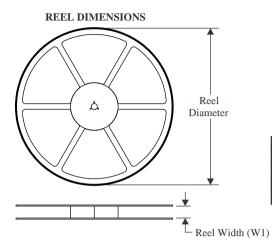

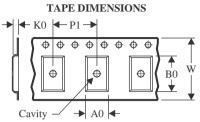

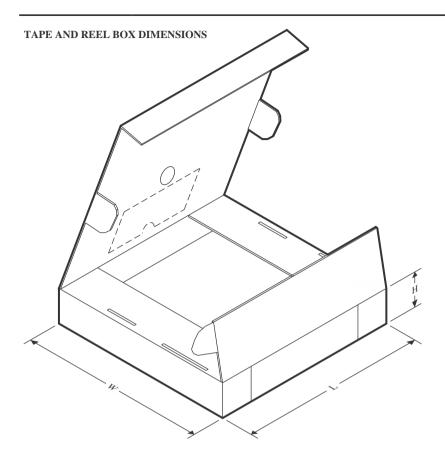

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

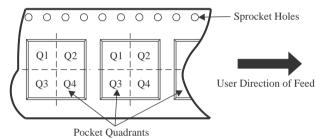

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device                   |       | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADC128S102CIMTX/<br>NOPB | TSSOP | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.95       | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

## \*All dimensions are nominal

| Device                   | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADC128S102CIMTX/<br>NOPB | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

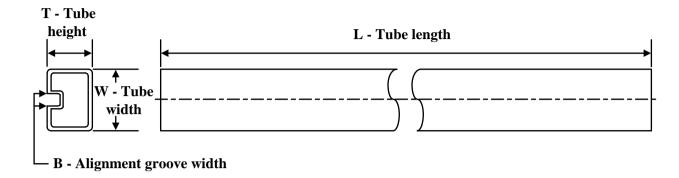

## **TUBE**

\*All dimensions are nominal

| Device              | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ADC128S102CIMT      | PW           | TSSOP        | 16   | 92  | 495    | 8      | 2514.6 | 4.06   |

| ADC128S102CIMT      | PW           | TSSOP        | 16   | 92  | 495    | 8      | 2514.6 | 4.06   |

| ADC128S102CIMT/NOPB | PW           | TSSOP        | 16   | 92  | 495    | 8      | 2514.6 | 4.06   |

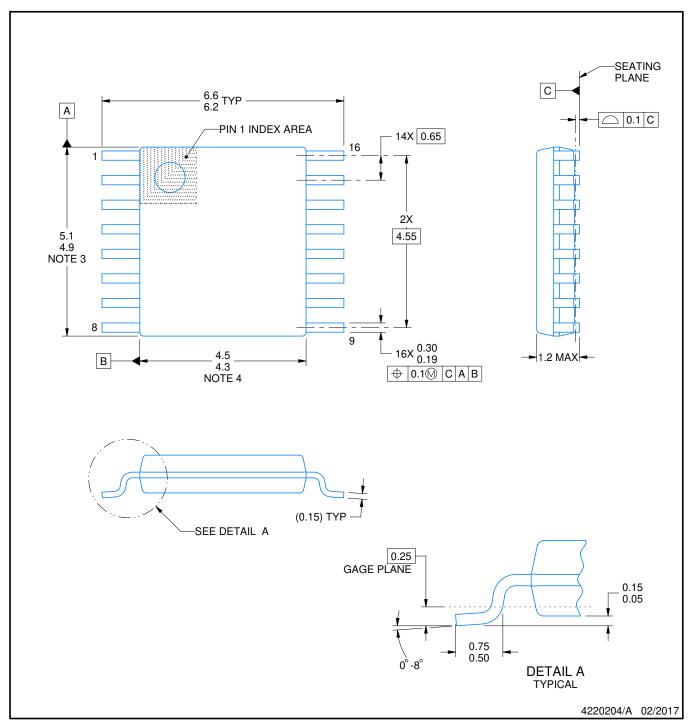

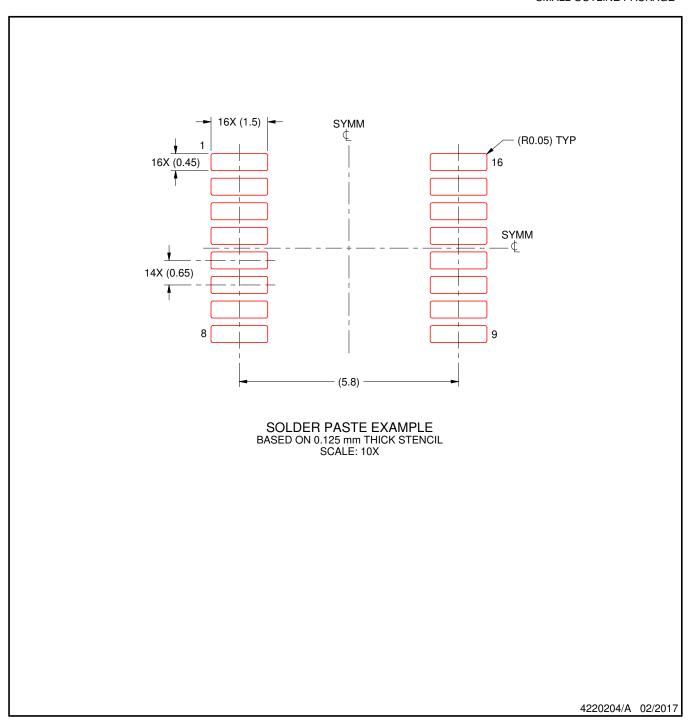

SMALL OUTLINE PACKAGE

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

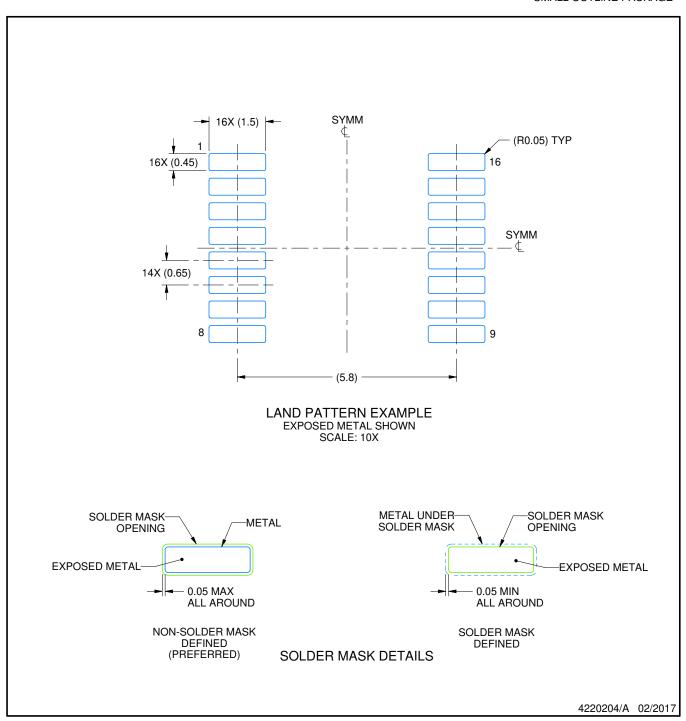

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated