# Primary-Side Regulated Flyback/Buck **80V DCDC Converter**

## **DESCRIPTION**

The MP6004 is a monolithic flyback dc-dc converter with a 180 V power switch that targets isolated or non-isolated 13 W PoE applications. It supports both primary-side regulated flyback and high-voltage buck applications.

MP6004 uses fixed peak current and variable frequency discontinuous conduction mode (DCM) to regulate constant output voltage. The primary-side regulation without opto-coupler feedback in flyback mode simplifies the design and saves BOM cost while buck mode minimizes the solution size for non-isolated applications. A 180 V integrated MOSFET optimizes the device for various wide voltage applications.

The MP6004 protection features include overload protection, over-voltage protection, opencircuit protection, and thermal shutdown.

The MP6004 is available in a QFN-14 3mm x 3mm package.

## **FEATURES**

- Supports Primary-Side Regulated Flyback without Opto-Coupler Feedback

- Supports Buck from Up to 80 V Input

- Integrated 180 V Switching Power MOSFET

- Internal 80 V Start-Up Circuit

- Up to 3 A Programmable Current Limit

- **Discontinuous Conduction Mode**

- OLP, OVP, Open-Circuit, and Thermal Protection

- Flexible Self-Power or External V<sub>CC</sub> Power

- Minimal External Component Count

- Available in a QFN-14 3mm x 3mm Package

### APPLICATIONS

- **Security Cameras**

- **VoIP Phones**

- **WLAN Access Points**

- General Flyback and Buck Converters

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

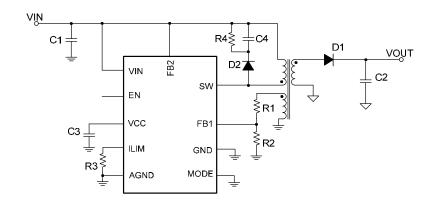

### TYPICAL APPLICATION

# **Efficiency**

Flyback, V<sub>OUT</sub> =12V

90 85 80 V<sub>IN</sub>=36√ 75 EFFICIENCY 70 65 V<sub>IN</sub>=48V 60 55 50 45 40 10 100 1000 LOAD CURRENT (mA)

# **ORDERING INFORMATION**

| Part Number* | Package            | Top Marking |  |

|--------------|--------------------|-------------|--|

| MP6004GQ     | QFN-14 (3mm x 3mm) | See Below   |  |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP6004GQ–Z)

# **TOP MARKING**

AMNY

LLL

AMN: Product code of MP6004GQ

Y: Year code LLL: Lot number

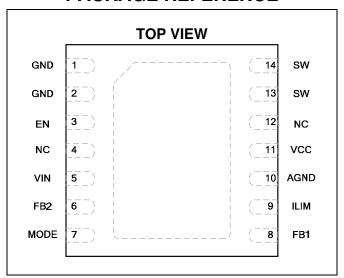

# **PACKAGE REFERENCE**

© 2015 MPS. All Rights Reserved.

| ABSOLUTE MAXIMUM                     |                                           |

|--------------------------------------|-------------------------------------------|

| SW                                   | 0.7 V to +180 V                           |

| FB1                                  |                                           |

| FB2 to VIN                           |                                           |

| All other pins                       | $-0.3 \text{ V to } +6.5 \text{ V}^{(3)}$ |

| VCC sinking current                  | 1.5 mA <sup>(4)</sup>                     |

| FB1 sinking current                  | ±1 mA <sup>(2)</sup>                      |

| EN sinking current                   | 1 mA <sup>(5)</sup>                       |

| Continuous power dissipation         |                                           |

|                                      |                                           |

| Junction temperature                 |                                           |

| Lead temperature                     |                                           |

| Storage temperature                  | 65°C to +150°C                            |

| Recommended Operating                |                                           |

| Supply voltage (V <sub>IN</sub> )    | 14 V to 80 V                              |

| Switching voltage (V <sub>SW</sub> ) | 0.5 V to +150 V                           |

| Maximum VCC sinking current          |                                           |

| Maximum FB1 sinking current          |                                           |

| Maximum EN sinking current           |                                           |

| Maximum switching frequency          |                                           |

| Maximum current limit                |                                           |

| Switching junction temp. $(T_J)$ .   | 40°C to +125°C                            |

| Thermal Resistance | $\boldsymbol{e}^{(8)}$ $\boldsymbol{\theta}_{JA}$ ( | $\theta_{JC}$ |      |

|--------------------|-----------------------------------------------------|---------------|------|

| QFN-14 (3mm x 3mm) |                                                     | 12            | °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- Refer to the "Output Voltage Setting" section on page 18.

- VCC and EN voltage can be pulled higher than this rating, but the external pull-up current should be limited. Refer to "VCC sinking current" and "EN sinking current" ratings to the left.

- Refer to the "V<sub>CC</sub> Power Supply Setting" section on page 17.. Refer to the "EN Control Setting" section on page 17.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction toambient thermal resistance  $\theta_{\text{JA}},$  and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J)$  $(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 48 V,  $V_{EN}$  = 5 V,  $V_{OUT}$  = 12 V,  $T_J$  = -40°C to 125°C, typical value is tested at 25°C, unless otherwise noted.

| Parameter                                    | Symbol              | Condition                                                     | Min    | Тур   | Max    | Units      |

|----------------------------------------------|---------------------|---------------------------------------------------------------|--------|-------|--------|------------|

| Power supply and UVLO                        |                     |                                                               |        |       |        |            |

| VIN UVLO rising threshold                    | $V_{\text{IN-R}}$   | V <sub>IN</sub> rising                                        | 10.5   | 11.6  | 12.8   | V          |

| VIN UVLO falling threshold                   | V <sub>IN-F</sub>   | V <sub>IN</sub> falling                                       | 7.4    | 8.2   | 9      | V          |

| VCC regulation <sup>(9)</sup>                | V <sub>CC</sub>     | Load = 0 mA to 10 mA                                          | 4.8    | 5.4   | 5.9    | V          |

| VCC UVLO rising threshold <sup>(9)</sup>     | V <sub>CC-R</sub>   | V <sub>IN</sub> is higher than UVLO, Vcc rising               | 4.3    | 4.7   | 5.1    | V          |

| VCC UVLO falling threshold <sup>(9)</sup>    | V <sub>CC-F</sub>   | V <sub>IN</sub> is higher than UVLO, Vcc falling              | 4      | 4.5   | 4.8    | V          |

| Quiescent current                            | $I_{Q}$             | $V_{FB1} = 2.2 \text{ V}, V_{FB2} = V_{IN}$                   |        | 380   |        | μΑ         |

| EN high-level voltage                        |                     |                                                               | 3.9    |       |        | V          |

| EN low-level voltage                         |                     |                                                               |        |       | 1.3    | V          |

| EN input current                             |                     |                                                               |        | 5.5   | 7.5    | μA         |

| Voltage feedback                             |                     |                                                               |        |       |        |            |

|                                              |                     | Respect to GND, T <sub>J</sub> = 25°C                         | 1.94   | 1.99  | 2.04   | V          |

| FB1 reference voltage                        | $V_{REF1}$          | Respect to GND, T <sub>J</sub> = -40°C to +125°C              | 1.93   | 1.99  | 2.05   | V          |

| FB1 leakage current                          | I <sub>FB1</sub>    | Respect to GND, V <sub>FB1</sub> = 2 V                        |        | 10    | 50     | nA         |

| Flyback mode DCM detect threshold on FB1     | V <sub>DCM1</sub>   | Respect to GND                                                | 25     | 50    | 75     | mV         |

| FB1 open-circuit threshold                   | $V_{FB1OPEN}$       |                                                               | -90    | -60   | -20    | mV         |

| FB1 OVP threshold                            | $V_{FB1OVP}$        |                                                               | 120%   | 125%  | 130%   | $V_{REF1}$ |

| Minimum diode conduction time for FB1 sample | T <sub>SAMPLE</sub> |                                                               | 1.4    | 2.2   | 3      | μs         |

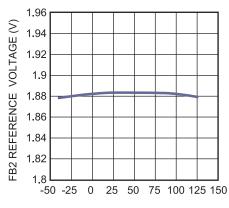

|                                              | V <sub>REF2</sub>   | Respect to V <sub>IN</sub> , T <sub>J</sub> = 25°C            | -1.955 | -1.88 | -1.805 | V          |

| FB2 reference voltage                        |                     | Respect to V <sub>IN</sub> , T <sub>J</sub> = -40°C to +125°C | -1.96  | -1.88 | -1.8   | V          |

| FB2 leakage current                          | I <sub>FB2</sub>    | Respect to V <sub>IN</sub> , V <sub>FB2</sub> = -2 V          |        | 10    | 50     | nA         |

| Buck mode DCM detect threshold on SW         | $V_{\text{DCM2}}$   | Respect to V <sub>IN</sub>                                    | 0      |       | 0.14   | V          |

| Switching power device                       |                     |                                                               |        |       |        |            |

| On resistance R <sub>ON-SW</sub>             |                     | V <sub>CC</sub> = 5.4 V                                       |        | 8.0   |        | Ω          |

| Current sense                                |                     |                                                               |        |       |        |            |

| Current limit                                | I <sub>LIMIT</sub>  | $R_{ILIM}$ = 53.6 k $\Omega$ , L = 47 $\mu$ H                 | 1.85   | 2.05  | 2.25   | Α          |

| Current leading-edge<br>Blanking time        | T <sub>LEB</sub>    |                                                               |        | 450   |        | ns         |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 48 V,  $V_{EN}$  = 5 V,  $V_{OUT}$  = 12 V,  $T_J$  = -40°C to 125°C, typical value is tested at 25°C, unless otherwise noted.

| Parameter                                    | Symbol                          | Condition | Min | Тур | Max | Units |

|----------------------------------------------|---------------------------------|-----------|-----|-----|-----|-------|

| DCDC converter thermal sh                    | DCDC converter thermal shutdown |           |     |     |     |       |

| Thermal shutdown temperature <sup>(10)</sup> | T <sub>SD</sub>                 |           |     | 150 |     | °C    |

| Thermal shutdown hysteresis <sup>(10)</sup>  | T <sub>HYS</sub>                |           |     | 20  |     | °C    |

#### NOTES:

<sup>9)</sup> The maximum VCC UVLO rising threshold is higher than the minimum VCC regulation in the EC table due to production distribution. However, for one unit, VCC regulation is higher than the VCC UVLO rising threshold. The VCC UVLO rising threshold is about 87 percent of the VCC regulation voltage, and the VCC UVLO falling threshold is about 83 percent of the VCC regulation voltage in one unit.

<sup>10)</sup> Guaranteed by characterization, not tested in production.

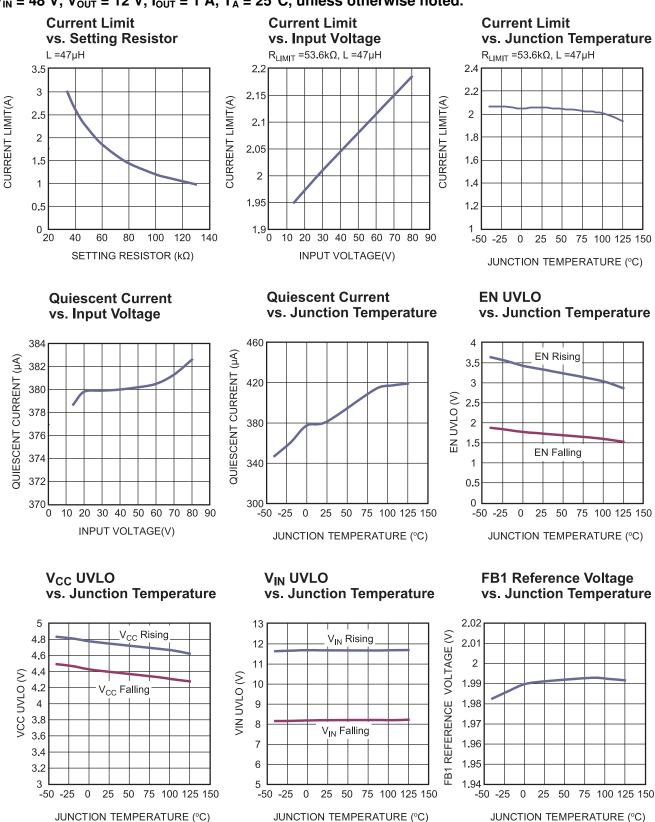

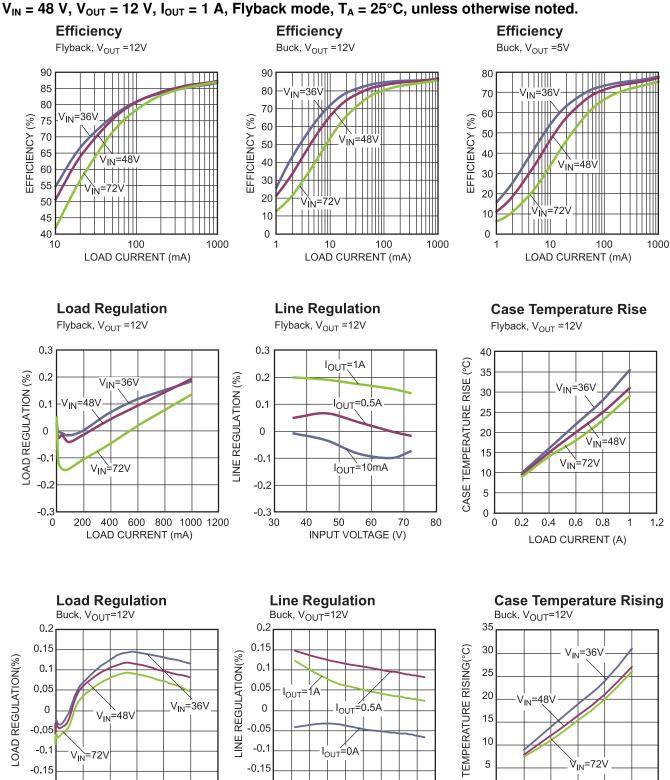

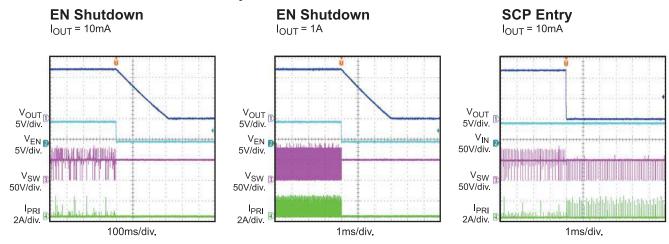

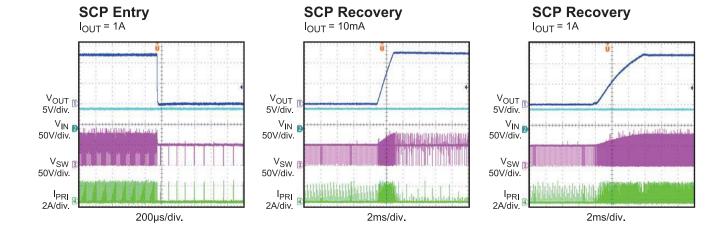

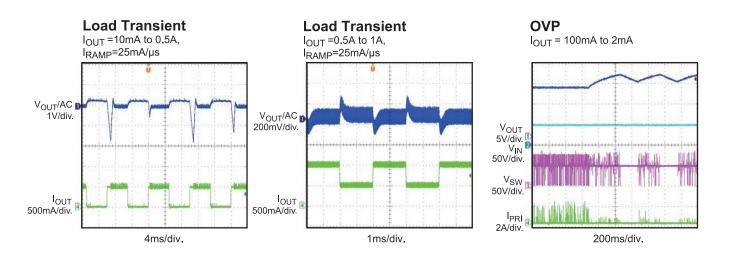

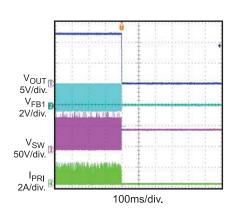

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V,  $I_{OUT}$  = 1 A,  $T_A$  = 25°C, unless otherwise noted.

$V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V,  $I_{OUT}$  = 1 A,  $T_A$  = 25°C, unless otherwise noted.

FB2 Reference Voltage vs. Junction Temperature

-0.2

-0.2

200 400 600 800 1000 1200

LOAD CURRENT(mA)

40 45 50 55 60 65

INPUT VOLTAGE(V)

0

0.2 0.4 0.6 0.8

LOAD CURRENT(A)

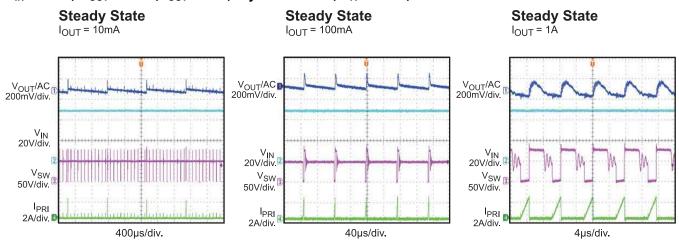

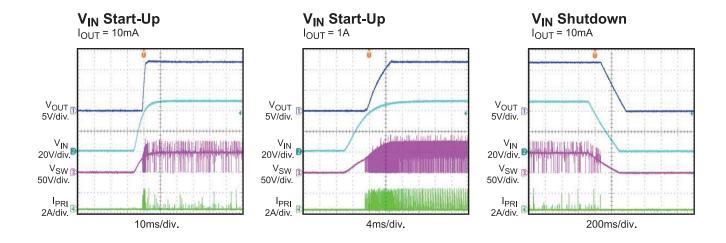

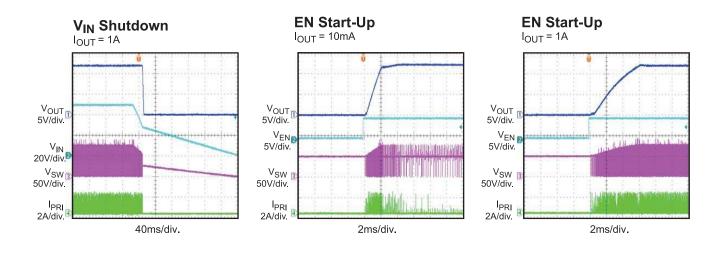

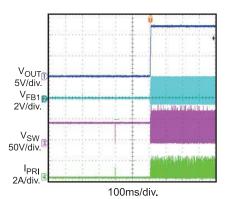

$V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V,  $I_{OUT}$  = 1 A, Flyback mode,  $T_A$  = 25°C, unless otherwise noted.

$V_{IN} = 48 \text{ V}$ ,  $V_{OUT} = 12 \text{ V}$ ,  $I_{OUT} = 1 \text{ A}$ , Flyback mode,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

$V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V,  $I_{OUT}$  = 1 A, Flyback mode,  $T_A$  = 25°C, unless otherwise noted.

FB1 Open-Circuit Entry I<sub>OUT</sub> = 1A

FB1 Open-Circuit Recovery I<sub>OUT</sub> = 1A

# **PIN FUNCTIONS**

| PIN#  | Name | Description                                                                                                                                                                                               |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2  | GND  | Switching converter power return.                                                                                                                                                                         |

| 3     | EN   | <b>Regulator on/off control input.</b> EN can program VIN UVLO start-up through a Zener diode and a resistor divider.                                                                                     |

| 4,12  | NC   | No connection. NC is not connected internally. Float NC or connect to GND in layout.                                                                                                                      |

| 5     | VIN  | Positive power supply terminal.                                                                                                                                                                           |

| 6     | FB2  | Feedback for non-isolated buck solution. Connect FB2 to VIN in flyback application.                                                                                                                       |

| 7     | MODE | <b>Buck mode or flyback mode select pin.</b> MODE is pulled up internally to VCC through a 1.5 μA current source. Float MODE for buck application mode; connect MODE to GND for flyback application mode. |

| 8     | FB1  | Feedback for flyback solution. Connect FB1 to GND in buck application.                                                                                                                                    |

| 9     | ILIM | <b>IC switching current limit program pin.</b> Connect ILIM to GND through a resistor to program the peak current limit.                                                                                  |

| 10    | AGND | Analog power return for switching converter control circuit.                                                                                                                                              |

| 11    | VCC  | Supply bias voltage pin, powered through internal LDO from VIN. It is recommended to connect a capacitor (no less than 1 $\mu$ F) between VCC and GND.                                                    |

| 13,14 | SW   | Drain of converter switching MOSFET.                                                                                                                                                                      |

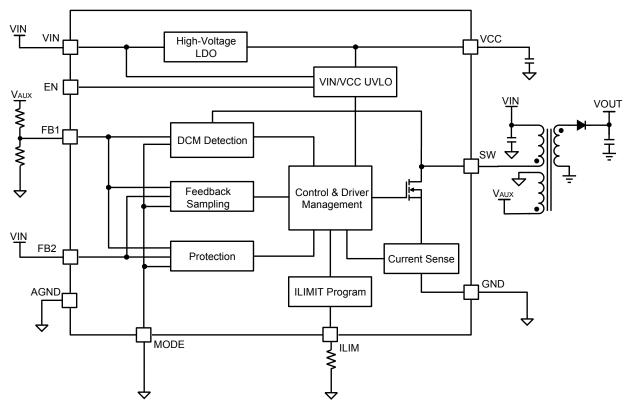

# **FUNCTION DIAGRAM**

Figure 1—Functional block diagram

## **OPERATION**

# Start-Up and Power Supply

MP6004 features an 80 V start-up circuit. When  $V_{\text{IN}}$  is higher than 4.3 V, the capacitor at VCC is charged through the internal LDO. Normally  $V_{\text{CC}}$  is regulated at 5.4 V (if VIN is high enough), and the  $V_{\text{CC}}$  UVLO is 4.7 V, typically. With the exception of  $V_{\text{CC}}$  UVLO, the MP6004 has an additional 11.6 V  $V_{\text{IN}}$  UVLO. When  $V_{\text{IN}}$  is higher than the 11.6 V UVLO,  $V_{\text{CC}}$  is charged higher than the 4.7 V UVLO, and EN pin is high, MP6004 starts switching.

V<sub>CC</sub> can be powered from the transformer auxiliary winding to save IC power loss. Refer to the "Vcc Power Supply Setting" section on page 18 for more details.

# Flyback and Buck Mode

MP6004 supports both flyback and buck topology applications. Connect MODE to GND to set the MP6004 in flyback mode, and float MODE to set the MP6004 in buck mode. MODE is pulled up internally to  $V_{\text{CC}}$  through a 1.5  $\mu\text{A}$  current source. Do not connect MODE to  $V_{\text{IN}}$  in buck mode, and do not place a resistor between MODE and GND in flyback mode.

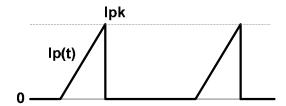

## **Switching Work Principle**

After start-up, MP6004 works in discontinuous conduction mode (DCM). The second switching cycle will not start until the inductor current drops to 0 A. In each cycle, the internal MOSFET is turned on, and the current-sense circuit senses the current  $I_{P(t)}$  internally.

Use Equation (1) to calculate the rate at which the current rises linearly in flyback mode:

$$\frac{dI_{p(t)}}{dt} = \frac{V_{IN}}{L_{M}} \tag{1}$$

When  $I_{P(t)}$  rises up to  $I_{PK}$ , the internal MOSFET turns off (see Figure 2). The energy stored in the primary-side inductance transfers to the secondary-side through the transformer.

Figure 2—Primary-side current waveform

The primary-side inductance  $(L_M)$  stores energy in each cycle as a function of Equation (2):

$$E = \frac{1}{2} L_{M} I_{PK}^{2} \tag{2}$$

Calculate the power transferred from the input to the output with Equation (3):

$$P = \frac{1}{2} L_{\rm M} I_{\rm PK}^2 F_{\rm S} \tag{3}$$

Where  $F_S$  is the switching frequency. When  $I_{PK}$  is constant, the output power depends on  $F_S$  and  $L_M$ .

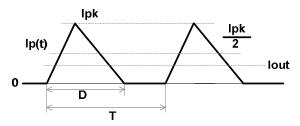

Use Equation (4) to calculate the rate at which the current rises linearly in buck mode:

$$\frac{dI_{p(t)}}{dt} = \frac{V_{IN} - V_{OUT}}{L_{M}}$$

(4)

The internal MOSFET turns off when  $I_{P(t)}$  rises to  $I_{PK}$  (see Figure 3). The output current is calculated with Equation (5):

$$I_{OUT} = \frac{1}{2}DI_{PK}$$

(5)

Where, D is the inductor current conducting duty cycle.

Figure 3—Inductor current waveform

## **Light-Load Control**

In flyback mode (if the load decreases), MP6004 stretches down the frequency automatically to reduce the power transferring while keeping the same I<sub>PK</sub> in each cycle. An approximate 10 kHz minimum frequency is applied to detect the output voltage even at a very light load. During this condition, the switching I<sub>PK</sub> jumps between 20 percent of the normal  $I_{PK}$  and 100 percent of the normal  $I_{PK}$  to reduce the power transferring. The MP6004 still transfers some energy to the output even if there is no load on the output due to the 10 kHz minimum frequency. This means that some load is required to maintain the output voltage, or else V<sub>OUT</sub> will rise and trigger an OVP.

In buck mode, the MP6004 has no minimum frequency limit, so it stretches down to a very low frequency and regulates the output automatically even there is no load on the output.

## **Frequency Control**

By monitoring the auxiliary winding voltage in flyback mode or monitoring the SW voltage in buck mode, the MP6004 detects and regulates the inductor current in DCM. The frequency is controlled by the peak current, the current ramp slew rate, and the load current. The maximum frequency occurs when the MP6004 runs in critical conduction mode, providing the maximum load power. The MP6004 switching frequency should be lower than 200 kHz in the design.

### **Voltage Control**

In flyback application, the MP6004 detects the auxiliary winding voltage from FB1 during the secondary-side diode conduction period.

Assume the secondary winding is the master, and the auxiliary winding is the slave. When the secondary-side diode conducts, the FB1 voltage is calculated with Equation (6):

$$V_{FB1} = \frac{N_A}{N_S} \times (V_{OUT} + V_{D1F}) \times \frac{R_2}{R_1 + R_2}$$

(6)

Where:

$V_{D1F}$  is the output diode forward-drop voltage.

$V_{OUT}$  is the output voltage.

$N_A$  and  $N_S$  are the turns of the auxiliary winding and the secondary-side winding, respectively.

R1 and R2 are the resistor dividers for sampling.

The output voltage differs from the secondarywinding voltage due to the current-dependant diode forward voltage drop. If the secondarywinding voltage is always detected at a fixed secondary current, the difference between the output voltage and the secondary-winding voltage is a fixed V<sub>D1F</sub>. MP6004 starts sampling the auxiliary-winding voltage after the internal power MOSFET turns off for 0.7 µs and finishes the sampling after the secondary-side diode conducts for 3 µs. This provides good regulation when the load changes. However, the secondary diode conducting period must be longer than 3 µs in each cycle, and the FB1 signal must be smooth 0.7 µs after the switch turns off.

With a buck solution, there is one FB2 pin referenced to VIN. It can be used as the reference voltage for the buck application. The output voltage is referenced to VIN and does not have the same GND as the input power.

### **Programming the Current Limit**

The MP6004 current limit is set by an external resistor (R3) from ILIM to ground. The value of R3 can be estimated with Equation (7):

$$I_{LIM} = \frac{100}{R3} + \frac{V_L \times 0.18}{L}$$

(7)

Where  $I_{\text{LIM}}$  is the current limit in A,  $V_{\text{L}}$  is the voltage applied on the inductor when the MOSFET turns on, R3 is the setting resistor in  $k\Omega$ , and L is the inductor in  $\mu H$ .

The current limit cannot be programmed higher than 3 A.

# Leading-Edge Blanking

Transformer parasitic capacitance induces a current spike on the sense resistor when the power switch turns on. The MP6004 includes a 450 ns leading-edge blanking period to avoid falsely terminating the switching pulse. During this blanking period, the current sense comparator is disabled, and the gate driver cannot switch off.

#### **DCM Detection**

The MP6004 regulator operates in discontinuous conduction mode in both flyback and buck modes.

In flyback mode, the MP6004 detects the falling edge of the FB1 voltage in each cycle. The second cycle switching will not start unless the chip detects a 50 mV falling edge on FB1.

In buck mode, the MP6004 detects the falling edge of the SW voltage in each cycle. The second cycle switching will not start unless the chip detects 0.14 V falling edge between  $V_{\text{SW}}$ - $V_{\text{IN}}$ .

# **Over-Voltage & Open-Circuit Protection**

In flyback mode, the MP6004 includes overvoltage protection (OVP) and open-circuit protection. If the voltage at FB1 exceeds 125 percent of  $V_{REF1}$  (or FB1's -60 mV falling edge cannot be detected because the feedback resistor is removed), immediately the MP6004 shuts off the driving signal and enters hiccup mode by re-charging the internal capacitor. The MP6004 resumes normal operation when the fault is removed.

In buck mode, if the voltage at FB2 is higher than the reference voltage, the MP6004 stops switching immediately.

#### **Over-Load Protection**

MP6004 will always work in DCM mode for any condition.

In flyback mode, the secondary-side diode conduction duty cycle is limited to about 80 percent. In an over-load condition, the output energy is limited by  $I_{PK}$  and  $F_{\rm S}.$  With a heavier load, the output drops and the diode conduction period becomes longer. This causes the switching frequency to drop so that the output energy can be limited. The MP6004 has same protection logic for an over-load/output-short condition.

In buck mode, the duty cycle limitation does not apply, but the output current is limited to half of  $I_{\text{PK}}$ .

#### Thermal Shutdown

When the junction temperature exceeds 150°C, the MP6004 shuts down. Once the temperature drops below 130°C, the part re-starts automatically.

## **APPLICATION INFORMATION**

## **EN Control Setting**

MP6004 turns on when EN goes high, and it turns off when EN goes low. EN is pulled low internally by an approximate 0.9  $M\Omega$  resistor.

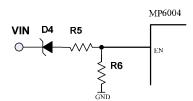

In flyback mode, the maximum on time is limited at about 8 µs. The secondary-side rectifier diode conduction time should be longer than 3 µs for FB1 feedback sampling. If V<sub>IN</sub> decreases and the inductor current cannot ramp the I<sub>PK</sub> to setting value within the maximum on time, the diode conduction time decreases to less than 3 µs, causing FB1 feedback sample failure. The MP6004 treats this failure as a V<sub>OUT</sub> drop and generates more pulses, causing  $V_{\text{OUT}}$  to overshoot. In this condition, EN can be used to program  $V_{\text{IN}}$ UVLO and shuts down the part before V<sub>IN</sub> drops (triggering the maximum on time). Since the EN high-level voltage is 3.9 V and the low-level voltage is 1.3 V, it is hard to program the V<sub>IN</sub> UVLO with a small hysteresis. In this condition, one resistor divider and one Zener diode is recommended (see Figure 4).

Figure 4—VIN UVLO setting with EN control

For example, the MP6004 should be turned on before  $V_{\text{IN}}$  rises to 36 V and shut down before  $V_{\text{IN}}$  drops to 20 V. One 20 V Zener diode (D4) and a resistor divider (R5 = 100 k $\Omega$ /R6 = 49.9 k $\Omega$ ) can be selected to program the  $V_{\text{IN}}$  UVLO. The programmed  $V_{\text{IN}}$  rising threshold can be calculated with Equation (8):

$$V_{IN\_R} < 20V + \frac{100k\Omega + 49.9k\Omega}{49.9k\Omega} \times 3.9V = 31.7V$$

(8)

The programmed  $V_{IN}$  falling threshold is calculated with Equation (9):

$$V_{IN\_F} > 20V + \frac{100k\Omega + 49.9k\Omega}{49.9k\Omega} \times 1.3V = 23.9V$$

(9)

In buck mode, FB2 feedback is not affected by the rectifier diode conduction time, but the Zener diode and resistor divider are recommended to set the appropriate V<sub>IN</sub> UVLO.

There is an internal Zener diode on EN, which clamps the EN voltage to prevent runaway. The maximum pull-up current for the internal Zener clamp (assuming 6.5 V) should be less than 0.5 mA. If EN is driven with an external signal, use a signal voltage less than 6.5 V or connect EN to the signal through a pull-up resistor that ensures the maximum pull-up current is less than 0.5 mA. If using a resistor divider (see Figure 4) and  $V_{\text{IN}}$ - $V_{\text{ZENER}}$  is higher than 6.5 V, the minimum resistance for the pull-up resistor R5 should be calculated with Equation (10):

$$\frac{V_{IN} - V_{ZENER} - 6.5V}{R5} - \frac{6.5V}{R6} < 0.5 \text{mA}$$

(10)

# V<sub>CC</sub> Power Supply Setting

The  $V_{\rm CC}$  voltage is charged through the internal LDO by VIN. Normally,  $V_{\rm CC}$  is regulated at 5.4 V, typically. A capacitor no less than 1  $\mu F$  is recommended for decoupling between  $V_{\rm CC}$  and GND.

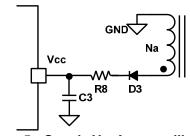

In flyback mode,  $V_{CC}$  can be powered from the transformer auxiliary winding to save the high-voltage LDO power loss.

Figure 5—Supply V<sub>CC</sub> from auxiliary winding

The auxiliary winding supply voltage can be calculated with Equation (11):

$$V_{CC} = \frac{N_A}{N_S} \times (V_{OUT} + V_{D1F}) - V_{D3F}$$

(11)

Where  $N_A$  and  $N_S$  are the turns of the auxiliary winding and the output winding,  $V_{D1F}$  is the output rectifier diode voltage drop, and  $V_{D3F}$  is the D3 voltage drop in Figure 5.

$V_{\text{CC}}$  voltage is clamped at about 6.2 V by one internal Zener diode. The clamp current

capability is about 1.2 mA. If the auxiliary winding power voltage is higher than 6.2 V (especially in a heavy-load condition), a series resistor (R8) is necessary to limit the current to VCC. For simple application, supply the  $V_{\rm CC}$  power through the internal LDO directly.

# **Output Voltage Setting**

In MP6004, there are two feedback pins for different application modes.

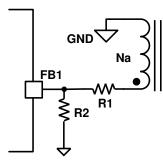

In flyback mode, the converter detects the auxiliary winding voltage from FB1. R1 and R2 are the resistor dividers for the feedback sampling (see Figure 6).

Figure 6—Feedback in isolation application

When the primary-side power MOSFET turns off, the auxiliary-winding voltage is sampled. The output voltage is estimated with Equation (12):

$$V_{OUT} = \frac{V_{REF1} \times (R_1 + R_2)}{R_2} \times \frac{N_S}{N_A} - V_{D1F}$$

(12)

Where,

$N_{\text{S}}$  is the transformer secondary-side winding turns.

$N_A$  is the transformer auxiliary winding turns.  $V_{D1F}$  is the rectifier diode forward drop.  $V_{REF1}$  is the reference voltage of FB1 (1.99 V, typically).

When the primary-side power MOSFET turns on, the auxiliary winding forces a negative voltage to FB1. The FB1 voltage is clamped to less than -0.7 V internally, but the clamp current should be limited to less than -0.5 mA by R1. For example, if the auxiliary winding forces -11 V to R1 (to make the current flowing from FB1 to R1 lower than -0.5 mA), R1 resistance must be higher than 22 k $\Omega$  (if ignoring R2 current).

Generally, select R2 with a 10 k $\Omega$  to 50 k $\Omega$  resistor to limit noise and provide an appropriate R1 for the -0.5 mA negative current limit

In buck application, the feedback pin is FB2. The output voltage can be estimated with Equation (13):

$$V_{OUT} = -\frac{R_1 + R_2}{R_2} \times V_{REF2}$$

(13)

Where,  $V_{REF2}$  is the reference voltage of FB2 -1.88 V, typically.

## **Maximum Switching Frequency**

When MP6004 works in DCM, the frequency reaches its maximum value during a full-load condition. The maximum frequency is affected by the peak current limit, the inductance, and the input/output voltage. Generally, design the maximum frequency lower than 200 kHz.

In buck mode, the maximum frequency occurs when the buck runs in critical conduction mode. The frequency can be calculated with Equation (14):

$$F_{SW\_MAX} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{I_{LIM} \times L \times V_{IN}}$$

(14)

Where,  $I_{\text{LIM}}$  is the  $I_{\text{PK}}$  set by the current limit resistor.

With a lighter load, the frequency is lower than the maximum frequency above.

In flyback mode, design the maximum frequency with the minimum input voltage and the maximum load condition. Calculate the frequency with Equation (15):

$$F_{SW} \le \frac{1}{T_{ON} + T_{CON} + T_{DELAY}}$$

(15)

Where:

T<sub>ON</sub> is the MOSFET one pulse turn-on time determined with Equation (16):

$$T_{ON} = \frac{I_{LIM} \times L_{M}}{V_{IN}}$$

(16)

$L_{\text{M}}$  is the transformer primary-winding inductance.

$T_{CON}$  is the rectifier diode current conducting time and can be calculated with Equation (17):

$$T_{CON} = \frac{N_S \times I_{LIM} \times L_M}{N_P \times (V_{OUT} + V_{D1F})}$$

(17)

Where,  $N_{\text{S}}$  is the transformer secondary-side winding turns.  $N_{\text{P}}$  is the transformer primary-side winding turns.

$T_{\text{DELAY}}$  is the resonant delay time from the rectifier diode current drop to 0 A to the auxiliary-winding voltage drop to 0 V. The resonant time can be tested on the board (estimate around 0.5  $\mu$ s).

In flyback mode, the MP6004 samples the feedback signal within 3  $\mu$ s after the primary-side MOSFET turns off. The secondary-side diode conduction time in Equation (17) should be higher than 3  $\mu$ s. This time period, combined with the duty cycle, determines the maximum frequency.

#### **Input Capacitor Selection**

An input capacitor is required to supply the AC ripple current to the inductor while limiting noise at the input source. A low ESR capacitor is required to keep the noise to the IC at a minimum. Ceramic capacitors are preferred, but tantalum or low ESR electrolytic capacitors will suffice. For ceramic capacitors, the capacitance dominates the impedance at the switching frequency. The ripple will be the worst at light load. The required input capacitance can be estimated with Equation (18):

$$C_{1} = \frac{0.5 \times I_{LIM} \times T_{ON}}{V_{INP P}}$$

(18)

Where  $C_1$  is the input capacitor value,  $V_{\mathsf{INP-P}}$  is the expected input ripple, and  $T_{\mathsf{ON}}$  is the MOSFET turn-on time.

In an isolated application,  $T_{ON}$  is calculated with Equation (19):

$$T_{ON} = \frac{I_{LIM} \times L_{M}}{V_{IN}}$$

(19)

In a non-isolation application,  $T_{ON}$  is calculated with Equation (20):

$$T_{ON} = \frac{I_{LIM} \times L}{V_{IN} - V_{OUT}}$$

(20)

Where L is the buck's inductor value.

#### **Output Capacitor Selection**

The output capacitor maintains the DC output voltage. For best results, use ceramic capacitors or low ESR capacitors to minimize the output voltage ripple. For ceramic capacitors, the capacitance dominates the impedance at the switching frequency.

In flyback application, the worst output ripple occurs under a light-load condition; the worst output ripple can be estimated by Equation (21):

$$V_{\text{OUTP\_P}} = \frac{0.5 \times N_{\text{P}} \times I_{\text{LIM}} \times T_{\text{CON}}}{N_{\text{S}} \times C2}$$

(21)

Where.

C2 is the output capacitor value.

V<sub>OUTP-P</sub> is the output ripple.

Normally, a 44  $\mu$ F or higher ceramic capacitor is recommended as the output capacitor. This allows a small Vo ripple and stable operation.

In buck application, the worst Vout ripple can be estimated with Equation (22):

$$V_{OUTP\_P} = \frac{0.5 \times I_{LIM}^{2} \times L \times (V_{IN} + V_{D1F})}{C2 \times (V_{IN} - V_{OUT}) \times (V_{OUT} + V_{D1F})}$$

(22)

#### Leakage Inductance

The transformer's leakage inductance decreases system efficiency and affects the output current and voltage precision. Optimize the transformer structure to minimize the leakage inductance. Aim for a leakage inductance less than 3 percent of the primary-winding inductance.

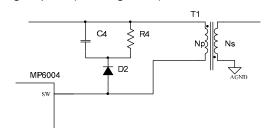

### **RCD Snubber for Flyback**

The transformer leakage inductance causes spikes and excessive ringing on the MOSFET drain voltage waveform, affecting the output voltage sampling 0.7 µs after the MOSFET turns off. The RCD snubber circuit limits the SW voltage spike (see Figure 7).

Figure 7—RCD snubber

The power dissipation in the snubber circuit is estimated with Equation (23):

$$P_{SN} = \frac{1}{2} \times L_{K} \times I_{LIM}^{2} \times F_{S}$$

(23)

Where,  $L_K$  is the leakage inductance.

Since R4 consumes the majority of the power, R4 is estimated with Equation (24):

$$R4 = \frac{V_{SN}^2}{P_{SN}} \tag{24}$$

Where,  $V_{SN}$  is the expected snubber voltage on C4.

The snubber capacitor C4 can be designed to get appropriate voltage ripple on the snubber using Equation (25):

$$\Delta V_{SN} = \frac{V_{SN}}{R4 \times C4 \times F_{S}}$$

(25)

Generally, a 15 percent ripple is acceptable.

#### **Buck Inductor Selection**

The inductor is required to transfer the energy between the input source and the output capacitors. Unlike normal application where inductors determine the inductor ripple, the MP6004 always works in DCM while  $V_{\rm IN}$ ,  $V_{\rm OUT}$ , and  $I_{\rm LIM}$  are constant. The inductor only determines the speed of the current rising and falling, which determines the switching period. The expected maximum frequency can determine the inductor value using Equation (26):

$$L \approx \frac{(V_{IN} - V_{OUT}) \times (V_{OUT} + V_{D1F})}{(V_{IN} + V_{D1F}) \times I_{PEAK}} \times \frac{1}{F_{SW}}$$

(26)

F<sub>SW</sub> is the expected maximum switching frequency, which should be lower than 200 kHz in general setting.

#### **Output Diode Selection**

The output rectifier diode supplies current to the output capacitor when the internal MOSFET is off. Use a Schottky diode to reduce loss due to the diode forward voltage and recovery time.

In isolation application, the diode should be rated for a reverse voltage greater than Equation (27):

$$V_{D1} = V_{OUT} + \frac{V_{IN} \times N_{S}}{N_{-}} + V_{PD1}$$

(27)

$V_{PD1}$  can be selected at 40 percent ~100 percent of  $V_{OUT}$  +  $V_{IN}$  x  $N_{S}/N_{P}$ . An RC or RCD snubber circuit for the output diode D1 is recommended.

In buck mode, the diode reverse voltage equates to the input voltage. A 20 percent ~ 40 percent margin is recommended.

In both applications, the current rating should be higher than the maximum output current.

### **Dummy Load**

When the system operates without a load in flyback mode, the output voltage rises above the normal operation voltage because of the minimum switching frequency limitation. Use a dummy load for good load regulation. A large dummy load decreases efficiency, so the dummy load is a tradeoff between efficiency and load regulation. For applications using Figure 10, a minimum load of around 10 mA is recommended.

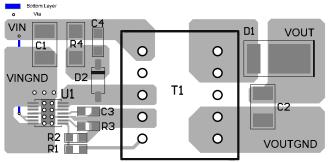

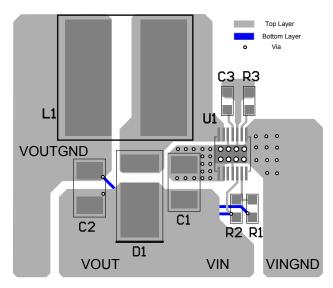

### **PCB Layout Guidelines**

Efficient PCB layout for high-frequency switching power supplies is critical. Poor layout may result in reduced performance, excessive EMI, resistive loss, and system instability. For best results, refer to Figure 8 and Figure 9 and follow the guidelines below:

### For flyback application:

- Keep the input loop as short as possible between the input capacitor, transformer, SW, and GND plane for minimal noise and ringing.

- 2. Keep the output loop between the rectifier diode, the output capacitor, and the transformer as short as possible.

- 3. Keep the clamp loop circuit between D2, C4, and the transformer as small as possible.

- Place the VCC capacitor close to VCC for the best decoupling. The current setting resistor R3 should be placed as close to ILIM and AGND as possible.

- Keep the feedback trace far away from noise sources (such as SW). The trace connecting FB1 should be short.

Top Layer

6. Use a single point connection between power GND and signal GND. Vias around GND and the thermal pad are recommended to lower the die temperature.

Figure 8—Recommended flyback layout

# For buck application:

- Keep the input loop as short as possible between the input capacitor, rectifier diode, SW, and GND plane for minimal noise and ringing.

- 2. Keep the output loop between the rectifier diode, the output capacitor, and the inductor as short as possible.

- Place the VCC capacitor close to VCC for the best decoupling. The current setting resistor R3 should be placed as close to ILIM and AGND as possible.

- 4. Connect the output voltage sense and VIN power supply from the output capacitor with parallel traces. The feedback trace should be far away from noise sources (such as SW). The trace connected to FB2 should be short.

- Use a single point connection between power GND and signal GND. Vias around GND and the thermal pad are recommended to lower the die temperature.

Figure 9—Recommended buck layout

#### **Design Example**

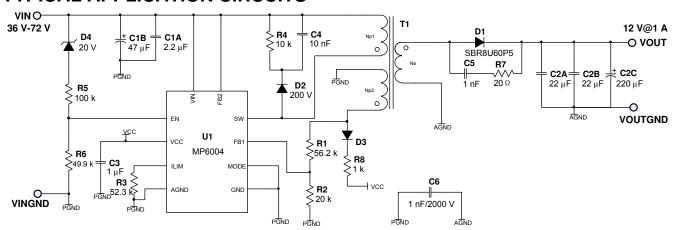

Table 1 shows a design example following the application guidelines for the following specifications in flyback applications:

Table 1—Flyback design example

| $V_{IN}$         | 36 V-72 V |

|------------------|-----------|

| $V_{OUT}$        | 12 V      |

| I <sub>out</sub> | 0 A-1 A   |

The typical application circuit for  $V_{\text{OUT}} = 12 \text{ V}$  in Figure 10 shows the detailed application schematic and is the basis for the typical performance waveforms. For more detailed device applications, please refer to the related evaluation board datasheet.

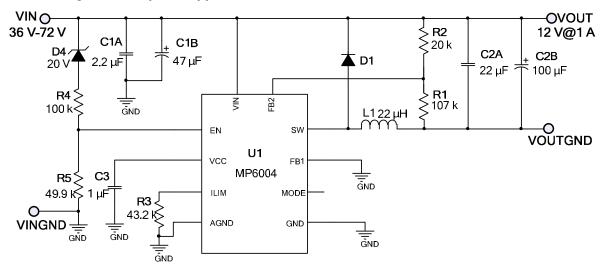

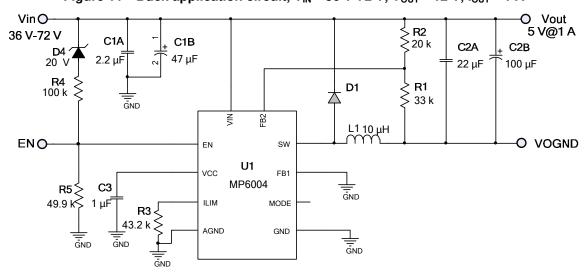

Table 2 shows a design example following the application guidelines for the following specifications in buck applications:

Table 2—Buck design example

| $V_{IN}$         | 36 V-72 V |

|------------------|-----------|

| V <sub>out</sub> | 12 V      |

| I <sub>OUT</sub> | 0 A-1 A   |

The typical application circuit is shown in Figure 11. For more detailed device applications, please refer to the related evaluation board datasheet.

## TYPICAL APPLICATION CIRCUITS

Figure 10—Flyback application circuit, V<sub>IN</sub> = 36 V-72 V, V<sub>OUT</sub> = 12 V, I<sub>OUT</sub> = 1 A

Figure 11—Buck application circuit,  $V_{IN} = 36 \text{ V-}72 \text{ V}$ ,  $V_{OUT} = 12 \text{ V}$ ,  $I_{OUT} = 1 \text{ A}$

Figure 12—Buck application circuit, V<sub>IN</sub> = 36 V-72 V, V<sub>OUT</sub> = 5 V, I<sub>OUT</sub> = 1 A

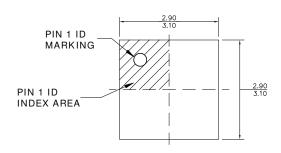

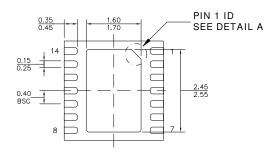

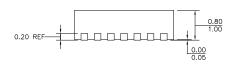

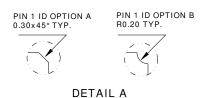

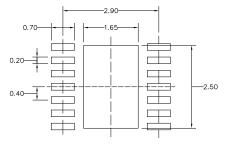

# **PACKAGE INFORMATION**

# QFN-14 (3mm X 3mm)

**TOP VIEW**

**BOTTOM VIEW**

SIDE VIEW

### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-229.

- 5) DRAWING IS NOT TO SCALE.

RECOMMENDED LAND PATTERN

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.