### MCU with 2KB SRAM and 64KB ECC E-Flash

### **GENERAL DESCRIPTION**

CS8977 is a general-purpose MCU with 64KB Code e-Flash memory with ECC and 2KB SRAM with ECC. The embedded flash for code storage has a builtin ECC that corrects one-bit errors and detects two-bit errors. CPU accesses the e-Flash through program address read and through Flash Controller which can perform software read/write operations of e-Flash.

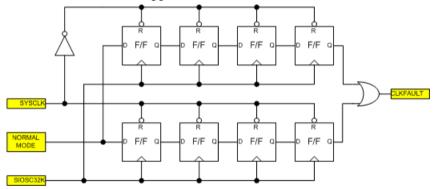

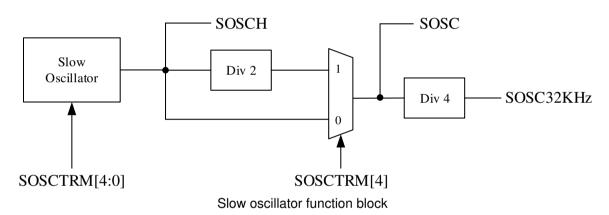

CS8977 has a 1-T 8051 with enhanced multiplication and division accelerator. There are three clock sources for the system. One is a 16MHz/32MHz IOSC (manufacturer calibration+/- 2%), another is XCLK, and the other one is SOSC32KHz (typical 32KHz) which is divided by the slow oscillator. ALL clock sources have a clock programmable divider for scaling down the frequency to save power dissipations. The clock selections are combined with flexible power management schemes, including NORMAL, IDLE, STOP, and SLEEP modes to balance speed and power consumption.

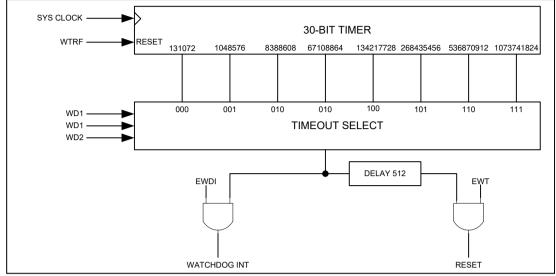

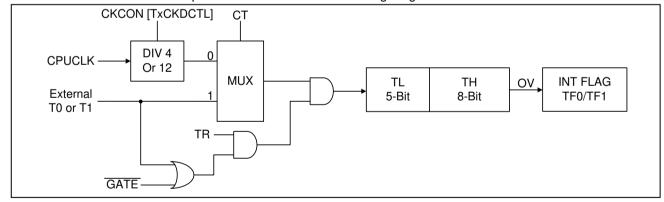

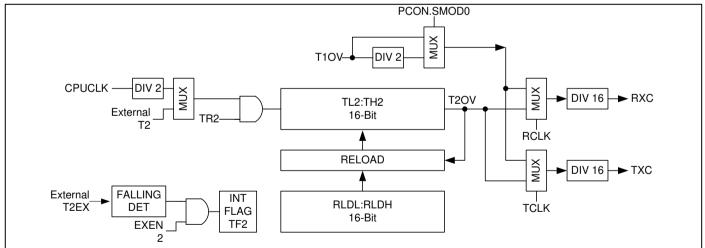

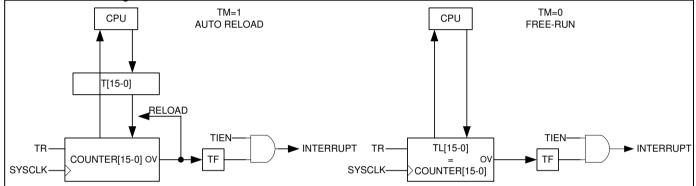

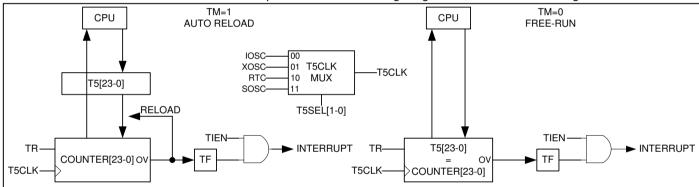

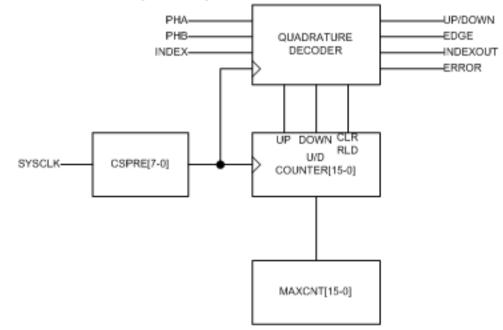

There are T0/T1/T2/T3/T4/T5 timers coupled with CPU and three WDTs where WDT1 is clocked by SYSCLK, and WDT2/WDT3 are clocked by a non-stop SOSC32KHz. An 8-bit/16-bit checksum and 16-bit CRC accelerator is included. There are EUART/LIN controllers, I2C master/slave controllers and SPI master/slave controller. The interfaces of these controllers are multiplexed with GPIO pins. Other useful peripherals include a buzzer control, six 8/10/12-bit PWMs, one channel of 16-bit timer/capture, and one 16-bit quadrature decoder. There are also 16 channels 8-bit PWM for LED control.

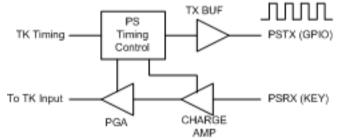

Analog peripherals include a 12-bit ADC with an internal temperature sensor, an 8-bit voltage output DAC, and four analog comparators with a programmable threshold. A touch key controller with up to 20-bit resolution is included. The touch key controller has shield output capability for moisture immunity and allows auto-detection wakeup from sleep mode (under 20uA). The maximum number of key inputs that can be scanned is 27. The touch key controller can also be used for proximity sensing.

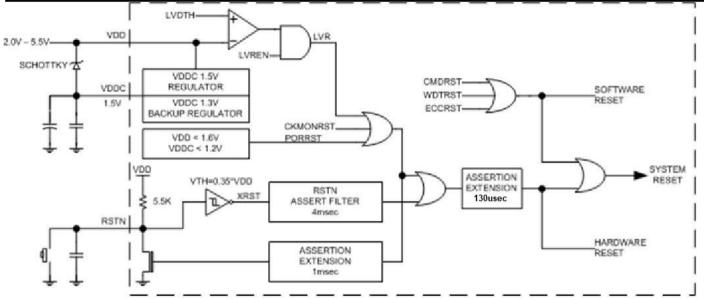

CS8977 provides a flexible means of flash programming that supports ISP and IAP. The protection of data loss is implemented in hardware by access restriction of critical storage segments. The code security is reinforced with sophisticated writer commands and ISP commands. The on-chip breakpoint processor also allows easy debugging which can be integrated with ISP. A reliable power-on-reset circuit and low supply voltage detection allow reliable operations under harsh environments.

### **APPLICATIONS**

- Touch key applications with high robustness and reliability requirements

- Automotive and appliance

### **FEATURES**

### CPU and Memory

- Up to 32MHz 1-Cycle 8051 CPU core

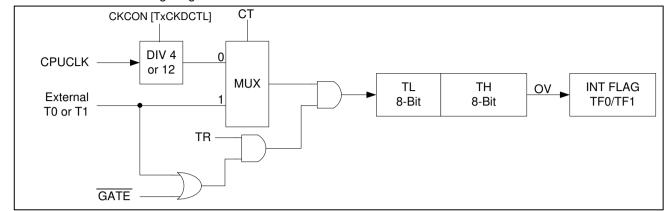

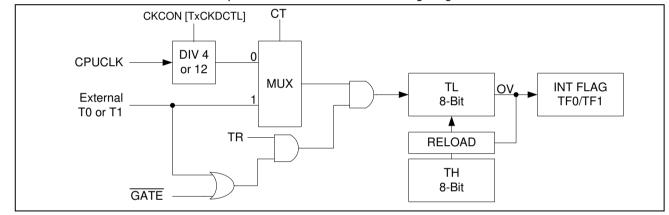

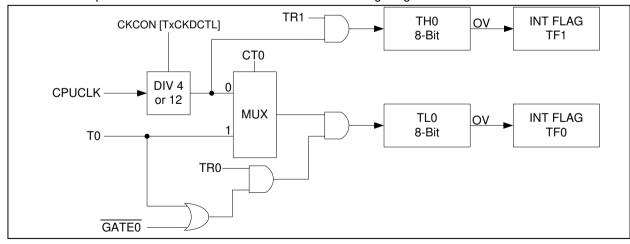

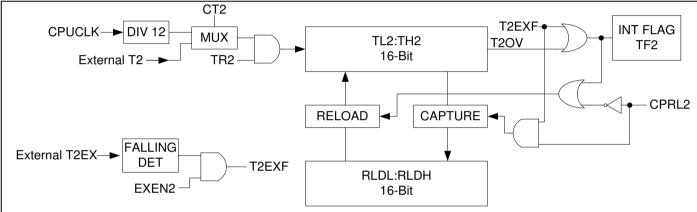

- 16-bit Timers T0/T1/T2/T3/T4 and 24-bit Timer T5

- Checksum and CRC accelerator

- WDT1 by SYSCLK, WDT2/WDT3 by SOSC32KHz

- Clock fault monitoring

- All GPIO pins can be assigned to two external interrupts

- Power-saving modes IDLE, STOP, and SLEEP

- 256B IRAM and 1792B XRAM with ECC check

- 64KB Code e-Flash with ECC and two 128x16 Information Block

- Code security and data loss protection

- 100K endurance and 10 years retention

#### **Clock Sources**

- Internal oscillator at 16MHz/32MHz(+/- 2%)

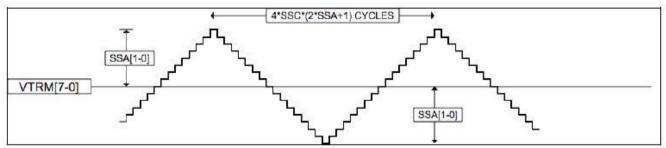

- Spread Spectrum option

- Internal low power oscillator 128KHz/256KHz

- External clock option and clock out

### **Digital Peripherals**

- 6 CH 8/10/12-bit center-aligned PWM controller

Trigger interrupt and ADC conversion

- 16 CH 8-bit PWM left/right alignment

- One 16-bit Timer/Capture and One 16-bit quadrature decoder

- Buzzer/Melody generator

- One I<sup>2</sup>C Master

- One I<sup>2</sup>C Slave also for ISP and debug

- One SPI Master/ Slave Controller

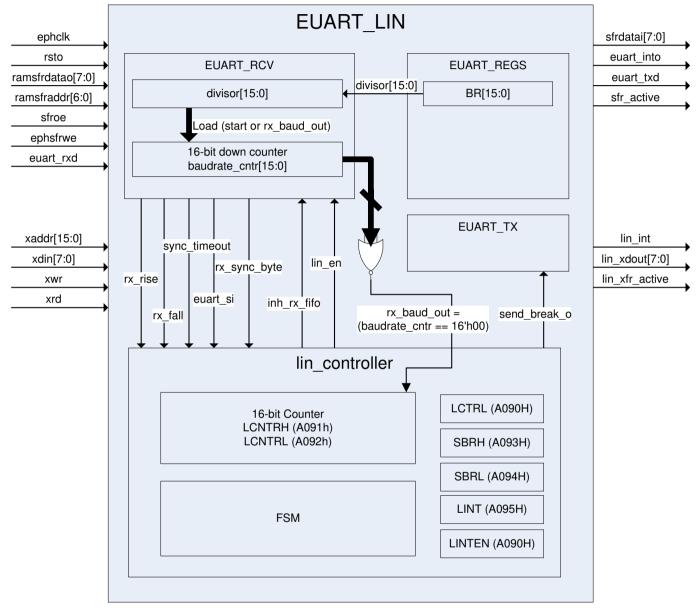

- One EUART1 and one EUART2/LIN

### Analog Peripherals

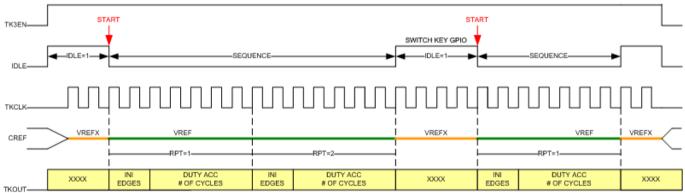

- Capacitance sense touch-key controller scan up to 27 key

- Shield output for moisture immunity

- Low power sleep mode wakeup (<20uA).</li>

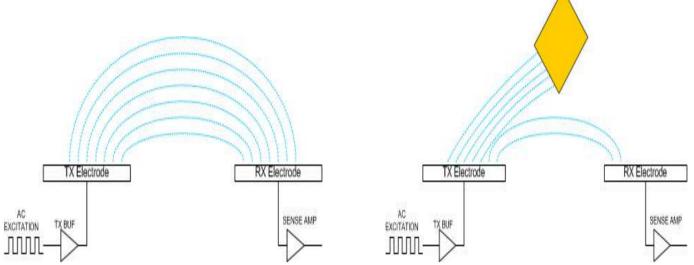

- Active Proximity sensing front-end

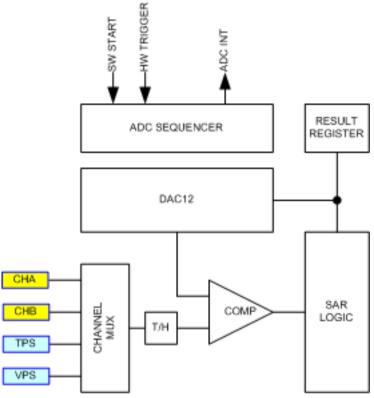

- 12-Bit SAR ADC with GPIO analog input

Temperature sensor and supply measurement

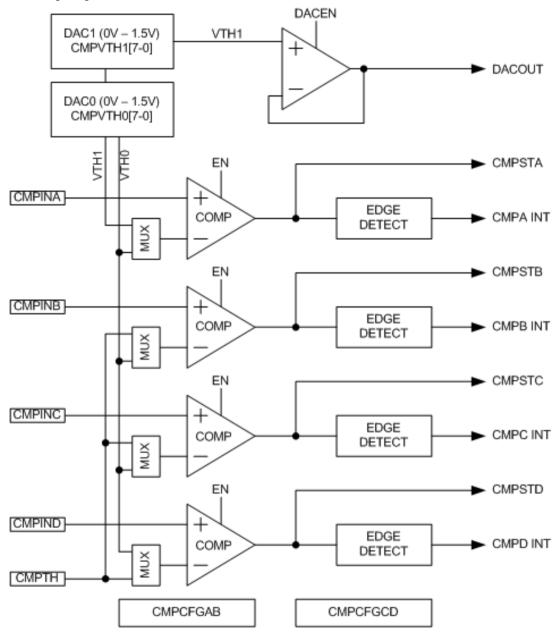

- 8-Bit DAC and four analog comparators

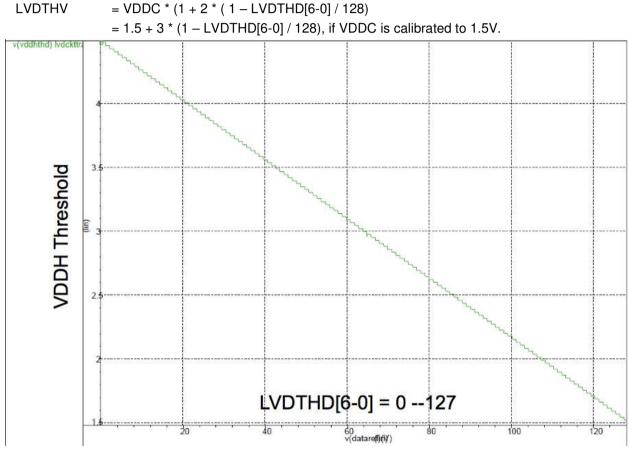

- Power-on reset and Low voltage detect (2.2V-4.5V)

### **Miscellaneous**

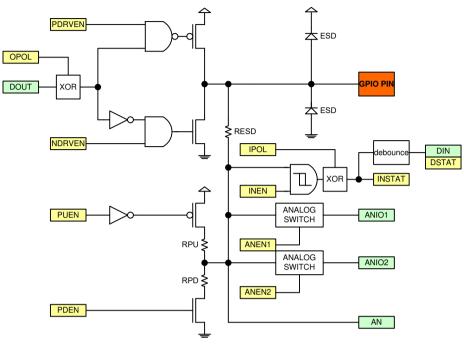

- Up to 28 GPIO pins with multi-function options

Configurable IO structure and noise filters

- ◆ 2.3V to 5.5V single supply

- Active current < 150uA/MHz in Normal mode

- Low power standby (1uA) in SLEEP mode

- Operating temperature -40°C to 85°C

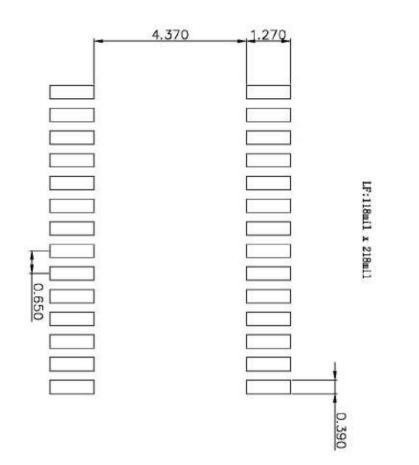

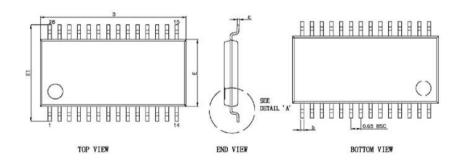

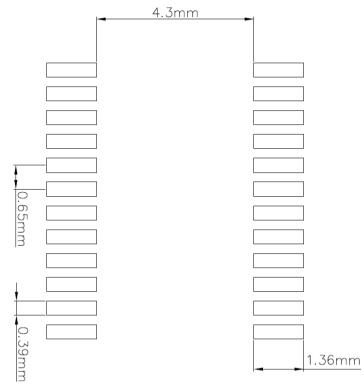

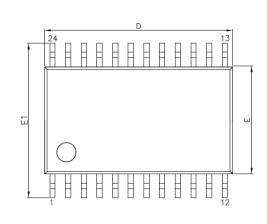

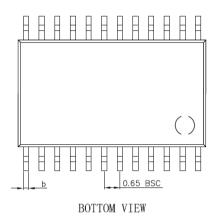

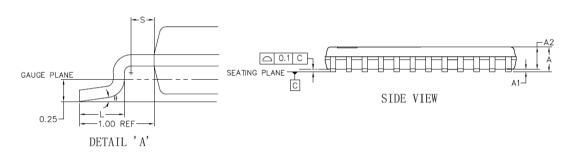

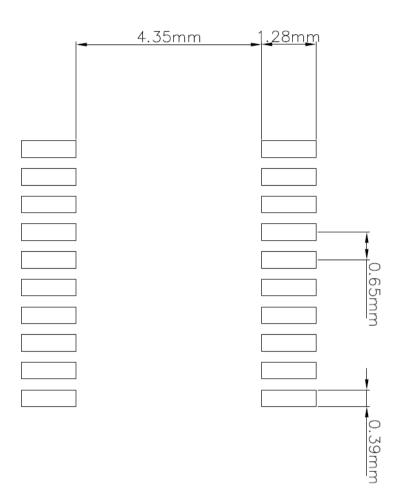

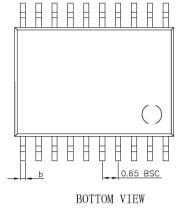

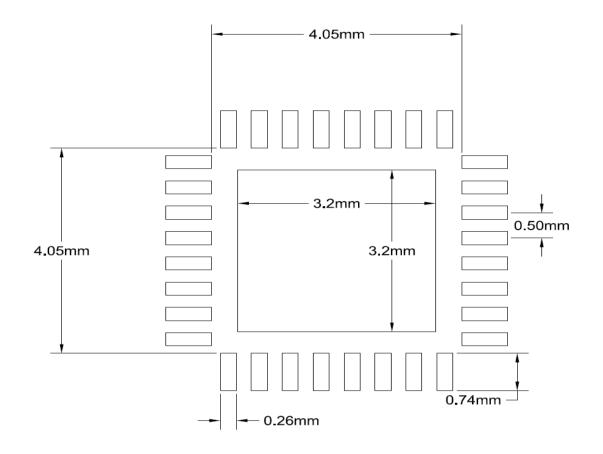

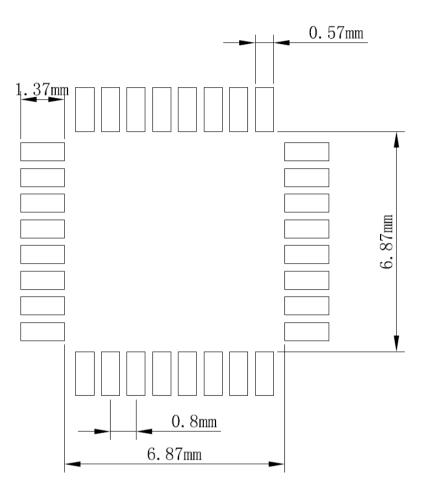

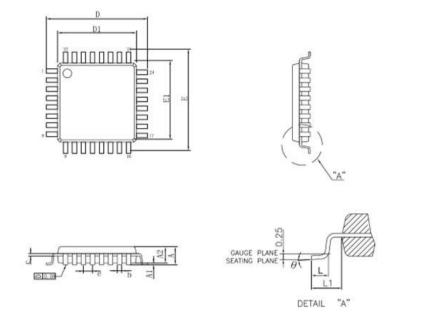

- TSSOP20/24/28, QFN-32 and LQFP32 package

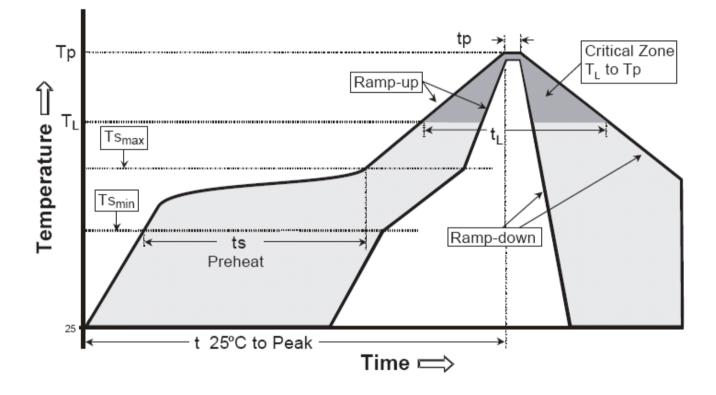

- RoHS & Halogen-Free compliant package

- TSCA Compliance

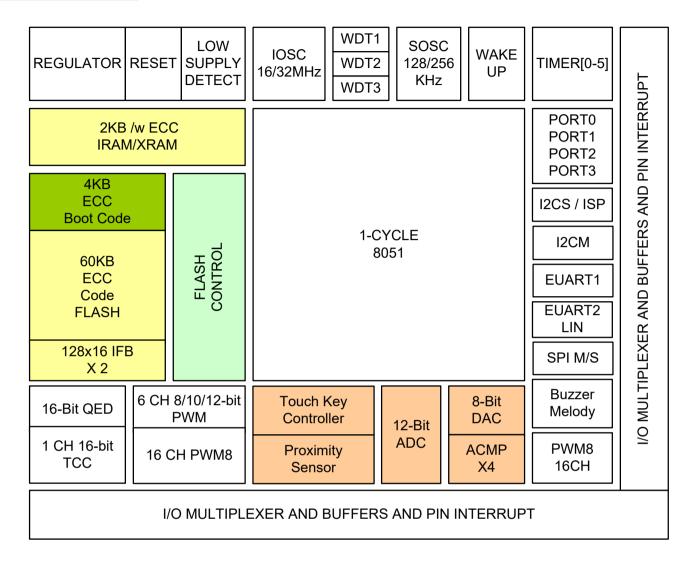

### IS31CS8977 BLOCK DIAGRAM

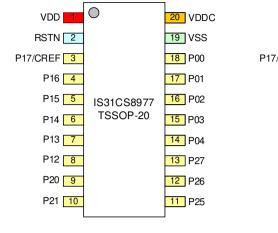

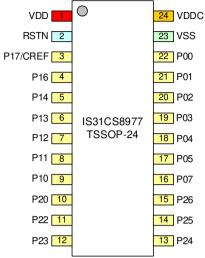

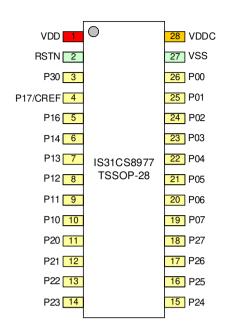

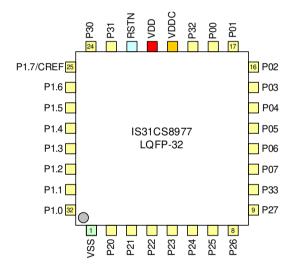

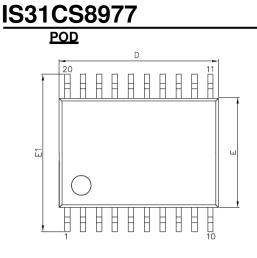

### IS31CS8977 PINOUT

### PIN Description and Multifunction Table

| TSSOP<br>20 | TSSOP<br>24 | TSSOP<br>28 | LQFP/<br>QFN<br>32 | NAME | TYPE | ANIO1 | ANIO2  | PIN DESCRIPTION                                                                      |

|-------------|-------------|-------------|--------------------|------|------|-------|--------|--------------------------------------------------------------------------------------|

| 1           | 1           | 1           | 21                 | VDD  | Р    | -     | -      | Supply Voltage 2.3V to 5.5V                                                          |

| 20          | 24          | 28          | 20                 | VDDC | P/O  | -     | -      | Internal 1.5V supply<br>Connect to external 1.0uF decoupling<br>capacitor.           |

| 2           | 2           | 2           | 22                 | RSTN | IO   | -     | -      | Active low reset input with internal 5K Ohm pull-up.                                 |

| 19          | 23          | 27          | 1                  | VSS  | G    |       |        | VSS                                                                                  |

| 18          | 22          | 26          | 18                 | P00  | IO/A | KEY   | ADCA   | Port 0.0 I/O with multi-function. This<br>pin also defaults to I2CS SDA for ISP      |

| 17          | 21          | 25          | 17                 | P01  | IO/A | KEY   | ADCB   | Port 0.1 I/O with multi-function. This<br>pin also defaults to I2CS SCL for ISP      |

| 16          | 20          | 24          | 16                 | P02  | IO/A | KEY   | DAC    | Port 0.2 I/O with multi-function.                                                    |

| 15          | 19          | 23          | 15                 | P03  | IO/A | KEY   | CMPA   | Port 0.3 I/O with multi-function.                                                    |

| 14          | 18          | 22          | 14                 | P04  | IO/A | KEY   | CMPB   | Port 0.4 I/O with multi-function.                                                    |

|             | 17          | 21          | 13                 | P05  | IO/A | KEY   | CMPC   | Port 0.5 I/O with multi-function.                                                    |

|             |             | 20          | 12                 | P06  | IO/A | KEY   | CMPD   | Port 0.6 I/O with multi-function.                                                    |

|             | 16          | 19          | 11                 | P07  | IO/A | KEY   | CMPTH  | Port 0.7 I/O with multi-function.                                                    |

|             | 9           | 10          | 32                 | P10  | IO/A | KEY   | ADCA   | Port 1.0 I/O with multi-function.                                                    |

|             | 8           | 9           | 31                 | P11  | IO/A | KEY   | ADCB   | Port 1.1 I/O with multi-function.                                                    |

| 8           | 7           | 8           | 30                 | P12  | IO/A | KEY   | SHIELD | Port 1.2 I/O with multi-function.                                                    |

| 7           | 6           | 7           | 29                 | P13  | IO/A | KEY   | CMPTH  | Port 1.3 I/O with multi-function.                                                    |

| 6           | 5           | 6           | 28                 | P14  | IO/A | KEY   | CMPD   | Port 1.4 I/O with multi-function.                                                    |

| 5           |             |             | 27                 | P15  | IO/A | KEY   | CMPC   | Port 1.5 I/O with multi-function.                                                    |

| 4           | 4           | 5           | 26                 | P16  | IO/A | KEY   | CMPB   | Port 1.6 I/O with multi-function.                                                    |

| 3           | 3           | 4           | 25                 | P17  | IO/A | CREF  | CMPA   | Port 1.7 I/O with multi-function.<br>Also serves as CREF for touch key<br>controller |

| 9           | 10          | 11          | 2                  | P20  | IO/A | KEY   | SHIELD | Port 2.0 I/O with multi-function.                                                    |

| 10          |             | 12          | 3                  | P21  | IO/A | KEY   | SHIELD | Port 2.1 I/O with multi-function.                                                    |

|             | 11          | 13          | 4                  | P22  | IO/A | KEY   | SHIELD | Port 2.2 I/O with multi-function.                                                    |

|             | 12          | 14          | 5                  | P23  | IO/A | KEY   | CMPA   | Port 2.3 I/O with multi-function.                                                    |

|             | 13          | 15          | 6                  | P24  | IO/A | KEY   | CMPB   | Port 2.4 I/O with multi-function.                                                    |

| 11          | 14          | 16          | 7                  | P25  | IO/A | KEY   | CMPC   | Port 2.5 I/O with multi-function.                                                    |

| 12          | 15          | 17          | 8                  | P26  | IO/A | KEY   | CMPD   | Port 2.6 I/O with multi-function.                                                    |

| 13          |             | 18          | 9                  | P27  | IO/A | KEY   | CMPTH  | Port 2.7 I/O with multi-function.                                                    |

|             |             | 3           | 24                 | P30  | IO/A | KEY   | ADCA   | Port 3.0 I/O with multi-function.                                                    |

|             |             |             | 23                 | P31  | IO/A | KEY   | ADCB   | Port 3.1 I/O with multi-function.                                                    |

|             |             |             | 19                 | P32  | IO/A | KEY   | DAC    | Port 3.2 I/O with multi-function.                                                    |

|             |             |             | 10                 | P33  | IO/A | KEY   | SHIELD | Port 3.3 I/O with multi-function.                                                    |

Note: If customers would like to use our CS89XX Touch Key Library software tool, please refer to our IS3XCS89XX Touch Key Library Tool User's Manual before starting your hardware schematics design.

Each GPIO pin can use MFCFG register to select pin functions. The function table is shown as the following table.

| MFCFG[5-0] | Function NAME | FUNCTION DESCRIPTION                                                                                |

|------------|---------------|-----------------------------------------------------------------------------------------------------|

| 00000      | LOW           | This forces the output to logic low state. Actual output depends on OPOL setting in IOCFG register. |

| 000001     | GPIO          | 8051 GPIO port                                                                                      |

| 000010     | SCK           | SPI SCK input or output depends on SPI MS setting.                                                  |

| 000011     | SDI           | SPI SDI input corresponds to MI or SI depending on SPI MS setting.                                  |

| 000100 | SDO    | SPI SDO output corresponds to MO or SO depending on SPI MS setting.                                 |

|--------|--------|-----------------------------------------------------------------------------------------------------|

| 000101 | SSN    | SPI SSN input or output depends on SPI MS setting.                                                  |

| 000110 | SSCL   | I2C Slave SCL I/O                                                                                   |

| 000111 | SSDA   | I2C Slave SDA I/O                                                                                   |

| 001000 | MSCL   | I2C Master SCL I/O                                                                                  |

| 001001 | MSDA   | I2C Master SDA I/O                                                                                  |

| 001010 | TX1    | EUART1 TX output                                                                                    |

| 001011 | RX1    | EUART1 RX input                                                                                     |

| 001100 | TX2    | EUART2/LIN TX output                                                                                |

| 001101 | RX2    | EUART2/LIN RX input                                                                                 |

| 001110 | BZ     | Buzzer/Melody output                                                                                |

| 001111 | XCLK   | External system clock input                                                                         |

| 010000 | Т0     | Timer 0 input                                                                                       |

| 010001 | T1     | Timer 1 input                                                                                       |

| 010010 | T2     | Timer 2 input                                                                                       |

| 010011 | IDX    | Quadrature Encoder IDX (Index) input                                                                |

| 010100 | PHA    | Quadrature Encoder PHA (Phase A) input                                                              |

| 010101 | PHB    | Quadrature Encoder PHA (Phase B) input                                                              |

| 010110 | XCAPT  | TCC (Timer Compare/Capture) Capture Input                                                           |

| 010111 | TC     | TCC (Timer Compare/Capture) Terminal Count output                                                   |

| 011000 | CC     | TCC (Timer Compare/Capture) Compare Count output                                                    |

| 011001 | PWM0   | PWM Channel 0 output                                                                                |

| 011010 | PWM1   | PWM Channel 1 output                                                                                |

| 011011 | PWM2   | PWM Channel 2 output                                                                                |

| 011100 | PWM3   | PWM Channel 3 output                                                                                |

| 011101 | PWM4   | PWM Channel 4 output                                                                                |

| 011110 | PWM5   | PWM Channel 5 output                                                                                |

| 011111 | HIGH   | This forces the output to logic high state. Actual output depends on OPOL setting in IOCFG register |

| 100000 | PSTX   | Proximity Sensor TX output                                                                          |

| 100001 | CLKO   | Clock Output                                                                                        |

| 100010 | PWM8-L | PWM8 left output                                                                                    |

| 100011 | PWM8-R | PWM8 right output                                                                                   |

\*\*\*\* MFCFG[5-0] default is 000000 after reset, thus default state is output logic low.

#### Note:

There are 16 channels of PWM - PWM0 to PWM15. The even channel is left-aligned and the odd channel is rightaligned. And the two of the continuous even and odd channels are grouped to map to two GPIO as follows. Each can be selected to be even or odd aligned by PWML and PWMR.

GPIO00 and GPIO01 are mapped to PWM0 and PWM1. GPIO02 and GPIO03 are mapped to PWM2 and PWM3. GPIO04 and GPIO05 are mapped to PWM4 and PWM5. GPIO06 and GPIO07 are mapped to PWM6 and PWM7. GPIO10 and GPIO11 are mapped to PWM8 and PWM9. GPIO12 and GPIO13 are mapped to PWM10 and PWM11. GPIO14 and GPIO15 are mapped to PWM10 and PWM13. GPIO16 and GPIO17 are mapped to PWM12 and PWM13. GPIO20 and GPIO21 are mapped to PWM0 and PWM15. GPIO22 and GPIO21 are mapped to PWM0 and PWM15. GPIO22 and GPIO23 are mapped to PWM2 and PWM3. GPIO24 and GPIO25 are mapped to PWM4 and PWM5. GPIO26 and GPIO27 are mapped to PWM6 and PWM5. GPIO26 and GPIO31 are mapped to PWM8 and PWM9. GPIO30 and GPIO31 are mapped to PWM8 and PWM9.

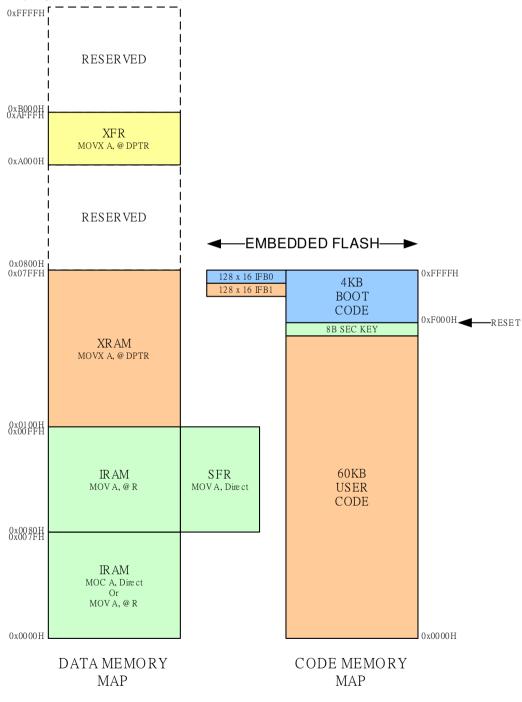

### IS31CS8977 MEMORY MAP

There is a total of 256 bytes of internal RAM in CS8977, the same as standard 8052. There is a total of 1792 bytes of auxiliary RAM allocated in the 8051 extended RAM area at 0x0100h - 0x07FFh. Programs can use "MOVX" instructions to access the XRAM.

There is a 64Kx16 embedded Flash memory for code storage. For CPU program access (Read-Only), the lower byte is used for actual access, and the upper byte is used for ECC check. The ECC is performed in nibble bases with each nibble in the high byte corresponding to the nibbles in the low byte. ECC in this case is capable of one-bit correction and two-bit detection for each nibble. This is significantly more robust than 8:5 ECC. ECC check of program access is through hardware and performed automatically. The embedded Flash can also be accessed through the Flash controller. The Flash controller allows both read/write access and is always in 16-bit width with no ECC. For erase operations, the page size of the Flash is 512x16. There are two 128x16 IFB blocks in the Flash. The first IFB is used for manufacturer and calibration data, and some areas are as user OTP data. The 2<sup>nd</sup> IFB is open for user applications with no restriction. Also please note that there is an 8-byte code security key located at the last 8 bytes of user program space to prevent pirate access to information.

### IS31CS8977 REGISTER MAP SFR (0x80 – 0xFF)

The SFR address map maintains maximum compatibilities to most existing 8051-like MCU. The following table shows the SFR address map. Since SFR can be accessed by direct addressing mode, registers of built-in peripherals that require fast access are mostly located in SFR. XFR is mainly used for on-chip peripheral control and configurations.

|                      | 0                    | 1                  | 2            | 3                     | 4                   | 5                    | 6                        | 7                        |

|----------------------|----------------------|--------------------|--------------|-----------------------|---------------------|----------------------|--------------------------|--------------------------|

| 0XF0                 | В                    | -                  | -            | -                     | I2CMSA              | I2CMCR               | I2CMBUF                  | I2CMTP                   |

| 0XE0                 | ACC                  | -                  | -            | -                     | -                   | -                    | -                        | -                        |

| 0XD0                 | PSW                  | -                  | -            | -                     | -                   | -                    | -                        | -                        |

| 0XC0                 | -                    | SBRK1              | SCON2        | I2CMTO                | PMR                 | STATUS               | MCON                     | ТА                       |

| 0XB0                 | P3                   | SCON1              | SCN1X        | SFIFO1                | SBUF1               | SINT1                | SBR1L                    | SBR1H                    |

| 0XA0                 | P2                   | SPICR              | SPIMR        | SPIST                 | SPIDATA             | SFIFO2               | SBUF2                    | SINT2                    |

| 0X90                 | P1                   | EXIF               | WTST         | DPX                   | -                   | DPX1                 | -                        | -                        |

| 0X80                 | P0                   | SP                 | DPL          | DPH                   | DPL1                | DPH1                 | DPS                      | PCON                     |

|                      | 8                    | 9                  | А            | В                     | С                   | D                    | E                        | F                        |

| 0XF8                 | EXIP                 | MD0                | MD1          | MD2                   | MD3                 | MD4                  | MD5                      | ARCON                    |

|                      |                      |                    |              |                       |                     |                      |                          |                          |

| 0XE8                 | EXIE                 | -                  | MXAX         | -                     | -                   | -                    | -                        | -                        |

| 0XE8<br>0XD8         | EXIE<br>WDCON        | -                  | MXAX<br>DPXR | -<br>I2CSCON2         | -<br>I2CSST2        | -<br>I2CSADR2        | -<br>I2CSDAT2            | -<br>I2CSADR2A           |

|                      |                      |                    |              | -<br>I2CSCON2<br>RLDH |                     |                      |                          | -<br>I2CSADR2A<br>T34CON |

| 0XD8                 | WDCON                | -                  | DPXR         |                       | I2CSST2             | I2CSADR2             | I2CSDAT2                 |                          |

| 0XD8<br>0XC8         | WDCON<br>T2CON       | -<br>TB            | DPXR<br>RLDL | RLDH                  | I2CSST2             | I2CSADR2             | I2CSDAT2<br>ADCCTLA      |                          |

| 0XD8<br>0XC8<br>0XB8 | WDCON<br>T2CON<br>IP | -<br>TB<br>ADCCTLB | DPXR<br>RLDL | RLDH                  | I2CSST2<br>TL2<br>- | I2CSADR2<br>TH2<br>- | I2CSDAT2<br>ADCCTLA<br>- | T34CON<br>-              |

### REGISTER MAP XFR (0xA000 – 0xAFFF)

|                              | 0                                          | 1                                          | 2                                        | 3                             | 4                                       | 5                                       | 6                                   | 7                                   |

|------------------------------|--------------------------------------------|--------------------------------------------|------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|-------------------------------------|-------------------------------------|

| A000                         | REGTRM                                     | IOSCITRM                                   | IOSCVTRM                                 | -                             | -                                       | -                                       | CLKOUT                              | SOSCTRM                             |

| A010                         | LVDCFG                                     | LVDTHD                                     | LVDHYS                                   | -                             | TSTMON                                  | FLSHVDD                                 | BSTCMD                              | RSTCMD                              |

| A020                         | FLSHDATL                                   | FLSHDATH                                   | FLSHADL                                  | FLSHADH                       | FLSHECC                                 | FLSHCMD                                 | ISPCLKF                             | FLSHPRTC                            |

| A030                         | FLSHPRT0                                   | FLSHPRT1                                   | FLSHPRT2                                 | FLSHPRT3                      | FLSHPRT4                                | FLSHPRT5                                | FLSHPRT6                            | FLSHPRT7                            |

| A040                         | NTAFRQL                                    | NTAFRQH                                    | NTADUR                                   | NTAPAU                        | NTBFRQL                                 | NTBFRQH                                 | NTBDUR                              | NTBPAU                              |

| A050                         | TCCFG1                                     | TCCFG2                                     | TCCFG3                                   | -                             | TCPRDL                                  | TCPRDH                                  | TCCMPL                              | ТССМРН                              |

| A060                         | TCCPTRL                                    | TCCPTRH                                    | TCCPTFL                                  | TCCPTFH                       | -                                       | -                                       | -                                   | -                                   |

| A070                         | QECFG1                                     | QECFG2                                     | QECFG3                                   | -                             | QECNTL                                  | QECNTH                                  | QEMAXL                              | QEMAXH                              |

|                              |                                            |                                            |                                          |                               |                                         |                                         |                                     |                                     |

|                              | 8                                          | 9                                          | A                                        | В                             | С                                       | D                                       | E                                   | F                                   |

| A008                         | 8<br>APSCFGA                               | 9<br>APSCFGB                               | A<br>APSCFGC                             | B<br>APSCFGD                  | C<br>TK3CFGE                            | D<br>PECCCFG                            | E<br>PECCADL                        | F<br>PECCADH                        |

| A008<br>A018                 | _                                          |                                            |                                          |                               |                                         |                                         |                                     |                                     |

|                              | APSCFGA                                    | APSCFGB                                    | APSCFGC                                  | APSCFGD                       | TK3CFGE                                 | PECCCFG                                 | PECCADL                             | PECCADH                             |

| A018                         | APSCFGA<br>TK3CFGA<br>TK3BASEL             | APSCFGB<br>TK3CFGB                         | APSCFGC<br>TK3CFGC                       | APSCFGD<br>TK3CFGD            | TK3CFGE<br>TK3HDTYL                     | PECCCFG<br>TK3HDTYH                     | PECCADL<br>TK3LDTYL                 | PECCADH<br>TK3LDTYH                 |

| A018<br>A028                 | APSCFGA<br>TK3CFGA<br>TK3BASEL             | APSCFGB<br>TK3CFGB<br>TK3BASEH             | APSCFGC<br>TK3CFGC<br>TK3THDL            | APSCFGD<br>TK3CFGD<br>TK3THDH | TK3CFGE<br>TK3HDTYL<br>TK3PUD           | PECCCFG<br>TK3HDTYH<br>DECCCFG          | PECCADL<br>TK3LDTYL                 | PECCADH<br>TK3LDTYH                 |

| A018<br>A028<br>A038         | APSCFGA<br>TK3CFGA<br>TK3BASEL<br>CMPCFGAB | APSCFGB<br>TK3CFGB<br>TK3BASEH<br>CMPCFGCD | APSCFGC<br>TK3CFGC<br>TK3THDL<br>CMPVTH0 | APSCFGD<br>TK3CFGD<br>TK3THDH | TK3CFGE<br>TK3HDTYL<br>TK3PUD<br>DACCFG | PECCCFG<br>TK3HDTYH<br>DECCCFG<br>CMPST | PECCADL<br>TK3LDTYL<br>DECCADL<br>- | PECCADH<br>TK3LDTYH<br>DECCADH<br>- |

| A018<br>A028<br>A038<br>A048 | APSCFGA<br>TK3CFGA<br>TK3BASEL<br>CMPCFGAB | APSCFGB<br>TK3CFGB<br>TK3BASEH<br>CMPCFGCD | APSCFGC<br>TK3CFGC<br>TK3THDL<br>CMPVTH0 | APSCFGD<br>TK3CFGD<br>TK3THDH | TK3CFGE<br>TK3HDTYL<br>TK3PUD<br>DACCFG | PECCCFG<br>TK3HDTYH<br>DECCCFG<br>CMPST | PECCADL<br>TK3LDTYL<br>DECCADL<br>- | PECCADH<br>TK3LDTYH<br>DECCADH<br>- |

|                              | 0                                                   | 1                                        | 2                                         | 3                                         | 4                                         | 5                                         | 6                    | 7                     |

|------------------------------|-----------------------------------------------------|------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------|-----------------------|

| A080                         | PWMCFG1                                             | PWMCFG2                                  | PWMCFG3                                   | -                                         | PWM0DTYL                                  | PWM0DTYH                                  | PWM1DTYL             | PWM1DTYH              |

| A090                         | LINCTRL                                             | LINCNTRH                                 | LINCNTRL                                  | LINSBRH                                   | LINSBRL                                   | LININT                                    | LININTEN             | -                     |

| A0A0                         | PWMDTY0                                             | PWMDTY1                                  | PWMDTY2                                   | PWMDTY3                                   | PWMDTY4                                   | PWMDTY5                                   | PWMDTY6              | PWMDTY7               |

| A0B0                         | LINTCON                                             | TXDTOL                                   | TXDTOH                                    | RXDTOL                                    | RXDTOH                                    | BSDCLRL                                   | BSDCLRH              | BSDWKC                |

| A0C0                         | FLSHPPT0                                            | FLSHPPT1                                 | FLSHPPT2                                  | FLSHPPT3                                  | FLSHPPT4                                  | FLSHPPT5                                  | FLSHPPT6             | FLSHPPT7              |

| A0D0                         | -                                                   | -                                        | -                                         | -                                         | -                                         | -                                         | -                    | -                     |

| A0E0                         | BPINTF                                              | BPINTE                                   | BPINTC                                    | BPCTRL                                    | -                                         | -                                         | -                    | -                     |

| A0F0                         | PC1AL                                               | PC1AH                                    | PC1AT                                     | -                                         | PC2AL                                     | PC2AH                                     | PC2AT                | -                     |

|                              |                                                     |                                          |                                           |                                           |                                           |                                           |                      |                       |

|                              | 8                                                   | 9                                        | A                                         | В                                         | С                                         | D                                         | E                    | F                     |

| A088                         | _                                                   | 9<br>PWM2DTYH                            |                                           |                                           |                                           | D<br>PWM4DTYH                             |                      | F<br>PWM5DTYH         |

| A088<br>A098                 |                                                     |                                          |                                           |                                           |                                           |                                           |                      |                       |

| -                            | PWM2DTYL                                            | PWM2DTYH                                 | PWM3DTYL<br>DBPCIDT                       | PWM3DTYH<br>DBPCNXL                       | PWM4DTYL<br>DBPCNXH                       | PWM4DTYH                                  | PWM5DTYL<br>STEPCTRL | PWM5DTYH<br>SI2CDBGID |

| A098                         | PWM2DTYL<br>DBPCIDL                                 | PWM2DTYH<br>DBPCIDH                      | PWM3DTYL<br>DBPCIDT                       | PWM3DTYH<br>DBPCNXL                       | PWM4DTYL<br>DBPCNXH                       | PWM4DTYH<br>DBPCNXT                       | PWM5DTYL<br>STEPCTRL | PWM5DTYH<br>SI2CDBGID |

| A098<br>A0A8                 | PWM2DTYL<br>DBPCIDL<br>PWMDTY8                      | PWM2DTYH<br>DBPCIDH                      | PWM3DTYL<br>DBPCIDT                       | PWM3DTYH<br>DBPCNXL                       | PWM4DTYL<br>DBPCNXH                       | PWM4DTYH<br>DBPCNXT                       | PWM5DTYL<br>STEPCTRL | PWM5DTYH<br>SI2CDBGID |

| A098<br>A0A8<br>A0B8         | PWM2DTYL<br>DBPCIDL<br>PWMDTY8<br>BSDACT            | PWM2DTYH<br>DBPCIDH                      | PWM3DTYL<br>DBPCIDT                       | PWM3DTYH<br>DBPCNXL                       | PWM4DTYL<br>DBPCNXH                       | PWM4DTYH<br>DBPCNXT                       | PWM5DTYL<br>STEPCTRL | PWM5DTYH<br>SI2CDBGID |

| A098<br>A0A8<br>A0B8<br>A0C8 | PWM2DTYL<br>DBPCIDL<br>PWMDTY8<br>BSDACT<br>FLSHPTI | PWM2DTYH<br>DBPCIDH<br>PWMDTY9<br>-<br>- | PWM3DTYL<br>DBPCIDT<br>PWMDTY10<br>-<br>- | PWM3DTYH<br>DBPCNXL<br>PWMDTY11<br>-<br>- | PWM4DTYL<br>DBPCNXH<br>PWMDTY12<br>-<br>- | PWM4DTYH<br>DBPCNXT<br>PWMDTY13<br>-<br>- | PWM5DTYL<br>STEPCTRL | PWM5DTYH<br>SI2CDBGID |

|                              | 0                                                       | 1                                                       | 2                                                       | 3                                                       | 4                    | 5                                         | 6                    | 7                    |

|------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|----------------------|-------------------------------------------|----------------------|----------------------|

| A100                         | IOCFGO00                                                | IOCFGO01                                                | IOCFGO02                                                | IOCFGO03                                                | IOCFGO04             | IOCFGO05                                  | IOCFGO06             | IOCFGO07             |

| A110                         | IOCFGI00                                                | IOCFGI01                                                | IOCFGI02                                                | IOCFGI03                                                | IOCFGI04             | IOCFGI05                                  | IOCFGI06             | IOCFGI07             |

| A120                         | MFCFG00                                                 | MFCFG01                                                 | MFCFG02                                                 | MFCFG03                                                 | MFCFG04              | MFCFG05                                   | MFCFG06              | MFCFG07              |

| A130                         | IOCFGO20                                                | IOCFGO21                                                | IOCFGO22                                                | IOCFGO23                                                | IOCFGO24             | IOCFGO25                                  | IOCFGO26             | IOCFGO27             |

| A140                         | IOCFGI20                                                | IOCFGI21                                                | IOCFGI22                                                | IOCFGI23                                                | IOCFGI24             | IOCFGI25                                  | IOCFGI26             | IOCFGI27             |

| A150                         | MFCFG20                                                 | MFCFG21                                                 | MFCFG22                                                 | MFCFG23                                                 | MFCFG24              | MFCFG25                                   | MFCFG26              | MFCFG27              |

| A160                         | -                                                       | -                                                       | -                                                       | -                                                       | -                    | -                                         | -                    | -                    |

| A170                         | -                                                       | -                                                       | -                                                       | -                                                       | -                    | -                                         | -                    | -                    |

|                              |                                                         |                                                         |                                                         |                                                         |                      |                                           |                      |                      |

|                              | 8                                                       | 9                                                       | A                                                       | В                                                       | С                    | D                                         | E                    | F                    |

| A108                         | 8<br>IOCFGO10                                           | 9<br>IOCFGO11                                           | A<br>IOCFGO12                                           | B<br>IOCFGO13                                           | C<br>IOCFGO14        | D<br>IOCFGO15                             | E<br>IOCFGO16        | F<br>IOCFGO17        |

| A108<br>A118                 |                                                         |                                                         |                                                         |                                                         |                      |                                           |                      |                      |

|                              | IOCFGO10                                                | IOCFGO11                                                | IOCFGO12                                                | IOCFGO13                                                | IOCFGO14             | IOCFGO15                                  | IOCFGO16             | IOCFGO17             |

| A118                         | IOCFGO10<br>IOCFGI10                                    | IOCFGO11<br>IOCFGI11                                    | IOCFGO12<br>IOCFGI12                                    | IOCFGO13<br>IOCFGI13                                    | IOCFGO14<br>IOCFGI14 | IOCFGO15<br>IOCFGI15                      | IOCFGO16<br>IOCFGI16 | IOCFGO17<br>IOCFGI17 |

| A118<br>A128                 | IOCFGO10<br>IOCFGI10<br>MFCFG10                         | IOCFGO11<br>IOCFGI11<br>MFCFG11                         | IOCFGO12<br>IOCFGI12<br>MFCFG12                         | IOCFGO13<br>IOCFGI13<br>MFCFG13                         | IOCFGO14<br>IOCFGI14 | IOCFGO15<br>IOCFGI15                      | IOCFGO16<br>IOCFGI16 | IOCFGO17<br>IOCFGI17 |

| A118<br>A128<br>A138         | IOCFG010<br>IOCFGI10<br>MFCFG10<br>IOCFG030             | IOCFG011<br>IOCFGI11<br>MFCFG11<br>IOCFG031             | IOCFG012<br>IOCFGI12<br>MFCFG12<br>IOCFG032             | IOCFG013<br>IOCFGI13<br>MFCFG13<br>IOCFG033             | IOCFGO14<br>IOCFGI14 | IOCFGO15<br>IOCFGI15<br>MFCFG15<br>-      | IOCFGO16<br>IOCFGI16 | IOCFGO17<br>IOCFGI17 |

| A118<br>A128<br>A138<br>A148 | IOCFG010<br>IOCFGI10<br>MFCFG10<br>IOCFG030<br>IOCFGI30 | IOCFGO11<br>IOCFGI11<br>MFCFG11<br>IOCFGO31<br>IOCFGI31 | IOCFG012<br>IOCFG112<br>MFCFG12<br>IOCFG032<br>IOCFG132 | IOCFG013<br>IOCFG113<br>MFCFG13<br>IOCFG033<br>IOCFGI33 | IOCFGO14<br>IOCFGI14 | IOCFGO15<br>IOCFGI15<br>MFCFG15<br>-<br>- | IOCFGO16<br>IOCFGI16 | IOCFGO17<br>IOCFGI17 |

1. <u>8051 CPU</u>

### 1.1 CPU Register

### ACC (0xE0) Accumulator R/W (0x00)

|    | 7 | 6        | 5 | 4   | 3     | 2 | 1 | 0 |  |  |  |

|----|---|----------|---|-----|-------|---|---|---|--|--|--|

| RD |   | ACC[7-0] |   |     |       |   |   |   |  |  |  |

| WR |   |          |   | ACC | [7-0] |   |   |   |  |  |  |

ACC is the CPU accumulator register and is involved in the direct operations of many instructions. ACC is bitaddressable.

### B (0xF0) B Register R/W (0x00)

|    | 7 | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|----|---|--------|---|---|---|---|---|---|--|--|--|

| RD |   | B[7-0] |   |   |   |   |   |   |  |  |  |

| WR |   | B[7-0] |   |   |   |   |   |   |  |  |  |

B register is used in standard 8051 multiplication and division instructions and is also used as an auxiliary register for temporary storage. B is also bit-addressable.

### PSW (0xD0) Program Status Word R/W (0x00)

|    | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----|----|----|----|-----|-----|----|----|---|

| RD | CY | AC | F0 | RS1 | RS0 | OV | UD | Р |

| WR | CY | AC | F0 | RS1 | RS0 | OV | UD | Р |

| С | Υ                                       | Carry Flag                            |

|---|-----------------------------------------|---------------------------------------|

| Α | C                                       | Auxiliary Carry Flag (BCD Operations) |

| F | 0                                       | General Purpose                       |

| R | IS1, RS0                                | Register Bank Select                  |

| С | V                                       | Overflow Flag                         |

| U | ID                                      | User Defined (reserved)               |

| Ρ | l i i i i i i i i i i i i i i i i i i i | Parity Flag                           |

|   |                                         |                                       |

### SP (0x81) Stack Pointer R/W (0x00)

|    | 7 | 6       | 5 | 4   | 3    | 2 | 1 | 0 |  |  |  |

|----|---|---------|---|-----|------|---|---|---|--|--|--|

| RD |   | SP[7-0] |   |     |      |   |   |   |  |  |  |

| WR |   |         |   | SP[ | 7-0] |   |   |   |  |  |  |

PUSH will result in ACC being written to SP+1 address. POP will load ACC from IRAM with the address of SP.

### ESP (0x9B) Extended Stack Pointer R/W (0x00)

|    | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----------|---|---|---|---|---|---|---|

| RD | ESP[7-0] |   |   |   |   |   |   |   |

| WR | ESP[7-0] |   |   |   |   |   |   |   |

In FLAT address mode, ESP and SP together form a 16-bit address for the stack pointer. ESP holds the higher byte of the 16-bit address.

### STATUS (0xC5) Program Status Word RO(0x00)

| 514105                                                                                                                                                                                                                                              |   |     |     |   |   |   |   |   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|---|---|---|---|---|--|--|--|

|                                                                                                                                                                                                                                                     | 7 | 6   | 5   | 4 | 3 | 2 | 1 | 0 |  |  |  |

| RD                                                                                                                                                                                                                                                  | - | HIP | LIP | - | - | - | - | - |  |  |  |

| WR                                                                                                                                                                                                                                                  | - | -   | -   | - | - | - | - | - |  |  |  |

| HIP High Priority (HP) Interrupt Status<br>HIP=0 indicates no HP interrupt.<br>HIP=1 indicates HP interrupt progressing.<br>LIP Low Priority (LP) Interrupt Status<br>LIP=0 indicates no LP interrupt.<br>LIP=1 indicates LP interrupt progressing. |   |     |     |   |   |   |   |   |  |  |  |

| SPTA1 UART1 Transmit Activity Status                                                                                                                                                                                                                |   |     |     |   |   |   |   |   |  |  |  |

|       | SPTA1=0 indicates no UART1 transmit activity. |

|-------|-----------------------------------------------|

|       | SPTA1=1 indicates UART1 transmit active.      |

| SPRA1 | UART1 Receive Activity Status                 |

|       | SPRA1=0 indicates no UART1 receive activity.  |

|       | SPRA1=1 indicates UART1 receive active.       |

| SPTA0 | UART0 Transmit Activity Status                |

|       | SPTA0=0 indicates no UART0 transmit activity. |

|       | SPTA0=1 indicates UART0 transmit active.      |

| SPRA0 | UART0 Receive Activity Status                 |

|       | SPRA0=0 indicates no UART0 receive activity.  |

|       | SPRA0=1 indicates UART0 receive active.       |

|       |                                               |

The program should check status conditions before entering SLEEP, STOP, IDLE, or PMM modes to prevent the loss of intended functions from delayed entry until these events are finished.

In CS8977, the UART0 and UART1 are not implemented, so the SPTA1, SPRA1, SPTA0, and SPRA0 are reserved.

### 1.2 Addressing Timing and Memory Modes

The clock speed of an MCU with embedded flash memory is usually limited by the access time of on-chip flash memory. While in modern process technology, the CPU can operate much faster and the access time of flash memory is usually around 40 nanoseconds, which becomes a bottleneck for CPU performance. To mitigate this problem, a programmable wait state function is incorporated to allow a faster CPU clock rate to access slower embedded flash memory. The wait state is controlled by WTST register as shown in the following tables.

### WTST (0x92) R/W (0x07)

|    | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|----|---|---|---|---|-------|-------|-------|-------|

| RD | - | - | - | - | WTST3 | WTST2 | WTST1 | WTST0 |

| WR | - | - | - | - | WTST3 | WTST2 | WTST1 | WTST0 |

WTST[3-0]

Wait State Control register. WTST holds the information about Program Memory access

| time  |       |       |       |                        |

|-------|-------|-------|-------|------------------------|

| WTST3 | WTST2 | WTST1 | WTST0 | Access<br>Time(SYSCLK) |

| 0     | 0     | 0     | 0     | 1                      |

| 0     | 0     | 0     | 1     | 2                      |

| 0     | 0     | 1     | 0     | 3                      |

| 0     | 0     | 1     | 1     | 4                      |

| 0     | 1     | 0     | 0     | 5                      |

| 0     | 1     | 0     | 1     | 6                      |

| 0     | 1     | 1     | 0     | 7                      |

| 0     | 1     | 1     | 1     | 8                      |

| 1     | 0     | 0     | 0     | 9                      |

| 1     | 0     | 0     | 1     | 10                     |

| 1     | 0     | 1     | 0     | 11                     |

| 1     | 0     | 1     | 1     | 12                     |

| 1     | 1     | 0     | 0     | 13                     |

| 1     | 1     | 0     | 1     | 14                     |

| 1     | 1     | 1     | 0     | 15                     |

| 1     | 1     | 1     | 1     | 16                     |

The default setting of the wait state control register after reset is 0x07 and the software must initialize the setting to change the wait state setting. Using an SYSCLK of 4MHz, the WTST can be set to a minimum because one clock period is 250ns, which is longer than the typical embedded flash access time. If SYSCLK is above 16MHz, then WTST should be set higher than value 1 to allow enough read access time.

### MCON (0xC6) XRAM Relocation Register R/W (0x00) TA Protected

|    | 7         | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----|-----------|-----------|---|---|---|---|---|---|--|

| RD | MCON[7-0] |           |   |   |   |   |   |   |  |

| WR |           | MCON[7-0] |   |   |   |   |   |   |  |

MCON holds the starting address of XRAM in 2KB steps. For example, if MCON[7-0] = 0x01, the starting address is 0x001000h. MCON is not meaningful in this chip because it only contains on-chip XRAM and MCON should not be modified from 0x00.

In LARGE mode, addressing is compatible with standard 8051 in 16-bit address. FLAT mode extends the program address to 20-bit and expands the stack space to 16-bit data space. The data space is always 16-bit in either LARGE or FLAT mode.

### ACON (0x9D) R/W (0x00) TA Protected

|    | 7 | 6 | 5       | 4 | 3      | 2  | 1   | 0   |

|----|---|---|---------|---|--------|----|-----|-----|

| RD | - | - | IVECSEL | - | DPXREN | SA | AM1 | AM0 |

| WR | - | - | IVECSEL | - | DPXREN | SA | AM1 | AM0 |

ACON is addressing mode control register.

| IVECSEL  | Interrupt Vector Selection                                                                |

|----------|-------------------------------------------------------------------------------------------|

|          | INTVSEC=1 maps the interrupt vector to B000 space.                                        |

|          | INTVSEC=0 maps to normal 0x0000 space.                                                    |

| DPXREN   | DPXR Register Control Bit.                                                                |

|          | If DPXREN is 0, "MOVX, @Ri" instruction uses P2 (0xA0) register and XRAM Address [15-8].  |

|          | If DPXREN is 1, DPXR (0xDA) register and XRAM Address [15-8] is used.                     |

| SA       | Extended Stack Address Mode Indicator. This bit is read-only.                             |

|          | 0 – 8051 standard stack mode where stack resides in internal 256-byte memory              |

|          | 1 – Extended stack mode. The stack pointer is ESP: SP in 16-bit addressing to data space. |

| AM1, AM0 | AM1 and AM0 Address Mode Control Bits                                                     |

|          | 00 – LARGE address mode in 16-bit                                                         |

|          | 1x – FLAT address mode with 20-bit program address                                        |

|          |                                                                                           |

### 1.3 MOVX A, @Ri Instructions

### DPXR (0xDA) R/W (0x00)

|    | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------|---|---|---|---|---|---|---|

| RD | DPXR[7-0] |   |   |   |   |   |   |   |

| WR | DPXR[7-0] |   |   |   |   |   |   |   |

DPXR is used to replace P2[7-0] for high byte of XRAM address bit[15-7] for "MOVX, @Ri" instructions only if DPXREN=1.

### MXAX (0xEA) MOVX Extended Address Register R/W (0x00)

|    | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----|---|-----------|---|---|---|---|---|---|--|

| RD |   | MXAX[7-0] |   |   |   |   |   |   |  |

| WR |   | MXAX[7-0] |   |   |   |   |   |   |  |

MXAX is used to provide the top 8-bit address for "MOVX @Ri" instructions only. MXAX does not affect other MOVX instructions.

When accessing XRAM using "MOVX, @DPTR" instruction, the address of XRAM access is formed by DPHi: DPLi depending on which data pointer is selected. Another form of MOVX instruction is "MOVX, @Ri". This instruction provides an efficient programming method to move content within a 256-byte data block. In "@Ri" instruction, the XRAM address [15-7] can be derived from two sources. If ACON.DPXREN = 0, the high order address [15-8] is from P2 (0xA0), if ACON.DPXREN = 1, the high order address is from DPXR (0xDA) register.

The maximum addressing space of XRAM is up to 16MB, and thus it requires a 24-bit address. For "MOVX, @DPTR", the XRAMADDR [23-16] is from either DPX (0x93) or DPX1 (0x95) depending on which data pointer is selected. For "MOVX, @Ri", the XRAMUADDR [23-16] is from MXAX (0xEA) register.

### 1.4 Dual Data Pointers and MOVX operations

In standard 8051, there is only one data pointer DPH: DPL to perform MOVX. The enhanced CPU provides 2<sup>nd</sup> data pointer DPH1:DPL1 to speed up the move, or to copy data block. The active DPTR is selected by setting DPS (Data Pointer Select) register. Through the control of DPS, efficient programming can be achieved.

### DPS (0x86) Data Pointer Select R/W (0x00)

|    | 7   | 6   | 5   | 4 | 3 | 2 | 1 | 0   |

|----|-----|-----|-----|---|---|---|---|-----|

| RD | ID1 | ID0 | TSL | - | - | - | - | SEL |

| WR | ID1 | ID0 | TSL | - | - | - | - | SEL |

ID[1:0]

SEL

Define the operation of Increment Instruction of DPTR, "INC DPTR". Standard 8051 only has increment DPTR instruction. ID[1-0] changes the definitions of "INC DPTR" instruction and allows flexible modifications of DPTR when "INC DPTR" instructions is executed.

| ID1 | ID0 | SEL=0    | SEL=1     |

|-----|-----|----------|-----------|

| 0   | 0   | INC DPTR | INC DPTR1 |

| 0   | 1   | DEC DPTR | INC DPTR1 |

| 1   | 0   | INC DPTR | DEC DPTR1 |

| 1   | 1   | DEC DPTR | DEC DPTR1 |

TSL Enable toggling selection of DPTR selection. When this bit is set, the selection of DPTR is toggled when DPTR is used in an instruction and executed.

DPTR selection bit. Set to select DPTR1, and clear to select DPTR. SEL is also affected by the state of ID[1:0] and TSL after DPTR is used in an instruction. When read, SEL reflects the current selection of command.

### DPL (0x82) Data Pointer Low R/W (0x00)

|    | 7        | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----|----------|----------|---|---|---|---|---|---|--|

| RD | DPL[7-0] |          |   |   |   |   |   |   |  |

| WR |          | DPL[7-0] |   |   |   |   |   |   |  |

DPL register holds the low byte of data pointer, DPTR.

### DPH (0x83) Data Pointer High R/W (0x00)

|    | 7        | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----|----------|----------|---|---|---|---|---|---|--|

| RD | DPH[7-0] |          |   |   |   |   |   |   |  |

| WR |          | DPH[7-0] |   |   |   |   |   |   |  |

DPH register holds the high byte of data pointer, DPTR.

### DPL1 (0x84) Extended Data Pointer Low R/W (0x00)

|    | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----|---|-----------|---|---|---|---|---|---|--|--|

| RD |   | DPL1[7-0] |   |   |   |   |   |   |  |  |

| WR |   | DPL1[7-0] |   |   |   |   |   |   |  |  |

DPL1 register holds the low byte of extended data pointer 1, DPTR1.

### DPH1 (0x85) Extended Data Pointer High R/W (0x00)

|    | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|----|---|-----------|---|---|---|---|---|---|--|--|--|

| RD |   | DPH1[7-0] |   |   |   |   |   |   |  |  |  |

| WR |   | DPH1[7-0] |   |   |   |   |   |   |  |  |  |

DPH1 register holds the high byte of extended data pointer 1, DPTR1.

### DPX (0x93) Data Pointer Top R/W (0x00)

|    | 7 6 5 4 3 2 1 |  |  |  |  |  |  | 0 |

|----|---------------|--|--|--|--|--|--|---|

| RD | DPX[7-0]      |  |  |  |  |  |  |   |

| WR | DPX[7-0]      |  |  |  |  |  |  |   |

DPX is used to provide the top 8-bit address of DPTR for addresses above 64KB. The lower 16-bit address is formed by DPH and DPL. DPX is not affected in LARGE mode and will form a full 24-bit address in FLAT mode, meaning auto increment and decrement when DPTR is changed. DPX value has no effect if on-chip data memory is less than 64KB.

### DPX1 (0x95) Extended Data Pointer Top R/W (0x00)

|    | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----|---|-----------|---|---|---|---|---|---|--|--|

| RD |   | DPX1[7-0] |   |   |   |   |   |   |  |  |

| WR |   | DPX1[7-0] |   |   |   |   |   |   |  |  |

DPX1 is used to provide the top 8-bit address of DPTR for addresses above 64KB. The lower 16-bit address is formed by DPH1 and DP1L. DPX1 is not affected in LARGE mode and will form a full 24-bit address in Flat mode, meaning auto increment and decrement when DPTR is changed. DPX1 value has no effect if on-chip data memory is less than 64KB.

### 1.5 Interrupt System

The CPU implements an enhanced Interrupt Control that allows a total of 15 interrupt sources and each with two programmable priority levels. The interrupts are sampled at the rising edge of SYSCLK. If interrupts are present and enabled, the CPU enters the interrupt service routine by vectoring to the highest priority interrupt. Among the 15 interrupt sources, 7 of them are from CPU internal integrated peripherals, 6 of them are from on-chip external peripherals, and 2 of them are used for external pin interrupt expansion. When an interrupt is shared, the interrupt service routine must decide which source is requesting the interrupt by examining the corresponding interrupt flag of the sharing peripherals.

The following table shows the interrupt sources and the corresponding interrupt vectors. The Flag Reset column shows whether the corresponding interrupt flag is cleared by hardware (self-cleared) or software. The software can only clear the interrupt flag but not set the interrupt flag. The Natural Priority column shows the inherent priority if more than one interrupt is assigned to the same priority level. Please note that the interrupts assigned with higher priority levels always get serviced first compared with interrupts assigned with lower priority levels regardless of the natural priority sequence.

| Interrupt  | Peripheral Source Description | Vectors (*Note)<br>IVECSEL=0/1 | FLAG RESET | Natural Priority |

|------------|-------------------------------|--------------------------------|------------|------------------|

| PINT0      | Expanded Pin INT0.x           | 0x0003/0xX003                  | Software   | 1                |

| TF0        | Timer 0                       | 0x000B/0xX00B                  | Hardware   | 2                |

| PINT1      | Expanded Pin INT1.x           | 0x0013/0xX013                  | Software   | 3                |

| TF1        | Timer 1                       | 0x001B/0xX01B                  | Hardware   | 4                |

| INT_EUART1 | EUART1                        | 0x0023/0xX023                  | Software   | 5                |

| TF2        | Timer 2                       | 0x002B/0xX02B                  | Software   | 6                |

| INT_EUART2 | EUART2/LIN/LIN_FAULT          | 0x0033/0xX033                  | Software   | 7                |

| I2CM       | I <sup>2</sup> C Master       | 0x003B/0xX03B                  | Software   | 8                |

| INT2       | LVT                           | 0x0043/0xX043                  | Software   | 9                |

| INT3       | Touch Key/ACMP                | 0x004B/0xX04B                  | Software   | 10               |

| INT4       | ADC                           | 0x0053/0xX053                  | Software   | 11               |

| WDIF       | Watchdog WDT1                 | 0x005B/0xX05B                  | Software   | 12               |

| INT6       | PWM/TCC/QE/PWM8               | 0x0063/0xX063                  | Software   | 13               |

| INT7       | SPI/I2C Slave                 | 0x006B/0xX06B                  | Software   | 14               |

| INT8       | T3/T4/T5/BZ                   | 0x0073/0xX073                  | Software   | 15               |

| ECC        | PECC/DECC/WDT2                | 0x007B/0xX07B                  | Software   | 0                |

| BKP | Break Point | 0xX080 | Software | 0 |

|-----|-------------|--------|----------|---|

| DBG | I2CS Debug  | 0xX0C0 | Software | 0 |

\* Note: When IVECSEL=1, the interrupt vector is relocated to the top available 4KB memory space for boot code usage. Therefore, X value is based on the MCU embedded flash size like X=F, for 64K, X=B for 48K, X=7 for 32K, and X=3 for 16K Flash size. In addition to the 15 peripheral interrupts, there are two highest priority interrupts associated with debugging and breakpoint. DBG interrupt is generated when I<sup>2</sup>C slave is configured as a debug port and a debug request from the host matches the debug ID. BKP interrupt is generated when a breakpoint match condition occurs. DBG has a higher priority than BKP. The BKP and DBG interrupts are not affected by the global interrupt enable EA bit of IE register (0xA8).

The interrupt-related registers are listed in the following. Each interrupt can be individually enabled or disabled by setting or clearing the corresponding bit in IE, EXIE, and integrated peripherals' control registers.

# There needs more information to support Break Point and I2CS Debug, please contact us for both applications.

### IE (0xA8) Interrupt Enable Register R/W (0x00)

|    | 7  | 6   | 5   | 4   | 3   | 2       | 1   | 0       |

|----|----|-----|-----|-----|-----|---------|-----|---------|

| RD | EA | ES2 | ET2 | ES0 | ET1 | PINT1EN | ET0 | PINT0EN |

| WR | EA | ES2 | ET2 | ES0 | ET1 | PINT1EN | ET0 | PINT0EN |

EA Global Interrupt Enable bit.

ES2 LIN-capable16550-like EUART2 Interrupt Enable bit.

ET2 Timer 2 Interrupt Enable bit.

ES0 EUART 1 Interrupt Enable bit.

ET1 Timer 1 Interrupt Enable bit.

PINT1EN Pin PINT1.x Interrupt Enable bit.

ET0 Timer 0 Interrupt Enable bit.

PINT0EN Pin PINT0.x Interrupt Enable bit.

### EXIE (0xE8) Extended Interrupt Enable Register R/W (0x00)

|    | 7     | 6     | 5     | 4    | 3     | 2     | 1     | 0     |

|----|-------|-------|-------|------|-------|-------|-------|-------|

| RD | EINT8 | EINT7 | EINT6 | EWDI | EINT4 | EINT3 | EINT2 | EI2CM |

| WR | EINT8 | EINT7 | EINT6 | EWDI | EINT4 | EINT3 | EINT2 | EI2CM |

| EINT8 | INT8 Interrupt Enable bit.                    |

|-------|-----------------------------------------------|

| EINT7 | INT7 Interrupt Enable bit.                    |

| EINT6 | INT6 Enable bit.                              |

| EWD1  | Watchdog Timer Interrupt Enable bit.          |

| EINT4 | INT4 Interrupt Enable bit.                    |

| EINT3 | INT3 Interrupt Enable bit.                    |

| EINT2 | INT2 Interrupt Enable bit.                    |

| EI2CM | I <sup>2</sup> C Master Interrupt Enable bit. |

Each interrupt can be individually assigned to either high or low. When the corresponding bit is set to 1, it indicates it is of high priority.

### IP (0xB8) Interrupt Priority Register R/W (0x00)

|    | 7  | 6           | 5              | 4            | 3        | 2   | 1   | 0   |

|----|----|-------------|----------------|--------------|----------|-----|-----|-----|

| RD | -  | PS2         | PT2            | PS0          | PT1      | PX1 | PT0 | PX0 |

| WR | -  | PS2         | PT2            | PS0          | PT1      | PX1 | PT0 | PX0 |

| Р  | S2 | LIN-capabl  | e 16550-like I | EUART2 Prior | ity bit. |     |     |     |

| Р  | T2 | Timer 2 Pri | ority bit.     |              |          |     |     |     |

PS0 EUART 1 Priority bit.

PT1 Timer 1 Priority bit.

PX1 Pin Interrupt INT1 Priority bit.

PT0 Timer 0 Priority bit.

PX0 Pin Interrupt INT0 Priority bit.

### EXIP (0xF8) Extended Interrupt Priority Register R/W (0x00)

|                                                                                                 | 7                                | 6                                                                                                       | 5     | 4    | 3     | 2     | 1     | 0     |

|-------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-------|-------|-------|-------|

| RD                                                                                              | PINT8                            | PINT7                                                                                                   | PINT6 | PWDI | PINT4 | PINT3 | PINT2 | PI2CM |

| WR                                                                                              | PINT8                            | PINT7                                                                                                   | PINT6 | PWDI | PINT4 | PINT3 | PINT2 | PI2CM |

| PINT8INT8 Priority bit.PINT7INT7 Priority bit.PINT6INT6 Priority bit.PWDIWatchdog Priority bit. |                                  |                                                                                                         |       |      |       |       |       |       |

| P                                                                                               | PINT4<br>PINT3<br>PINT2<br>PI2CM | INT4 Priority bit.<br>INT3 Priority bit.<br>INT2 Priority bit.<br>I <sup>2</sup> C Master Priority bit. |       |      |       |       |       |       |

#### EXIF (0x91) Extended Interrupt Flag R/W (0x00)

|    | 7     | 6           | 5     | 4 | 3     | 2     | 1     | 0      |

|----|-------|-------------|-------|---|-------|-------|-------|--------|

| RD | INT8F | INT7F       | INT6F | - | INT4F | INT3F | INT2F | I2CMIF |

| WR | -     | -           | -     | - | -     | -     | -     | I2CMIF |

| IN | JT8F  | INT8 Flag I | oit   |   |       |       |       |        |

| INT8F  | INT8 Flag bit                                                                     |

|--------|-----------------------------------------------------------------------------------|

| INT7F  | INT7 Flag bit                                                                     |

| INT6F  | INT6 Flag bit                                                                     |

| INT4F  | INT4 Interrupt Flag bit                                                           |

| INT3F  | INT3 Flag bit                                                                     |

| INT2F  | INT2 Flag bit                                                                     |

| I2CMIF | I <sup>2</sup> C Master Interrupt Flag bit. This bit must be cleared by software. |

| Note:  | Writing to INT2F to INT8F has no effect.                                          |

|        |                                                                                   |

The interrupt flags of internal peripherals are stored in the corresponding flag registers in the peripheral and EXIF registers. These peripherals include T0, T1, T2, and WDT. Software needs to clear the corresponding flags located in the peripherals (for T0, T1, T2, and WDT). For I2CM, the interrupt flag is located in the EXIF register bit I2CMIF. This needs to be cleared by software.

INT2 to INT8 is used to connect to the external peripherals. INT2F to INT8F is the direct equivalent of the interrupt flag from the corresponding peripherals. These peripherals include Timer 3, Timer 4, Timer 5, Buzzer, SPI, I2CS, PWMx, TCC, QE, ADC, TKC3, etc.

### WKMASK (0x9F) R/W (0xFF) Wake Up Mask Register TB Protected

|    | 7                                                                   | 6                                                                            | 5                                                                                 | 4                                                                                      | 3                                                                                                            | 2                                                                       | 1                                                        | 0       |

|----|---------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|---------|

| RD | WEINT8                                                              | WEINT7                                                                       | WEINT6                                                                            | WEINT4                                                                                 | WEINT3                                                                                                       | WEINT2                                                                  | WEPINT1                                                  | WEPINT0 |

| WR | WEINT8                                                              | WEINT7                                                                       | WEINT6                                                                            | WEINT4                                                                                 | WEINT3                                                                                                       | WEINT2                                                                  | WEPINT1                                                  | WEPINT0 |

|    | VEINT8<br>VEINT7<br>VEINT6<br>VEINT4<br>VEINT3<br>VEINT2<br>VEPINT1 | Set this bit<br>Set this bit<br>Set this bit<br>Set this bit<br>Set this bit | to allow INT7<br>to allow INT6<br>to allow INT4<br>to allow INT3<br>to allow INT2 | to trigger the<br>to trigger the<br>to trigger the<br>to trigger the<br>to trigger the | wake-up of C<br>wake-up of C<br>wake-up of C<br>wake-up of C<br>wake-up of C<br>wake-up of C<br>wake-up of C | PU from STO<br>PU from STO<br>PU from STO<br>PU from STO<br>PU from STO | P modes.<br>P modes.<br>P modes.<br>P modes.<br>P modes. |         |

| V  | VEPINT0                                                             |                                                                              |                                                                                   |                                                                                        | wake-up of C                                                                                                 |                                                                         |                                                          |         |

WKMASK register defines the wakeup control of the interrupt signals from the STOP mode. The wake-up is performed by these interrupts and the internal oscillator is turned on and SYSCLK resumes if enabled. The interrupt can be set as a level trigger or an edge trigger and the wake-up always runs in accordance with the edge. The wake-up control is wired separately from the interrupt logic, and therefore, after waking up, the CPU does not necessarily enter the interrupt service routine if the corresponding interrupt is not enabled. In this case, the CPU continues onto the next instruction, which initiates the STOP mode. Extra attention should be exerted on the modes of exit and re-entry to ensure proper operation.

All clocks are stopped in STOP/SLEEP mode. Hence, the peripherals that require a clock such as Timer 3, Timer 4, Buzzer, SPI, PWMx, EUART1, ADC, and LVD cannot perform a wake-up function. Only external pins and peripherals that do not require a clock or use SOSC32KHz clock, can be used for wakeup purposes. Such peripherals are like I2CS2, LIN, WDT2, Timer 5, and TKC3

PINT0 and PINT1 are used for external GPIO pin Interrupts. All GPIO pins can be enabled to generate the PINT0 or PINT1 depending on its MFCFG register setting. Each GPIO pin also contains the rising/falling edge detections and either one or both edges can be used for interrupt triggering. The same signaling can be used for generating wake-up.

### TCON (0x88) R/W (0x00)

|                                                                                                                                                                                                                                                                                                                                                                                 | 7     | 6        | 5   | 4   | 3      | 2 | 1               | 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-----|-----|--------|---|-----------------|---|

| RD                                                                                                                                                                                                                                                                                                                                                                              | TF1   | TR1      | TF0 | TR0 | PINT1F | - | PINT0F          | - |