#### **PRODUCTION DATASHEET**

#### DESCRIPTION

The LX27901 is a high performance LED controller optimized for LCD-TV and other be realized by inputting a dimming pulse multi-lamp LCD display systems and provides a cost competitive solution for off-PFC LED drive applications.

The controller provides a pair of PWM drive signals with adequate capacity to drive a half bridge or other double ended DC to DC converter circuit with the addition of simple external circuitry to provide safety isolation.

The device includes a regulated 5.25V output (VDD) activated by the ENABLE input working from the VIN input voltage of up to 27V. VDD is capable of providing 5mA source current to external circuitry while supplying the on chip driver stage and the control circuitry.

The controller allows the user to utilize two different converter drive schemes, LLC resonant or PWM control mode, selected by the signal level at ENABLE pin, to best fit a wide spectrum of application needs.

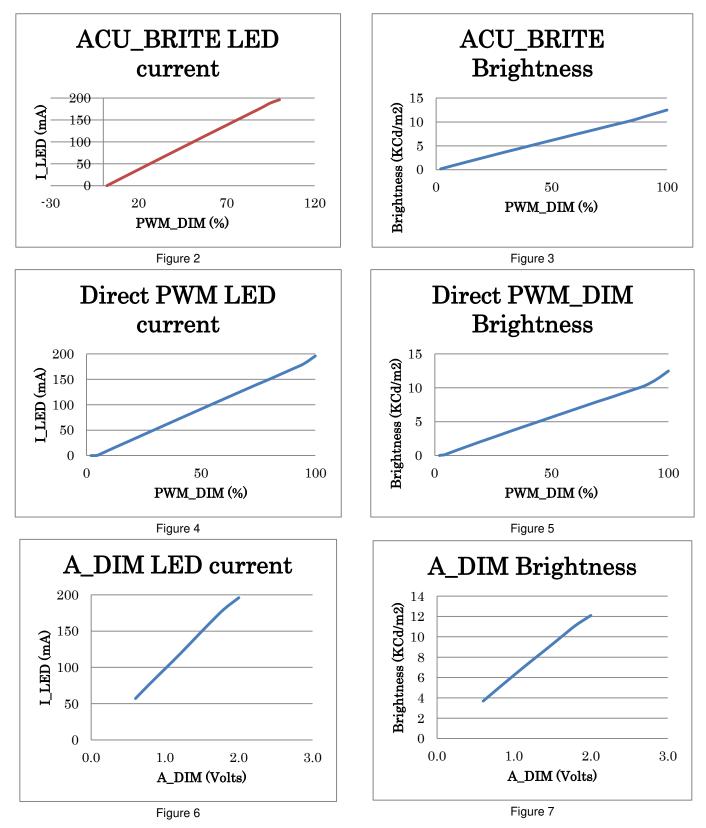

In addition, a proprietary ACU BRITE algorithm is incorporated in the dimming control operation to allow the user to adaptively adjust the PWM dimming duty to achieve accurate brightness control over a wide dimming duty cycle range while maintaining the highest operating efficiency.

The LX27901 supports analog LED current control utilizing the BRTA pin as the analog LED current setting function.

Direct PWM input dimming operation can train to DIM pin directly.

The ACU\_BRITE algorithm allows the DC to DC converter to be turned off when the digital dimming operation is at off state to eliminate no-load power losses. The controller also provides a proprietary synchronous regulation function to allow the user to control the LED current and dimming operation from an un-regulated switching power supply source to minimize the number of power conversion stages and the associated losses and component costs. In synchronous regulation mode, AOUT and BOUT form a pair of drive signals to control the LED string pairs in AC current mode, and COUT provides another option to control the LED in DC current mode.

A versatile set of system monitoring and protection functions are incorporated in the LX27901 design to provide reliable protection of the device and the system. Three input pins, ISNS, VSNS and UVS/SYN are assigned to support the regulation and protection sense feedback needs over wide range of application configurations. Likewise a dedicated fault indication pin allows the user to generate a direct fault report to the system and configure addition protection features with simple external circuits.

The device is available in 16 lead SOIC surface mount package in the industrial temperature range.

#### **KEY FEATURES**

LX27901

- Three Selectable Drive Modes to Support Wide Range of Topologies

- Optimized Solution for Off PFC LED **Drive Applications**

- 0.8A Source & Sink Drive Capacity

- On Chip 5.25V Regulator

- Direct Connection to Input Voltage up to 27V

- ACU BRITE Algorithm to Provide Accurate Brightness Control at Highest Operating Efficiency Over Wide Dimming Duty Range

- User Selectable Dimming Mode Control

- Synchronous Regulation Function to Minimize Power Conversion Stage

- Accurate LED Current Matching In Combination With Microsemi's Nondissipative Balancing Technology

- · Robust Operation at Open and Short LED Conditions

- Compensated External and Internal **PWM Dimming Operation**

- Dedicated Fault Indication

- LED Current and Voltage Monitoring

- RoHS Compliant & Halogen Free

#### APPLICATIONS

- LCD LED Backlight TV

- LCD LED Backlight Monitors

- Other LED Backlight Systems

IMPORTANT: For the most current data, consult MICROSEM's website: http://www.microsemi.com

|                     | PACKAGE ORDER INFO                                                                               | THERMAL DATA                                                                                                                                                                            |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| T <sub>A</sub> (°C) | Plastic SOIC 16 Pin                                                                              | $\theta_{\rm JA} = 82.2 \ {\rm ^{o}C/W}$                                                                                                                                                |  |  |  |

|                     | RoHS Compliant / Pb-free                                                                         | THERMAL RESISTANCE-JUNCTION TO AMBIENT                                                                                                                                                  |  |  |  |

| -40 to +85          | LX27901ID                                                                                        | Junction Temperature Calculation: $T_J = T_A + (P_D x \theta_{JA})$ .<br>The $\theta_{JA}$ numbers are guidelines for the thermal performance of the device/pc-board system. All of the |  |  |  |

| No                  | te: Available in Tape & Reel. Append the letters "TR" to the part number.<br>(i.e. LX27901ID-TR) | above assume no ambient airflow. $\theta_{JA}$ number above is with 4-layer pcb board.                                                                                                  |  |  |  |

## Microsemi.

## LX27901

## High Performance LED Controller

#### **PRODUCTION DATASHEET**

#### ABSOLUTE MAXIMUM RATINGS

| Supply Input Voltage, VIN                              | 0.3V to 36V           |

|--------------------------------------------------------|-----------------------|

| Signal Outputs, VDD, AOUT, BOUT, C_OUT                 |                       |

| Signal Inputs, C_R, BRTA                               |                       |

| Signal Inputs, ENABLE, DIM, ISNS, VSNS, UVS/SYN        | 0.3V to VDD+0.3V      |

| Signal Outputs COMP, SST/BCOM, FAULT                   | 0.3V to VDD           |

| Maximum Junction Temperature                           |                       |

| Storage Temperature Range                              | 65°C to 150°C         |

| Peak Package Solder Reflow Temperature (40 seconds max | kimum exposure) 260°C |

| Lead Temperature. (Soldering 10 seconds)               |                       |

Notes: Exceeding these ratings could cause damage to the device. All voltages are with respect to GND. Currents are positive into, negative out of specified terminal. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

#### LX27901ID

D PACKAGE

(Top View) RoHS / Pb-free Matte Tin Pin Finish

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise listed, the following specifications apply over the operating ambient temperature of -40 °C < Temp < 85 °C, and VIN = 7.5V to 27V, except where otherwise noted and the following test conditions: VIN = 12V,  $C_{C_R}$  = 330pF,  $R_{C_R}$  = 15k $\Omega$

| Parameters                              | Symbol               | Test Conditions/Comments                                | MIN  | TYP  | MAX  | Units |

|-----------------------------------------|----------------------|---------------------------------------------------------|------|------|------|-------|

| Power                                   | -                    |                                                         |      | •    | •    |       |

| Controller Input Voltage                | VIN                  |                                                         | 7.5  |      | 27   | V     |

| Controller Operating Voltage            | VDD                  | $1\mu F$ bypass cap on VDD pin,<br>$I_{VDD} = 0$ to 5mA | 5.0  | 5.25 | 5.5  | V     |

| Power Supply Input Current              | IIN                  | AOUT, BOUT = no load, VDD = no load                     |      | 7    | 10   | mA    |

| Sleep Mode Current                      | IDD <sub>SLEEP</sub> | $VIN = 24V, V_{ENABLE} < 0.8V$                          |      | 200  | 400  | μA    |

| VDD Off Voltage                         |                      | ENABLE < 0.8V                                           |      | 0.1  |      | V     |

| Enable                                  |                      |                                                         | ·    |      |      | -     |

| ENABLE On                               | EN <sub>H</sub>      |                                                         | 1.7  |      |      | V     |

| Shut Down                               | ENL                  |                                                         |      |      | 0.8  | V     |

| LLC Resonant Mode<br>Threshold          | V <sub>LLCTH</sub>   | LLC resonant drive mode, VDD = $5.25V\pm0.25V^{\odot}$  | 2    |      | 2.8  | V     |

| PWM Switching Mode<br>Threshold         | V <sub>PWMTH</sub>   | PWM switching drive mode, VDD = 5.25V±0.25V             | 3.2  | 3.5  | 3.7  | V     |

| Synchronous LED Drive Mode<br>Threshold | V <sub>SYN</sub>     | Synchronous LED drive mode, VDD = 5.25V±0.25V           | 4.3  |      | VDD  | V     |

| Input High Current                      | ENIIH                | ENABLE = 2V                                             |      |      | 10   | μA    |

| Input Low Current                       | ENIIL                | $0V < V_{ENABLE} < 0.8V$                                |      |      | 5    | μA    |

| Under Voltage Lockout                   |                      |                                                         |      |      |      |       |

| VDD Startup Threshold                   | VDD <sub>UVLOR</sub> | Rising Threshold.                                       | 4.3  | 4.6  | 4.9  | V     |

| VDD UVLO Threshold                      | VDD <sub>UVLOF</sub> | Falling Threshold.                                      | 3.95 | 4.25 | 4.55 | V     |

| VDD UVLO Hysteresis                     | VDD <sub>UVLOH</sub> |                                                         |      | 0.4  |      | V     |

<sup>(1)</sup> NOTE: The LX27901 operates at LLC mode when the Enable voltage  $\geq 1.7V$  @ VIN=12V

## High Performance LED Controller

#### **PRODUCTION DATASHEET**

| Unless otherwise listed, the following s | pecifications appl      | <b>ELECTRICAL CHARACTERISTICS</b><br>y over the operating ambient temperature of -40°C < Temp < 8                                                                         | 35°C, and V | 'IN = 7.5V | to 27V, exc | ept  |

|------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|------|

| where otherwise noted and the followin   | g test conditions:      | VIN = 12V, $C_{C,R}$ = 330pF, $R_{C,R}$ = 15k $\Omega$<br>Test Conditions/Comments                                                                                        | 1           | 1          | 1           | 1    |

| Parameters                               | Symbol                  | Test Conditions/Comments                                                                                                                                                  | MIN         | TYP        | MAX         | Unit |

| Output                                   |                         |                                                                                                                                                                           | 1           | 1          | 1           |      |

| Output Resistance                        | R <sub>SINK</sub>       | $I_{SINK}$ , AOUT and BOUT, $T_A = 25^{\circ}C$                                                                                                                           |             | 5          | 6           | Ω    |

| Output Resistance                        | R <sub>SOURCE</sub>     | $I_{SOURCE}$ , AOUT and BOUT, $T_A = 25^{\circ}C$                                                                                                                         |             | 5          | 6           | Ω    |

| Dead Time                                | OUT <sub>DT</sub>       | $T_A = 25^{\circ}C$ , at full duty                                                                                                                                        | 270         | 350        | 430         | ns   |

| C_OUT Output Resistance                  | $R_{C_{OUT}}$           | Source and sink                                                                                                                                                           |             | 10         | 20          | Ω    |

| Switching Frequency Oscil                | llator                  |                                                                                                                                                                           |             |            |             |      |

| Switching Frequency<br>Tolerance         | OSCIN                   | $T_A = 25^{\circ}C$ , Frequency of AOUT, BOUT in PWM mode, $C_C = 330pF$ , $R_C = 15K$ .                                                                                  | 138         | 150        | 162         | kH   |

| LLC Frequency Control<br>Current Source  |                         | V <sub>ENABLE</sub> < 2.8V                                                                                                                                                | 0           | 160        |             | μA   |

| Ramp Valley Voltage                      | OSCVV                   |                                                                                                                                                                           |             | 0.5        |             | V    |

| Ramp Peak Voltage                        | OSCPV                   |                                                                                                                                                                           |             | 2.5        |             | V    |

| Synchronization Range                    |                         | Ratio of UVS/SYN input over C_R oscillator<br>free run frequency                                                                                                          | 1.05        |            | 3           | Rat  |

| LED Dimming Control                      |                         |                                                                                                                                                                           |             |            |             |      |

| ISNS Reference                           | ISNS <sub>REF</sub>     | $T_A = 25^{\circ}$ C, input, Corresponds to 2V after 4.75X internal amplifier.                                                                                            | 414.6       | 421        | 427.4       | ۳۱   |

| ISNS Linear Input Range                  |                         | Linear operation range for internal circuit                                                                                                                               | 600         |            |             | m۱   |

| BRTA Input Range                         |                         | 4.75X of ISNS signal. Input outside the range is clamped at upper or lower limit internally.                                                                              | 0.5         |            | 2.0         | V    |

| Pre-Amplifier Gain                       | K <sub>PRAMP</sub>      |                                                                                                                                                                           |             | 4.75       |             |      |

| Error Amp Output Capacity                |                         | Source and Sink                                                                                                                                                           |             | 100        |             | μA   |

| DIM Input Voltage Range                  | V <sub>DIM</sub>        | Effective for duty from 0 to 100%                                                                                                                                         | 0.5         |            | 2.0         | V    |

| PWM Dimming Mode Control<br>Threshold    | Vpdmodeth               | Voltage level of FAULT pin, in ACU_BRITE<br>PWM dimming mode when below threshold; in<br>conventional PWM dimming mode when<br>above threshold.                           | 2.8         | 3.0        | 3.2         | v    |

| Fault Monitoring and Prote               | ction                   |                                                                                                                                                                           |             |            |             |      |

| VSNS Threshold                           | $VSNS_{TH}$             |                                                                                                                                                                           | 1.8         | 2.0        | 2.2         | V    |

| ∆VCOMP Voltage                           | V <sub>VCOMP_diff</sub> | Vcomp2 when the Aout present @ Vsns=0V,<br>ISNS=0.15V; Vcomp1 when the Aout disabled<br>@ Vsns=3V, ISNS=0V; $T_A = 25^{\circ}C$<br>$\Delta$ VCOMP Voltage=Vcomp2 – Vcomp1 | 0.1         |            |             | v    |

| UVS/SYN Threshold                        | UVS/SYN <sub>TH</sub>   | Fault when below the threshold, positive and negative input                                                                                                               | 0.33        | 0.4        | 0.45        | V    |

| UVS/SYN Input Range                      | V <sub>UVS/SYN</sub>    | Functional operation range, positive and negative input                                                                                                                   | -0.5        |            | 4           | V    |

| ISNS Fault Threshold                     | VISNSTH                 | Fault when below the threshold                                                                                                                                            | 90          | 110        | 130         | ۳    |

| Over Current Threshold                   | OC <sub>TH</sub>        | Upper threshold for ISNS input                                                                                                                                            | 580         | 630        | 680         | ۳    |

| Short Circuit Threshold                  | SCTH                    | Upper threshold for ISNS input                                                                                                                                            | 940         | 1000       | 1060        | ۳    |

|                                          | 1                       |                                                                                                                                                                           | 1           | 1          | 1           | 1    |

LX27901

www.*Microsemi*.com

Copyright © 2011 Rev. 1.1

## High Performance LED Controller

#### **PRODUCTION DATASHEET**

#### **ELECTRICAL CHARACTERISTICS**

| Unless otherwise listed, the following specifications apply over the operating ambient temperature of -40°C < Temp < 85°C, and VIN = 7.5V to 27V, except where otherwise noted and the following test conditions: VIN = 12V, C <sub>C R</sub> = 330pF, R <sub>C R</sub> = 15k $\Omega$ |                                                                                  |                                                                                 |   |       |       |       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|-------|-------|-------|--|--|

| Parameters Symbol Test Conditions/Comments MIN TYP MAX U                                                                                                                                                                                                                               |                                                                                  |                                                                                 |   |       |       |       |  |  |

| Fault Count                                                                                                                                                                                                                                                                            | FC                                                                               | At clock frequency of AOUT, BOUT                                                |   | 256   |       | Count |  |  |

| Fault reset Interval F <sub>RESET_1</sub> Interval for resetting fault counter after POR, At clock frequency of AOUT, BOUT 32768                                                                                                                                                       |                                                                                  |                                                                                 |   |       | Count |       |  |  |

| Fault reset Interval                                                                                                                                                                                                                                                                   | F <sub>RESET_R</sub>                                                             | Periodic Interval for resetting fault counter, At clock frequency of AOUT, BOUT |   | 65536 |       | Count |  |  |

| Fault Output Sinking Capacity                                                                                                                                                                                                                                                          | F <sub>SINK</sub>                                                                | VFAULT ≤ 0.8V, TA = 25°C                                                        | 4 | 6     |       | mA    |  |  |

| Fault Output Open Impedance                                                                                                                                                                                                                                                            | R <sub>F</sub>                                                                   | When in open state                                                              | 5 |       |       | MΩ    |  |  |

| Bias & References                                                                                                                                                                                                                                                                      | Bias & References                                                                |                                                                                 |   |       |       |       |  |  |

| Soft Start Charging Source                                                                                                                                                                                                                                                             | coft Start Charging Source I <sub>SSC</sub> C_B Charging source at start up 2 μA |                                                                                 |   |       |       |       |  |  |

| Power-Up Sequencing                                                                                                                                                                                                                                                                    |                                                                                  |                                                                                 |   |       |       |       |  |  |

| Start up Time Out                                                                                                                                                                                                                                                                      | TSTART                                                                           | After POR                                                                       |   | 32768 |       | Count |  |  |

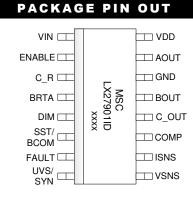

| Name         | Pin # | FUNCTIONAL PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | Pin # | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VIN          | 1     | Input voltage pin. A built-in regulator is connected to this pin to step down the input voltage to the internal operating voltage VDD. This pin can accept input voltage from 7.5V to 27V to provide the flexibility of interfacing with either 12V or 24V system supply. A low ESR decoupling capacitor of not less than $1\mu$ F should be connected from this pin to GND with low impedance traces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ENABLE       | 2     | Enable pin to control the on/off operation of the controller. A logic low signal <0.8V on this pin sets the controller in sleep mode to save energy, and a signal > 1.7V activates the controller operation. The DC signal level on this pin also sets the drive mode of the controller. With VDD= $5.25V\pm5\%$ , when $1.7V < V_{ENABLE} < 2.8V$ the AOUT, BOUT signal is set in LLC resonant drive mode; when $3.2V < V_{ENABLE} < 3.7V$ the controller drives the power converter in normal PWM drive mode; and when $V_{ENABLE} > 4.3V$ the controller is set in synchronous LED drive mode.                                                                                                                                                                                                                                                                                             |

| C_R          | 3     | Converter operating frequency programming terminal. A pull-up resistor from this pin to VDD and a capacitor connected from this pin to ground determines the operating frequency of the inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BRTA         | 4     | Terminal for programming the analog LED current setting. An analog signal is accepted from this pin to set the reference level for the LED current control loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DIM          | 5     | PWM dimming control input. $V_{DIM} > 2V$ sets the dimming operation in continuous analog mode. A PWM signal of low level <0.5V and high level > 2V will force the PWM dimming operation to follow the PWM signal directly. Input level <0.5V will stop the controller output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SST/BCOM     | 6     | For PWM dimming brightness compensation and soft start. The elapsed dimming demand and the accumulated LED current over the active dimming period are compared at this pin. The comparison result is used to control the LED light output to exactly match the dimming demand with compensation for the distortion of the LED current during dimming operation. At start up this pin is connected to a $2\mu$ A charging current source to control the soft start process. An internal active pull down circuit is connected from this pin to COMP to force the COMP voltage rise slowly with the charge of the capacitor at this pin. Soft start completes when the voltage rises to 2.5V and the control enters normal operation mode. The $2\mu$ A charging source and the COMP pull down circuit are disconnected then, and this pin is connected to the brightness compensation circuit. |

| FAULT        | 7     | Fault indication pin with open drain output. Internally pulled down when an open LED string.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| right @ 2011 |       | Miaracomi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

www.Microsemi.com

## High Performance LED Controller

**PRODUCTION DATASHEET**

|              |          | FUNCTIONAL PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | Pin #    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |          | severely shorted LED string, over voltage of the LED strings, or over current occurs. Once latched, the fault signal can only be reset by ENABLE or power recycling. The voltage level at this pin during normal operation also sets the operation mode of dimming control. When the voltage is above 3V the COMP signal is turned on and off by the digital dimming control signal and AOUT, BOUT and C_OUT are turned on and off accordingly by the COMP signal. When the voltage at the FAULT pin is below 3V the COMP signal is turned on and off by the control signal from the ACU_BRITE dimming control algorithm, and AOUT, BOUT and C_OUT are turned on and off accordingly by the COMP signal. The voltage level of this pin during normal operation can be set by an external resistive divider.                                                                                                                                                                                                                                                                                                                                   |

| UVS/SYN      | 8        | Sense for under voltage conditions. A threshold of 0.4V is set internally to compare the sense feedback signal to this pin when the LED strings are on. A fault will be declared if the sensed signal stays below the threshold over certain counts set by the internal circuitry. LED string current and voltage sense signals can be fed to this pin to detect open or short string conditions. When the controller is set in synchronous regulation mode UVS/SYN will receive the synchronization signal from the power supply to synchronize the switching frequency of AOUT and BOUT. An internal rectifier circuit is included to allow an AC input signal to be connected to this pin directly.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VSNS         | 9        | Voltage sense input pin. The voltage signal on this pin feeds the over voltage detection circuit. A threshold of 2V is set internally for fault detection. When the voltage sense signal reaches the threshold of 2V, a clamping current source will be activated to pull down COMP signal to limit the sensed voltage. In the meanwhile, the fault monitoring circuit will start counting the accumulated fault duration and set up the fault flag when the fault count reaches pre-determined counts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ISNS         | 10       | Current sense input pin. A full wave rectifier circuit is built in to allow AC input to this pin. The regulation point at this pin is 421mV which is amplified by 4.75 times and then fed to the error amplifier to compare with a reference signal of 2V to regulate the LED current. This signal is also used to detect open LED, over current and short circuit conditions. The threshold for open LED is 110mV, the threshold of over current is 630mV, and the threshold for short circuit is 1000mV. A fault flag will be declared if ISNS signal stays below 110mV or above 630mV over defined counts, and the operation will be cut off immediately when ISNS signal goes above 1000mV.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| COMP         | 11       | Output of the error amplifier. The error amplifier is a Gm type that provides robust control behavior and simple compensation. The signal on this pin feeds to the PWM modulation circuit to control the drive output to regulate the LED current. At start up the voltage of this pin is controlled by the soft start circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| C_OUT        | 12       | Gate signal to drive an additional MOSFET for LED current regulation. The signal is in synchronous with the C_R oscillator frequency and is leading edge modulated by the output of the error amplifier in LLC and synchronous regulation modes and trailing edge modulated in PWM half bridge drive mode. This signal can be used in combination with AOUT and BOUT to extend the regulation range in LLC operation mode or provide additional driving capabilities in synchronous regulation mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AOUT<br>BOUT | 15<br>13 | Gate drive output. These driver outputs are capable of providing 0.8A source and sink current at nominal operating voltage. Dead time is inserted to prevent possible shoot through at full duty cycle when these signals are used for half bridge or full bridge driving. Internal pull down resistors of $20k\Omega$ is provided at each pin. When the controller is in resonant drive mode AOUT and BOUT are driven to maximum duty and their switching frequency varies with COMP signal level; when the controller is in PWM drive mode these two outputs generate pulse width modulated drive signals at fixed frequency; and when the controller is in synchronous LED drive mode, UVS/SYN receives the synchronization signal, AOUT outputs a NFET drive signal in synchronous with the negative cycle of the UVS/SYN input and BOUT outputs a PFET drive signal in synchronous with the negative cycle of the UVS/SYN input to drive respective external power devices to control the LED current directly. Different from the PWM drive mode, the pulse width of AOUT and BOUT is leading edge modulated in synchronous drive mode. |

| GND          | 14       | Ground return of the on chip circuit. It is important to provide a low impedance ground plane to this pin and the signal control circuitry in PCB layout, and not let the ground return current of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## High Performance LED Controller

**PRODUCTION DATASHEET**

|                          | FUNCTIONAL PIN DESCRIPTION |                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name                     | Name Pin # Description     |                                                                                                                                                                                                                                                    |  |  |  |  |

|                          |                            | inverter power circuit flow through the signal ground plane. Low ESR bypass capacitors for VDD and VDD should be connected with lowest possible impedance to this pin through the signal ground plane.                                             |  |  |  |  |

| VDD                      | 16                         | The operating voltage of the IC. A built-in regulator supplies a regulated 5.25V derived from VIN supply to this pin. A low ESR decoupling capacitor of not less than $1\mu$ F should be connected from this pin to GND with low impedance traces. |  |  |  |  |

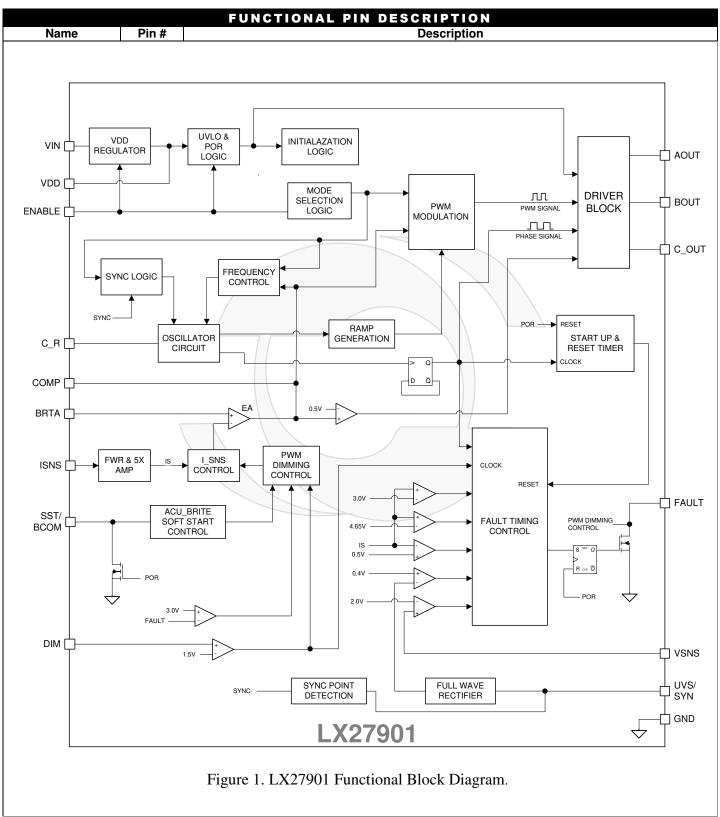

| FUNCTIONAL BLOCK DIAGRAM |                            |                                                                                                                                                                                                                                                    |  |  |  |  |

High Performance LED Controller

**PRODUCTION DATASHEET**

Copyright © 2011 Rev. 1.1 Page 7

# **Microsemi**

## LX27901

High Performance LED Controller

**PRODUCTION DATASHEET**

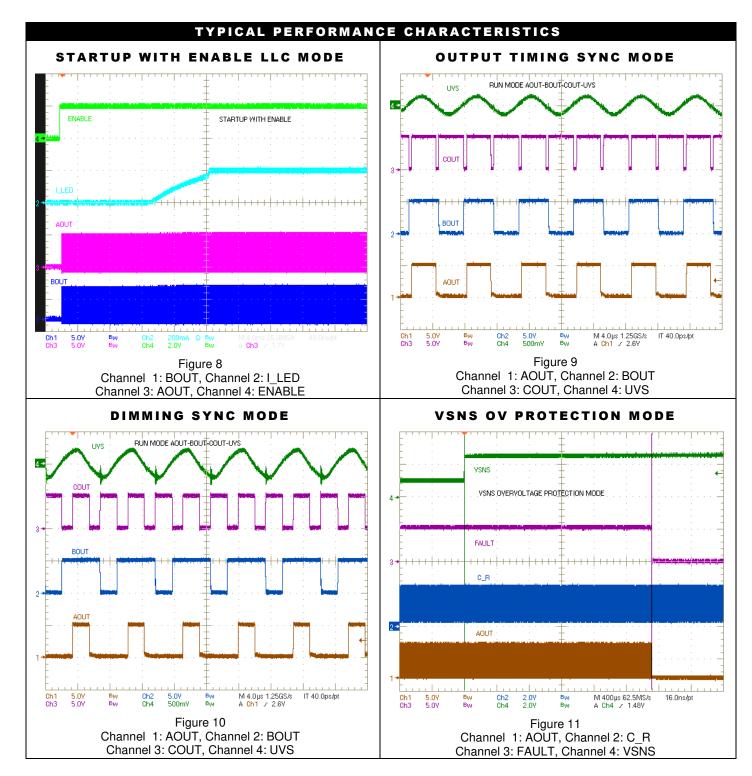

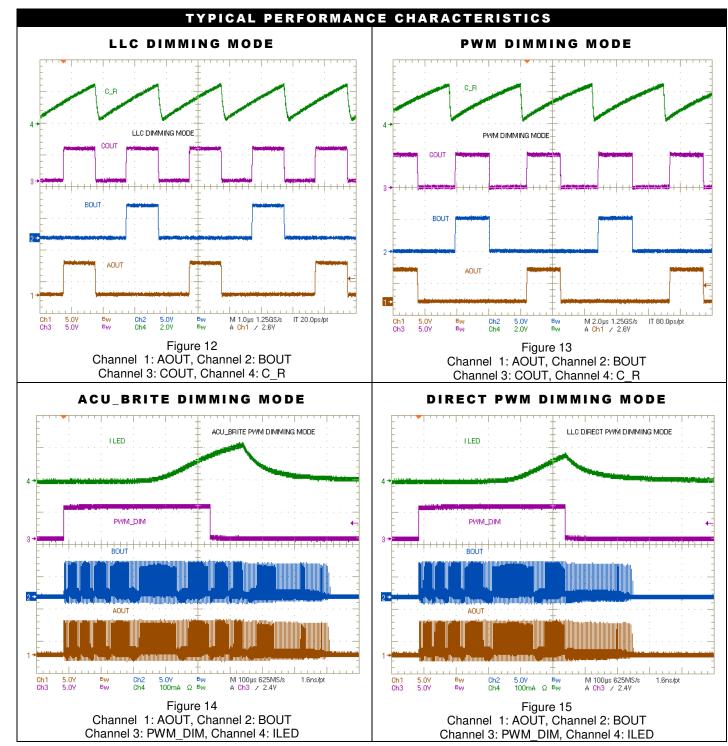

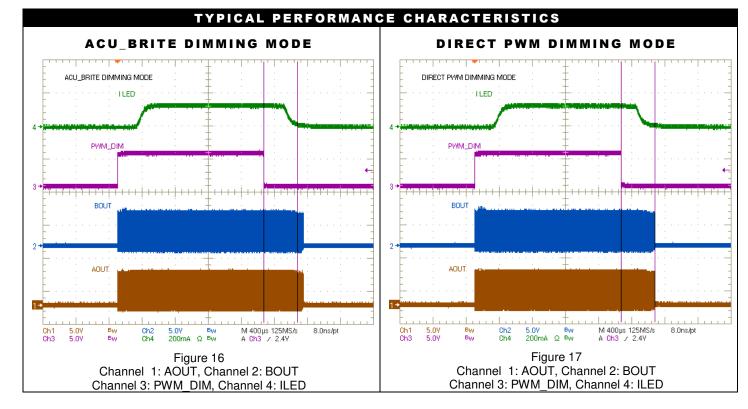

TYPICAL PERFORMANCE CHARACTERISTICS

www.Microsemi.com

LX27901

Copyright © 2011 Rev. 1.1

High Performance LED Controller

**PRODUCTION DATASHEET**

Copyright © 2011 Rev. 1.1

High Performance LED Controller

**PRODUCTION DATASHEET**

High Performance LED Controller

**PRODUCTION DATASHEET**

www.*Microsemi*.com

High Performance LED Controller

**PRODUCTION DATASHEET**

High Performance LED Controller

**PRODUCTION DATASHEET**

#### **PRODUCTION DATASHEET**

#### **OPERATION DESCRIPTION**

#### INTRODUCTION

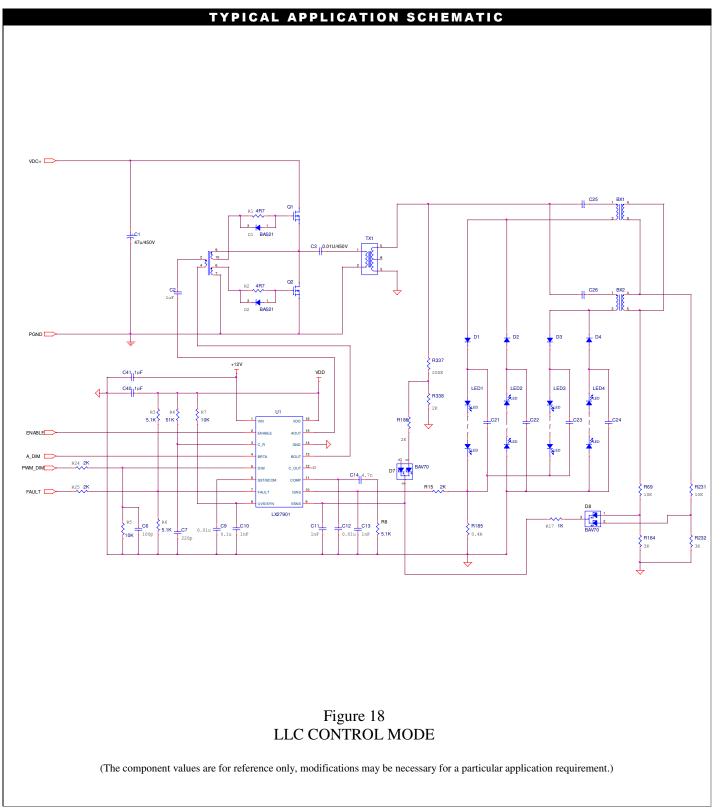

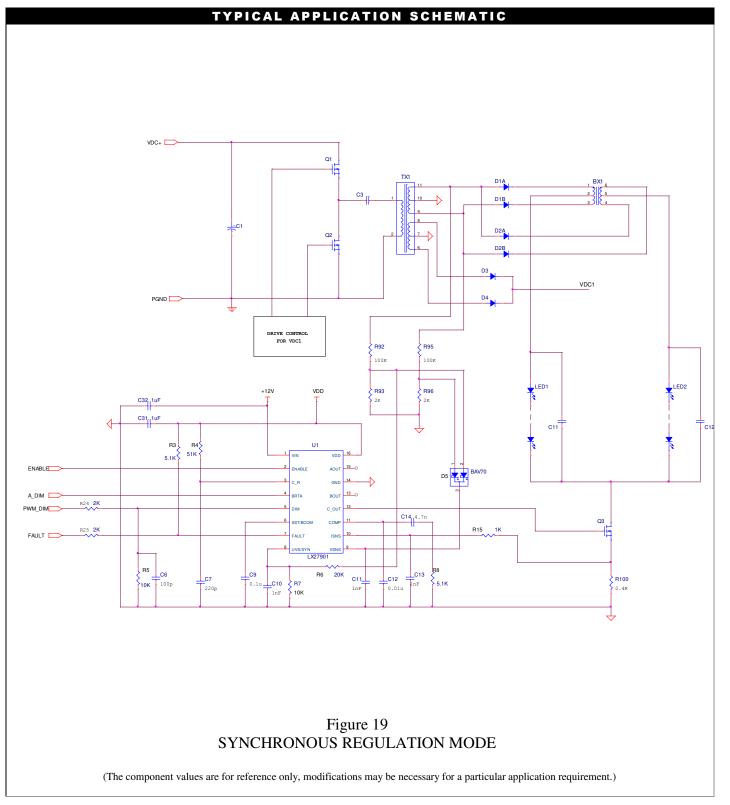

This section describes the operation of LX27901 LED drive controller. LX27901 is primarily designed for LIPS power systems for LED backlit LCD TV and other large screen CCFL backlight applications that addresses the need to drive a half bridge or full bridge inverter stage from the 400V PFC output across the safety isolation barrier. It provides an optimized low cost solution for such applications while providing a set of comprehensive control features to fully satisfy the technical requirements.

#### 1. SYSTEM OVERVIEW

The system contains the following main function blocks:

Power and Start-Up Logic Oscillator and Frequency Control Circuit Regulation Control Circuit Dimming Control Circuit Drive Control Circuitry Fault Detection and Protection Circuitry

The power and start-up logic provides regulated power to the on chip circuitry and controls the start-up sequencing, power on reset, and soft start operation etc. The oscillator and frequency logic generates the clock signals for the LLC and PWM operation and timing for the operation and protection. The regulation and dimming control logic handles the LED current regulation and dimming control operation with Microsemi's proprietary ACU\_BRITE technology to provide accurate brightness control with nondissipative operation of the power devices. The drive control circuit converts the PWM signal from the regulation and control circuit to power drive signals to drive the external power devices of the power supply and LED string control. The fault detection and protection logic monitors the operation of the internal and external circuits and provides fault warning and protection for the system.

#### 2. POWER CONTROL AND START UP

The LX27901 has a built in regulator to step down the input voltage VIN to a regulated 5.25V supply VDD to support the on chip circuitry. The regulator is controlled by the ENABLE signal and is only activated when ENABLE voltage goes above its logic threshold and thus minimizing the power consumption at sleep mode. An UVLO circuit is employed to monitor the VDD voltage. The UVLO circuit releases the lock out function when VDD reaches its rising threshold and initiates the Power On Reset (POR) signal.

The POR signal initializes the whole control circuitry by resetting the counters, registers, fault latch, setting the analog signals such as the SST/BCOM voltage to predetermined initial values, while holding off the output signals to pre-determined inactive states. After the preset delay time the POR signal is released and the controller operation starts.

#### 3. OSCILLATOR AND FREQUENCY CONTROL

The system has a built in switching frequency oscillator to provide ramp signal and clock signal to the power supply LLC and PWM control logic and internal counter-timer etc. A resistor and a capacitor is required to connect between VDD and the switching frequency oscillator programming terminal C\_R and from C\_ R to ground respectively to set the oscillating frequency. A controlled charging current source is also provided internally to the C\_R pin to adjust the oscillator frequency when the ENABLE voltage level is set in LLC resonance control mode. When the ENABLE voltage level is set in PWM mode, the current source is disconnected and the oscillator returns to the free run frequency set by the external RC components.

#### 4. REGULATION CONTROL

The regulation circuit controls the LED current through a closed loop regulation. The LED current is sensed and fed to the ISNS pin as a feedback signal where it is regulated by an internal error amplifier to match the current reference threshold. The error amplifier is a Gm type which is essentially a voltage controlled current source. The output signal feeds the PWM control circuit to adjust the PWM drive signals to control the power device operation of the external power circuit. The output of the error amplifier is also connected to COMP pin to allow the user to adjust the compensation for the control loop with external components connected to this pin. Three power supply control modes are incorporated into the Controller operation: LLC Resonant control mode, PWM control mode, and synchronous regulation mode. In LLC resonant mode the PWM drive output signals AOUT and BOUT remain at full duty cycle, and the output signal from the error amplifier controls the internal charging current source at C\_R pin to adjust the switching frequency of AOUT and BOUT to regulate the LED current. Note that in this mode the operating frequency of the drive signals should be always higher than the resonance frequency of the external power circuit in order to maintain stable regulation of the output.

LX27901

High Performance LED Controller

#### **PRODUCTION DATASHEET**

#### **OPERATION DESCRIPTION**

In PWM control mode the internal current source at C\_R pin is disconnected and AOUT and BOUT signals remain at the fixed frequency set by the RC components at C\_R pin, and the LED current is regulated by adjusting the pulse width of the AOUT and BOUT signals. In synchronous regulation mode the synchronization signal from the power supply is received from UVS/SYN pin and AOUT and BOUT output drive signals in synchronous with the synchronization signal to drive respective external switches in series with the LED strings to control the LED current. In this mode AOUT and BOUT are leading edge modulated PWM drive signals controlled by the closed current loop from ISNS feedback. The three control modes are selectable by the voltage level of ENABLE signal. With VDD= $5.25V\pm5\%$ , when 1.7V<V<sub>ENABLE</sub><2.8V the controller is in LLC resonant drive mode; when  $3.2V \le V_{ENABLE} \le 3.7V$  the controller drives the power supply in PWM drive mode; and when V<sub>ENABLE</sub>>4.3V the controller drives the external device in synchronous regulation mode. Note that when the Enable voltage is reached to 1.7V, it operates at LLC mode.

#### 5. DIMMING CONTROL

The LX27901 supports external burst dimming and analog dimming functions. In external digital dimming mode a dimming pulse train is supplied to DIM pin and the dimming operation follows the input pulse train directly. It is recommended that the high state of the pulse train should be higher than 2V and the low state should be lower than 0.5V. This signal is compared with an internal DC level of 1.5V to generate an internal PWM pulse train to control the burst dimming operation.

A unique feature called ACU\_BRITE is incorporated to compensate the LED current error by digital dimming duty adjustment. A capacitor from SST/BCOM pin to ground provides an integration function for such control. Α controlled charging current source and a controlled discharging current source are connected internally to the SST/BCOM pin. The charging current source is linearly proportional to the internal current regulation reference and turned on and off by the internal digital dimming signal. The discharging current source is proportional to the ISNS signal at the same ratio as the charging source to the internal reference. At power on reset the SST/BCOM capacitor is discharged to zero and the capacitor is used for soft start operation. When the capacitor voltage reaches 2.5V it switches over to ACU\_BRITE dimming control function. The voltage of SST/BCOM is fed to a comparator and compared with a threshold level of 2.5V. When V<sub>SST/BCOM</sub> is greater than 2.5V, the LED current is turned on, and when V<sub>SST/BCOM</sub> is lower than 2.5V, the LED current is turned off.

With such control mechanism the integration of the LED current always matches the integration of its reference over the digital dimming operation to yield an accurate brightness control. This feature essentially enables the control of dimming operation by turning on and off the power supply directly without losing dimming accuracy, instead of putting an additional control device in series with the LED string to control the LED on/off. The LED current distortion at the rising and falling edge of the digital dimming operation is accurately compensated by the dimming duty adjustment, the no load power supply losses at LED off state are eliminated, and the serial control device is removed.

#### 6. DRIVE CONTROL CIRCUIT

The drive control circuit converts the PWM signal from the regulation and control circuit to the drive output signals AOUT, BOUT and C\_OUT to drive the external power devices for the power supply and LED string control. The signals from AOUT and BOUT are 180° out of phase. When the controller is in LLC resonant mode AOUT and BOUT remain at full duty, and their switching frequency varies with the COMP signal level to adjust the power supply output. When the controller is in the PWM control mode AOUT and BOUT remain at a fixed switching frequency but their duty cycle varies with the COMP signal level. When in synchronous regulation mode AOUT outputs a NFET drive signal in synchronous with the positive cycle of the synchronization signal from UVS/SYN pin, and BOUT outputs a PFET drive signal in synchronous with the negative cycle of the synchronization signal from UVS/SYN to drive the external devices. In this mode the AOUT and BOUT signal is a leading edge modulated PWM signal with their falling edge in synchronous with the zero crossing point of the synchronization signal to minimize their turn off transient and their pulse width is controlled by the closed current loop from ISNS feedback. The driving capacity of AOUT and BOUT is 0.8A in both the sourcing and sinking mode.

The signal from C\_OUT provides the user additional control for LED current regulation. The signal is in synchronous with the C\_R oscillator frequency and is leading edge modulated by the output of the error amplifier in LLC and synchronous regulation modes, and trailing edge modulated in PWM half bridge drive mode. This signal can be used in combination with AOUT and BOUT to extend regulation range in LLC operation mode or provide additional driving capabilities in synchronous regulation mode.

#### **PRODUCTION DATASHEET**

#### **OPERATION DESCRIPTION**

#### 7. SOFT START

Soft start is accomplished by internal circuitry in combination with the SST/BCOM capacitor charging control. At power on the SST/BCOM capacitor is discharged to zero during POR. When the operation commences following POR the SST/BCOM pin is disconnected from the dimming control circuit and a small soft start current source of 2  $\mu$ A is turned on to charge the SST/BCOM capacitor slowly.

The voltage of the SST/BCOM capacitor pulls down the COMP signal through the soft start circuit to force the V<sub>COMP</sub> signal to rise slowly together with it. During this course the voltage amplitude of SST/BCOM is monitored. When the SST/BCOM signal rises to 2.5V, the soft start current source is turned off and the SST/BCOM pin switches over to the internal dimming control circuit. The capacitor at SST/BCOM is charged and discharged by the ACU\_BRITE brightness compensation circuit and its voltage is compared with a 2.5V reference to turn on and off the AOUT, BOUT and C\_OUT signals while the COMP signal resumes its role in the regulation function. During start up a timer-counter circuit is also furnished to monitor the system operation. If the ISNS signal does not reach 100mV after the counter reaches the full count of 32k (15 bit) clock cycles, the start-up is considered failed and a fault flag is raised by pulling down the FAULT pin signal.

#### 8. FAULT DETECTION AND PROTECTION

The following system operating conditions are monitored with fault report or protection actions:

- a) Open LED string

- b) Short LED string

- c) Power supply failure

- d) Over voltage

- e) Over current

The above fault conditions are monitored from the ISNS, VSNS and UVS/SYN inputs. The ISNS signal is used to monitor open LED, power supply failure and over current conditions. Open LED detection is disabled during start up until the 15 bit counter times out. After the counter time out if ISNS signal is still below 100mV while the LED is on, it indicates an open LED or power supply failure condition.

A fault counter will start to count the fault. When the counter reaches the full count of 256, a fault condition is confirmed and the FAULT pin is pulled to low state to indicate a fault condition.

The fault counter is incremented by a clock at the same frequency as AOUT, BOUT and reset at 32768 clock pulses and after that it periodically reset at an interval of 65536 clock pulses.

In addition, during the interval if there is any single occurrence of ISNS>110mV it will reset the fault counter and the fault counting has to start all over again. Such reset mechanism guarantees reliable fault detection and prevents noise triggered false fault reporting. The ISNS signal is also used to monitor over current and short circuit conditions.

A typical threshold of 630mV is set for over current detection and a typical threshold of 1000mV is set for short circuit detection. The fault counter will start counting when ISNS>630mV occurs and reports a fault when the counter reaches full count of 256. The Fault counter is reset at 32768 clock cycle and then periodical reset at every 65536 clock cycle interval is also employed.

In addition, a time delay circuit, similar to a one shot, is employed to hold the over current status for about  $50\mu$ s. The fault counter will be reset if the over current condition does not persist when the elapsed holding time is over. When ISNS signal exceeds 1000mV typically it will be recognized as a short circuit. The output signal will be shut off immediately with a fault flag raised. The short circuit detection is active all the time after POR release.

The VSNS signal is used to limit and monitor over voltage condition. When the voltage sense signal reaches the threshold of 2V, a clamping current source will be activated to pull down COMP signal to limit the sensed voltage, and when the comp voltage decreases below 0.5V, then it disables the gate-drive outputs. It provides the regulation operation to keep the output voltage at VSNS 2V.

The UVS/SYN signal provides further means for fault detection. A threshold of 0.4V is set internally for the UVS/SYN signal. When UVS/SYN<0.4V occurs, the fault counter also starts counting and reports a fault condition when the counter reaches full count.

The counter is reset at 32768 clock cycle and then periodical reset at every 65536 clock cycle interval also applies to the UVS/SYN fault count. Similarly a time delay circuit is also employed to hold the over voltage status for about 50 $\mu$ s. The fault counter will be reset if the over current condition does not persist when the elapsed holding time is over.

High Performance LED Controller

**PRODUCTION DATASHEET**

#### APPLICATION INFORMATION

#### SETTING OPERATING FREQUENCY

The switching frequency of AOUT and BOUT is programmed with the external capacitor and resistor, R<sub>C\_R</sub> and C<sub>C\_R</sub>.

$$f \approx \frac{374200}{R_{C_{-R}}^{0.94} \cdot C_{C_{-R}}^{0.91}}$$

$f_{SW}$  is the switching frequency in kHz,  $\mathbf{R}_{C_R}$  is in k $\Omega$ , and  $\mathbf{C}_{C_R}$  is in pF. For most applications, The switching frequency (minimum operating frequency in LLC Mode) is set at less than 150kHz. Normally  $\mathbf{C}_{C_R}$  can be chosen from 220pF to 470pF, and the value of  $\mathbf{R}_{C_R}$  can also be used to adjust the frequency control range in LLC mode. In LLC mode, maximum operating frequency is approximately  $f_{max} \approx 0.84 \times (0.0452 \cdot R_{C_R} + 0.92) \times f_{min}$ , and the ratio  $f_{m=f_{max}/f_{min}}$ , and the operating frequency at arbitrary Vcomp voltage can be expressed as  $f \approx f_{min} \{0.2(6f_m - 1) - 0.4(f_m - 1)V_{comp}\}$

#### SETTING COMP PIN CAPACITOR

An external capacitor  $C_{COMP}$  is connected from this pin to ground to adjust loop response of the inverter module. The error amplifier is a GM type that provides robust control behavior and simple compensation. The ideal current error amplifier compensation depends on the dimming mode operation range. If minimal dimming is required by the application the loop response can be slower, but for wide range digital dimming it must be fast enough to allow the lamp current to get to full amplitude within a few current cycles.

If value of  $C_{COMP}$  is small the gain will be increased and may result in overshoot, and the loop could become unstable. However as the capacitor value is increased it will reduce the gain and the loop response may be too slow. Therefore it is necessary to choose an optimal value, typical recommended values range from 1nF to 10nF, but should be adjusted depending on the application requirements.

### VIN, VDD BYPASS CAPACITOR

The LX27901 has internal Low Dropout Regulator to generate an accurate 5V supply for the internal control circuitry. In order to have stable operation, it is required to provide bypass capacitor with low ESR between both VIN and VDD and ground. It is recommended to use a capacitance of not less than  $1\mu$ F for VIN and  $1\mu$ F for VDD.

#### LAYOUT GUIDELINES

It is important to have a good PCB layout to achieve stable operation. Especially, high voltage section and the power switching section of the circuit layout require particular attention. High voltage section layout also needs to be planned carefully to meet Safety requirement as well as proper isolation from the control circuit. Following are guidelines for inverter PCB layout

- 1) Use a star-ground connection for analog and power ground. Analog ground should be isolated from power ground except one connection point, GND pin.

- 2) Route high speed digital signal traces away from sensitive analog signals.

- 3) Place decoupling cap as close to related pin as possible.

- 4) Make shortest and direct connection from feedback sources.

- 5) Keep short and wide for high current signal paths especially ground.

- 6) Make trace as thick as possible

- 7) Route current sense and voltage divider traces away from high voltage field.

High Performance LED Controller

**PRODUCTION DATASHEET**

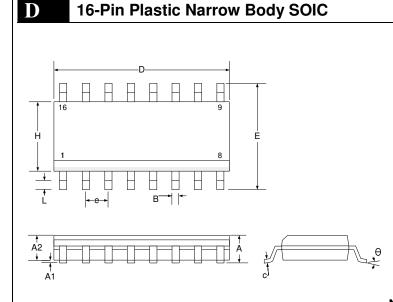

#### PACKAGE DIMENSIONS

|                   | MILLIMETERS |       | INCHES |       |  |  |

|-------------------|-------------|-------|--------|-------|--|--|

| DIM               | MIN         | MAX   | MIN    | MAX   |  |  |

| Α                 | 1.35        | 1.75  | 0.053  | 0.069 |  |  |

| A1                | 0.10        | 0.25  | 0.004  | 0.010 |  |  |

| A2                | 1.25        | 1.52  | 0.049  | 0.060 |  |  |

| b                 | 0.33        | 0.51  | 0.013  | 0.020 |  |  |

| С                 | 0.19        | 0.25  | 0.007  | 0.010 |  |  |

| D                 | 9.78        | 10.01 | 0.385  | 0.394 |  |  |

| E                 | 5.79        | 6.20  | 0.228  | 0.244 |  |  |

| е                 | 1.27        | BSC   | 0.050  | BSC   |  |  |

| Н                 | 3.81        | 4.01  | 0.150  | 0.158 |  |  |

| L                 | 0.40        | 1.27  | 0.016  | 0.050 |  |  |

| Θ                 | 0           | 8     | 0      | 8     |  |  |

| *LC               |             | 0.10  |        | 0.004 |  |  |

| *Lead Coplanarity |             |       |        |       |  |  |

#### Note:

- 1. Controlled dimensions are in mm, inches are for reference only.

- 2. Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage.

**PRODUCTION DATASHEET**

NOTES

Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

PRODUCTION DATA - Information contained in this document is proprietary to