# RENESAS

# DATASHEET

## ISL83080E/82E/83E/85E/86E/88E

±15kV ESD, 5V, Full Fail-Safe, 1/8 Unit Load, RS-485/RS-422 Transceivers

FN6085 Rev 10.01 Jul 5, 2022

The ISL8308xE (ISL83080E, ISL83082E, ISL83083E, ISL83085E, ISL83086E, ISL83088E) are BiCMOS, ESD protected, 5V powered, single transceivers that meet both the RS-485 and RS-422 standards for balanced communication. Each driver output, and receiver input, is protected against  $\pm$ 15kV ESD strikes without latch-up, and unlike competitive products, this family is specified for 10% tolerance supplies (4.5V to 5.5V).

These devices have very low bus currents (+ $125\mu$ A/- $75\mu$ A), so they present a true 1/8 unit load to the RS-485 bus. This allows up to 256 transceivers on the network without violating the RS-485 specification's 32 unit load maximum, and without using repeaters. For example, in a remote utility meter reading system, individual meter readings are routed to a concentrator via an RS-485 network, so the high allowed node count minimizes the number of repeaters required. Data for all meters is then read out from the concentrator via a single access port, or a wireless link.

Receiver (Rx) inputs feature a "Full Fail-Safe" design, which ensures a logic high Rx output if Rx inputs are floating, shorted, or terminated but undriven.

The ISL83080E, ISL83082E, ISL83083E, ISL83085E use slew rate limited drivers which reduce EMI, and minimize reflections from improperly terminated transmission lines, or unterminated stubs in multidrop and multipoint applications. Slew rate limited versions also include receiver input filtering to enhance noise immunity in the presence of slow input signals.

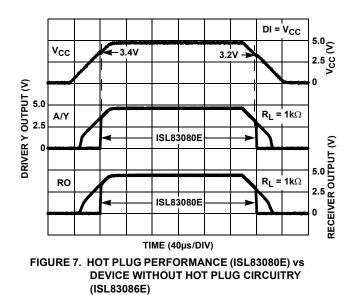

Hot Plug circuitry ensures that the Tx and Rx outputs remain in a high impedance state until the power supply has stabilized, and the Tx outputs are fully short circuit protected.

The ISL83080E, ISL83083E, ISL83086E are configured for full duplex (separate Rx input and Tx output pins) applications. The half duplex versions multiplex the Rx inputs and Tx outputs to allow transceivers with output disable functions in 8 Ld packages.

### Features

- Pb-Free Available (RoHS Compliant)

- Tiny MSOP Packages Save 50% Board Space

- Full Fail-Safe (Open, Short, Terminated and Floating) Receivers

- Hot Plug Circuitry (ISL83080E, ISL83082E, ISL83083E, ISL83085E)

- Tx and Rx Outputs Remain Three-state During Power-up/Power-down

- True 1/8 Unit Load Allows up to 256 Devices on the Bus

- · Specified for Single 5V, 10% Tolerance, Supplies

- High Data Rates..... up to 10Mbps

- -7V to +12V Common Mode Input Voltage Range

- · Half and Full Duplex Pinouts

- · Three-State Rx and Tx Outputs

- Current Limiting and Thermal Shutdown for driver Overload Protection

## Applications

- · Automated Utility Meter Reading Systems

- High Node Count Systems

- Factory Automation

- Field Bus Networks

- · Security Camera Networks

- · Building Environmental Control Systems

- Industrial/Process Control Networks

| PART NUMBER | HALF/FULL<br>DUPLEX | DATA<br>RATE<br>(Mbps) | SLEW-<br>RATE<br>LIMITED? | HOT<br>PLUG | #<br>DEVICES<br>ON BUS | Rx/Tx<br>ENABLE? | QUIESCEN<br>T I <sub>CC</sub> (μΑ) | LOW POWER<br>SHUTDOWN? | PIN<br>COUNT |

|-------------|---------------------|------------------------|---------------------------|-------------|------------------------|------------------|------------------------------------|------------------------|--------------|

| ISL83080E   | Full                | 0.115                  | Yes                       | Yes         | 256                    | Yes              | 530                                | Yes                    | 10, 14       |

| ISL83082E   | Half                | 0.115                  | Yes                       | Yes         | 256                    | Yes              | 530                                | Yes                    | 8            |

| ISL83083E   | Full                | 0.5                    | Yes                       | Yes         | 256                    | Yes              | 530                                | Yes                    | 10, 14       |

| ISL83085E   | Half                | 0.5                    | Yes                       | Yes         | 256                    | Yes              | 530                                | Yes                    | 8            |

| ISL83086E   | Full                | 10                     | No                        | No          | 256                    | Yes              | 530                                | Yes                    | 10, 14       |

| ISL83088E   | Half                | 10                     | No                        | No          | 256                    | Yes              | 530                                | Yes                    | 8            |

#### TABLE 1. SUMMARY OF FEATURES

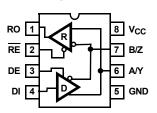

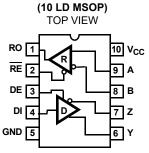

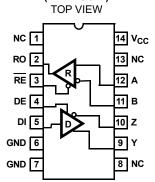

### Pinouts

#### ISL83082E, ISL83085E, ISL83088E (8 LD MSOP, SOIC) TOP VIEW

ISL83080E, ISL83083E, ISL83086E

ISL83080E, ISL83083E, ISL83086E (14 LD SOIC)

## Truth Tables

| TRANSMITTING |        |         |          |         |  |  |  |  |

|--------------|--------|---------|----------|---------|--|--|--|--|

|              | INPUTS | OUTPUTS |          |         |  |  |  |  |

| RE           | DE     | DI      | Z        | Y       |  |  |  |  |

| Х            | 1      | 1       | 0        | 1       |  |  |  |  |

| Х            | 1      | 0       | 1        | 0       |  |  |  |  |

| 0            | 0      | Х       | High-Z   | High-Z  |  |  |  |  |

| 1            | 0      | Х       | High-Z * | High-Z* |  |  |  |  |

NOTE: \*Shutdown Mode (See Note 11).

| RECEIVING |                   |                   |                        |         |  |  |  |  |

|-----------|-------------------|-------------------|------------------------|---------|--|--|--|--|

|           | INPUTS            |                   |                        |         |  |  |  |  |

| RE        | DE<br>Half Duplex | DE<br>Full Duplex | A-B                    | RO      |  |  |  |  |

| 0         | 0                 | Х                 | ≥ <b>-</b> 0.05V       | 1       |  |  |  |  |

| 0         | 0                 | Х                 | ≤ <b>-</b> 0.2V        | 0       |  |  |  |  |

| 0         | 0                 | х                 | Inputs<br>Open/Shorted | 1       |  |  |  |  |

| 1         | 0                 | 0                 | Х                      | High-Z* |  |  |  |  |

| 1         | 1                 | 1                 | Х                      | High-Z  |  |  |  |  |

NOTE: \*Shutdown Mode (See Note 11).

## **Pin Descriptions**

| PIN | FUNCTION                                                                                                                                                        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO  | Receiver output: If A - B $\geq$ -50mV, RO is high; If A - B $\leq$ -200mV, RO is low; RO = High if A and B are unconnected (floating) or shorted.              |

| RE  | Receiver output enable. RO is enabled when $\overline{RE}$ is low; RO is high impedance when $\overline{RE}$ is high.                                           |

| DE  | Driver output enable. The driver outputs, Y and Z, are enabled by bringing DE high. They are high impedance when DE is low.                                     |

| DI  | Driver input. A low on DI forces output Y low and output Z high. Similarly, a high on DI forces output Y high and output Z low.                                 |

| GND | Ground connection.                                                                                                                                              |

| A/Y | ±15kV HBM ESD Protected RS-485/RS-422 level, noninverting receiver input and noninverting driver output. Pin is an input if DE = 0; pin is an output if DE = 1. |

## **Pin Descriptions** (Continued)

| PIN             | FUNCTION                                                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| B/Z             | ±15kV HBM ESD Protected RS-485/RS-422 level, Inverting receiver input and inverting driver output. Pin is an input if DE = 0; pin is an output if DE = 1. |

| А               | ±15kV HBM ESD Protected RS-485/RS-422 level, noninverting receiver input.                                                                                 |

| В               | ±15kV HBM ESD Protected RS-485/RS-422 level, inverting receiver input.                                                                                    |

| Y               | ±15kV HBM ESD Protected RS-485/RS-422 level, noninverting driver output.                                                                                  |

| Z               | ±15kV HBM ESD Protected RS-485/RS-422 level, inverting driver output.                                                                                     |

| V <sub>CC</sub> | System power supply input (4.5V to 5.5V).                                                                                                                 |

| NC              | No Connection.                                                                                                                                            |

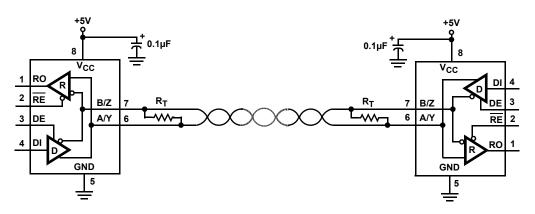

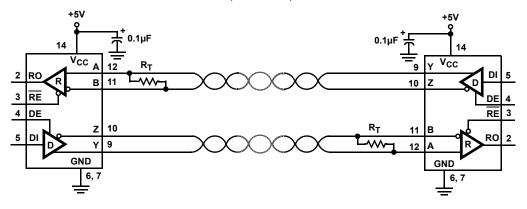

## **Typical Operating Circuit**

ISL83082E, ISL83085E, ISL83088E

ISL83080E, ISL83083E, ISL83086E

### **Ordering Information**

| PART NUMBER (Note 2) | PART MARKING | PACKAGE DESCRIPTION<br>(RoHS Compliant) | PKG. DWG. # | CARRIER TYPE<br>(Note 1) | TEMP. RANGE  |

|----------------------|--------------|-----------------------------------------|-------------|--------------------------|--------------|

| ISL83080EIBZ         | 83080EIBZ    | 14 Ld SOIC                              | M14.15      | Tube                     | -40 to +85°C |

| ISL83080EIBZ-T       |              |                                         |             | Reel, 2.5k               |              |

| ISL83080EIUZ         | 3080Z        | 10 Ld MSOP                              | M10.118     | Tube                     |              |

| ISL83080EIUZ-T       |              |                                         |             | Reel, 2.5k               |              |

| ISL83082EIBZ         | 83082        | 8 Ld SOIC                               | M8.15       | Tube                     |              |

| ISL83082EIBZ-T       | EIBZ         |                                         |             | Reel, 2.5k               |              |

| ISL83082EIUZ         | 3082Z        | 8 Ld MSOP                               | M8.118      | Tube                     |              |

| ISL83082EIUZ-T       |              |                                         |             | Reel, 2.5k               |              |

| ISL83083EIBZ         | 83083EIBZ    | 14 Ld SOIC                              | M14.15      | Tube                     |              |

| ISL83083EIBZ-T       |              |                                         |             | Reel, 2.5k               | -            |

| ISL83083EIUZ         | 3083Z        | 10 Ld MSOP                              | M10.118     | Tube                     |              |

| ISL83083EIUZ-T       |              |                                         |             | Reel, 2.5k               |              |

| ISL83085EIBZ         | 83085        | 8 Ld SOIC                               | M8.15       | Tube                     |              |

| ISL83085EIBZ-T       | EIBZ         |                                         |             | Reel, 2.5k               | -            |

| ISL83085EIUZ         | 3085Z        | 8 Ld MSOP                               | M8.118      | Tube                     |              |

| ISL83085EIUZ-T       |              |                                         |             | Reel, 2.5k               | -            |

| ISL83086EIBZ         | 83086EIBZ    | 14 Ld SOIC                              | M14.15      | Tube                     | -            |

| ISL83086EIBZ-T       |              |                                         |             | Reel, 2.5k               |              |

| ISL83086EIUZ         | 3086Z        | 10 Ld MSOP                              | M10.118     | Tube                     | -            |

| ISL83086EIUZ-T       |              |                                         |             | Reel, 2.5k               |              |

| ISL83088EIBZ         | 83088        | 8 Ld SOIC                               | M8.15       | Tube                     |              |

| ISL83088EIBZ-T       | EIBZ         |                                         |             | Reel, 2.5k               |              |

| ISL83088EIUZ         | 3088Z        | 8 Ld MSOP                               | M8.118      | Tube                     |              |

| ISL83088EIUZ-T       |              |                                         |             | Reel, 2.5k               | 1            |

NOTES:

1. See TB347 for details about reel specifications.

2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matter tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), see the ISL83080E, ISL83082E, ISL83083E, ISL83085E, ISL83086E, ISL83088E product pages. For more information about MSL, see TB363.

#### Absolute Maximum Ratings

| V <sub>CC</sub> to Ground                                        | Thern  |

|------------------------------------------------------------------|--------|

| Input Voltages                                                   | 8 L    |

| DI, DE, RE                                                       | 8 L    |

| Input/Output Voltages                                            | 10     |

| A, B, Y, Z                                                       | 14     |

| A, B, Y, Z (Transient Pulse Through 100 $\Omega$ , Note 14) ±75V | Maxir  |

| RO                                                               | Maxir  |

| Short Circuit Duration                                           | Pb-fre |

| Y, Z                                                             |        |

| ESD Rating Table                                                 | One    |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 4)           | θ <sub>JA</sub> (°C/W) |

|------------------------------------------------|------------------------|

| 8 Ld SOIC Package                              | 105                    |

| 8 Ld MSOP Package                              | 140                    |

| 10 Ld MSOP Package                             | 190                    |

| 14 Ld SOIC Package                             | 128                    |

| Maximum Junction Temperature (Plastic Package) |                        |

| Maximum Storage Temperature Range              | C to +150°C            |

| Pb-free reflow profile                         | . see TB493            |

|                                                |                        |

#### **Operating Conditions**

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

#### NOTE:

4.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See TB379 for details.

| -                                                                                                 | Test Condition<br>Note 6). | ns: V <sub>CC</sub> = 4.5V to 5.5V; Unles                                       | s Otherwise Spe       | ecified. Typ | icals are at    | V <sub>CC</sub> = 5 | V, T <sub>A</sub> = +25 | °C    |

|---------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------|-----------------------|--------------|-----------------|---------------------|-------------------------|-------|

| PARAMETER                                                                                         | SYMBOL                     | TEST CONDIT                                                                     | ONS                   | TEMP<br>(°C) | MIN<br>(Note 5) | ТҮР                 | MAX<br>(Note 5)         | UNITS |

| DC CHARACTERISTICS                                                                                | I                          |                                                                                 |                       |              |                 |                     |                         |       |

| Driver Differential V <sub>OUT</sub> (no load)                                                    | V <sub>OD1</sub>           | R <sub>L</sub> = ∞                                                              |                       | Full         | -               | -                   | V <sub>CC</sub>         | V     |

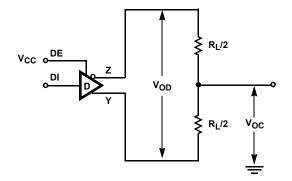

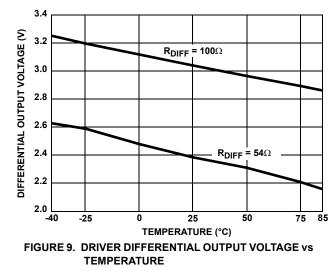

| Driver Differential V <sub>OUT</sub> (with load)                                                  | V <sub>OD2</sub>           | R <sub>L</sub> = 100Ω (RS-422) (Figure                                          | e 1A)                 | Full         | 2               | 2.9                 | -                       | V     |

|                                                                                                   |                            | R <sub>L</sub> = 54Ω (RS-485) (Figure                                           | 1A)                   | Full         | 1.5             | 2.4                 | -                       | V     |

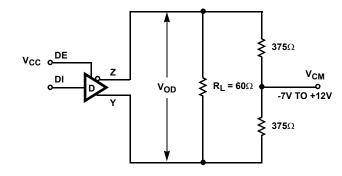

|                                                                                                   |                            | $R_L = 60\Omega, \ \text{-7V} \le V_{CM} \le 12V$                               | (Figure 1B)           | Full         | 1.5             | 2.6                 | -                       | V     |

| Change in Magnitude of Driver<br>Differential V <sub>OUT</sub> for<br>Complementary Output States | ΔV <sub>OD</sub>           | R <sub>L</sub> = 54Ω or 100Ω (Figure 1A)                                        |                       | Full         | -               | 0.01                | 0.2                     | V     |

| Driver Common-Mode V <sub>OUT</sub>                                                               | V <sub>OC</sub>            | $R_L = 54\Omega \text{ or } 100\Omega \text{ (Figure 1A)}$                      |                       | Full         | -               | 2.85                | 3                       | V     |

| Change in Magnitude of Driver<br>Common-Mode V <sub>OUT</sub> for<br>Complementary Output States  | ΔV <sub>OC</sub>           | R <sub>L</sub> = 54Ω or 100Ω (Figure 1A)                                        |                       | Full         | -               | 0.01                | 0.1                     | V     |

| Logic Input High Voltage                                                                          | V <sub>IH</sub>            | DE, DI, RE                                                                      |                       | Full         | 2               | -                   | -                       | V     |

| Logic Input Low Voltage                                                                           | VIL                        | DE, DI, RE                                                                      |                       | Full         | -               | -                   | 0.8                     | V     |

| DI Input Hysteresis Voltage                                                                       | V <sub>HYS</sub>           |                                                                                 |                       | 25           | -               | 100                 | -                       | mV    |

| Logic Input Current                                                                               | I <sub>IN1</sub>           | DE, DI, RE                                                                      |                       | Full         | -2              | -                   | 2                       | μA    |

| Input Current (A, B)                                                                              | I <sub>IN2</sub>           | DE = 0V, V <sub>CC</sub> = 0V or 5.5V                                           | V <sub>IN</sub> = 12V | Full         | -               | 70                  | 125                     | μA    |

|                                                                                                   |                            |                                                                                 | V <sub>IN</sub> = -7V | Full         | -75             | 55                  | -                       | μΑ    |

| Output Leakage Current (Y, Z) (Full                                                               | I <sub>IN3</sub>           | $\overline{\text{RE}} = 0$ V, DE = 0V, V <sub>CC</sub> = 0V                     | V <sub>IN</sub> = 12V | Full         | -               | 7                   | 125                     | μA    |

| Duplex Versions Only)                                                                             |                            | or 5.5V                                                                         | V <sub>IN</sub> = -7V | Full         | -75             | 11                  | -                       | μA    |

| Output Leakage Current (Y, Z)                                                                     | I <sub>IN3</sub>           | $\overline{RE} = V_{CC},  DE = 0V,$                                             | V <sub>IN</sub> = 12V | Full         | -               | 0                   | 20                      | μA    |

| in Shutdown Mode (Full Duplex)                                                                    |                            | $V_{CC} = 0V \text{ or } 5.5V$                                                  | V <sub>IN</sub> = -7V | Full         | -20             | 9                   | -                       | μA    |

| Driver Short-Circuit Current, $V_O$ = High or Low                                                 | I <sub>OSD1</sub>          | DE = $V_{CC}$ , -7V $\leq$ V <sub>Y</sub> or V <sub>Z</sub> $\leq$ 12V (Note 8) |                       | Full         | -               | -                   | ±250                    | mA    |

| Receiver Differential Threshold<br>Voltage                                                        | V <sub>TH</sub>            | $-7V \le V_{CM} \le 12V$                                                        |                       | Full         | -200            | -90                 | -50                     | mV    |

**Electrical Specifications** Test Conditions: V<sub>CC</sub> = 4.5V to 5.5V; Unless Otherwise Specified. Typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C (Note 6). (Continued)

| PARAMETER                                               | SYMBOL                              | TEST CONDITIONS                                                                                                                                 | TEMP<br>(°C) | MIN<br>(Note 5)     | ТҮР    | MAX<br>(Note 5) | UNITS |

|---------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|--------|-----------------|-------|

| Receiver Input Hysteresis                               | $\Delta V_{TH}$                     | V <sub>CM</sub> = 0V                                                                                                                            | 25           | -                   | 20     | -               | mV    |

| Receiver Output High Voltage                            | V <sub>OH</sub>                     | I <sub>O</sub> = -4mA, V <sub>ID</sub> = -50mV                                                                                                  | Full         | V <sub>CC</sub> - 1 | 4.6    | -               | V     |

| Receiver Output Low Voltage                             | V <sub>OL</sub>                     | I <sub>O</sub> = -4mA, V <sub>ID</sub> = -200mV                                                                                                 | Full         | -                   | 0.2    | 0.4             | V     |

| Three-State (high impedance)<br>Receiver Output Current | I <sub>OZR</sub>                    | $0.4V \le V_O \le 2.4V$                                                                                                                         | Full         | -1                  | 0.03   | 1               | μA    |

| Receiver Input Resistance                               | R <sub>IN</sub>                     | $-7V \le V_{CM} \le 12V$                                                                                                                        | Full         | 96                  | 160    | -               | kΩ    |

| Receiver Short-Circuit Current                          | I <sub>OSR</sub>                    | $0V \le V_O \le V_{CC}$                                                                                                                         | Full         | ±7                  | -      | ±85             | mA    |

| SUPPLY CURRENT                                          |                                     | 1                                                                                                                                               |              |                     |        |                 |       |

| No-Load Supply Current (Note 7)                         | ICC                                 | Half Duplex Versions, DE = $V_{CC}$ , $\overline{RE} = X$ ,<br>DI = 0V or $V_{CC}$                                                              | Full         | -                   | 560    | 700             | μA    |

|                                                         |                                     | All Versions, DE = 0V, $\overline{RE}$ = 0V, or Full Duplex<br>Versions, DE = V <sub>CC</sub> , $\overline{RE}$ = X. DI = 0V or V <sub>CC</sub> | Full         | -                   | 530    | 650             | μA    |

| Shutdown Supply Current                                 | I <sub>SHDN</sub>                   | DE = 0V, $\overline{RE}$ = V <sub>CC</sub> , DI = 0V or V <sub>CC</sub>                                                                         | Full         | -                   | 0.07   | 2               | μA    |

| ESD PERFORMANCE                                         |                                     | 1                                                                                                                                               |              |                     | I      |                 |       |

| RS-485 Pins (A, Y, B, Z)                                |                                     | Human Body Model (HBM), Pin to GND                                                                                                              | 25           | -                   | ±15    | -               | kV    |

| All Other Pins                                          |                                     | HBM, per MIL-STD-883 Method 3015                                                                                                                | 25           | -                   | ±7     | -               | kV    |

|                                                         |                                     | Machine Model                                                                                                                                   | 25           | -                   | > ±250 | -               | V     |

| DRIVER SWITCHING CHARACTE                               | RISTICS (11                         | 5kbps Versions; ISL83080E, ISL83082E)                                                                                                           |              |                     |        |                 |       |

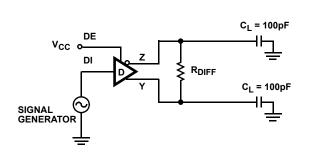

| Driver Differential Output Delay                        | t <sub>PLH</sub> , t <sub>PHL</sub> | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF (Figure 2)                                                                                      | Full         | 500                 | 780    | 1300            | ns    |

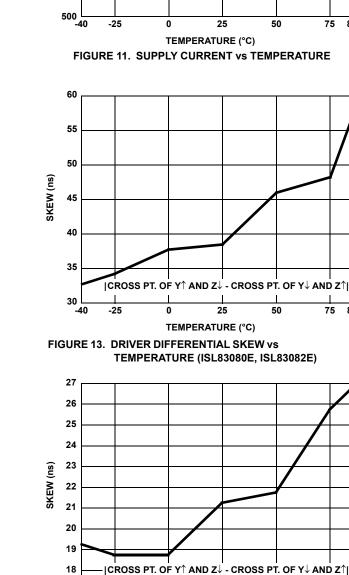

| Driver Differential Output Skew                         | t <sub>SKEW</sub>                   | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF (Figure 2)                                                                                      | Full         | -                   | 40     | 100             | ns    |

| Driver Differential Rise or Fall Time                   | t <sub>R</sub> , t <sub>F</sub>     | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100pF (Figure 2)                                                                                           | Full         | 667                 | 1000   | 1500            | ns    |

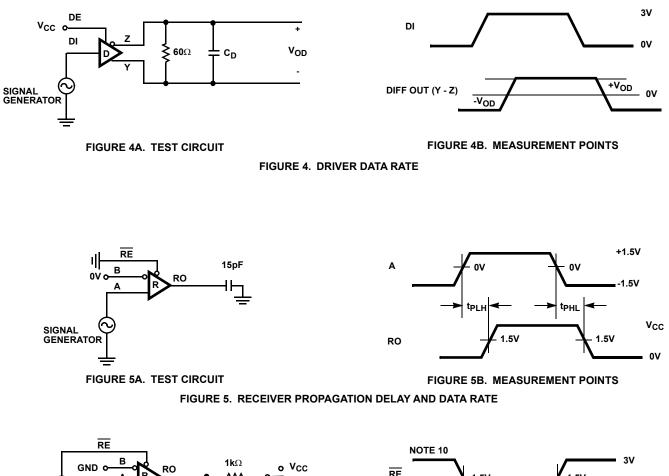

| Maximum Data Rate                                       | f <sub>MAX</sub>                    | C <sub>D</sub> = 820pF (Figure 4) (Note 15)                                                                                                     | Full         | 115                 | 666    | -               | kbps  |

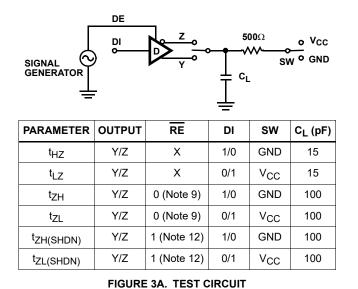

| Driver Enable to Output High                            | t <sub>ZH</sub>                     | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>(Figure 3), (Note 9)                                                                 | Full         | -                   | 278    | 1500            | ns    |

| Driver Enable to Output Low                             | t <sub>ZL</sub>                     | $R_L = 500\Omega$ , $C_L = 100pF$ , SW = $V_{CC}$ (Figure 3) (Note 9)                                                                           | Full         | -                   | 35     | 1500            | ns    |

| Driver Disable from Output Low                          | t <sub>LZ</sub>                     | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = $V_{CC}$ (Figure 3)                                                                                     | Full         | -                   | 67     | 100             | ns    |

| Driver Disable from Output High                         | t <sub>HZ</sub>                     | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = GND (Figure 3)                                                                                          | Full         | -                   | 38     | 100             | ns    |

| Time to Shutdown                                        | t <sub>SHDN</sub>                   | (Note 11)                                                                                                                                       | Full         | 60                  | 160    | 600             | ns    |

| Driver Enable from Shutdown to<br>Output High           | <sup>t</sup> ZH(SHDN)               | $R_L = 500\Omega$ , $C_L = 100pF$ , SW = GND (Figure 3)<br>(Notes 11, 12)                                                                       | Full         | -                   | 400    | 2000            | ns    |

| Driver Enable from Shutdown to<br>Output Low            | <sup>t</sup> ZL(SHDN)               | $R_L = 500\Omega$ , $C_L = 100pF$ , SW = V <sub>CC</sub> (Figure 3) (Notes 11, 12)                                                              | Full         | -                   | 155    | 2000            | ns    |

| DRIVER SWITCHING CHARACTE                               | RISTICS (50                         | 0kbps Versions; ISL83083E, ISL83085E)                                                                                                           |              |                     | 1      |                 | 1     |

| Driver Differential Output Delay                        | t <sub>PLH</sub> , t <sub>PHL</sub> | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100pF (Figure 2)                                                                                           | Full         | 250                 | 360    | 1000            | ns    |

| Driver Differential Output Skew                         | <sup>t</sup> SKEW                   | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF (Figure 2)                                                                                      | Full         | -                   | 20     | 100             | ns    |

| Driver Differential Rise or Fall Time                   | t <sub>R</sub> , t <sub>F</sub>     | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100pF (Figure 2)                                                                                           | Full         | 200                 | 475    | 750             | ns    |

| Maximum Data Rate                                       | f <sub>MAX</sub>                    | C <sub>D</sub> = 820pF (Figure 4) (Note 15)                                                                                                     | Full         | 500                 | 1000   | -               | kbps  |

**Electrical Specifications** Test Conditions: V<sub>CC</sub> = 4.5V to 5.5V; Unless Otherwise Specified. Typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C (Note 6). (Continued)

| PARAMETER                                           | SYMBOL                              | TEST CONDITIONS                                                                             | TEMP<br>(°C) | MIN<br>(Note 5) | ТҮР | MAX<br>(Note 5) | UNITS     |

|-----------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------|--------------|-----------------|-----|-----------------|-----------|

| Driver Enable to Output High                        | t <sub>ZH</sub>                     | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>(Figure 3), (Note 9)             | Full         | -               | 137 | 1000            | ns        |

| Driver Enable to Output Low                         | t <sub>ZL</sub>                     | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = V <sub>CC</sub> (Figure 3),<br>(Note 9) |              | -               | 35  | 1000            | ns        |

| Driver Disable from Output Low                      | t <sub>LZ</sub>                     | $R_L$ = 500 $\Omega$ , $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 3)                        | Full         | -               | 65  | 100             | ns        |

| Driver Disable from Output High                     | t <sub>HZ</sub>                     | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = GND (Figure 3),                                     | Full         | -               | 38  | 100             | ns        |

| Time to Shutdown                                    | t <sub>SHDN</sub>                   | (Note 11)                                                                                   | Full         | 60              | 160 | 600             | ns        |

| Driver Enable from Shutdown to<br>Output High       | <sup>t</sup> ZH(SHDN)               | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>(Figure 3), (Notes 11, 12)       | Full         | -               | 260 | 1500            | ns        |

| Driver Enable from Shutdown to<br>Output Low        | <sup>t</sup> ZL(SHDN)               | $R_L$ = 500Ω, $C_L$ = 100pF, SW = V <sub>CC</sub> (Figure 3), (Notes 11, 12)                | Full         | -               | 155 | 1500            | ns        |

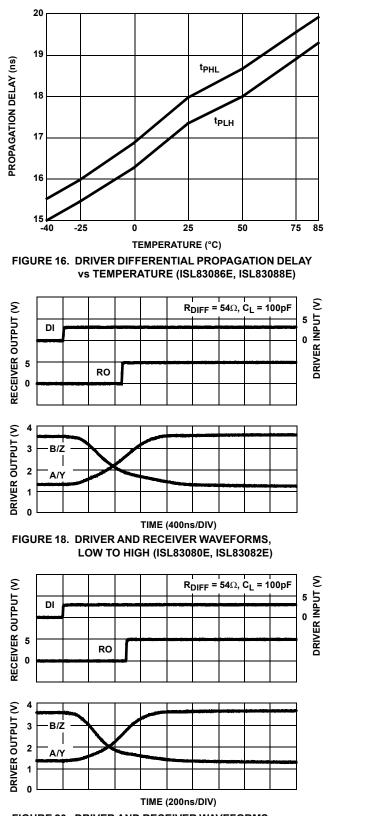

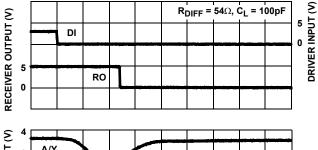

| DRIVER SWITCHING CHARACTE                           | RISTICS (10                         | Mbps Versions; ISL83086E, ISL83088E)                                                        |              |                 |     |                 | <u>.I</u> |

| Driver Differential Output Delay                    | t <sub>PLH</sub> , t <sub>PHL</sub> | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF (Figure 2)                                  | Full         | -               | 20  | 60              | ns        |

| Driver Differential Output Skew                     | t <sub>SKEW</sub>                   | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100pF (Figure 2)                                       | Full         | -               | 1   | 10              | ns        |

| Driver Differential Rise or Fall Time               | t <sub>R</sub> , t <sub>F</sub>     | R <sub>DIFF</sub> = 54Ω, C <sub>L</sub> = 100pF (Figure 2)                                  | Full         | -               | 13  | 25              | ns        |

| Maximum Data Rate                                   | f <sub>MAX</sub>                    | C <sub>D</sub> = 470pF (Figure 4) (Note 15)                                                 | Full         | 10              | 15  | -               | Mbps      |

| Driver Enable to Output High                        | <sup>t</sup> zH                     | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>(Figure 3), (Note 9)             | Full         | -               | 35  | 150             | ns        |

| Driver Enable to Output Low                         | t <sub>ZL</sub>                     | $R_L = 500\Omega$ , $C_L = 100pF$ , SW = V <sub>CC</sub> (Figure 3), (Note 9)               | Full         | -               | 30  | 150             | ns        |

| Driver Disable from Output Low                      | t <sub>LZ</sub>                     | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = V <sub>CC</sub> (Figure 3)                          | Full         | -               | 66  | 100             | ns        |

| Driver Disable from Output High                     | t <sub>HZ</sub>                     | $R_L = 500\Omega$ , $C_L = 15pF$ , SW = GND (Figure 3)                                      | Full         | -               | 38  | 100             | ns        |

| Time to Shutdown                                    | t <sub>SHDN</sub>                   | (Note 11)                                                                                   | Full         | 60              | 160 | 600             | ns        |

| Driver Enable from Shutdown to<br>Output High       | <sup>t</sup> ZH(SHDN)               | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 100pF, SW = GND<br>(Figure 3), (Notes 11, 12)       | Full         | -               | 115 | 250             | ns        |

| Driver Enable from Shutdown to<br>Output Low        | <sup>t</sup> ZL(SHDN)               | $R_L$ = 500Ω, $C_L$ = 100pF, SW = V <sub>CC</sub> (Figure 3),<br>(Notes 11, 12)             | Full         | -               | 84  | 250             | ns        |

| RECEIVER SWITCHING CHARAC                           | TERISTICS                           | 115kbps and 500kbps Versions; ISL83080E                                                     | THRU IS      | L83085E)        |     | 1               | .1        |

| Maximum Data Rate                                   | f <sub>MAX</sub>                    | (Figure 5) (Note 15)                                                                        | Full         | 0.5             | 10  | -               | Mbps      |

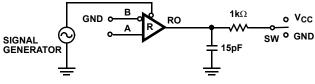

| Receiver Input to Output Delay                      | t <sub>PLH</sub> , t <sub>PHL</sub> | (Figure 5)                                                                                  | Full         | -               | 100 | 150             | ns        |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub> | t <sub>SKD</sub>                    | (Figure 5)                                                                                  | Full         | -               | 7   | 10              | ns        |

| Receiver Enable to Output Low                       | t <sub>ZL</sub>                     | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 6),<br>(Note 10)                    | Full         | -               | 10  | 50              | ns        |

| Receiver Enable to Output High                      | tzH                                 | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = GND (Figure 6),<br>(Note 10)                                | Full         | -               | 10  | 50              | ns        |

| Receiver Disable from Output Low                    | t <sub>LZ</sub>                     | $R_L$ = 1k $\Omega$ , $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 6)                         | Full         | -               | 10  | 50              | ns        |

| Receiver Disable from Output High                   | t <sub>HZ</sub>                     | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = GND (Figure 6),                                      | Full         | -               | 10  | 50              | ns        |

| Time to Shutdown                                    | <sup>t</sup> SHDN                   | (Note 11)                                                                                   | Full         | 60              | 160 | 600             | ns        |

| Receiver Enable from Shutdown to<br>Output High     | <sup>t</sup> ZH(SHDN)               | R <sub>L</sub> = 1kΩ, C <sub>L</sub> = 15pF, SW = GND (Figure 6),<br>(Notes 11, 13)         | Full         | -               | 150 | 2000            | ns        |

## **Electrical Specifications** Test Conditions: V<sub>CC</sub> = 4.5V to 5.5V; Unless Otherwise Specified. Typicals are at V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C (Note 6). (Continued)

| PARAMETER                                           | SYMBOL                              | TEST CONDITIONS                                                               | TEMP<br>(°C) | MIN<br>(Note 5) | ТҮР | MAX<br>(Note 5) | UNITS |

|-----------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------|--------------|-----------------|-----|-----------------|-------|

| FARAMETER                                           | STMBOL                              | TEST CONDITIONS                                                               | (0)          | (NOLE 5)        | TIF | (NOLE 5)        | UNITS |

| Receiver Enable from Shutdown to<br>Output Low      | <sup>t</sup> ZL(SHDN)               | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 6),<br>(Notes 11, 13) | Full         | -               | 150 | 2000            | ns    |

| RECEIVER SWITCHING CHARAC                           | TERISTICS                           | (10Mbps Versions; ISL83086E, ISL83088E)                                       | 1 1          |                 |     |                 | 1     |

| Maximum Data Rate                                   | f <sub>MAX</sub>                    | (Figure 5) (Note 15)                                                          | Full         | 10              | 15  | -               | Mbps  |

| Receiver Input to Output Delay                      | t <sub>PLH</sub> , t <sub>PHL</sub> | (Figure 5)                                                                    | Full         | -               | 70  | 125             | ns    |

| Receiver Skew   t <sub>PLH</sub> - t <sub>PHL</sub> | t <sub>SKD</sub>                    | (Figure 5)                                                                    | Full         | -               | 0   | 10              | ns    |

| Receiver Enable to Output Low                       | t <sub>ZL</sub>                     | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 6)<br>(Note 10)       | Full         | -               | 10  | 30              | ns    |

| Receiver Enable to Output High                      | t <sub>ZH</sub>                     | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = GND (Figure 6)<br>(Note 10)                   | Full         | -               | 10  | 30              | ns    |

| Receiver Disable from Output Low                    | <sup>t</sup> LZ                     | $R_L$ = 1k $\Omega$ , $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 6)           | Full         | -               | 10  | 30              | ns    |

| Receiver Disable from Output High                   | t <sub>HZ</sub>                     | $R_L = 1k\Omega$ , $C_L = 15pF$ , SW = GND (Figure 6)                         | Full         | -               | 10  | 30              | ns    |

| Time to Shutdown                                    | <sup>t</sup> SHDN                   | (Note 11)                                                                     | Full         | 60              | 160 | 600             | ns    |

| Receiver Enable from Shutdown to Output High        | <sup>t</sup> ZH(SHDN)               | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = GND (Figure 6)<br>(Notes 11, 13)              | Full         | -               | 150 | 2000            | ns    |

| Receiver Enable from Shutdown to Output Low         | <sup>t</sup> ZL(SHDN)               | $R_L$ = 1kΩ, $C_L$ = 15pF, SW = V <sub>CC</sub> (Figure 6)<br>(Notes 11, 13)  | Full         | -               | 150 | 2000            | ns    |

NOTES:

5. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 6. All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified.

- 7. Supply current specification is valid for loaded drivers when DE = 0V.

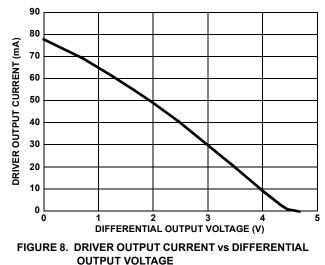

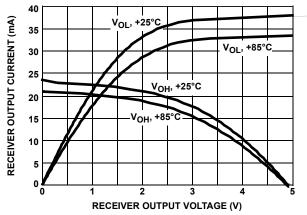

- 8. Applies to peak current. See "Typical Performance Curves" beginning on page 12 for more information.

- 9. Keep  $\overline{RE} = 0$  to prevent the device from entering SHDN.

- 10. The RE signal high time must be short enough (typically <100ns) to prevent the device from entering SHDN.

- 11. Transceivers are put into shutdown by bringing RE high and DE low. If the inputs are in this state for less than 60ns, the parts are guaranteed not to enter shutdown. If the inputs are in this state for at least 600ns, the parts are guaranteed to have entered shutdown. See "Low Power Shutdown Mode" on page 12.

- 12. Keep  $\overline{RE}$  = VCC, and set the DE signal low time >600ns to ensure that the device enters SHDN.

- 13. Set the  $\overline{RE}$  signal high time >600ns to ensure that the device enters SHDN.

- 14. Tested according to TIA/EIA-485-A, section 4.2.6 (±75V for 15µs at a 1% duty cycle).

- 15. Limits established by characterization and are not production tested.

## Test Circuits and Waveforms

FIGURE 1A.  $V_{\mbox{OD}}$  and  $V_{\mbox{OC}}$

FIGURE 1B. VOD WITH COMMON MODE LOAD

1.5V

t<sub>PLI</sub>

90%

10%

tp

зv

0V

VOH

VOL

+VOD

-V<sub>OD</sub>

1.5V

t<sub>PHL</sub>

90%

10%

te

3V

FIGURE 1. DC DRIVER TEST CIRCUITS

DI

OUT (Z)

OUT (Y)

DIFF OUT (Y - Z)

FIGURE 2A. TEST CIRCUIT

SKEW = |t<sub>PLH</sub> - t<sub>PHL</sub>|

2A. TEST CIRCUIT

FIGURE 2B. MEASUREMENT POINTS

FIGURE 2. DRIVER PROPAGATION DELAY AND DIFFERENTIAL TRANSITION TIMES

FIGURE 3B. MEASUREMENT POINTS

FIGURE 3. DRIVER ENABLE AND DISABLE TIMES

## Test Circuits and Waveforms (Continued)

| PARAMETER                       | DE | Α     | SW              |

|---------------------------------|----|-------|-----------------|

| t <sub>HZ</sub>                 | 0  | +1.5V | GND             |

| t <sub>LZ</sub>                 | 0  | -1.5V | V <sub>CC</sub> |

| t <sub>ZH</sub> (Note 10)       | 0  | +1.5V | GND             |

| t <sub>ZL</sub> (Note 10)       | 0  | -1.5V | V <sub>CC</sub> |

| t <sub>ZH(SHDN)</sub> (Note 13) | 0  | +1.5V | GND             |

| t <sub>ZL(SHDN)</sub> (Note 13) | 0  | -1.5V | V <sub>CC</sub> |

FIGURE 6A. TEST CIRCUIT

RE 1 5\ .5V 0V t<sub>ZH</sub>, t<sub>ZH</sub>(SHDN) t<sub>HZ</sub> NOTES 9, 12 OUTPUT HIGH VOH /<sub>OH</sub> - 0.5V RO 1.5V 0V t<sub>ZL</sub>, t<sub>ZL(SHDN)</sub> t<sub>LZ</sub> NOTES 9, 12 Vcc RO 1.5\ V<sub>OL</sub> + 0.5V V<sub>OL</sub> OUTPUT LOW

FIGURE 6B. MEASUREMENT POINTS

FIGURE 6. RECEIVER ENABLE AND DISABLE TIMES

## Application Information

RS-485 and RS-422 are differential (balanced) data transmission standards for use in long haul or noisy environments. RS-422 is a subset of RS-485, so RS-485 transceivers are also RS-422 compliant. RS-422 is a point-to-multipoint (multidrop) standard, which allows only one driver and up to 10 (assuming one unit load devices) receivers on each bus. RS-485 is a true multipoint standard, which allows up to 32 one unit load devices (any combination of drivers and receivers) on each bus. To allow for multipoint operation, the RS-485 specification requires that drivers must handle bus contention without sustaining any damage.

Another important advantage of RS-485 is the extended common mode range (CMR), which specifies that the driver outputs and receiver inputs withstand signals that range from +12V to -7V. RS-422 and RS-485 are intended for runs as long as 4000', so the wide CMR is necessary to handle ground potential differences, as well as voltages induced in the cable by external fields.

#### **Receiver Features**

These devices utilize a differential input receiver for maximum noise immunity and common mode rejection. Input sensitivity is  $\pm 200$  mV, as required by the RS-422 and RS-485 specifications.

Receiver input resistance of 96k $\Omega$  surpasses the RS-422 specification of 4k $\Omega$ , and is eight times the RS-485 "Unit Load (UL)" requirement of 12k $\Omega$  minimum. Thus, these products are known as "one-eighth UL" transceivers, and there can be up to 256 of these devices on a network while still complying with the RS-485 loading specification.

Receiver inputs function with common mode voltages as great as  $\pm$ 7V outside the power supplies (i.e., +12V and -7V), making them ideal for long networks where induced voltages are a realistic concern.

All the receivers include a "full fail-safe" function that guarantees a high level receiver output if the receiver inputs are unconnected (floating) or shorted.

Receivers easily meet the data rates supported by the corresponding driver, and all receiver outputs are three-statable through the active low  $\overline{\text{RE}}$  input.

#### **Driver Features**

The RS-485/RS-422 driver is a differential output device that delivers at least 1.5V across a 54 $\Omega$  load (RS-485), and at least 2V across a 100 $\Omega$  load (RS-422). The drivers feature low propagation delay skew to maximize bit width, and to minimize EMI.

All drivers are three-statable through the active high DE input.

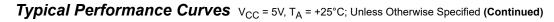

The 115kbps and 500kbps driver outputs are slew rate limited to minimize EMI, and to minimize reflections in

unterminated or improperly terminated networks. Outputs of the ISL83086E, ISL83088E drivers are not limited, so faster output transition times allow data rates of at least 10Mbps.

#### Hot Plug Function

When a piece of equipment powers up, there is a period of time where the processor or ASIC driving the RS-485 control lines (DE,  $\overline{RE}$ ) is unable to ensure that the RS-485 Tx and Rx outputs are kept disabled. If the equipment is connected to the bus, a driver activating prematurely during power-up may crash the bus. To avoid this scenario, the ISL83080, ISL83082, ISL83083, ISL83085 versions incorporate a "Hot Plug" function. Circuitry monitoring V<sub>CC</sub> ensures that, during power-up and power-down, the Tx and Rx outputs remain disabled, regardless of the state of DE and  $\overline{RE}$ , if V<sub>CC</sub> is less than ~3.4V. This gives the processor/ASIC a chance to stabilize and drive the RS-485 control lines to the proper states.

#### ESD Protection

All pins on these devices include class 3 Human Body Model (HBM) ESD protection structures, but the RS-485 pins (driver outputs and receiver inputs) incorporate advanced structures allowing them to survive ESD events in excess of ±15kV HBM. The RS-485 pins are particularly vulnerable to ESD damage because they typically connect to an exposed port on the exterior of the finished product. Simply touching the port pins, or connecting a cable, can cause an ESD event that might destroy unprotected ICs. These new ESD structures protect the device whether or not it is powered up, protect without allowing any latchup mechanism to activate, and without degrading the RS-485 common mode range of -7V to +12V. This built-in ESD protection eliminates the need for board level protection structures (e.g., transient suppression diodes), and the associated, undesirable capacitive load they present.

#### Data Rate, Cables, and Terminations

RS-485/RS-422 are intended for network lengths up to 4000', but the maximum system data rate decreases as the transmission length increases. Devices operating at 10Mbps are limited to lengths less than 100', while the 115kbps versions can operate at full data rates with lengths of several 1000'.

Twisted pair is the cable of choice for RS-485/RS-422 networks. Twisted pair cables tend to pick up noise and other electromagnetically induced voltages as common mode signals, which are effectively rejected by the differential receivers in these ICs.

Proper termination is imperative (when using the 10Mbps devices) to minimize reflections. Short networks using the 115kbps versions need not be terminated, but, terminations are recommended unless power dissipation is an overriding concern.

In point-to-point, or point-to-multipoint (single driver on bus) networks, the main cable should be terminated in its characteristic impedance (typically  $120\Omega$ ) at the end farthest from the driver. In multi-receiver applications, stubs connecting receivers to the main cable should be kept as short as possible. Multipoint (multi-driver) systems require that the main cable be terminated in its characteristic impedance at both ends. Stubs connecting a transceiver to the main cable should be kept as short as possible.

#### **Built-In Driver Overload Protection**

As stated previously, the RS-485 specification requires that drivers survive worst case bus contentions undamaged.

These devices meet this requirement via driver output short circuit current limits, and on-chip thermal shutdown circuitry.

The driver output stages incorporate short circuit current limiting circuitry which ensures that the output current never exceeds the RS-485 specification, even at the common mode voltage range extremes. Additionally, these devices utilize a foldback circuit which reduces the short circuit current, and thus the power dissipation, whenever the contending voltage exceeds either supply.

In the event of a major short circuit condition, devices also include a thermal shutdown feature that disables the drivers whenever the die temperature becomes excessive. This eliminates the power dissipation, allowing the die to cool. The drivers automatically re-enable after the die temperature drops about +15°C. If the contention persists, the thermal shutdown/re-enable cycle repeats until the fault is cleared. Receivers stay operational during thermal shutdown.

#### Low Power Shutdown Mode

These CMOS transceivers all use a fraction of the power required by their bipolar counterparts, but they also include a shutdown feature that reduces the already low quiescent  $I_{CC}$  to a 70nA trickle. These devices enter shutdown whenever the receiver and driver are *simultaneously* disabled ( $\overline{RE} = V_{CC}$  and DE = GND) for a period of at least 600ns. Disabling both the driver and the receiver for less than 60ns guarantees that the transceiver will not enter shutdown.

Note that receiver and driver enable times increase when the transceiver enables from shutdown. Refer to Notes 9 thru 13, at the end of the "Electrical Specification Table" on page 8, for more information.

### Typical Performance Curves V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C; Unless Otherwise Specified

560

550

540

520

510

(Рл) <sup>230</sup>

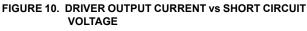

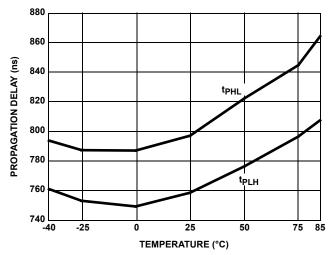

FIGURE 12. DRIVER DIFFERENTIAL PROPAGATION DELAY vs TEMPERATURE (ISL83080E, ISL83082E)

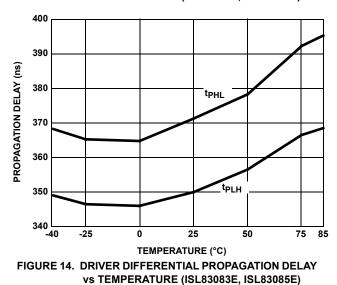

HALF DUPLEX, DE =  $V_{CC}$ ,  $\overline{RE} = X$

HALF DUPLEX, DE = GND,  $\overline{RE}$  = GND

85

85

FULL DUPLEX, DE = X,  $\overline{RE}$  = GND

## **Typical Performance Curves** V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C; Unless Otherwise Specified (Continued)

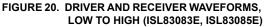

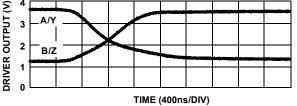

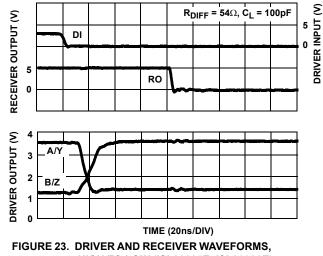

FIGURE 19. DRIVER AND RECEIVER WAVEFORMS, HIGH TO LOW (ISL83080E, ISL83082E)

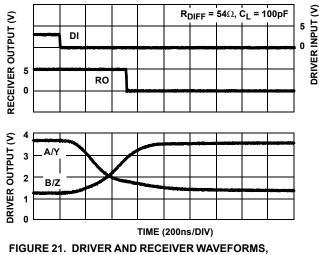

HIGH TO LOW (ISL83083E, ISL83085E)

## **Typical Performance Curves** V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C; Unless Otherwise Specified (Continued)

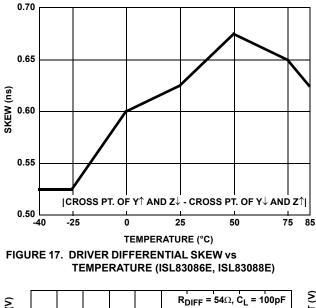

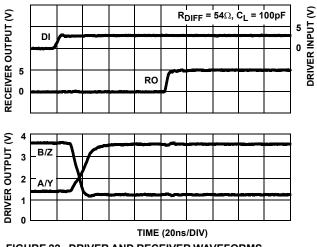

FIGURE 22. DRIVER AND RECEIVER WAVEFORMS, LOW TO HIGH (ISL83086E, ISL83088E)

FIGURE 24. RECEIVER OUTPUT CURRENT vs RECEIVER OUTPUT VOLTAGE

HIGH TO LOW (ISL83086E, ISL83088E)

## **Die Characteristics**

SUBSTRATE POTENTIAL (POWERED UP):

GND

#### TRANSISTOR COUNT:

525

#### PROCESS:

Si Gate BiCMOS

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Jul 5, 2022  | 10.01    | Removed ISL83084E information from datasheet.<br>Updated Ordering Information table format and added Note 3.<br>Added test condition for VOD1.<br>Removed maximum limit for VOD2.<br>Removed About Intersil section.<br>Updated M8.118 POD to the latest revision, changes are as follows:<br>-Corrected typo in the side view 1 updating package thickness tolerance from ±010 to ±0.10.<br>Updated M10.118 POD to the latest revision, changes are as follows:<br>-Corrected typo in the side view 1 updating package thickness tolerance from ±010 to ±0.10.<br>Updated M10.118 POD to the latest revision, changes are as follows:<br>-Corrected typo in the side view 1 updating package thickness tolerance from ±010 to ±0.10.<br>Updated M14.15 POD to the latest revision, changes are as follows:<br>-In Side View B and Detail A:<br>Added lead length dimension (1.27 – 0.40)<br>Changed angle of the lead to 0-8 degrees.<br>Updated M8.15 POD to the latest revision, changes are as follows:<br>-Added the coplanarity spec into the drawing.        |  |

| Feb 15, 2016 | 10.00    | Added Rev History and About Intersil verbiage.<br>Updated "Ordering Information" on page 4.<br>Updated POD M8.118 to current version with following changes:<br>Updated to new Intersil format by adding land pattern and moving dimensions from table onto drawing<br>Corrected lead width dimension in side view 1 from "0.25 - 0.036" to "0.25 - 0.36"<br>Updated POD M10.118 to current version with following change:<br>Updated POD M10.118 to current version with following change:<br>Updated POD M14.15 to current version with following change:<br>Added land pattern and moved dimensions from table onto drawing.<br>Updated POD M8.15 to current version with following changes:<br>Updated POD M8.15 to current version with following changes:<br>Updated to new POD format by removing table and moving dimensions onto drawing and adding land<br>pattern.<br>Changed in Typical Recommended Land Pattern the following:<br>2.41(0.095) to 2.20(0.087)<br>0.76 (0.030) to 0.60(0.023)<br>0.200 to 5.20(0.205)<br>Changed Note 1 "1982" to "1994" |  |

## Package Outline Drawings

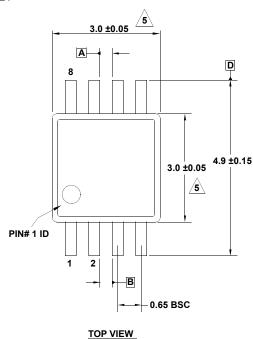

For the most recent package outline drawing, see M8.118.

M8.118 8 Lead Mini Small Outline Plastic Package Rev 5, 5/2021

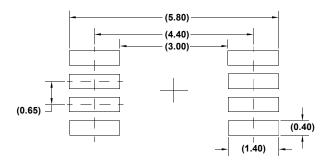

TYPICAL RECOMMENDED LAND PATTERN

NOTES:

- 1. Dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSEY14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included.

- 4. Plastic interlead protrusions of 0.15mm max per side are not included.

- 5. Dimensions are measured at Datum Plane "H".

- 6. Dimensions in ( ) are for reference only.

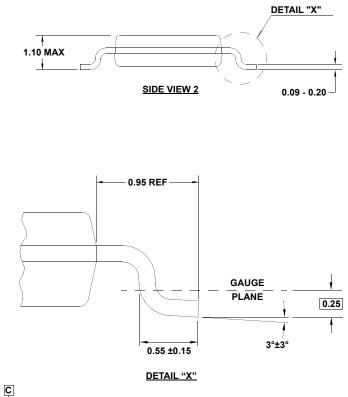

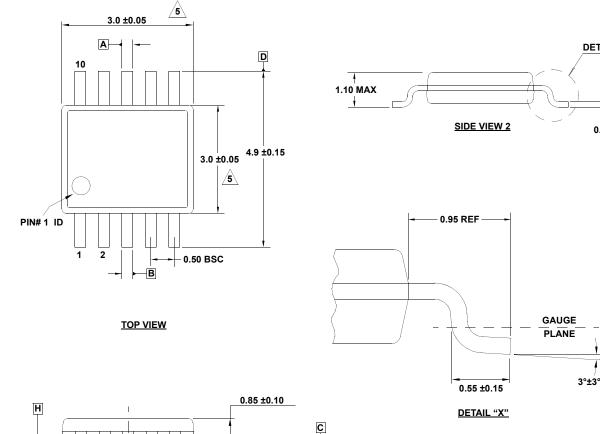

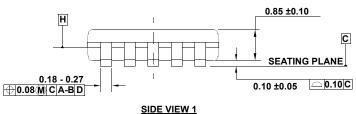

For the most recent package outline drawing, see M10.118.

M10.118 10 Lead Mini Small Outline Plastic Package

Rev 2, 5/2021

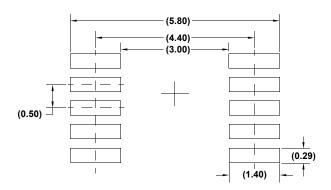

TYPICAL RECOMMENDED LAND PATTERN

NOTES:

- 1. Dimensions are in millimeters.

- 2. Dimensioning and tolerancing conform to JEDEC MO-187-BA and AMSEY14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included.

- 4. Plastic interlead protrusions of 0.15mm max per side are not included.

- **5.** Dimensions are measured at Datum Plane "H".

- 6. Dimensions in ( ) are for reference only.

DETAIL "X"

0.09 - 0.20

0.25

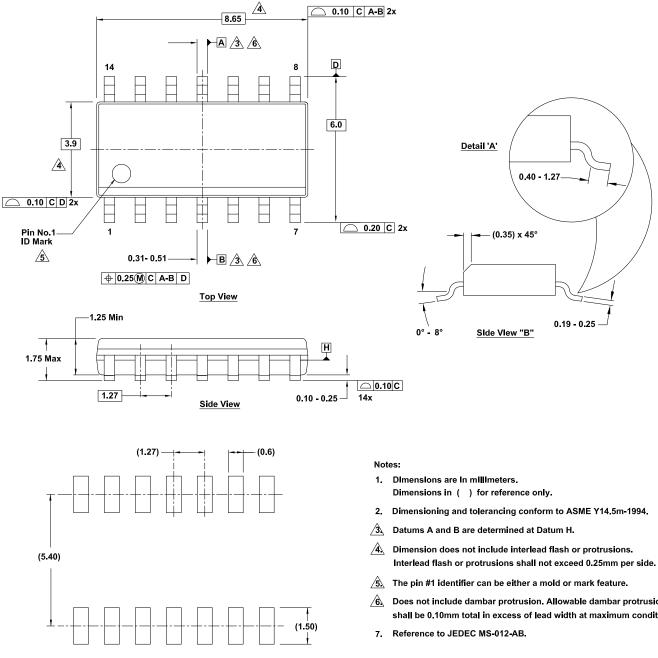

For the most recent package outline drawing, see M14.15.

#### M14.15

14 Lead Narrow Body Small Outline Plastic Package Rev 2, 6/20

Typical Recommended Land Pattern

Does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm total in excess of lead width at maximum condition.

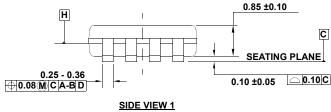

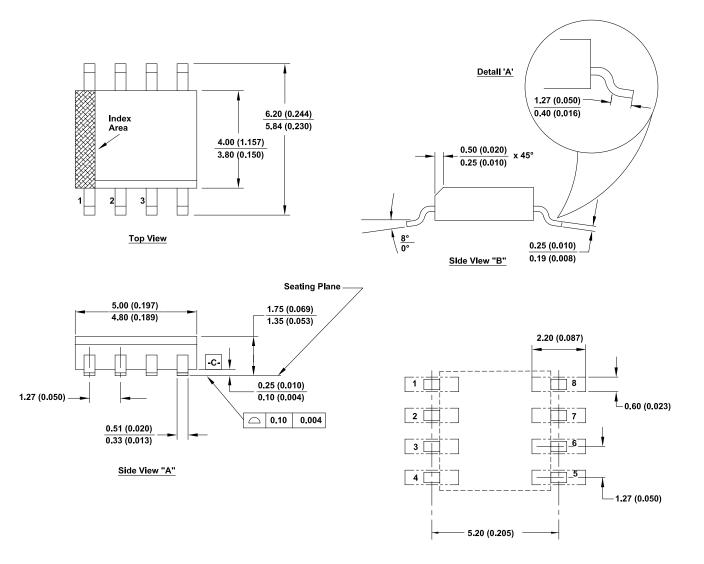

For the most recent package outline drawing, see M8.15.

#### M8.15

8 Lead Narrow Body Small Outline Plastic Package Rev 5, 4/2021

#### NOTES:

- 1 Dimensioning and tolerancing conform to AMSEY14.5m-1994.

- 2 Package length does not include mold flash, protrustion or gate burrs. Mold flash, protrustion and gate burrs shall not exceed 0.15mm (0.006 Inch) per slde.

- 3. Package width does not include interlead flash or protrustions. Interlead flash and protrustions shallnot exceed 0.25mm (0.010 inch) per side.

- 4. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 5 Terminal numbers are shown for reference only.

- 6 The lead width as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 7 Controlling dimension: MILLIMETER. Converted inch dimension are not necessarily exact.

- 8 This outline conforms to JEDEC publication MS-012-AA ISSUE C.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/