#### **General Description**

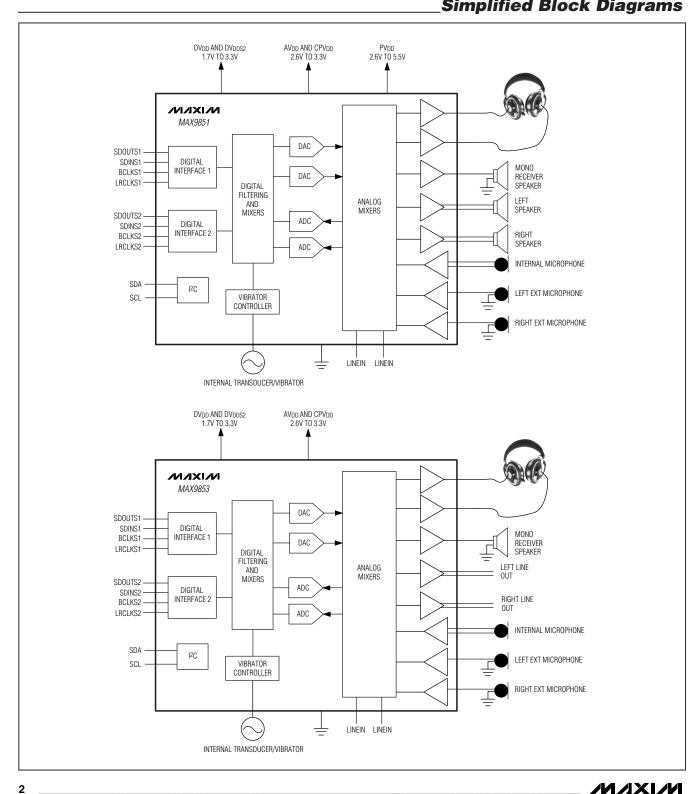

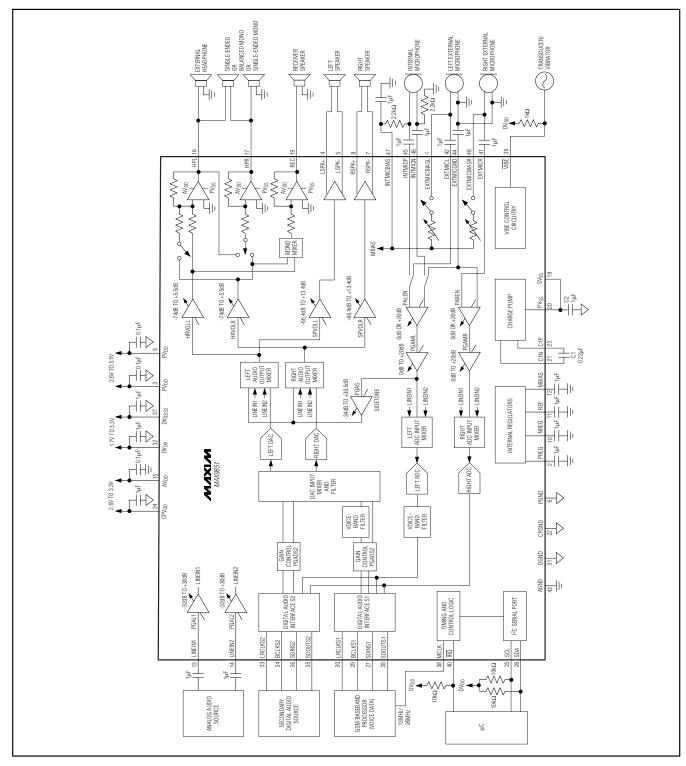

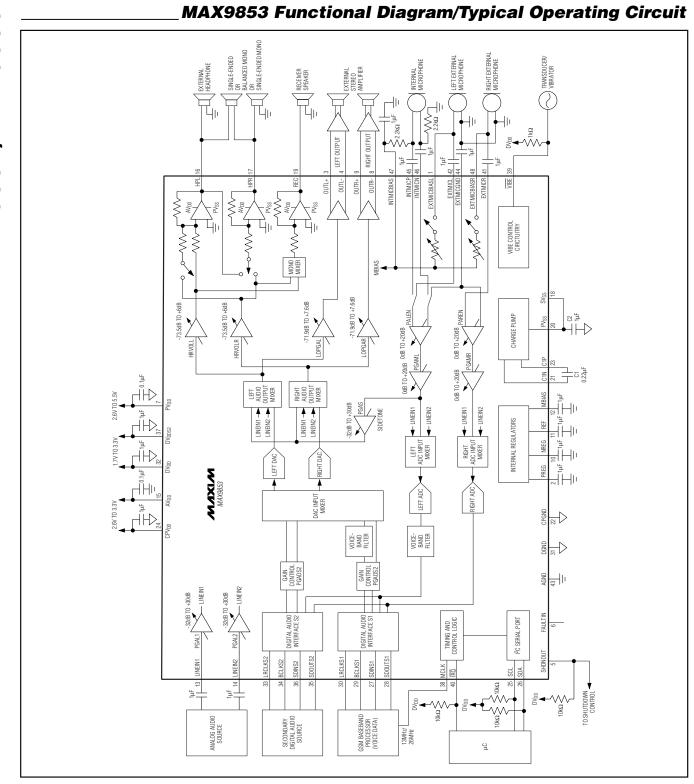

The MAX9851/MAX9853 are single-chip, stereo audio CODECs designed to provide a complete audio solution for a GSM/GPRS/EDGE cell phone. The MAX9851/MAX9853 provide stereo DirectDrive<sup>™</sup> headphone amplifiers, a mono receiver speaker amplifier, stereo Class D speaker amplifiers (MAX9851 only), stereo differential line outputs (MAX9853 only), microphone input amplifiers, plus flexible input selection and gain control. Two serial digital audio interfaces are included, one intended to accept voiceband data and the other accepting I<sup>2</sup>S data. The voiceband interface can be reconfigured as needed to act as a secondary I<sup>2</sup>S feed input—allowing multiple audio source mixing of ringer tones or other audio at different sample rates. A transducer/vibrator signal can be derived from digital audio.

The stereo digital-to-analog converter (DAC) path includes filtering and mixing, programmable-gain amplifiers (PGA), soft muting, and optional voiceband digital filtering. The MAX9851/MAX9853 accept up to two digital audio inputs at different sample rates. All analog inputs have PGAs on the front end, allowing dynamic range optimization with a wide range of input sources.

The stereo analog-to-digital converter (ADC) converts audio signals from either internal or external microphones or stereo line inputs. The microphone amplifiers have a programmable gain from 0 to 40dB to handle both amplified microphones and electret modules. In addition to a digital highpass filter to remove DC offset voltages, the ADC also features voiceband digital filtering.

The digital audio interfaces support a variety of serial audio formats. The secondary serial audio interface has an independent supply voltage to allow integration into multiple supply systems. Control for volume levels, signal mixing, and operating modes is done through the I<sup>2</sup>C 2-wire interface.

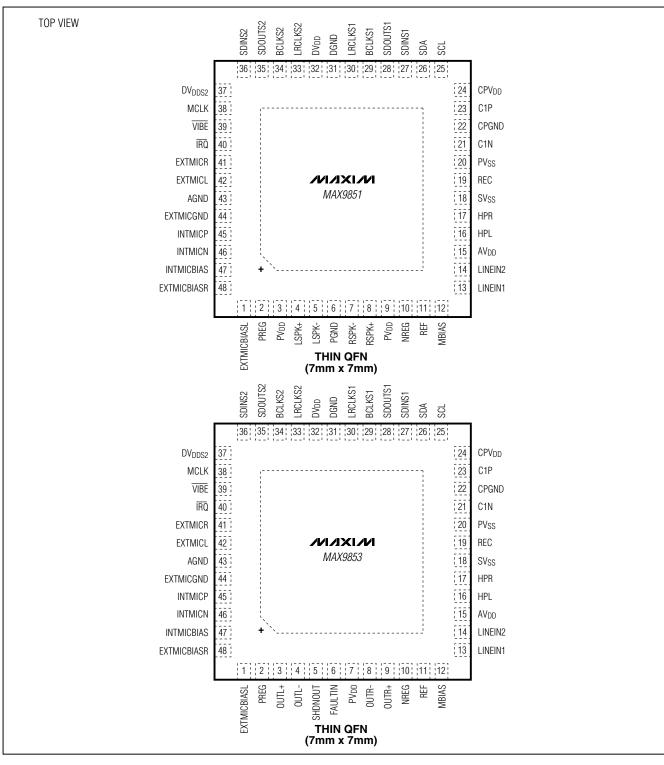

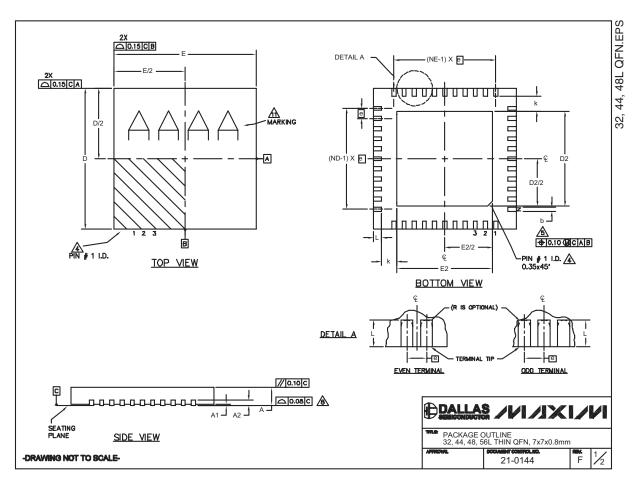

All circuitry is optimized for high PSRR. The MAX9851/ MAX9853 use a thermally efficient, space-saving 48-pin thin QFN package (7mm x 7mm x 0.8mm) with an exposed pad.

#### **Applications**

GSM/GPRS/EDGE Cell Phones PDAs/SmartPhones

#### **Features**

+1.7V to +3.3V (Digital) and +2.6V to +3.3V (Analog) Operation

///XI///

- +2.6V to +5.5V Class D Speaker Amplifier Operation (Direct from Battery)

- Low 26mW Quiescent Power Consumption (Playback)

- ♦ High 98dB Power-Supply Rejection Ratio

- ♦ 8kHz to 48kHz Sample Rate (Replay and Record)

- Stereo 18-Bit ADC and DAC

- Low-Noise Stereo Microphone Inputs and Stereo Line Inputs

- Dual Source Digital Mixing (DAC)

- Selectable Voiceband Filter for Recording/Playback Modes

- Digital Filtering, Soft Mute, and Volume Control

- Low-Noise, High-PSRR Microphone Bias Generator

- Stereo DirectDrive Headphone Amplifier (2 x 50mW)

- Mono DirectDrive Handset Receiver Amplifier (1 x 105mW)

- Stereo Class D, Ultra-Low-EMI, Filterless Speaker Amplifier with Active Emissions Limiting (2 x 1.25W, 8Ω) (MAX9851)

- Stereo Differential Line Output Amplifiers (MAX9853)

- Clickless/Popless Operation

- Flexible Shutdown Modes for Power Saving

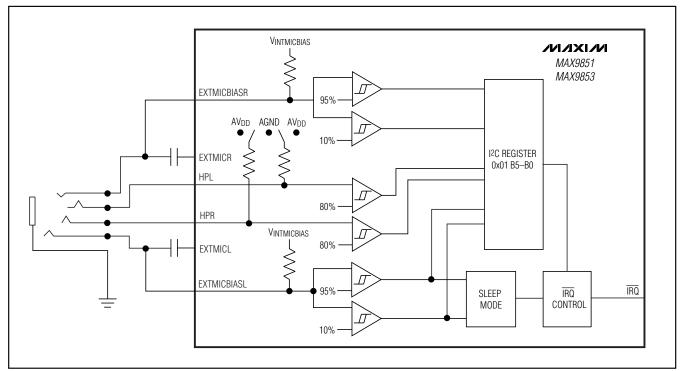

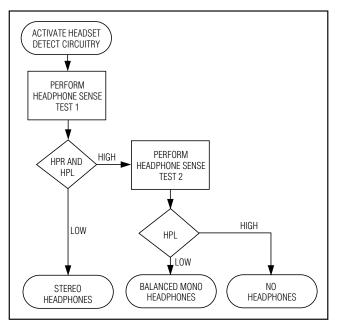

- Comprehensive Headset Detection

- Ultra-Low Power Wake-Up on Headset Detection

#### **Ordering Information**

| PART        | PIN-PACKAGE                        | PKG CODE |

|-------------|------------------------------------|----------|

| MAX9851ETM+ | 48 TQFN-EP*<br>(7mm x 7mm x 0.8mm) | T4877-6  |

| MAX9853ETM+ | 48 TQFN-EP*<br>(7mm x 7mm x 0.8mm) | T4877-6  |

Note: All devices specified over the -40°C to +85°C temperature range.

+Denotes lead-free package.

\*EP = Exposed pad.

Pin Configurations and Selector Guide appear at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Simplified Block Diagrams

# Stereo Audio CODECs with Microphone, DirectDrive Headphones, Speaker Amplifiers, or Line Outputs LRCLKS1, BCLKS1, SDOUTS1, SDINS1.....-0.3V to DV<sub>DD</sub> + 0.3V LRCLKS2, BCLKS2, SDOUTS2,

| LINCLINDZ, DOLINDZ, ODOUI   | 02,                               |

|-----------------------------|-----------------------------------|

| SDINS2                      | 0.3V to DV <sub>DDS2</sub> + 0.3V |

| Short Circuit to AGND Durat | ion:                              |

|                             |                                   |

HPL, HPR, REC .....Continuous LSPK+, LSPK-, RSPK+, RSPK-.....Subject to Maximum Package Power Dissipation

INTMICBIAS, EXTMICBIASL, EXTMICBIASR......Continuous Short Circuit to AV<sub>DD</sub> Duration EXTMICBIASL, EXTMICBIASR ......Continuous

Current Into/Out of Any Pin (unless otherwise noted)......100mA Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| 48-Pin Thin QFN (derate 40mW/°C abov | 'e +70°C)3200mW |

|--------------------------------------|-----------------|

| Junction Temperature                 | +150°C          |

| Operating Temperature Range          | 40°C to +85°C   |

| Storage Temperature Range            | 65°C to +150°C  |

| Lead Temperature (soldering, 10s)    | +300°C          |

|                                      |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ELECTRICAL CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS

AV<sub>DD</sub>, DV<sub>DD</sub>, DV<sub>DDS2</sub>, CPV<sub>DD</sub>....-0.3V to +4V PV<sub>SS</sub>, SV<sub>SS</sub> .....-4V to +0.3V PV<sub>DD</sub>.....-0.3V to +6V AGND, DGND, CPGND, PGND.....-0.3V to +0.3V HPL, HPR, REC .....(SV<sub>SS</sub> - 0.3V) to (AV<sub>DD</sub> + 0.3V)

LSPK+, LSPK-, RSPK+, RSPK- .....-0.3V to (PV<sub>DD</sub> + 0.3V)

LINEIN1, LINEIN2.....-2V to +2V EXTMICBIASL, EXTMICBIASR.....-0.3V to (AVDD + 0.3V)

INTMICP, INTMICN, EXTMICL, EXTMICR .....-2V to +2V

EXTMICGND.....-0.3V to +0.3V

C1N.....(PV<sub>SS</sub> - 0.3V) to (CPGND + 0.3V)

C1P.....(CPGND - 0.3V) to (CPV<sub>DD</sub> + 0.3V)

PREG, REF, MBIAS, INTMICBIAS.....-0.3V to (AVDD + 0.3V) NREG ......+0.3V to (SV<sub>SS</sub> - 0.3V)

FAULTIN.....-0.3V to (AV<sub>CC</sub> + 0.3V) MCLK, IRQ, VIBE, SCL, SDA.....-0.3V to +4V SHDNOUT .....-0.3V to +6V

(Voltages with respect to AGND)

OUTL+, OUTL-, OUTR+, OUTR-,

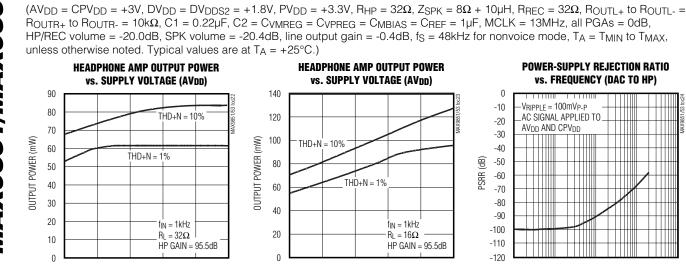

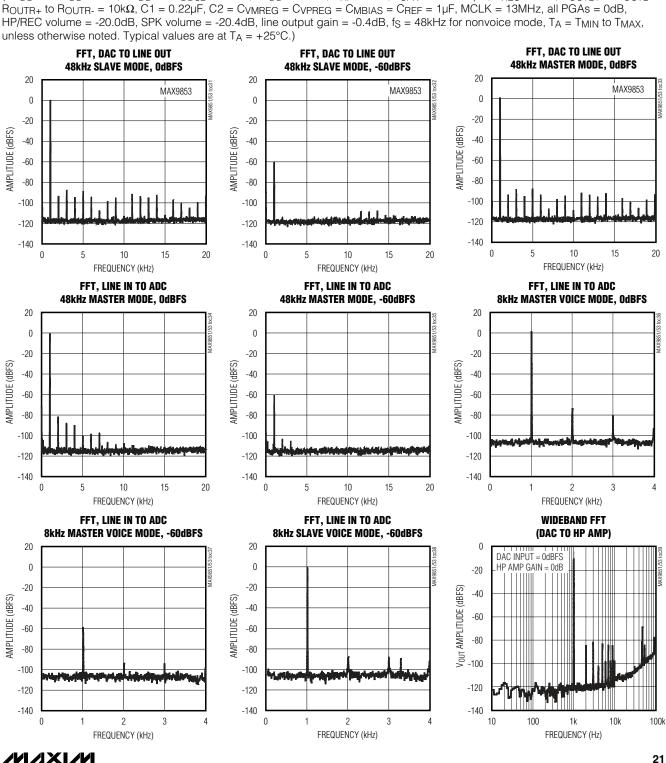

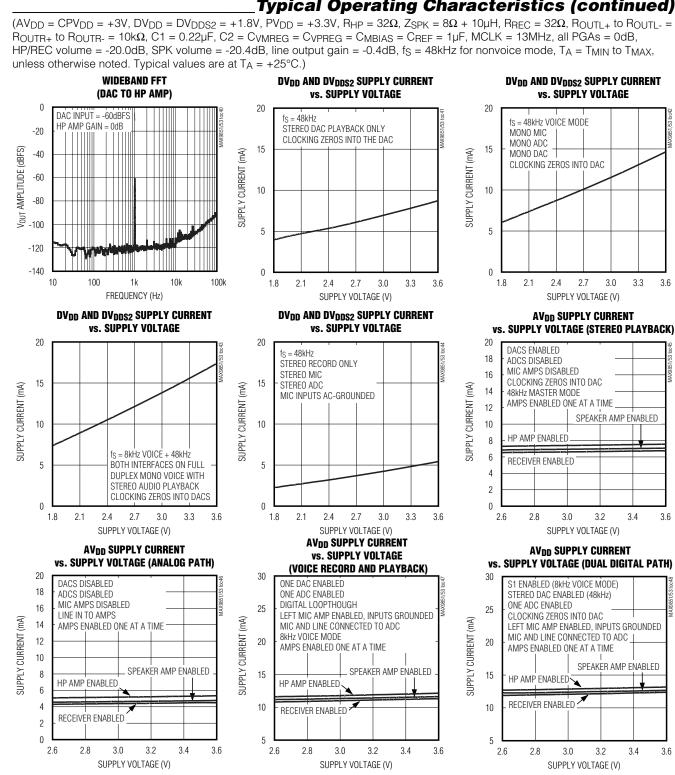

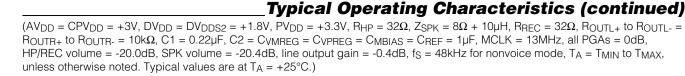

$(AV_{DD} = CPV_{DD} = +3V, DV_{DD} = DV_{DDS2} = +1.8V, PV_{DD} = +3.3V, R_{HP} = 32\Omega, Z_{SPK} = 8\Omega + 10\mu H, R_{REC} = 32\Omega, R_{OUTL+} to R_{OUTL-} = -10\mu H, R_{REC} = -10\mu$  $10k\Omega$ , Routr+ to Routr- =  $10k\Omega$ , C1 =  $0.22\mu$ F, C2 = CNREG = CPREG = CINTMICBIAS, CMBIAS = CREF =  $1\mu$ F, MCLK = 13MHz, all PGAs = 0dB, HP/REC volume = -20.0dB, SPK volume = -20.4dB, line output gain = -0.4dB, TA = TMIN to TMAX, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (See Functional Diagrams/Typical Operating Circuits).

| PARAMETER              | SYMBOL                                   | CONDITIONS                                                           |                                                      | MIN | ТҮР | MAX | UNITS |

|------------------------|------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------|-----|-----|-----|-------|

| Analog Supply Voltage  | AV <sub>DD</sub> ,<br>CPV <sub>DD</sub>  | $AV_{DD} = CPV_{DD}$ , no                                            | 2.6                                                  |     | 3.3 | V   |       |

| Digital Supply Voltage | DV <sub>DD</sub> ,<br>DV <sub>DDS2</sub> | No load                                                              | No load                                              |     |     | 3.3 | V     |

| Speaker Supply Voltage | PVDD                                     | No load                                                              |                                                      | 2.6 |     | 5.5 | V     |

|                        |                                          |                                                                      | Stereo headphone                                     |     | 7.2 |     |       |

|                        |                                          | DAC playback<br>mode, no output<br>loads<br>(Note 1)                 | Stereo speaker<br>(MAX9851)/line output<br>(MAX9853) |     | 6.5 | 8.5 |       |

|                        |                                          |                                                                      | Mono receiver                                        |     | 6.4 |     |       |

|                        |                                          | Line only playback<br>mode, no output<br>loads                       | Stereo headphone                                     |     | 5.0 |     |       |

| Analog Supply Current  | AI <sub>DD</sub>                         |                                                                      | Stereo speaker<br>(MAX9851)/line output<br>(MAX9853) |     | 4.6 |     | mA    |

|                        |                                          |                                                                      | Mono receiver                                        |     | 4.4 |     |       |

|                        |                                          |                                                                      | Stereo headphone                                     |     | 7.2 |     |       |

|                        |                                          | DAC plus line<br>input playback<br>mode, no output<br>loads (Note 1) | Stereo speaker<br>(MAX9851)/line output<br>(MAX9853) |     | 6.4 |     |       |

|                        |                                          |                                                                      | Mono receiver                                        |     | 6.3 |     |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = CPV_{DD} = +3V, DV_{DD} = DV_{DDS2} = +1.8V, PV_{DD} = +3.3V, R_{HP} = 32\Omega, Z_{SPK} = 8\Omega + 10\mu$ H, R<sub>REC</sub> =  $32\Omega$ , R<sub>OUTL+</sub> to R<sub>OUTL+</sub> to

| PARAMETER                         | SYMBOL             | CONDITIONS                                                                  |                                                      | MIN     | ТҮР  | MAX  | UNITS |

|-----------------------------------|--------------------|-----------------------------------------------------------------------------|------------------------------------------------------|---------|------|------|-------|

|                                   |                    |                                                                             | Stereo headphone                                     |         | 11.9 |      |       |

|                                   |                    | Full-duplex voice<br>mode, no output<br>loads                               | Stereo speaker<br>(MAX9851)/line output<br>(MAX9853) |         | 11.2 |      |       |

|                                   |                    |                                                                             | Mono receiver                                        |         | 11.1 | 14.5 |       |

|                                   |                    | Full-duplex voice                                                           | Stereo headphone                                     |         | 11.9 |      |       |

| Analog Supply Current             | AI <sub>DD</sub>   | mode plus DAC<br>playback mode,<br>no output loads                          | Stereo speaker<br>(MAX9851)/line output<br>(MAX9853) |         | 11.2 |      | mA    |

|                                   |                    | (Notes 1, 2)                                                                | Mono receiver                                        |         | 11.1 |      |       |

|                                   |                    | ADC record mode (                                                           | Note 3)                                              |         | 12.2 |      | 1     |

|                                   |                    | ADC record mode p<br>playback mode (No                                      | olus DAC headphone<br>tes 1, 3)                      |         | 18.2 | 24.0 |       |

| Speaker Supply Current (Note 4)   |                    | Mono Class D speaker mode                                                   |                                                      |         | 5    |      |       |

|                                   | PIDD               | Stereo Class D spea                                                         | aker mode                                            |         | 10   | 14   | mA    |

|                                   |                    | Sleep mode (MAX9851, MAX9853)                                               |                                                      |         | 2    | 15   | μA    |

|                                   |                    | Playback operation (Note 1), no output loads                                |                                                      |         | 2.7  | 3.7  |       |

| Digital Supply Current            | DI <sub>DD</sub>   | Full duplex voice operation (Note 2), no output loads, $T_A = +25^{\circ}C$ |                                                      |         | 6.2  | 7.8  | mA    |

|                                   |                    | Record operation (N                                                         | Record operation (Notes 1, 3)                        |         | 3.9  | 5.2  |       |

| Analog Shutdown Current           | AI <sub>SHDN</sub> | IAVDD + ICPVDD, TA                                                          | = +25°C                                              |         | 1.4  | 20   | μA    |

| Digital Shutdown Current          | DISHDN             | IDVDD + IDVDDS2, T                                                          | A = +25°C                                            |         | 0.5  | 10   | μA    |

| PV <sub>DD</sub> Shutdown Current | Discourse          |                                                                             | MAX9851                                              |         | 1    | 20   |       |

| (Note 4)                          | PISHDN             | $I_{PVDD}, T_A = +25^{\circ}C$                                              | MAX9853                                              |         | 0.1  | 5    | μA    |

| Shutdown to Full Operation        | ton                | ADC and DAC fu mode                                                         | lly operational, master                              |         | 70   |      | ms    |

| DAC PERFORMANCE (Note 5) (D       | AC in Maste        | r Mode)                                                                     |                                                      |         |      |      |       |

| Gain Error                        |                    |                                                                             |                                                      |         | ±1   | ±7   | %     |

| Channel Gain Matching             |                    |                                                                             |                                                      |         | ±1   |      | %     |

| Dynamic Range (Note 6)            | DR                 | fs = 8kHz (voice modes), headphone<br>volume = +5.5dB                       |                                                      |         | 75.5 |      | dB    |

| Dynamic nange (NOLE D)            | Un                 | f <sub>S</sub> = 8kHz and 48kH<br>headphone volume                          | z (stereo audio modes),<br>= +5.5dB                  | 84 87.5 |      |      | dB    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| MAX   | UNITS    |

|-------|----------|

| )     | dB       |

| )     |          |

|       | alD      |

|       | - dB     |

|       | dB       |

|       | dB       |

|       | UB       |

|       |          |

|       | fs       |

| ±0.2  | dB       |

| 0.58  | fs       |

|       | dB       |

| -     | dB       |

|       |          |

| 175   | Hz       |

| 130   | Hz       |

| ±0.2  | dB       |

|       | Hz       |

|       | dB       |

|       | <u> </u> |

| 350   | Hz       |

| 260   | Hz       |

| ±0.2  | dB       |

|       | Hz       |

|       | dB       |

|       | <u> </u> |

|       | Hz       |

| ±0.05 | dB       |

| 3900  | Hz       |

|       | dB       |

|       | 3900     |

MAX9851/MAX9853

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = CPV_{DD} = +3V, DV_{DD} = DV_{DDS2} = +1.8V, PV_{DD} = +3.3V, R_{HP} = 32\Omega, Z_{SPK} = 8\Omega + 10\mu$ H, R<sub>REC</sub> =  $32\Omega$ , R<sub>OUTL+</sub> to R<sub>OUTL+</sub> to

| PARAMETER                             | SYMBOL          | COND                                                      | MIN                                                                             | ТҮР   | MAX   | UNITS |    |  |

|---------------------------------------|-----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|----|--|

| DAC VOICEBAND LOWPASS                 | FILTER (S1 Moi  | no Voice Audio Input I                                    | Path, f <sub>S</sub> = 16kHz)                                                   |       |       |       |    |  |

| Stopband Cutoff                       | fPL             |                                                           |                                                                                 | 7000  |       |       | Hz |  |

| Passband Ripple                       |                 | f < fpL                                                   | f < fpL                                                                         |       |       | ±0.05 | dB |  |

| Stopband Cutoff                       | fsl             |                                                           |                                                                                 |       |       | 7800  | Hz |  |

| Stopband Attenuation                  |                 | $f > f_{SL}$                                              |                                                                                 | 75    |       |       | dB |  |

| DAC ADJUSTABLE HIGHPAS                | S FILTER        |                                                           |                                                                                 |       |       |       |    |  |

| DC Attenuation                        | DCATT           | Register 0x07 bits [3:0                                   | 0] = 0x5, 0xA, or 0xF                                                           |       | 90    |       | dB |  |

|                                       |                 | Register 0x07 [3:0] =                                     | 0x5                                                                             | 55    |       | 91    |    |  |

| Highpass Cutoff (-3dB)                | fP              | Register 0x07 [3:0] =                                     | 0xA                                                                             | 171   |       | 279   | Hz |  |

|                                       |                 | Register 0x07 [3:0] =                                     | 0xF                                                                             | 327   |       | 533   |    |  |

| DAC INPUT GAIN CONTROL (              | Register 0x0C a | and 0x0D)                                                 |                                                                                 |       |       |       |    |  |

| Gain Control Range                    |                 | For both input data inf                                   | terfaces                                                                        | -96   |       | 0     | dB |  |

| ADC DC ACCURACY                       |                 |                                                           |                                                                                 |       |       |       |    |  |

| Gain Error                            |                 |                                                           |                                                                                 |       | ±1    | ±7    | %  |  |

| Full-Scale Conversion                 | 0dBFS           | $f_{IN} = 1 kHz$ , line input,                            |                                                                                 | 2.05  |       | VP-P  |    |  |

| Channel Gain Matching                 |                 |                                                           |                                                                                 |       | ±1    |       | %  |  |

| ADC DYNAMIC SPECIFICATIO              | ONS (Note 8)    |                                                           |                                                                                 |       |       |       |    |  |

|                                       |                 | $BW = 22Hz$ to $f_S / 2$ (8)                              | 73                                                                              | 75    |       |       |    |  |

| Dynamic Range (Note 6)                | DR              | BW = 22Hz to 20kHz<br>(48kHz stereo audio                 | T <sub>A</sub> = +25°C                                                          | 77    | 82    |       | dB |  |

|                                       |                 | modes, A-weighted)                                        | $T_A = T_{MIN}$ to $T_{MAX}$                                                    | 71    |       |       |    |  |

|                                       |                 | $BW = 22Hz \text{ to } f_S / 2 (8)$                       |                                                                                 | -85.5 |       |       |    |  |

|                                       |                 | 1kHz, 0dBFS, f <sub>S</sub> = 8kH                         | Hz (voice mode)                                                                 |       | -85.5 |       |    |  |

| Total Harmonic Distortion             | THD             | 1kHz, 0dBFS, $f_S = 48k$<br>mode)                         | <hz (stereo="" audio<="" td=""><td></td><td>-85.5</td><td></td><td>dB</td></hz> |       | -85.5 |       | dB |  |

|                                       |                 | 1kHz, 0dBFS, f <sub>S</sub> = 8kł                         | Hz (voice mode)                                                                 |       | 75    |       |    |  |

| Signal-to-Noise Ratio                 | SNR             | 1kHz, 0dBFS, $f_S = 48k$<br>mode, A-weighted)             | , ,                                                                             |       | 81.5  |       | dB |  |

|                                       |                 | 1kHz, 0dBFS, fs = 8kHz (stereo audio<br>mode, A-weighted) |                                                                                 |       | 87.5  |       | 20 |  |

| Channel Crosstalk                     |                 | Driven channel at -1c<br>48kHz (from MICL t<br>ADCL)      |                                                                                 | -75   |       | dB    |    |  |

|                                       |                 | $AV_{DD} = 2.6V$ to $3.3V$                                |                                                                                 | 48    | 63    |       |    |  |

| Power-Supply Rejection Ratio (Note 9) | PSRR            | PSRR $f = 217Hz$ , $V_{RIPPLE} = 100mV_{P-P}$             |                                                                                 |       | 63    |       | dB |  |

| (11018 3)                             |                 | f = 10kHz, VRIPPLE =                                      | 100mV <sub>P-P</sub>                                                            |       | 50    |       |    |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                  | SYMBOL           | CONDITIONS                                                                            | MIN    | ТҮР                      | MAX    | UNITS |

|------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|--------|--------------------------|--------|-------|

| ADC DIGITAL FILTER PATH (St                                | ereo Audio M     | odes)                                                                                 | •      |                          |        |       |

| Passband Cutoff                                            | fPBL             |                                                                                       | 0.44   |                          |        | fs    |

| Passband Ripple                                            |                  | f < f <sub>PBL</sub>                                                                  |        |                          | ±0.5   | dB    |

| Stopband Cutoff                                            | f <sub>SBL</sub> |                                                                                       |        |                          | 0.58   | fs    |

| Stopband Attenuation                                       |                  | f > f <sub>SBL</sub>                                                                  | 53     |                          |        | dB    |

| Attenuation at fs/2                                        |                  |                                                                                       |        | -6.02                    |        | dB    |

| ADC VOICEBAND HIGHPASS F                                   | LTER (S1 Mo      | no Voice Input Path, f <sub>S</sub> = 8kHz)                                           |        |                          |        |       |

| Passband Cutoff                                            | fрн              |                                                                                       |        |                          | 175    | Hz    |

| Passband -3dB Cutoff                                       | fрз_н            |                                                                                       |        |                          | 130    | Hz    |

| Passband Ripple                                            |                  | f > fPH                                                                               |        |                          | ±0.2   | dB    |

| Stopband Cutoff                                            | fsн              |                                                                                       | 77     |                          |        | Hz    |

| Stopband Attenuation                                       |                  | f < f <sub>SH</sub>                                                                   | 28     |                          |        | dB    |

| ADC VOICEBAND HIGHPASS F                                   | LTER (S1 Mo      | no Voice Input Path, f <sub>S</sub> = 16kHz)                                          |        |                          |        |       |

| Passband Cutoff                                            | fрн              |                                                                                       |        |                          | 350    | Hz    |

| Passband -3dB Cutoff                                       | fрз_н            |                                                                                       |        |                          | 260    | Hz    |

| Passband Ripple                                            |                  | f > fPH                                                                               |        |                          | ±0.2   | dB    |

| Stopband Cutoff                                            | fsн              |                                                                                       | 154    |                          |        | Hz    |

| Stopband Attenuation                                       |                  | f < f <sub>SH</sub>                                                                   | 28     |                          |        | dB    |

| ADC VOICEBAND LOWPASS FI                                   | LTER (S1 Mo      | no Voice Input Path, f <sub>S</sub> = 8kHz)                                           |        |                          |        |       |

| Passband Cutoff                                            | f <sub>PL</sub>  |                                                                                       | 3500   |                          |        | Hz    |

| Passband Ripple                                            |                  | f < fpL                                                                               |        |                          | ±0.05  | dB    |

| Stopband Cutoff                                            | fsL              |                                                                                       |        |                          | 3900   | Hz    |

| Stopband Attenuation                                       |                  | f > f <sub>SL</sub>                                                                   | 75     |                          |        | dB    |

| ADC VOICEBAND LOWPASS FI                                   | LTER (S1 Mo      | no Voice Input Path, f <sub>S</sub> = 16kHz)                                          |        |                          |        |       |

| Passband Cutoff                                            | fPL              |                                                                                       | 7000   |                          |        | Hz    |

| Passband Ripple                                            |                  | f < fpL                                                                               |        |                          | ±0.05  | dB    |

| Stopband Cutoff                                            | fsL              |                                                                                       |        |                          | 7800   | Hz    |

| Stopband Attenuation                                       |                  | f > f <sub>SL</sub>                                                                   | 75     |                          |        | dB    |

| ADC DC-BLOCKING FILTER                                     |                  |                                                                                       |        |                          |        |       |

| DC-Blocking Filter -3dB Corner                             | fC               | As a fraction of output sample rate                                                   |        | f <sub>S</sub> /<br>1608 |        | Hz    |

| DC Attenuation                                             |                  |                                                                                       |        | 120                      |        | dB    |

| Maximum DC Input                                           |                  |                                                                                       |        | 0.125                    |        | V     |

| DAC/ADC DATA RATE ACCURA                                   | CY               |                                                                                       |        |                          |        |       |

| LRCLK Output Sample Rate<br>Deviation From Ideal (Note 10) |                  | $f_S = 8kHz$ to $48kHz$ (master mode with DAC only enabled) (See Table 1 for details) | -0.025 |                          | +0.025 | %     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = CPV_{DD} = +3V, DV_{DD} = DV_{DDS2} = +1.8V, PV_{DD} = +3.3V, R_{HP} = 32\Omega, Z_{SPK} = 8\Omega + 10\mu$ H, R<sub>REC</sub> =  $32\Omega$ , R<sub>OUTL+</sub> to R<sub>OUTL+</sub> to

| PARAMETER                                                  | SYMBOL           | CONDI                                                                   | TIONS                                  | MIN 1 | ГҮР МАХ                | UNITS |

|------------------------------------------------------------|------------------|-------------------------------------------------------------------------|----------------------------------------|-------|------------------------|-------|

| DAC/ADC DATA RATE ACCURA                                   | СҮ               |                                                                         |                                        |       |                        |       |

|                                                            |                  |                                                                         | f <sub>S</sub> = 8kHz (voice<br>mode)  |       | 0                      |       |

|                                                            |                  |                                                                         | f <sub>S</sub> = 16kHz (voice<br>mode) |       | 0                      |       |

|                                                            |                  |                                                                         | f <sub>S</sub> = 8kHz                  | (     | ).31                   |       |

|                                                            |                  | Master mode with                                                        | f <sub>S</sub> = 11.025kHz             | (     | ).27                   |       |

| LRCLK Output Sample Rate<br>Deviation From Ideal (Note 10) |                  | ADC SDOUT enabled; audio mode, unless                                   | $f_S = 12 kHz$                         | (     | ).31                   | %     |

| Deviation rom ideal (Note 10)                              |                  | otherwise noted                                                         | $f_S = 16 kHz$                         | -(    | 0.43                   |       |

|                                                            |                  |                                                                         | f <sub>S</sub> = 22.05kHz              | -(    | 0.41                   |       |

|                                                            |                  |                                                                         | $f_S = 24 kHz$                         | (     | ).31                   |       |

|                                                            |                  |                                                                         | $f_S = 32 kHz$                         | -(    | 0.43                   |       |

|                                                            |                  |                                                                         | $f_{S} = 44.1 \text{kHz}$              | -     | 1.74                   |       |

|                                                            |                  |                                                                         | $f_{\rm S} = 48 \text{kHz}$            | -(    | 0.43                   |       |

| LRCLK Input Sample Rate Range                              |                  | Synchronous or asynch mode with only DAC er                             |                                        | 7.8   | 50                     | kHz   |

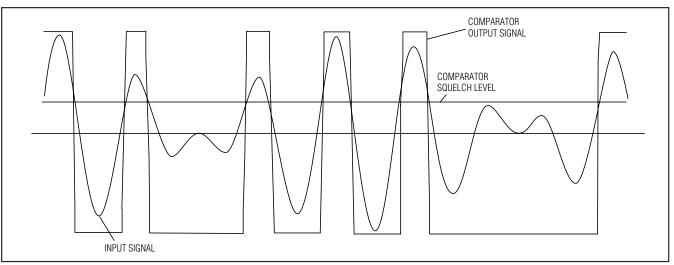

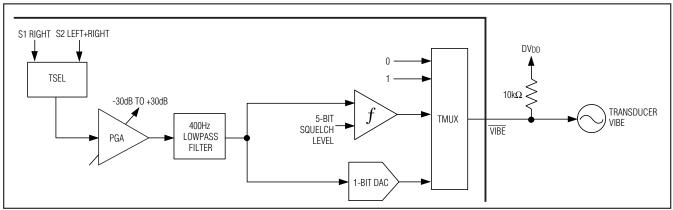

| DAC TRANSDUCER/VIBE OUTPU                                  | Л                |                                                                         |                                        |       |                        | •     |

| Vibe PGA Range                                             | TGAIN            | 11 steps in 6dB increm                                                  | ents                                   | -30   | +30                    | dB    |

| 0dBFS Output Voltage                                       |                  | 1-bit DAC output exterr resistor to DV <sub>DD</sub> (TGAII             |                                        | ים    | V <sub>DD</sub> /<br>2 | VP-P  |

| Output Offset Voltage                                      |                  | 1-bit DAC output extern<br>signal, pullup resistor to                   |                                        | D'    | V <sub>DD</sub> /<br>2 | V     |

| Vibe PGA Output Resolution                                 | PGAR             |                                                                         |                                        |       | 10                     | bits  |

|                                                            |                  | f <sub>S</sub> = 8kHz, 16kHz, or 32                                     | 2kHz                                   |       | 483                    |       |

| LPF Passband -3dB Cutoff                                   | fPBL             | f <sub>S</sub> = 11.025kHz, 22.05k                                      | Hz, or 44.1kHz                         | (     | 665                    | Hz    |

|                                                            |                  | $f_{\rm S} = 12$ kHz, 24kHz, or 4                                       | l8kHz                                  |       | 724                    |       |

| LPF Stopband Attenuation                                   | f <sub>SBL</sub> | f > 3.5xf <sub>PBL</sub>                                                |                                        | 27    |                        | dB    |

| 1-Bit DAC Digital Dynamic Range                            | DRv              | Ideal dynamic range (0 to 8kHz or 0 to $f_S / 2$<br>for $f_S < 16kHz$ ) |                                        |       | 48                     | dB    |

| 1-Bit DAC Operating Frequency                              | fv               |                                                                         |                                        | (     | 650                    | kHz   |

| OPEN-DRAIN DIGITAL OUTPUT                                  | (VIBE)           |                                                                         |                                        |       |                        |       |

| Output High Current                                        | Іон              | V <sub>OUT</sub> = DV <sub>DD</sub>                                     |                                        |       | 3                      | μA    |

| Output Low Voltage                                         | Vol              | I <sub>OL</sub> = 3mA                                                   |                                        |       | 0.4                    | V     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                             | SYMBOL        | С                                                          | ONDIT                     | IONS                           |                   | MIN             | ТҮР  | MAX  | UNITS |  |

|-------------------------------------------------------|---------------|------------------------------------------------------------|---------------------------|--------------------------------|-------------------|-----------------|------|------|-------|--|

| HEADPHONE AMPLIFIERS                                  |               |                                                            |                           |                                |                   |                 |      |      |       |  |

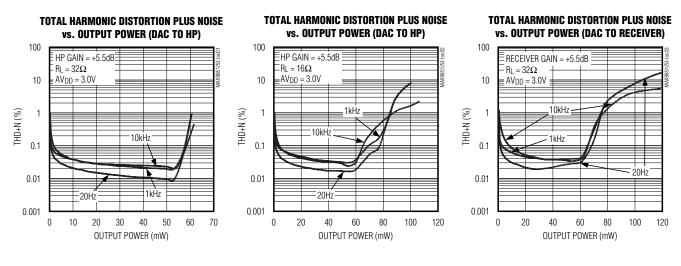

| Output Power                                          | Pour          | f = 1kHz, THD <                                            | 1%,                       | $R_L = 16\Omega$               |                   |                 | 80   |      | mW    |  |

| Output Power                                          | Pout          | volume +5.5dB                                              |                           | $R_L = 32\Omega$               |                   | 30              | 55   |      | TIVV  |  |

| 0dBFS Output Voltage                                  |               | +4.5dB volume s signal from the a                          |                           |                                | -scale            | 3.14            | 3.38 | 3.62 | Vp-p  |  |

|                                                       |               |                                                            | attina                    | Stereo/mo                      | ono               | 1.54            | 1.66 | 1.78 | V/V   |  |

| Line In to HP Out Voltage Gain                        |               | +4.5dB volume s                                            | etting                    | Balanced                       | mono              | 3.1             | 3.35 | 3.6  | V/V   |  |

| Output Offset Voltage                                 | Vos           |                                                            |                           |                                |                   |                 | 10   | 40   | mV    |  |

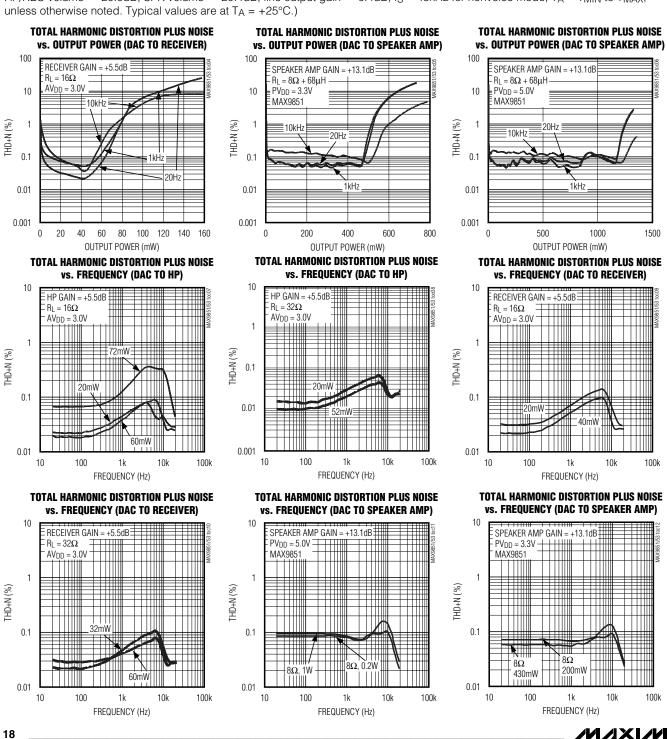

| Total Harmonic Distortion Plus                        | THD+N         | $R_L = 32\Omega$ , $P_{OUT}$<br>BW = 22Hz to 20            |                           | N, f = 1kHz                    | ,<br>-,           |                 | 0.03 |      | ~ %   |  |

| Noise                                                 |               | $R_L = 16\Omega, P_{OUT}$<br>BW = 22Hz to 20               |                           | N, f = 1kHz                    | ,<br>-,           |                 | 0.03 |      | 70    |  |

| Dynamic Range                                         | DR            | +5.5dB volume setting (DAC input to HP output), A-weighted |                           |                                | 70                | 87.5            |      | dB   |       |  |

|                                                       |               | AV <sub>CC</sub> = 2.6V to 3.6V                            |                           |                                | 60                | 95              |      |      |       |  |

| Power-Supply Rejection Ratio<br>(DAC Input to HP Out) | PSRR          | $V_{RIPPLE} = 100 mV_{P-P}, f = 217 Hz$                    |                           |                                |                   | 95              |      | dB   |       |  |

|                                                       |               | VRIPPLE = 100m                                             | / <sub>P-P</sub> , f =    | = 10kHz                        |                   |                 | 68   |      |       |  |

| Maximum Capacitive Load                               | CL            | No sustained osc                                           | No sustained oscillations |                                |                   |                 | 150  |      | рF    |  |

| Crosstalk (Line Input to<br>Headphone Output)         |               | $R_L = 32\Omega$ , $P_{OUT}$                               | = 1.6m                    | W, f = 1kH                     | Z                 |                 | -85  |      | dB    |  |

| Channel Gain Matching                                 | AVMATCH       | Line input to hea                                          | dphone                    | e output                       |                   |                 | ±1   |      | %     |  |

| 0                                                     |               | Peak voltage, 32<br>samples per sec                        |                           | Into shuto<br>disabled         | down, HP          |                 | -53  |      |       |  |

| Click-and-Pop Level                                   | KCP           | A-weighted,<br>$R_L = 32\Omega$ (Note 11)                  |                           | Out of shutdown,<br>HP enabled |                   |                 | -48  |      | dBV   |  |

| SPEAKER AMPLIFIERS (MAX98                             | 51) (Note 12) |                                                            |                           | •                              |                   |                 |      |      | •     |  |

|                                                       |               |                                                            |                           | = 3.3V,<br>-N < 1%             | $R_L = 8\Omega$   |                 | 500  |      |       |  |

| 0.1.15                                                |               | f = 1 kHz,<br>2V <sub>P-P</sub> line input,                |                           | = 5V,<br>-N < 1%               | $R_L = 8\Omega$   |                 | 1150 |      | <br>  |  |

| Output Power                                          | Pout          | +13.1dB<br>speaker amp<br>volume setting                   |                           | = 3.3V,<br>-N < 10%            | $R_L = 8\Omega$   |                 | 600  |      | mW    |  |

|                                                       |               | P\                                                         | PV[                       | PVDD                           | = 5V,<br>-N < 10% | $R_L = 8\Omega$ |      | 1250 |       |  |

| 0dBFS Output Voltage                                  |               | +12.1dB volume                                             | settino                   | , Pvdd = +                     | -5V               |                 | 8.4  |      | Vp-p  |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = CPV_{DD} = +3V, DV_{DD} = DV_{DDS2} = +1.8V, PV_{DD} = +3.3V, R_{HP} = 32\Omega, Z_{SPK} = 8\Omega + 10\mu$ H, R<sub>REC</sub> =  $32\Omega$ , R<sub>OUTL+</sub> to R<sub>OUTL-</sub> =  $10k\Omega$ , R<sub>OUTR+</sub> to R<sub>OU</sub>

| PARAMETER                                  | SYMBOL          | CONDITI                                                                                                                         | ONS             | MIN  | ТҮР   | МАХ  | UNITS |

|--------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|------|-------|

| Line In to Speaker Out Voltage<br>Gain     |                 | +12.1dB volume setting,                                                                                                         | $P_{VDD} = +5V$ | 4.0  | 4.2   | 4.4  | V/V   |

| Output Offset Voltage                      | Vos             |                                                                                                                                 |                 |      | 10    | 100  | mV    |

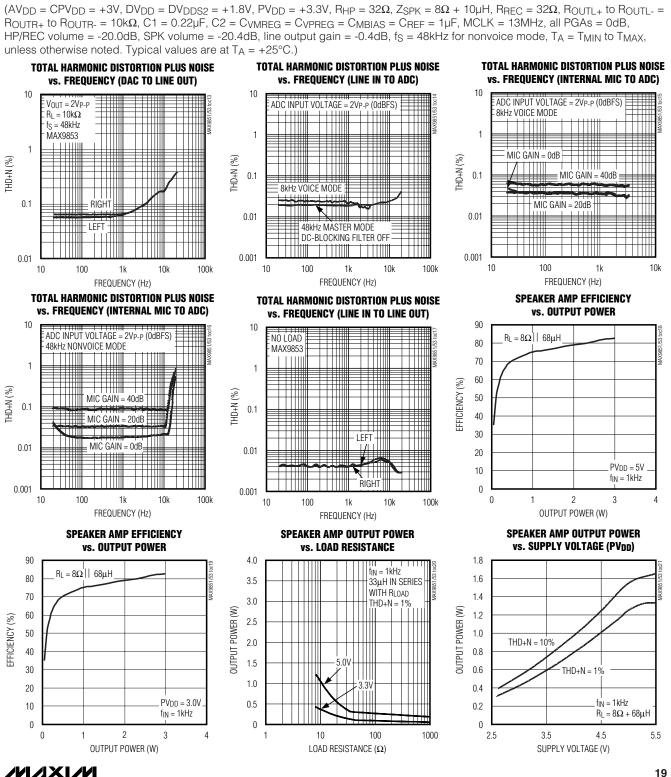

| Total Harmonic Distortion Plus<br>Noise    | THD+N           | $R_L = 8\Omega$ , $P_{OUT} = 125mW$<br>22Hz to 20kHz, +10.1dB                                                                   |                 |      | 0.03  |      | %     |

| Dynamic Range                              | DR              | +12.1dB volume setting,                                                                                                         | A-weighted      |      | 90    |      | dB    |

|                                            |                 | $PV_{DD} = 2.6V \text{ to } 5.5V$                                                                                               |                 | 50   | 70    |      |       |

| Power-Supply Rejection Ratio               | PSRR            | $V_{RIPPLE} = 100mV_{P-P}, f =$                                                                                                 | 217Hz           |      | 70    |      | dB    |

|                                            |                 | VRIPPLE = 100mVP-P, f =                                                                                                         | 10kHz           |      | 55    |      |       |

| Crosstalk                                  |                 | $R_L = 8\Omega$ , $P_{OUT} = 100$ mW                                                                                            | /, f = 1kHz     |      | 60    |      | dB    |

| Channel Gain Matching                      | AVMATCH         |                                                                                                                                 |                 |      | ±4    |      | %     |

| Class D Switching Frequency                |                 |                                                                                                                                 |                 |      | 1100  |      | kHz   |

| Click-and-Pop Level                        | K <sub>CP</sub> | Peak voltage, 32-<br>samples per second,                                                                                        | Into shutdown   |      | -35   |      | dBV   |

|                                            | NCP             | $ \begin{array}{l} \mbox{A-weighted} \\ \mbox{R}_L = 8\Omega \mbox{ (Note 11)} \end{array} \mbox{Out of shutdown} \end{array} $ |                 | -35  |       |      | UDV   |

| Efficiency                                 |                 | POUT = 1W per channel,                                                                                                          | $R_L = 8\Omega$ |      | 75    |      | %     |

| LINE OUTPUT AMPLIFIERS (MA                 | X9853) (Note    | 12)                                                                                                                             |                 |      |       |      |       |

| Line Output Common-Mode<br>Voltage         |                 |                                                                                                                                 |                 | 1.13 | 1.23  | 1.33 | V     |

| Line Output Differential Offset<br>Voltage |                 |                                                                                                                                 |                 | -90  |       | +90  | mV    |

| Maximum Differential Output<br>Voltage     |                 |                                                                                                                                 |                 | 3.16 | 4.16  | 4.74 | Vp-p  |

| Dynamic Range                              | DR              | 1.4mV <sub>RMS</sub> (-60dB) outpu<br>A-weighted                                                                                | it voltage,     |      | 88    |      | dB    |

| Total Harmonic Distortion Plus<br>Noise    | THD+N           | $f_{IN} = 1$ kHz, $V_{OUT} = 2V_{P-P}$ , BW = 22Hz to 20kHz                                                                     |                 |      | 0.004 |      | %     |

|                                            |                 | $AV_{DD} = 2.6V \text{ to } 3.6V$                                                                                               |                 | 57   | 100   |      |       |

| Power-Supply Rejection Ratio               | PSRR            | VRIPPLE = 100mVP-P, f =                                                                                                         | 217Hz           |      | 95    |      | dB    |

|                                            |                 | VRIPPLE = 100mVP-P, f =                                                                                                         | 20kHz           |      | 55    |      | 1     |

| Line Input to Line Output Gain<br>Accuracy |                 |                                                                                                                                 |                 | -0.4 |       | +0.6 | dB    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                | SYMBOL          | CON                                                                                                                                                                                                                                                                                                                | IDITIONS                                                            | MIN   | ТҮР   | MAX   | UNITS |

|----------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|

| <b>RECEIVER AMPLIFIER (Note 12)</b>                      |                 |                                                                                                                                                                                                                                                                                                                    |                                                                     |       |       |       |       |

|                                                          |                 |                                                                                                                                                                                                                                                                                                                    | $R_L = 16\Omega$ , input signal from LINEIN1                        |       | 80    |       |       |

| Output Power                                             | Роит            | f = 1kHz, THD <<br>1%, +5.5dB<br>volume setting                                                                                                                                                                                                                                                                    | $R_L = 16\Omega$ , input signal<br>is the sum of<br>LINEIN1+LINEIN2 |       | 105   |       | mW    |

|                                                          |                 |                                                                                                                                                                                                                                                                                                                    | $R_L = 32\Omega$ , input signal from LINEIN1                        | 35    | 55    |       |       |

| Maximum Output Voltage                                   |                 |                                                                                                                                                                                                                                                                                                                    | ing, 0dB PGA setting,<br>from DAC output, only 1                    | 3.09  | 3.35  | 3.64  | Vp-p  |

| Line In to REC Out Voltage Gain                          |                 | +4.5dB volume setti<br>only 1 input selected                                                                                                                                                                                                                                                                       | ing, 0dB PGA setting,<br>d                                          | 1.54  | 1.68  | 1.82  | V/V   |

| Output Offset Voltage                                    | Vos             |                                                                                                                                                                                                                                                                                                                    |                                                                     |       | 10    | 60    | mV    |

| Total Harmonic Distortion Plus                           | THD+N           | $\begin{aligned} R_L &= 32\Omega, P_{OUT} = 40\text{mW}, \text{f} = 1\text{kHz}, \text{BW} = \\ 22\text{Hz to } 20\text{kHz}, +3\text{dB volume setting} \\ R_L &= 16\Omega, P_{OUT} = 40\text{mW}, \text{f} = 1\text{kHz}, \text{BW} = \\ 22\text{Hz to } 20\text{kHz}, +3\text{dB volume setting} \end{aligned}$ |                                                                     |       | 0.03  |       | %     |

| Noise                                                    |                 |                                                                                                                                                                                                                                                                                                                    |                                                                     |       | 0.04  |       | 70    |

| Dynamic Range                                            | DR              | +6dB volume setting                                                                                                                                                                                                                                                                                                | g, A-weighted                                                       |       | 92    |       | dB    |

|                                                          |                 | $AV_{DD} = 2.6V$ to $3.3V$                                                                                                                                                                                                                                                                                         |                                                                     | 60    | 100   |       |       |

| Power-Supply Rejection Ratio                             | PSRR            | $V_{RIPPLE} = 100 m V_{P-F}$                                                                                                                                                                                                                                                                                       | o, f = 217Hz                                                        |       | 98    |       | dB    |

|                                                          |                 | $V_{RIPPLE} = 100 m V_{P-F}$                                                                                                                                                                                                                                                                                       | p, f = 20kHz                                                        |       | 65    |       |       |

| Maximum Capacitive Load                                  | CL              | No sustained oscilla                                                                                                                                                                                                                                                                                               | itions                                                              |       | 150   |       | pF    |

| Click-and-Pop Level                                      | K <sub>CP</sub> | Peak voltage, 32 sa A-weighted, $R_L = 16$                                                                                                                                                                                                                                                                         |                                                                     |       | -44.6 |       | dBV   |

| VOLUME CONTROL/PGAs                                      | -               |                                                                                                                                                                                                                                                                                                                    |                                                                     |       |       |       |       |

| Headphone/Receiver Volume<br>Control Range               |                 |                                                                                                                                                                                                                                                                                                                    |                                                                     | -80   |       | +6.1  | dB    |

| Headphone/Receiver Mute<br>Attenuation                   |                 | f = 1kHz                                                                                                                                                                                                                                                                                                           |                                                                     |       | 100   |       | dB    |

| Speaker Volume Control Range<br>(MAX9851)                |                 |                                                                                                                                                                                                                                                                                                                    |                                                                     | -72.4 |       | +13.7 | dB    |

| Speaker Mute Attenuation<br>(MAX9851)                    |                 | f = 1kHz                                                                                                                                                                                                                                                                                                           |                                                                     |       | 100   |       | dB    |

| Differential Line Output Gain<br>Control Range (MAX9853) |                 |                                                                                                                                                                                                                                                                                                                    |                                                                     | -78.4 |       | +7.9  | dB    |

| Differential Line Output Mute<br>Attenuation (MAX9853)   |                 | f = 1kHz                                                                                                                                                                                                                                                                                                           |                                                                     |       | 100   |       | dB    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = CPV_{DD} = +3V, DV_{DD} = DV_{DDS2} = +1.8V, PV_{DD} = +3.3V, R_{HP} = 32\Omega, Z_{SPK} = 8\Omega + 10\mu$ H, R<sub>REC</sub> =  $32\Omega$ , R<sub>OUTL+</sub> to R<sub>OUTL+</sub> to

| PARAMETER                               | SYMBOL   |                                                            | CONDITIONS                                                | MIN   | ТҮР   | МАХ                                                                                                                                                                                                                            | UNITS  |

|-----------------------------------------|----------|------------------------------------------------------------|-----------------------------------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Sidetone Volume Control Range           |          |                                                            |                                                           | -34.0 |       | +30.5                                                                                                                                                                                                                          | dB     |

| Sidetone Mute Attenuation               |          | f = 1kHz, sidetone deselected from input mixer             |                                                           |       | 80    |                                                                                                                                                                                                                                | dB     |

| CHARGE PUMP                             |          |                                                            |                                                           |       |       |                                                                                                                                                                                                                                |        |

| Charge-Pump Oscillator<br>Frequency     | fosc     |                                                            |                                                           | 295   | 650   | 1200                                                                                                                                                                                                                           | kHz    |

| MICROPHONE AMPLIFIERS                   |          | •                                                          |                                                           |       |       |                                                                                                                                                                                                                                |        |

| Preamplifier Gain                       | AVPRE    | EXTMIC_                                                    | $AV_{PRE} = +20dB$<br>$AV_{PRE} = +20dB$                  | +18.5 |       | +20.5                                                                                                                                                                                                                          | dB     |

| MIC PGA Gain                            | AVMICPGA | PGA gain = $00$                                            | dB                                                        | -0.9  |       | +0.4                                                                                                                                                                                                                           | dB     |

| MIC Mute Attenuation                    |          | PGA gain = $+3$<br>f = 1kHz                                | 200B                                                      | +18.5 | 105   | +20.5                                                                                                                                                                                                                          | dB     |

| Common-Mode Rejection Ratio             | CMRR     |                                                            | = 100mV <sub>P-P</sub> at 217Hz,<br>IB                    |       | 80    |                                                                                                                                                                                                                                | dB     |

| MIC Input Voltage Range                 |          | INTMIC_, EXT                                               | MIC_                                                      | -1    |       | +1                                                                                                                                                                                                                             | V      |

| wite input voltage hange                |          | EXTMICGND                                                  |                                                           | -0.1  |       | +0.1                                                                                                                                                                                                                           | v      |

| MIC Input Resistance                    | RIN_MIC  | INTMIC_, EXT                                               | MIC_                                                      | 30    | 50    | 70                                                                                                                                                                                                                             | kΩ     |

| MIC GND Sense Input<br>Resistance       | RIN_MICS | EXTMICGND                                                  |                                                           | 15    | 25    | 36                                                                                                                                                                                                                             | kΩ     |

| MIC Input Resistance Matching           | Rматсн   | INTMICP to INTMICN or EXTMICL to<br>EXTMICR                |                                                           |       | 0.3   |                                                                                                                                                                                                                                | %      |

| MIC Input Bias Voltage                  | VCML     | Measured at INTMIC_, EXTMIC_, and EXTMICGND                |                                                           | -0.1  | 0     | +0.1                                                                                                                                                                                                                           | V      |

| Input Voltage Noise                     | EIN_MIC  | f = 1kHz, AV <sub>PF</sub>                                 | $RE = +20$ dB, $R_{SOURCE} = 0\Omega$                     |       | 25    |                                                                                                                                                                                                                                | nV/√Hz |

|                                         |          |                                                            | AV <sub>MICPGA</sub> = 0dB,<br>= 1kHz, BW = 22Hz to 20kHz |       | 0.035 |                                                                                                                                                                                                                                |        |

| Total Harmonic Distortion Plus<br>Noise | THD+N    | $V_{IN} = 200 m V_P$                                       | IB, AV <sub>MICPGA</sub> = 0dB,<br>_P,<br>= 22Hz to 20kHz |       | 0.035 |                                                                                                                                                                                                                                | %      |

|                                         |          | $AV_{PRE} = +20c$<br>$V_{IN} = 20mV_{P-F}$<br>BW = 22Hz to |                                                           |       | 0.06  |                                                                                                                                                                                                                                |        |

|                                         |          | $AV_{DD} = 2.6V t$                                         | o 3.3V, T <sub>A</sub> = +25°C                            | 48    | 65    |                                                                                                                                                                                                                                | dB     |

| MIC Power-Supply Rejection<br>Ratio     | PSRR     | VRIPPLE = 100<br>output referred                           | mV <sub>P-P</sub> at 217Hz,<br>d                          |       | 65    |                                                                                                                                                                                                                                | dB     |

| Παιιυ                                   |          | VRIPPLE = 100<br>output referred                           | mVp-p at 10kHz,                                           |       | 65    | $ \begin{array}{c} +1 \\ +0.1 \\ \hline 0 70 \\ \hline 5 36 \\ \hline 3 \\ 0 +0.1 \\ \hline 5 \\ 35 \\ \hline 35 \\ \hline 06 \\ \hline 5 \\ \hline 5 \\ \hline 6 \\ \hline 7 \\ 7 \\ 7 \\ 7 \\ 7 \\ 7 \\ 7 \\ 7 \\ 7 \\ 7 \\$ | dB     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                  | SYMBOL             | CONDITIONS                                     | MIN                            | ТҮР                        | MAX                        | UNITS               |

|--------------------------------------------|--------------------|------------------------------------------------|--------------------------------|----------------------------|----------------------------|---------------------|

| MICROPHONE BIAS                            | •                  |                                                |                                |                            |                            |                     |

| INTMICBIAS Output Voltage                  | VMICBIAS           |                                                | 2.3                            | 2.4                        | 2.5                        | V                   |

| INTMICBIAS Load Regulation                 |                    | IMICBIAS = 0 to 2mA                            |                                | 0.7                        | 10                         | Ω                   |

| INTMICBIAS Minimum Capacitive Load         |                    |                                                |                                | 1                          |                            | μF                  |

| INTMICBIAS Short-Circuit Current           |                    | To AGND                                        |                                | 15                         |                            | mA                  |

|                                            |                    | $AV_{DD} = 2.6V$ to 3.3V, $T_A = +25^{\circ}C$ |                                | 72                         |                            | dB                  |

| INTMICBIAS Power-Supply<br>Rejection Ratio | PSRR               | V <sub>RIPPLE</sub> = 100mV at 217Hz           |                                | 85                         |                            | dB                  |

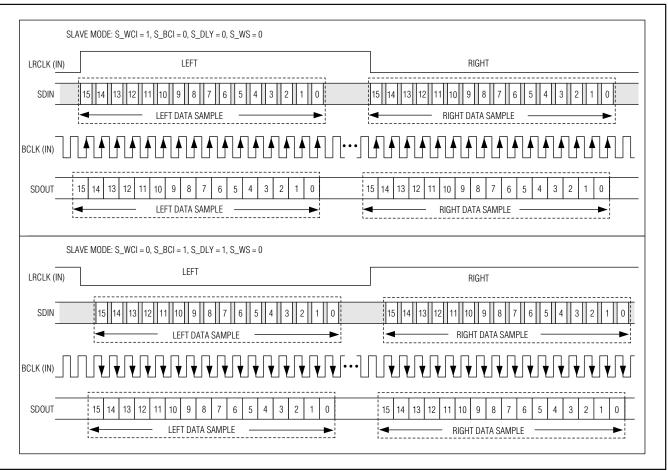

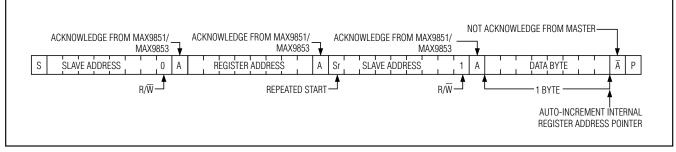

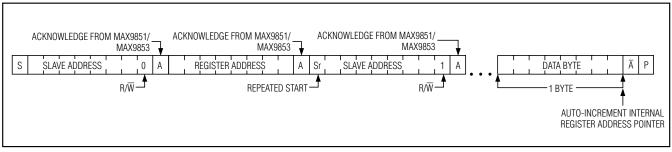

|                                            |                    | VRIPPLE = 100mV at 10kHz                       |                                | 70                         |                            | Ω<br>μF<br>mA<br>dB |