# Low Cost Analog Multiplier

Data Sheet AD633

#### **FEATURES**

4-quadrant multiplication

Low cost, 8-lead SOIC and PDIP packages

Complete—no external components required

Laser-trimmed accuracy and stability

Total error within 2% of full scale

Differential high impedance X and Y inputs

High impedance unity-gain summing input

Laser-trimmed 10 V scaling reference

#### **APPLICATIONS**

Multiplication, division, squaring Modulation/demodulation, phase detection Voltage-controlled amplifiers/attenuators/filters

#### **GENERAL DESCRIPTION**

The AD633 is a functionally complete, four-quadrant, analog multiplier. It includes high impedance, differential X and Y inputs, and a high impedance summing input (Z). The low impedance output voltage is a nominal 10 V full scale provided by a buried Zener. The AD633 is the first product to offer these features in modestly priced 8-lead PDIP and SOIC packages.

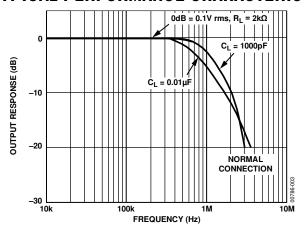

The AD633 is laser calibrated to a guaranteed total accuracy of 2% of full scale. Nonlinearity for the Y input is typically less than 0.1% and noise referred to the output is typically less than 100  $\mu V$  rms in a 10 Hz to 10 kHz bandwidth. A 1 MHz bandwidth, 20 V/ $\mu s$  slew rate, and the ability to drive capacitive loads make the AD633 useful in a wide variety of applications where simplicity and cost are key concerns.

The versatility of the AD633 is not compromised by its simplicity. The Z input provides access to the output buffer amplifier, enabling the user to sum the outputs of two or more multipliers, increase the multiplier gain, convert the output voltage to a current, and configure a variety of applications. For further information, see the Multiplier Application Guide.

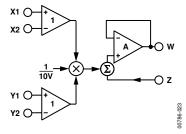

#### **FUNCTIONAL BLOCK DIAGRAM**

Fiaure 1.

The AD633 is available in 8-lead PDIP and SOIC packages. It is specified to operate over the  $0^{\circ}$ C to  $70^{\circ}$ C commercial temperature range (J Grade) or the  $-40^{\circ}$ C to  $+85^{\circ}$ C industrial temperature range (A Grade).

#### **PRODUCT HIGHLIGHTS**

- 1. The AD633 is a complete four-quadrant multiplier offered in low cost 8-lead SOIC and PDIP packages. The result is a product that is cost effective and easy to apply.

- 2. No external components or expensive user calibration are required to apply the AD633.

- 3. Monolithic construction and laser calibration make the device stable and reliable.

- 4. High (10 M $\Omega$ ) input resistances make signal source loading negligible.

- 5. Power supply voltages can range from ±8 V to ±18 V. The internal scaling voltage is generated by a stable Zener diode; multiplier accuracy is essentially supply insensitive.

| TABLE OF CONTENTS                                                                                                |

|------------------------------------------------------------------------------------------------------------------|

| Features                                                                                                         |

| Applications1                                                                                                    |

| Functional Block Diagram1                                                                                        |

| General Description                                                                                              |

| Product Highlights                                                                                               |

| Revision History                                                                                                 |

| Specifications                                                                                                   |

| Absolute Maximum Ratings                                                                                         |

| Thermal Resistance                                                                                               |

| ESD Caution                                                                                                      |

|                                                                                                                  |

| Pin Configurations and Function Descriptions                                                                     |

| Typical Performance Characteristics                                                                              |

| Functional Description                                                                                           |

| Error Sources                                                                                                    |

| Applications Information9                                                                                        |

| Multiplier Connections                                                                                           |

|                                                                                                                  |

| REVISION HISTORY                                                                                                 |

| 3/15—Rev. J to Rev. K                                                                                            |

| Changes to General Description Section                                                                           |

| Changes to Figure 12 Caption and Figure 14 Caption9                                                              |

| Added Model Results Section, Examples of DC, Sin, and                                                            |

| Pulse Solutions Using Multisim Section, and Figure 24                                                            |

| Through Figure 29, Renumbered Sequentially                                                                       |

| Added Examples of DC, Sin, and Pulse Solutions Using                                                             |

| PSPICE Section, Examples of DC, Sin, and Pulse Solutions Using SIMatrix Section, and Figure 20 Through Figure 27 |

| Using SIMetrix Section, and Figure 30 Through Figure 37 14 Added Figure 38 Through Figure 41                     |

| 7. man 1. garo 00 1. manga 1. garo 11                                                                            |

| 9/13—Rev. I to Rev. J                                                                                            |

| Reorganized Layout                                                                                               |

| Change to Table 1                                                                                                |

| Changes to Figure 4                                                                                              |

| Added Figure 10, Renumbered Sequentially                                                                         |

| Changes to Figure 15                                                                                             |

| Changes to Figure 20                                                                                             |

| Changes to Figure 31                                                                                             |

| Added Figure 3213                                                                                                |

| 2/12—Rev. H to Rev. I                                                                                            |

| Changes to Figure 1                                                                                              |

| Changes to Figure 2                                                                                              |

| Changes to Generating Inverse Functions Section 8                                                                |

| Changes to Figure 15                                                                                             |

Added Evaluation Board Section and Figure 23 to Figure 29,

| Squaring and Frequency Doubling9                           |

|------------------------------------------------------------|

| Generating Inverse Functions9                              |

| Variable Scale Factor                                      |

| Current Output                                             |

| Linear Amplitude Modulator10                               |

| Voltage-Controlled, Low-Pass and High-Pass Filters 10      |

| Voltage-Controlled Quadrature Oscillator                   |

| Automatic Gain Control (AGC) Amplifiers11                  |

| Model Results                                              |

| Examples of DC, Sin, and Pulse Solutions Using Multisim 13 |

| Examples of DC, Sin, and Pulse Solutions Using PSPICE 14   |

| Examples of DC, Sin, and Pulse Solutions Using SIMetrix 14 |

| Evaluation Board                                           |

|                                                            |

| Outline Dimensions                                         |

| Ordering Guide                                             |

|                                                            |

|                                                            |

| Renumbered Sequentially                                    |

| Changes to Ordering Guide                                  |

| 4/11—Rev. G to Rev. H                                      |

| Changes to Figure 1, Deleted Figure 21                     |

| Added Figure 2, Figure 3, Table 4, Table 55                |

| Deleted Figure 9, Renumbered Subsequent Figures6           |

| Changes to Figure 159                                      |

| 4/10—Rev. F to Rev. G                                      |

| Changes to Equation 16                                     |

| Changes to Equation 5 and Figure 147                       |

| Changes to Figure 219                                      |

| 10/09—Rev. E to Rev. F                                     |

| Changes to Format                                          |

| Changes to Figure 219                                      |

| Updated Outline Dimensions                                 |

| Changes to Ordering Guide                                  |

| 10/02 Pay D to Pay E                                       |

| 10/02—Rev. D to Rev. E                                     |

| Edits to Title of 8-Lead Plastic SOIC Package (RN-8)       |

| Edite to Ordering Childe                                   |

| Edits to Ordering Guide2                                   |

| Edits to Ordering Guide                                    |

## **SPECIFICATIONS**

$T_{A}$  = 25°C,  $V_{S}$  = ±15 V,  $R_{L}$   $\geq$  2  $k\Omega.$

Table 1.

|                                      |                                                 |                                                       | AD633J, AD633A    |                  |              |

|--------------------------------------|-------------------------------------------------|-------------------------------------------------------|-------------------|------------------|--------------|

| Parameter                            | Conditions                                      | Min                                                   | Тур               | Max              | Unit         |

| TRANSFER FUNCTION                    |                                                 | (XI                                                   | (1 - X2)(Y1 - Y2) | -                |              |

|                                      |                                                 | $W = \frac{\langle x x \rangle}{\langle x x \rangle}$ | 10 V              | + <i>Z</i>       |              |

| MULTIPLIER PERFORMANCE               |                                                 |                                                       |                   |                  |              |

| Total Error                          | $-10 \text{ V} \leq X, Y \leq +10 \text{ V}$    |                                                       | ±1                | ±21              | % full scale |

| T <sub>MIN</sub> to T <sub>MAX</sub> |                                                 |                                                       | ±3                |                  | % full scale |

| Scale Voltage Error                  | SF = 10.00 V nominal                            |                                                       | ±0.25%            |                  | % full scale |

| Supply Rejection                     | $V_S = \pm 14  V \text{ to } \pm 16  V$         |                                                       | ±0.01             |                  | % full scale |

| Nonlinearity, X                      | $X = \pm 10 \text{ V}, Y = +10 \text{ V}$       |                                                       | ±0.4              | ±1¹              | % full scale |

| Nonlinearity, Y                      | $Y = \pm 10 \text{ V}, X = +10 \text{ V}$       |                                                       | ±0.1              | ±0.41            | % full scale |

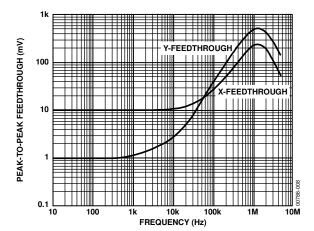

| X Feedthrough                        | Y nulled, $X = \pm 10 V$                        |                                                       | ±0.3              | ±1¹              | % full scale |

| Y Feedthrough                        | X nulled, $Y = \pm 10 \text{ V}$                |                                                       | ±0.1              | ±0.41            | % full scale |

| Output Offset Voltage <sup>2</sup>   |                                                 |                                                       | ±5                | ±50 <sup>1</sup> | mV           |

| DYNAMICS                             |                                                 |                                                       |                   |                  |              |

| Small Signal Bandwidth               | $V_O = 0.1 \text{ V rms}$                       |                                                       | 1                 |                  | MHz          |

| Slew Rate                            | $V_0 = 20 \text{ V p-p}$                        |                                                       | 20                |                  | V/µs         |

| Settling Time to 1%                  | $\Delta V_0 = 20 \text{ V}$                     |                                                       | 2                 |                  | μs           |

| OUTPUT NOISE                         |                                                 |                                                       |                   |                  |              |

| Spectral Density                     |                                                 |                                                       | 0.8               |                  | μV/√Hz       |

| Wideband Noise                       | f = 10 Hz to 5 MHz                              |                                                       | 1                 |                  | mV rms       |

|                                      | f = 10 Hz to 10 kHz                             |                                                       | 90                |                  | μV rms       |

| OUTPUT                               |                                                 |                                                       |                   |                  |              |

| Output Voltage Swing                 |                                                 | ±11 <sup>1</sup>                                      |                   |                  | V            |

| Short Circuit Current                | $R_L = 0 \Omega$                                |                                                       | 30                | 40 <sup>1</sup>  | mA           |

| INPUT AMPLIFIERS                     |                                                 |                                                       |                   |                  |              |

| Signal Voltage Range                 | Differential                                    | ±10 <sup>1</sup>                                      |                   |                  | V            |

|                                      | Common mode                                     | ±10 <sup>1</sup>                                      |                   |                  | V            |

| Offset Voltage (X, Y)                |                                                 |                                                       | ±5                | ±30 <sup>1</sup> | mV           |

| CMRR (X, Y)                          | $V_{CM} = \pm 10 \text{ V, } f = 50 \text{ Hz}$ | 60¹                                                   | 80                |                  | dB           |

| Bias Current (X, Y, Z)               |                                                 |                                                       | 0.8               | 2.01             | μΑ           |

| Differential Resistance              |                                                 |                                                       | 10                |                  | MΩ           |

| POWER SUPPLY                         |                                                 |                                                       |                   |                  |              |

| Supply Voltage                       |                                                 |                                                       |                   |                  |              |

| Rated Performance                    |                                                 |                                                       | ±15               |                  | V            |

| Operating Range                      |                                                 | ±81                                                   |                   | ±18 <sup>1</sup> | V            |

| Supply Current                       | Quiescent                                       |                                                       | 4                 | 6 <sup>1</sup>   | mA           |

<sup>&</sup>lt;sup>1</sup> This specification was tested on all production units at electrical test. Results from those tests are used to calculate outgoing quality levels. All minimum and maximum specifications are guaranteed; however, only this specification was tested on all production units.

<sup>2</sup> Allow approximately 0.5 ms for settling following power on.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| Supply Voltage                       | ±18 V           |

| Internal Power Dissipation           | 500 mW          |

| Input Voltages <sup>1</sup>          | ±18 V           |

| Output Short-Circuit Duration        | Indefinite      |

| Storage Temperature Range            | −65°C to +150°C |

| Operating Temperature Range          |                 |

| AD633J                               | 0°C to 70°C     |

| AD633A                               | −40°C to +85°C  |

| Lead Temperature (Soldering, 60 sec) | 300°C           |

| ESD Rating                           | 1000 V          |

$<sup>^{\</sup>rm 1}$  For supply voltages less than  $\pm 18$  V, the absolute maximum input voltage is equal to the supply voltage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 3.

| Package Type | <b>Ө</b> ЈА | Unit |

|--------------|-------------|------|

| 8-Lead PDIP  | 90          | °C/W |

| 8-Lead SOIC  | 155         | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

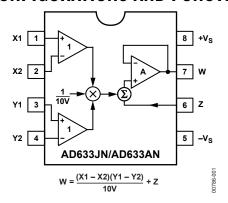

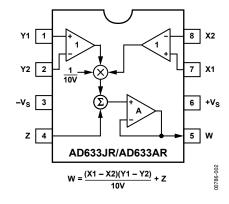

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 2. 8-Lead PDIP

Figure 3. 8-Lead SOIC

**Table 4. 8-Lead PDIP Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                       |

|---------|-----------------|-----------------------------------|

| 1       | X1              | X Multiplicand Noninverting Input |

| 2       | X2              | X Multiplicand Inverting Input    |

| 3       | Y1              | Y Multiplicand Noninverting Input |

| 4       | Y2              | Y Multiplicand Inverting Input    |

| 5       | −V <sub>S</sub> | Negative Supply Rail              |

| 6       | Z               | Summing Input                     |

| 7       | W               | Product Output                    |

| 8       | +V <sub>s</sub> | Positive Supply Rail              |

**Table 5. 8-Lead SOIC Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                       |  |

|---------|-----------------|-----------------------------------|--|

| 1       | Y1              | Y Multiplicand Noninverting Input |  |

| 2       | Y2              | Y Multiplicand Inverting Input    |  |

| 3       | −V <sub>S</sub> | Negative Supply Rail              |  |

| 4       | Z               | Summing Input                     |  |

| 5       | W               | Product Output                    |  |

| 6       | +V <sub>S</sub> | Positive Supply Rail              |  |

| 7       | X1              | X Multiplicand Noninverting Input |  |

| 8       | X2              | X Multiplicand Inverting Input    |  |

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Frequency Response

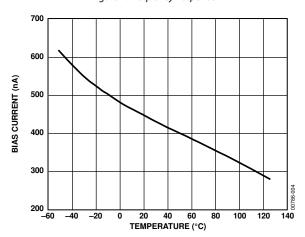

Figure 5. Input Bias Current vs. Temperature (X, Y, or Z Inputs)

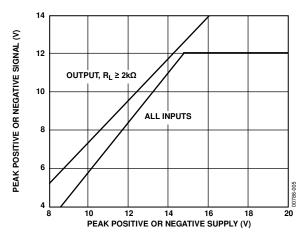

Figure 6. Input and Output Signal Ranges vs. Supply Voltages

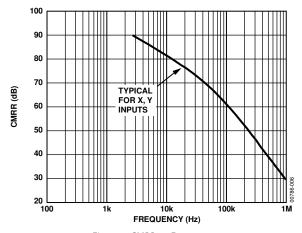

Figure 7. CMRR vs. Frequency

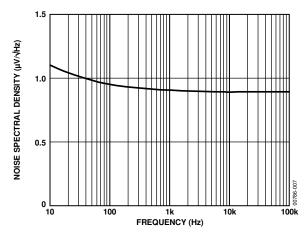

Figure 8. Noise Spectral Density vs. Frequency

Figure 9. AC Feedthrough vs. Frequency

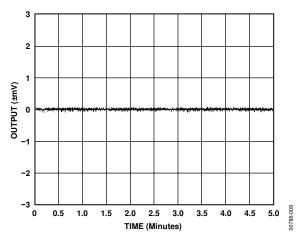

Figure 10. Typical  $V_{\text{OS}}$  vs. Time, For Five Minutes Following Power Up

### **FUNCTIONAL DESCRIPTION**

The AD633 is a low cost multiplier comprising a translinear core, a buried Zener reference, and a unity-gain connected output amplifier with an accessible summing node. Figure 1 shows the functional block diagram. The differential X and Y inputs are converted to differential currents by voltage-to-current converters. The product of these currents is generated by the multiplying core. A buried Zener reference provides an overall scale factor of 10 V. The sum of  $(X \times Y)/10 + Z$  is then applied to the output amplifier. The amplifier summing Node Z allows the user to add two or more multiplier outputs, convert the output voltage to a current, and configure various analog computational functions.

Inspection of the block diagram shows the overall transfer function is

$$W = \frac{(X1 - X2)(Y1 - Y2)}{10 \text{ V}} + Z \tag{1}$$

#### **ERROR SOURCES**

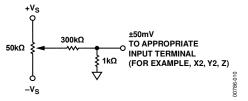

Multiplier errors consist primarily of input and output offsets, scale factor error, and nonlinearity in the multiplying core. The input and output offsets can be eliminated by using the optional trim of Figure 11. This scheme reduces the net error to scale factor errors (gain error) and an irreducible nonlinearity component in the multiplying core. The X and Y nonlinearities are typically 0.4% and 0.1% of full scale, respectively. Scale factor error is typically 0.25% of full scale. The high impedance Z input should always reference the ground point of the driven system, particularly if it is remote. Likewise, the differential X and Y inputs should reference their respective grounds to realize the full accuracy of the AD633.

Figure 11. Optional Offset Trim Configuration

### APPLICATIONS INFORMATION

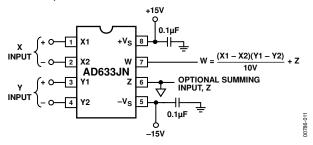

The AD633 is well suited for such applications as modulation and demodulation, automatic gain control, power measurement, voltage-controlled amplifiers, and frequency doublers. These applications show the pin connections for the AD633JN (8-lead PDIP), which differs from the AD633JR (8-lead SOIC).

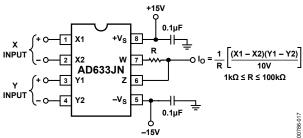

#### **MULTIPLIER CONNECTIONS**

Figure 12 shows the basic connections for multiplication. The X and Y inputs normally have their negative nodes grounded, but they are fully differential, and in many applications, the grounded inputs may be reversed (to facilitate interfacing with signals of a particular polarity while achieving some desired output polarity), or both may be driven.

Figure 12. Basic Multiplier Connections (See the Model Results Section)

#### **SQUARING AND FREQUENCY DOUBLING**

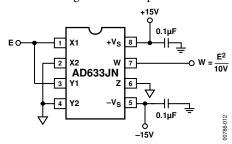

As is shown in Figure 13, squaring of an input signal, E, is achieved simply by connecting the X and Y inputs in parallel to produce an output of  $E^2/10$  V. The input can have either polarity, but the output is positive. However, the output polarity can be reversed by interchanging the X or Y inputs. The Z input can be used to add a further signal to the output.

Figure 13. Connections for Squaring

When the input is a sine wave E sin  $\omega t$ , this squarer behaves as a frequency doubler, because

$$\frac{\left(E\sin\omega t\right)^2}{10\text{ V}} = \frac{E^2}{20\text{ V}}\left(1-\cos 2\omega t\right) \tag{2}$$

Equation 2 shows a dc term at the output that varies strongly with the amplitude of the input, E. This can be avoided using the connections shown in Figure 14, where an RC network is used to generate two signals whose product has no dc term. It uses the identity

$$\cos\theta\sin\theta = \frac{1}{2}(\sin 2\theta) \tag{3}$$

Figure 14. Bounceless Frequency Doubler (See the Model Results Section)

At  $\omega_o = 1/CR$ , the X input leads the input signal by 45° (and is attenuated by  $\sqrt{2}$ ), and the Y input lags the X input by 45° (and is also attenuated by  $\sqrt{2}$ ). Because the X and Y inputs are 90° out of phase, the response of the circuit is (satisfying Equation 3)

$$W = \frac{1}{(10 \text{ V})} \frac{E}{\sqrt{2}} \left( \sin \omega_0 t + 45^\circ \right) \frac{E}{\sqrt{2}} \left( \sin \omega_0 t + 45^\circ \right)$$

$$= \frac{E^2}{(40 \text{ V})} \left( \sin 2 \omega_0 t \right) \tag{4}$$

which has no dc component. Resistor R1 and Resistor R2 are included to restore the output amplitude to  $10~\rm V$  for an input amplitude of  $10~\rm V$ .

The amplitude of the output is only a weak function of frequency; the output amplitude is 0.5% too low at  $\omega=0.9~\omega_0$  and  $\omega_0=1.1~\omega_0$ .

#### **GENERATING INVERSE FUNCTIONS**

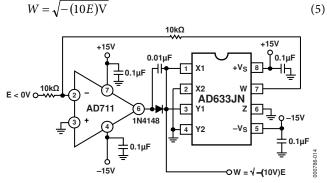

Inverse functions of multiplication, such as division and square rooting, can be implemented by placing a multiplier in the feedback loop of an op amp. Figure 15 shows how to implement square rooting with the transfer function for the condition  $\rm E < 0$ .

The 1N4148 diode is required to prevent latchup, which can occur in such applications if the input were to change polarity, even momentarily.

Figure 15. Connections for Square Rooting

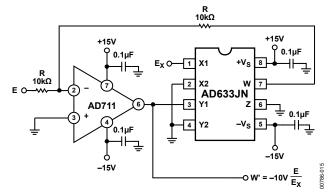

Likewise, Figure 16 shows how to implement a divider using a multiplier in a feedback loop. The transfer function for the divider is

$$W = -\left(10 \text{ V}\right) \frac{E}{E_{\text{V}}} \tag{6}$$

Figure 16. Connections for Division

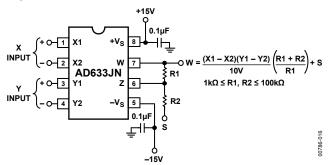

#### **VARIABLE SCALE FACTOR**

In some instances, it may be desirable to use a scaling voltage other than 10 V. The connections shown in Figure 17 increase the gain of the system by the ratio (R1+R2)/R1. This ratio is limited to 100 in practical applications. The summing input, S, can be used to add an additional signal to the output, or it can be grounded.

Figure 17. Connections for Variable Scale Factor

#### **CURRENT OUTPUT**

The voltage output of the AD633 can be converted to a current output by the addition of a resistor, R, between the W and Z pins of the AD633 as shown in Figure 18.

Figure 18. Current Output Connections

This arrangement forms the basis of voltage-controlled integrators and oscillators as is shown later in this section. The transfer function of this circuit has the form

$$I_O = \frac{1}{R} \frac{(XI - X2)(YI - Y2)}{10 \text{ V}} \tag{7}$$

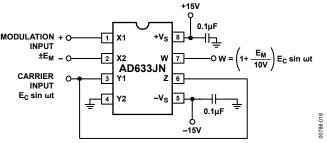

#### LINEAR AMPLITUDE MODULATOR

The AD633 can be used as a linear amplitude modulator with no external components. Figure 19 shows the circuit. The carrier and modulation inputs to the AD633 are multiplied to produce a double sideband signal. The carrier signal is fed forward to the Z input of the AD633 where it is summed with the double sideband signal to produce a double sideband with the carrier output.

Figure 19. Linear Amplitude Modulator

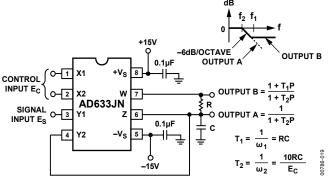

#### VOLTAGE-CONTROLLED, LOW-PASS AND HIGH-PASS FILTERS

Figure 20 shows a single multiplier used to build a voltage-controlled, low-pass filter. The voltage at Output A is a result of filtering E<sub>s</sub>. The break frequency is modulated by E<sub>C</sub>, the control input. The break frequency, f<sub>2</sub>, equals

$$f_2 = \frac{E_C}{10(2\pi RC)}$$

(8)

and the roll-off is 6 dB per octave. This output, which is at a high impedance point, may need to be buffered.

Figure 20. Voltage-Controlled, Low-Pass Filter

The voltage at Output B, the direct output of the AD633, has the same response up to frequency  $f_1$ , the natural breakpoint of RC filter, and then levels off to a constant attenuation of  $f_1/f_2 = 10/E_C$

$$f_1 = \frac{1}{2 \pi RC} \tag{9}$$

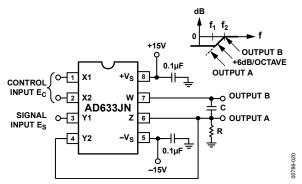

For example, if  $R=8~k\Omega$  and  $C=0.002~\mu\text{F}$ , then Output A has a pole at frequencies from 100 Hz to 10 kHz for  $E_C$  ranging from 100 mV to 10 V. Output B has an additional 0 at 10 kHz (and can be loaded because it is the low impedance output of the multiplier). The circuit can be changed to a high-pass filter Z interchanging the resistor and capacitor as shown in Figure 21.

Figure 21. Voltage-Controlled, High-Pass Filter

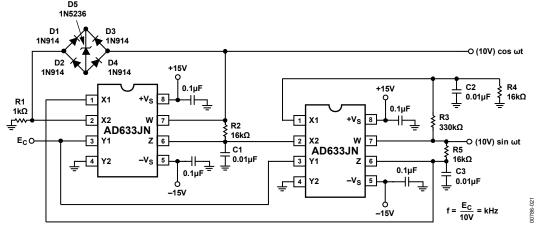

#### **VOLTAGE-CONTROLLED QUADRATURE OSCILLATOR**

Figure 22 shows two multipliers being used to form integrators with controllable time constants in second-order differential equation feedback loop. R2 and R5 provide controlled current output operation. The currents are integrated in capacitors C1 and C2, and the resulting voltages at high impedance are applied to the X inputs of the next AD633. The frequency control input, Ec,

connected to the Y inputs, varies the integrator gains with a calibration of 100 Hz/V. The accuracy is limited by the Y input offsets. The practical tuning range of this circuit is 100:1. C2 (proportional to C1 and C3), R3, and R4 provide regenerative feedback to start and maintain oscillation. The diode bridge, D1 through D4 (1N914s), and Zener diode D5 provide economical temperature stabilization and amplitude stabilization at ±8.5 V by degenerative damping. The output from the second integrator (10 V sin  $\omega$ t) has the lowest distortion.

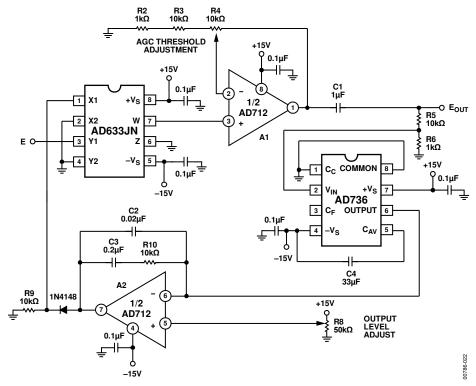

#### **AUTOMATIC GAIN CONTROL (AGC) AMPLIFIERS**

Figure 23 shows an AGC circuit that uses an rms-to-dc converter to measure the amplitude of the output waveform. The AD633 and A1, half of an AD712 dual op amp, form a voltage-controlled amplifier. The rms-to-dc converter, an AD736, measures the rms value of the output signal. Its output drives A2, an integrator/comparator whose output controls the gain of the voltage-controlled amplifier. The 1N4148 diode prevents the output of A2 from going negative. R8, a 50 k $\Omega$  variable resistor, sets the output level of the circuit. Feedback around the loop forces the voltages at the inverting and noninverting inputs of A2 to be equal, thus the AGC.

Figure 22. Voltage-Controlled Quadrature Oscillator

Figure 23. Connections for Use in Automatic Gain Control Circuit

### **MODEL RESULTS**

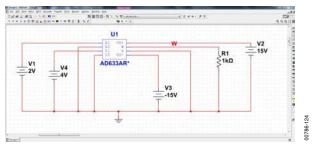

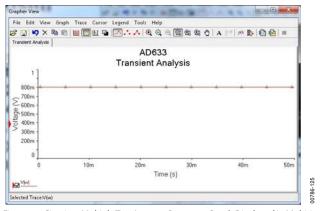

Circuit simulation using SPICE models embedded in various application formats such as PSPICE, Multisim, and SIMetrix is a popular and efficient method of assessing the integrity of a circuit before creating the printed circuit board in which the circuits are ultimately used. Although impossible to demonstrate all of the multiplier functions in every available program, Figure 24 through Figure 41 demonstrate how the schematic and graph for simple dc, sin(x), and pulse applications appear in three popular SPICE programs. If a simulator is not shown here, a good way to progress is to start with a basic dc circuit to verify that the circuit converges and then continue with waveforms that are more complex. When analyzing nonlinear devices such as multipliers, the most common simulation issue is convergence, the iterative process by which SPICE seeks the initial dc bias condition before completely solving the circuit and displaying a graph.

Figure 24 through Figure 41 are arranged schematic first, followed by the graphic result. If the user has a problem with a simulator, the most efficient fix is to contact applications support for the program in use.

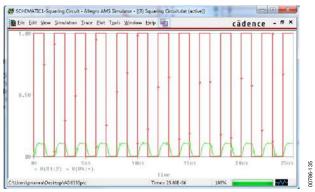

# **EXAMPLES OF DC, SIN, AND PULSE SOLUTIONS USING MULTISIM**

Figure 24. Circuit to Multiply Two Integers Schematic Created in Multisim

Figure 25. Circuit to Multiply Two Integers Response Graph Displayed in Multisim  $(2 V \times 4 V)/10 V = 0.8 V$

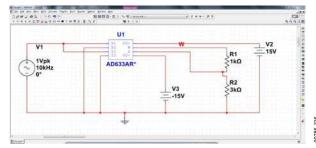

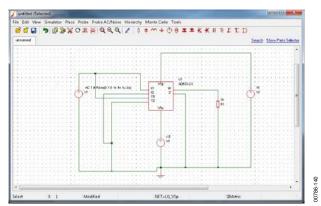

Figure 26. Frequency Doubler Circuit Schematic Created in Multisim

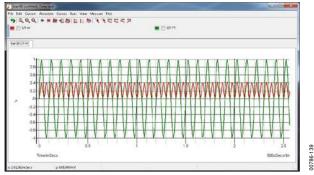

Figure 27. Frequency Doubler Response Graph Displayed in Multisim

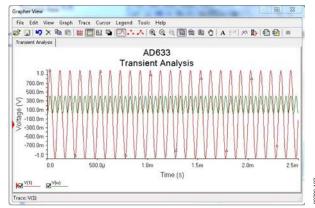

Figure 28. Pulse Circuit Schematic Created in Multisim

Figure 29. Pulse Circuit Response Graph Displayed in Multisim

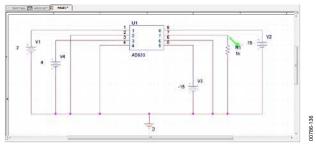

# EXAMPLES OF DC, SIN, AND PULSE SOLUTIONS USING PSPICE

Figure 30. Simple Circuit Schematic Created in PSPICE

Figure 31. Simple Circuit Response Graph Displayed in PSPICE  $(2 V \times 4 V)/10 V = 0.8 V$

Figure 32. Frequency Doubler Circuit Schematic Created in PSPICE

Figure 33. Frequency Doubler Response Graph Displayed in PSPICE

Figure 34. Pulse Circuit Schematic Created in PSPICE

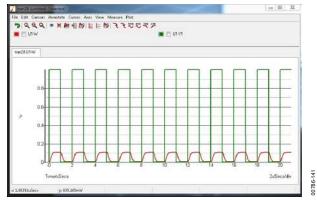

Figure 35. Pulse Circuit Response Graph Displayed in PSPICE

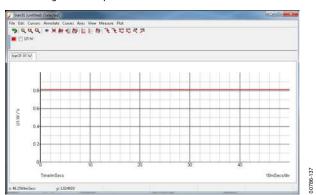

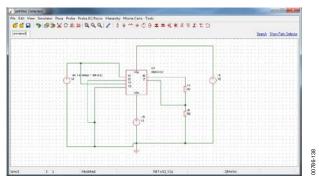

# EXAMPLES OF DC, SIN, AND PULSE SOLUTIONS USING SIMETRIX

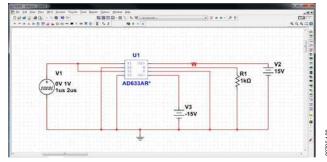

Figure 36. Simple Circuit Schematic Created in SIMetrix

Figure 37.Simple Circuit Response Graph Displayed in SIMetrix  $(2 \text{ V} \times 4 \text{ V})/10 \text{ V} = 0.8 \text{ V}$

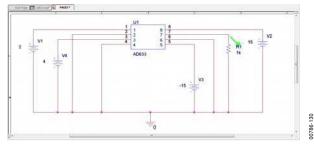

Figure 38. Frequency Doubler Circuit Schematic Created in SIMetrix

Figure 39. Frequency Doubler Response Graph Displayed in SIMetrix

Figure 40. Pulse Circuit Schematic Created in SIMetrix

Figure 41. Pulse Circuit Response Displayed in SIMetrix

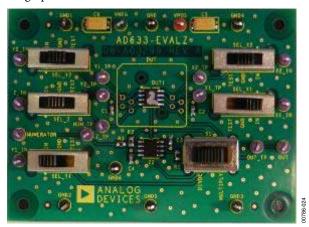

### **EVALUATION BOARD**

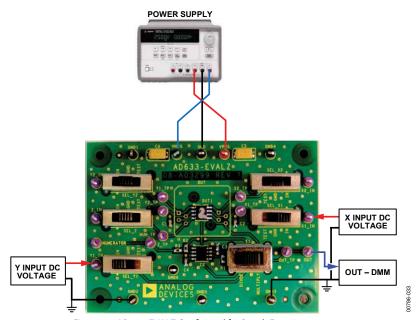

The evaluation board of the AD633 enables simple bench-top experimenting to be performed with easy control of the AD633. Built-in flexibility allows convenient configuration to accommodate most operating configurations. Figure 42 is a photograph of the AD633 evaluation board.

Figure 42. AD633 Evaluation Board

Any dual-polarity power supply capable of providing 10 mA or greater is all that is required to perform the intended tests, in addition to whatever test equipment the user wants.

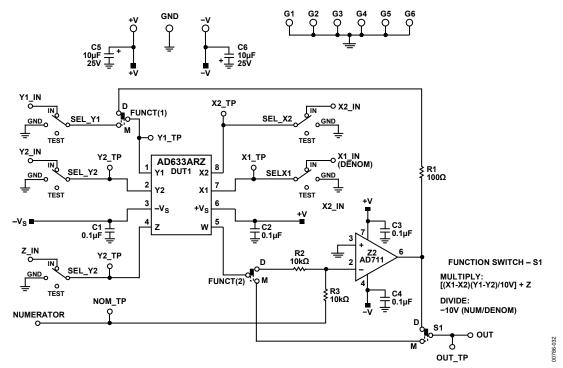

Referring to the schematic in Figure 49, inputs to the multiplier are differential and dc-coupled. Three-position slide switches enhance flexibility by enabling the multiplier inputs to be connected to an active signal source, to ground, or to a test loop connected directly to the device pin for direct measurements, such as bias current. Inputs may be connected single ended or differentially, but must have a dc path to ground for bias current. If the impedance of an input source is non-zero, an equal value impedance must be connected to the opposite polarity input to avoid introducing additional offset voltage.

The AD633-EVALZ can be configured for multiplier or divider operation by switch S1. Refer to Figure 16 for divider circuit connections.

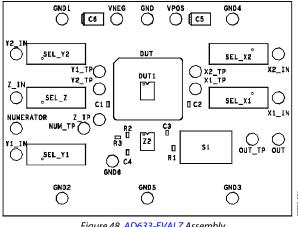

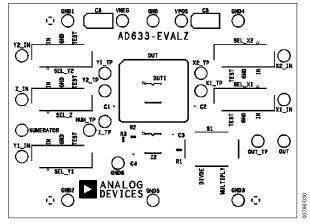

Figure 43 through Figure 46 are the signal, power, and groundplane artworks, and Figure 47 shows the component and circuit side silkscreen. Figure 48 shows the assembly.

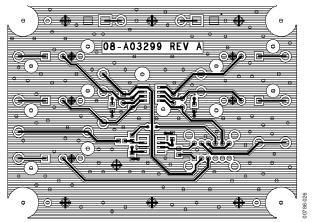

Figure 43. Component Side Copper

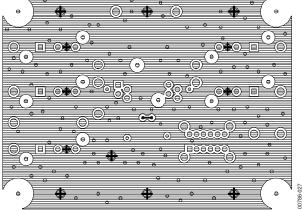

Figure 44. Circuit Side Copper

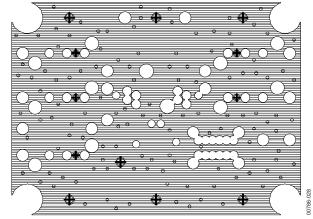

Figure 45. Inner Layer Ground Plane

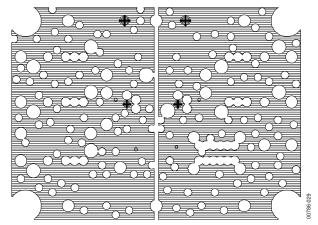

Figure 46. Inner Layer Power Plane

Figure 48. AD633-EVALZ Assembly

Figure 47. Component Side Silk Screen

Figure 49. Schematic of the AD633 Evaluation Board

Figure 50. AD633-EVALZ Configured for Bench Experiments

## **OUTLINE DIMENSIONS**

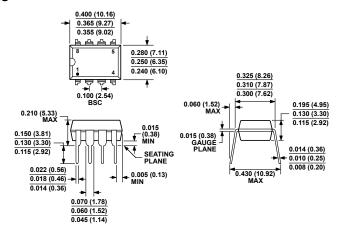

COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 51. 8-Lead Plastic Dual-in-Line Package [PDIP] (N-8)

Dimensions shown in inches and (millimeters)

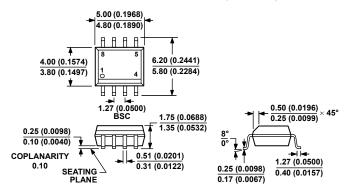

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 52. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                               | Package Option |

|--------------------|-------------------|-------------------------------------------------------------------|----------------|

| AD633ANZ           | −40°C to +85°C    | 8-Lead Plastic Dual-in-Line Package [PDIP]                        | N-8            |

| AD633ARZ           | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]                    | R-8            |

| AD633ARZ-R7        | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N], 7" Tape and Reel  | R-8            |

| AD633ARZ-RL        | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N], 13" Tape and Reel | R-8            |

| AD633JN            | 0°C to 70°C       | 8-Lead Plastic Dual-in-Line Package [PDIP]                        | N-8            |

| AD633JNZ           | 0°C to 70°C       | 8-Lead Plastic Dual-in-Line Package [PDIP]                        | N-8            |

| AD633JR            | 0°C to 70°C       | 8-Lead Standard Small Outline Package [SOIC_N]                    | R-8            |

| AD633JR-REEL       | 0°C to 70°C       | 8-Lead Standard Small Outline Package [SOIC_N], 13" Tape and Reel | R-8            |

| AD633JR-REEL7      | 0°C to 70°C       | 8-Lead Standard Small Outline Package [SOIC_N], 7" Tape and Reel  | R-8            |

| AD633JRZ           | 0°C to 70°C       | 8-Lead Standard Small Outline Package [SOIC_N]                    | R-8            |

| AD633JRZ-R7        | 0°C to 70°C       | 8-Lead Standard Small Outline Package [SOIC_N], 7" Tape and Reel  | R-8            |

| AD633JRZ-RL        | 0°C to 70°C       | 8-Lead Standard Small Outline Package [SOIC_N], 13" Tape and Reel | R-8            |

| AD633-EVALZ        |                   | Evaluation Board                                                  |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.