May 2011

# FXLP4555 1.8V / 3.0V SIM Card Power Supply and Level Shifter

#### **Features**

- Supports 1.8V or 3.0V SIM Cards

- LDO Supplies >50mA Under 1.8V and 3.0V

- Built-in Pull-up Resistor for I/O Pin in Both Directions

- ESD Protection: 8kV (Human Body Model, According to ISO-7816 Specifications)

- Supports Clock ≥ 5MHz

- Supports "Clock Stop" Power Management per ISO7816-3 Specifications

- Low-Profile 3x3mm MLP-16 Package

## **Applications**

- SIM Card Interface Circuit for 2G, 2.5G, and 3G Mobile Phones

- Identification Module

- Smart Card Readers

- Wireless PC Cards

### **Description**

The FXLP4555 is a level-shifter analog circuit designed to translate the voltages between a SIM card and an external baseband. A built-in LDO-type DC-DC converter allows the FXLP4555 to drive 1.8V and 3.0V SIM cards. The device fulfills the ISO7816-3 smart-card interface standard as well as GSM 11.11 (11.12 and 11.18) and 3G mobile requirements (IMT-2000/3G UICC standard). The EN pin enables a low-current Shutdown Mode that extends battery life. The card power supply voltage (VCC C) is selected using a single pin (VSEL).

## **Ordering Information**

| Part Number | Operating<br>Temperature Range | Top<br>Mark | Package                                     | Packing Method               |  |

|-------------|--------------------------------|-------------|---------------------------------------------|------------------------------|--|

| FXLP4555MPX | (LP4555MPX -40 to +85°C        |             | 16-Lead,MLP,Quad,JEDEC<br>MO-220,3MM Square | 3000 Units<br>on Tape & Reel |  |

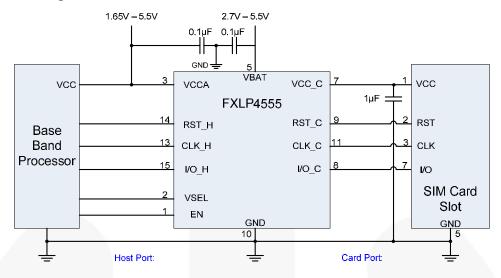

## **Application Diagram**

Figure 1. Typical Application

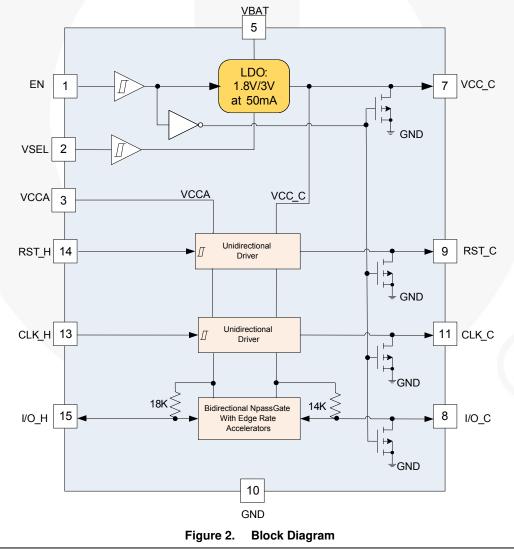

## **Functional Block Diagram**

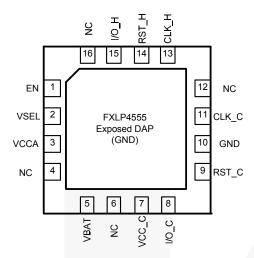

## **Pin Configuration**

Figure 3. Pin Assignments (Top View)

## **Pin Definitions**

| Pin | Name  | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | EN    | INPUT            | Power-Down Mode. EN=LOW $\rightarrow$ low-current Shutdown Mode activated. EN=HIGH $\rightarrow$ normal operation. A LOW level on this pin resets the SIM interface, switching off the $V_{CC\_C}$ .                                                                                                                                                                                                                       |  |  |  |

| 2   | VSEL  | INPUT            | The signal present on this pin programs the SIM_V <sub>CC</sub> value: VSEL=LOW $\rightarrow$ SIM_V <sub>CC</sub> =1.8V; VSEL=HIGH $\rightarrow$ SIM_V <sub>CC</sub> =3V.                                                                                                                                                                                                                                                  |  |  |  |

| 3   | VCCA  | POWER            | Connected to the baseband power supply; this pin configures the level shifter input stage to accept signals from the baseband. A 0.1 $\mu$ F capacitor is used to bypass the power supply voltage. When V <sub>CCA</sub> is below 1.1V (typical), the V <sub>CC_C</sub> (SIM Card V <sub>CC</sub> ) is disabled and FXLP4555 enters Shutdown Mode.                                                                         |  |  |  |

| 4   | NC    |                  | No connect. It is recommended to solder to PCB GND.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 5   | VBAT  | POWER            | LDO converter supply input. The input voltage ranges from 2.7V to 5.5V. This pin needs to be bypassed by a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                |  |  |  |

| 6   | NC    |                  | No connect. It is recommended to solder to PCB GND.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 7   | VCC_C | POWER            | Connected to the SIM card power supply pin. An internal LDO converter is programmable by the external baseband to supply either 1.8V or 3.0V output voltage. An external 1.0 $\mu$ F minimum ceramic capacitor must be connected across V <sub>CC_C</sub> and GND. During a normal operation, the V <sub>CC_C</sub> voltage can be set to 1.8V, followed by a 3.0V value, or can start directly at either of these values. |  |  |  |

| 8   | I/O_C | INPUT/<br>OUTPUT | Handles the connection to the serial I/O of the card connector. A bi-directional level translator adapts the serial I/O signal between the card and the baseband. A $14k\Omega$ (typical) pull-up resistor provides a high-impedance state for the SIM card I/O link.                                                                                                                                                      |  |  |  |

| 9   | RST_C | OUTPUT           | Connected to the RESET pin of the card connector. A level translator adapts the external reset (RST) signal to the SIM card.                                                                                                                                                                                                                                                                                               |  |  |  |

| 10  | GND   | GROUND           | Ground reference for the integrated circuit and associated signals. Care must be taken to avoid voltage spikes when the device operates in normal operation.                                                                                                                                                                                                                                                               |  |  |  |

| 11  | CLK_C | OUTPUT           | Connected to the CLOCK pin of the card connector. The CLOCK (CLK) signal comes from the external clock generator; the internal level shifter adapts the voltage defined for the $V_{\text{CC\_C}}$ .                                                                                                                                                                                                                       |  |  |  |

| 12  | NC    |                  | No connect. It is recommended to solder to PCB GND.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 13  | CLK_H | INPUT            | The clock signal, coming from the external controller, must have a duty cycle within the range defined by the specification (typically 50%). The built-in level shifter translates the input signal to the external SIM card CLK input.                                                                                                                                                                                    |  |  |  |

## Pin Definitions (Continued)

| Pin | Name        | Туре             | Description                                                                                                                                                                                                                                          |

|-----|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | RST_H       | INPUT            | The RESET signal present at this pin is connected to the SIM card through the internal level shifter, which translates the level according to the $V_{\text{CC\_C}}$ programmed value.                                                               |

| 15  | I/O_H       | INPUT/<br>OUTPUT | This pin is connected to the baseband. A bidirectional level translator adapts the serial I/O signal between the smart card and the baseband. A built-in constant $18k\Omega$ (typical) resistor provides a high-impedance state when not activated. |

| 16  | NC          |                  | No connect. It is recommended to solder to pcb GND.                                                                                                                                                                                                  |

| 17  | Exposed DAP | Ground           | Must be soldered to PCB ground plane.                                                                                                                                                                                                                |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A = +25$ °C.

| Symbol               | Parameter                                                                                                  |                                            | Min.                                             | Тур. | Max.              | Unit                               |       |

|----------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------|------|-------------------|------------------------------------|-------|

| $V_{BAT}$            | LDO Power S                                                                                                | Supply Voltage                             |                                                  | -0.5 | $V_{BAT}$         | 6.0                                | V     |

| $V_{CCA}$            | Power Supply                                                                                               | from Baseband                              | Side                                             | -0.5 | $V_{CCA}$         | 6.0                                | V     |

| V <sub>CC_C</sub>    | External Card Power Supply                                                                                 |                                            |                                                  | -0.5 | V <sub>CC_C</sub> | 6.0                                | V     |

| V <sub>IN</sub>      | Digital Input F                                                                                            | Digital Input Pin Voltage                  |                                                  |      | V <sub>IN</sub>   | V <sub>CCA</sub> +0.5,<br>but <6.0 | V     |

| I <sub>IN</sub>      | Digital Input F                                                                                            | Pin Current                                |                                                  | -5   |                   | +5                                 | mA    |

| V <sub>OUT</sub>     | Digital Output                                                                                             | : Pin Voltage                              |                                                  | -0.5 | V <sub>OUT</sub>  | V <sub>CCA</sub> +0.5,<br>but <6.0 | V     |

| I <sub>OUT</sub>     | Digital Output                                                                                             | Pin Current                                |                                                  | -10  | -                 | +10                                | mA    |

| V <sub>OUT_SIM</sub> | SIM Card Out                                                                                               | tput Pin Voltage                           |                                                  | -0.5 | V <sub>OUT</sub>  | SIM_V <sub>CC</sub> +<br>0.5<6.0   | V     |

| I <sub>OUT_SIM</sub> | SIM Card Out                                                                                               | SIM Card Output Pin Current <sup>(1)</sup> |                                                  |      |                   | 15                                 | mA    |

| $P_D$                | Power Dissipation at T <sub>A</sub> =+85°C                                                                 |                                            |                                                  |      |                   | 440                                | mW    |

| $\Theta_{JA}$        | Thermal Resistance, Junction-to-Air                                                                        |                                            |                                                  |      |                   | 72                                 | °C/W  |

| T <sub>A</sub>       | Operating Ambient Temperature Range                                                                        |                                            |                                                  | -40  |                   | +85                                | °C    |

| $T_J$                | Operating Jur                                                                                              | Operating Junction Temperature Range       |                                                  |      |                   | +125                               | °C    |

| $T_{JMAX}$           | Maximum Jur                                                                                                | nction Temperatu                           | re                                               |      |                   | +125                               | °C    |

| $T_{STG}$            | Storage Temp                                                                                               | perature Range                             |                                                  | -65  |                   | +150                               | °C    |

|                      |                                                                                                            | Human Body                                 | SIM Card Pins<br>(7,8,9,10,11)                   |      | 8000              |                                    |       |

| ESD                  | Model, JESD22-A114 Electrostatic Discharge Capability  Model, JESD22-A114 R=1500Ω, C=100pF  All Other Pins |                                            |                                                  | 2000 |                   | V                                  |       |

|                      |                                                                                                            | Charged<br>Device Model,                   | SIM Card Pins<br>(7,8,9,10,11)<br>All Other Pins |      | 2000              |                                    |       |

|                      |                                                                                                            | JESD22-C101                                | 600                                              |      |                   |                                    |       |

|                      | Moisture Sens                                                                                              | sitivity Level                             |                                                  |      | 1                 | V.                                 | Level |

#### Notes:

- 1. Internally limited.

- 2. Meets or exceeds JEDEC specification EIA/JESD78 IC latchup test.

### **Electrical Characteristics**

$T_A$ =-40°C to +85°C. Device meets the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

| Symbol                            | Parameter                        | Condition                                                                                                                     | Min.                      | Тур. | Max.                      | Unit   |

|-----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|---------------------------|--------|

| Power Supp                        | ly Section                       |                                                                                                                               | 1                         | •    |                           | U.     |

| $V_{BAT}$                         | Power Supply                     |                                                                                                                               | 2.7                       |      | 5.5                       | V      |

| I V <sub>BAT</sub>                | Operating Current                | $I_{CC}$ =0mA, $V_{BAT}$ > 3.0V if $V_{SEL}$ =1 or $V_{BAT}$ > 2.7V if $V_{SEL}$ =0                                           |                           | 16   | 25                        | μΑ     |

| I V <sub>BAT_SD</sub>             | Shutdown Current                 | EN=Low                                                                                                                        |                           |      | 3                         | μΑ     |

| $V_{CCA}$                         | Operating Voltage                |                                                                                                                               | 1.65                      |      | 5.50                      | V      |

| I <sub>VCCA</sub>                 | Operating Current <sup>(3)</sup> | fCLK=1MHz                                                                                                                     |                           | 7    | 12                        | μΑ     |

| IV <sub>CCA_SD</sub>              | Shutdown Current                 | EN=Low                                                                                                                        |                           |      | 1                         | μΑ     |

| $V_{CCA}$                         | Under-Voltage<br>Lockout         |                                                                                                                               | 0.6                       |      | 1.5                       | V      |

|                                   |                                  | V <sub>SEL</sub> =High, V <sub>BAT</sub> =3.0V, IV <sub>CC_C</sub> =50mA                                                      |                           | 2.8  |                           |        |

| V <sub>CC_C</sub>                 | SIM Card Supply<br>Voltage       | $\begin{aligned} &V_{SEL}\text{=High, } V_{BAT}\text{=}3.3V-5.5V, \\ &IV_{CC\_C}\text{=}0\text{mA}-50\text{mA} \end{aligned}$ | 2.8                       | 3.0  | 3.2                       | V      |

|                                   |                                  | VSEL=Low, $V_{BAT}$ =2.7V - 5.5V, 1.7 1.8 1.9 1.9                                                                             | 1.9                       |      |                           |        |

| lvcc_c_sc                         | Short-Circuit Current            | V <sub>CC_C</sub> Shorted to Ground, T <sub>A</sub> =25°C                                                                     |                           |      | 175                       | mA     |

| D <b>igital Input</b>             | / Output Section (CLK,           | RST, I/O, EN, VSEL)                                                                                                           |                           |      |                           |        |

| V <sub>IN</sub>                   | Input Voltage Range              | EN, VSEL, RST_H, CLK_H, I/O_H                                                                                                 | 0                         |      | V <sub>CCA</sub>          | V      |

| I <sub>IH</sub> , I <sub>IL</sub> | Input Current                    | EN, VSEL, RST_H, CLK_H                                                                                                        | -100                      |      | 100                       | nA     |

| V <sub>IH</sub>                   | High Level Input<br>Voltage      | RST_H, CLK_H, EN, VSEL                                                                                                        | 0.7 •<br>V <sub>CCA</sub> |      | $V_{CCA}$                 | V      |

| V <sub>IL</sub>                   | Low Level Input                  | RST_H, CLK_H                                                                                                                  |                           |      | 0.2 *<br>V <sub>CCA</sub> | V      |

|                                   | Voltage                          | EN, VSEL                                                                                                                      | 0                         |      | 0.4                       | ·<br>I |

| V <sub>OH_I/O</sub>               | High Level Output<br>Voltage     | I/O_C=V <sub>CC_C</sub> , I <sub>OH_I/O</sub> =-20μA                                                                          | 0.7 •<br>V <sub>CCA</sub> |      | V <sub>CCA</sub>          | V      |

| V <sub>OL_I/O</sub>               | Low Level Output<br>Voltage      | I/O_C=0 V, I <sub>OL_I/O</sub> =200μA                                                                                         | 0                         |      | 0.4                       | V      |

| I <sub>IH</sub>                   | High Level Input<br>Current      | I/O                                                                                                                           | -20                       |      | 20                        | μΑ     |

| I <sub>IL</sub>                   | Low Level Input<br>Current       | 1/0                                                                                                                           |                           |      | 1.0                       | mA     |

| R <sub>pu_I/O_H</sub>             | I/O Pull-Up Resistor             |                                                                                                                               | 12                        | 18   | 24                        | kΩ     |

Continued on the following page...

## **Electrical Characteristics** (Continued)

| Symbol        | Parameter                                            | Condition                                                                                                                                     | Min.                       | Тур. | Max.              | Unit     |

|---------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|-------------------|----------|

| SIM Interface | Section <sup>(4)</sup>                               |                                                                                                                                               |                            | •    | 1                 |          |

|               |                                                      | Output RST_C V <sub>OH</sub> at I <sub>RST_C</sub> =-20μA                                                                                     | 0.9 •<br>V <sub>CC_C</sub> |      | V <sub>CC_C</sub> | V        |

|               | V -12.0V                                             | Output RST_C V <sub>OL</sub> at I <sub>RST_C</sub> =+200μA                                                                                    | 0                          |      | 0.4               | V        |

|               | V <sub>CC_C</sub> =+3.0V<br>(V <sub>SEL</sub> =HIGH) | Output RST_C Rise Time at C <sub>OUT</sub> =30pF (10% - 90%) <sup>(3)</sup>                                                                   |                            |      | 1                 | μs       |

| DST C         |                                                      | Output RST_C Fall Time at C <sub>OUT</sub> =30pF (90% - 10%) <sup>(3)</sup>                                                                   | 1                          |      | 1                 | μs       |

| RST_C         |                                                      | Output RST_C V <sub>OH</sub> at I <sub>RST_C</sub> =-20μA 0.9 • V <sub>CC_C</sub>                                                             |                            |      | V <sub>CC_C</sub> | <b>V</b> |

|               | V <sub>CC C</sub> =+1.8V                             | Output RST_C $V_{OL}$ at $I_{RST\_C}$ =+200 $\mu$ A                                                                                           | 0                          |      | 0.4               | V        |

|               | (V <sub>SEL</sub> =LOW)                              | Output RST_C Rise Time at C <sub>OUT</sub> =30pF (10% - 90%) <sup>(3)</sup>                                                                   |                            | 1    | μs                |          |

|               |                                                      | Output RST_C Fall Time at C <sub>OUT</sub> =30pF (90% - 10%) <sup>(3)</sup>                                                                   |                            |      | 1                 | μs       |

|               |                                                      | Output Duty Cycle                                                                                                                             | 40                         |      | 60                | %        |

|               |                                                      | Maximum Output Frequency                                                                                                                      | 5                          | 1    |                   | MHz      |

|               | V =13.0V                                             | Output V <sub>OH</sub> at I <sub>CLK_C</sub> =-20μA                                                                                           | 0.9 •<br>V <sub>CC_C</sub> |      | Vcc_c             | V        |

|               | (V <sub>SEL</sub> =HIGH)                             | $C_{CC}$ =+3.0V Output V <sub>OL</sub> at I <sub>CLK_C</sub> =+200μA 0 Output CLK_C Rise Time at C <sub>OUT</sub> =30pF $(10\% - 90\%)^{(3)}$ | 0                          |      | 0.4               | V        |

|               |                                                      |                                                                                                                                               |                            | 18   | ns                |          |

| CLK C         |                                                      | Output CLK_C Fall Time at C <sub>OUT</sub> =30pF (90% - 10%) <sup>(3)</sup>                                                                   | 1                          | 18   | ns                |          |

| CLK_C         |                                                      | Output Duty Cycle                                                                                                                             | 40                         |      | 60                | %        |

|               |                                                      | Maximum Output Frequency                                                                                                                      | 5                          |      |                   | MHz      |

|               | V =14.0V                                             | Output V <sub>OH</sub> at I <sub>CLK_C</sub> =-20μA                                                                                           | 0.9 •<br>V <sub>CC_C</sub> |      | V <sub>CC_C</sub> | V        |

|               | V <sub>CC_C</sub> =+1.8V<br>(V <sub>SEL</sub> =LOW)  | Output V <sub>OL</sub> at I <sub>CLK_C</sub> =+200μA                                                                                          | 0                          |      | 0.4               | V        |

|               | ,                                                    | Output CLK _C Rise Time at C <sub>OUT</sub> =30pF (10% - 90%) <sup>(3)</sup>                                                                  |                            |      | 18                | Ns       |

|               |                                                      | Output CLK_C Fall Time at COUT=30pF (90% - 10%) <sup>(3)</sup>                                                                                |                            |      | 18                | ns       |

Continued on the following page...

### **Electrical Characteristics** (Continued)

| Symbol                | Parameter                                            | Condition                                                                              | Min.                       | Тур. | Max.              | Unit |

|-----------------------|------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------|------|-------------------|------|

|                       |                                                      | Output V <sub>OH</sub> at I <sub>I/O_C</sub> =-20µA, V <sub>I/O</sub> =V <sub>DD</sub> | 0.8 •<br>V <sub>CC_C</sub> |      | V <sub>CC_C</sub> | V    |

|                       | \/ =+3 0\/                                           | Output V <sub>OL</sub> at I <sub>I/O_C</sub> =+1mA, V <sub>I/O</sub> =0V               | 0                          |      | 0.4               | V    |

|                       | V <sub>CC_C</sub> =+3.0V<br>(V <sub>SEL</sub> =HIGH) | I/O_C Rise Time at C <sub>OUT</sub> =30pF (10% - 90%) <sup>(3)</sup>                   |                            |      | 1                 | μs   |

| 1/0.0                 |                                                      | I/O_C Fall Time at C <sub>OUT</sub> =30pF (90% - 10%) <sup>(3)</sup>                   |                            |      | 1                 | μs   |

| I/O_C                 | V <sub>CC_C</sub> =+1.8V<br>(V <sub>SEL</sub> =LOW)  | Output V <sub>OH</sub> at I <sub>I/O_C</sub> =-20µA, V <sub>I/O</sub> =V <sub>DD</sub> | 0.8 •<br>V <sub>CC_C</sub> |      | V <sub>CC_C</sub> | V    |

|                       |                                                      | Output V <sub>OL</sub> at I <sub>I/O_C</sub> =+1mA, V <sub>I/O</sub> =0V               | 0                          |      | 0.3               | V    |

|                       |                                                      | I/O_C Rise Time at C <sub>OUT</sub> =30Pf (10% - 90%) <sup>(3)</sup>                   |                            |      | 1                 | μs   |

|                       |                                                      | I/O_C Fall Time at C <sub>OUT</sub> =30pF (90% - 10%) <sup>(3)</sup>                   |                            |      | 1                 | μs   |

| R <sub>pu_I/O_C</sub> | Card I/O Pull-Up<br>Resistor                         |                                                                                        | 10                         | 14   | 18                | kΩ   |

#### Notes:

- Guaranteed by design over the specified operating temperature range.

All the dynamic specifications (AC specifications) are guaranteed by characterization over the specified operating temperature range, unless otherwise indicated.

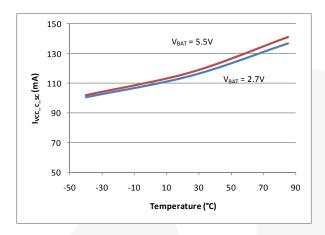

### **Typical Performance Characteristics**

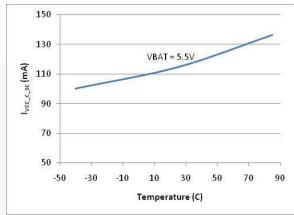

Figure 4. Short-Circuit Current ,( $I_{VCC\_C\_SC}$ ) vs. Temperature  $V_{CC\_C}$ =1.8V ( $V_{SEL}$ =LOW)

Figure 5. Short-Circuit Current, ( $I_{VCC\_C\_SC}$ ) vs. Temperature  $V_{CC\_C}$ =3.0V ( $V_{SEL}$ =HIGH)

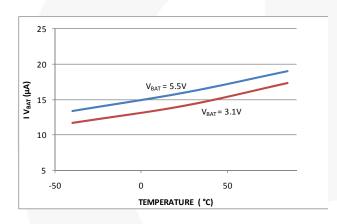

Figure 6.  $IV_{BAT}$  vs. Temperature at  $V_{CC\_C}$ =3.0V  $(V_{SEL}$ =HIGH)

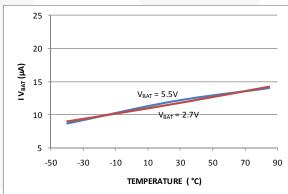

Figure 7.  $IV_{BAT}$  vs. Temperature at  $V_{CC\_C}$ =1.8V ( $V_{SEL}$ =LOW)

### **Application Information**

### **Card Supply Converter**

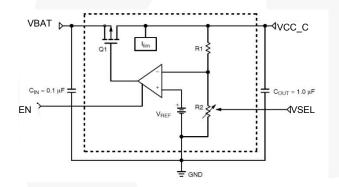

The FXLP4555 interface DC-DC converter is a Low Dropout (LDO) voltage regulator capable of supplying a current in excess of 50mA under 1.8V or 3.0V. Quiescent current is typically lower than 20µA (see Figure 6 and Figure 7). VSEL is a select input, allowing a logic level signal to select a regulated voltage of 1.8V (VSEL = LOW) or 3.0V (VSEL = HIGH).

FXLP4555 has a shutdown input (EN) that allows it to turn off or turn on the regulator output. Figure 8 shows a simplified view of the voltage regulator. The  $V_{CC\_C}$  output is internally current limited and protected against short circuits. The short-circuit current ( $I_{VCC\_C\_SC}$ ) is constant over the SIM Card  $V_{CC}$  and  $V_{BAT}$ , while it varies with operating temperature, typically in the range of 90mA to 140mA (Figure 4 and Figure 5).

To guarantee a stable LDO, the VCC\_C output is connected to a  $1.0\mu F$  bypass ceramic capacitor to ground. At the input,  $V_{BAT}$  is bypassed to ground with a  $0.1\mu F$  ceramic capacitor.

Figure 8. Simplified Block Diagram of the LDO Voltage Regulator

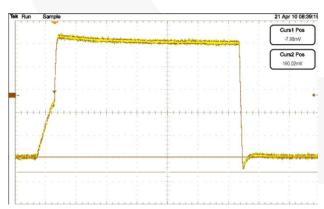

Figure 10. SIM\_IO Typical Rise and Fall Times with Stray Capacitance > 30pF (33pF Capacitor Connected on the Board)

### **Level Shifters**

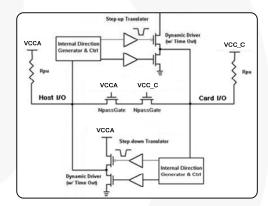

The level shifters accommodate any voltage difference between the Baseband (BB) Processor (1.65V – 5.5V) and the SIM card (1.8V or 3V). The RESET and CLOCK level shifters are uni-directional (from BB to SIM).

The bidirectional I/O line automatically adapts the voltage difference between the baseband and the SIM card in both directions. In addition, with the pull-up resistor, an active edge rate accelerator circuit (see Figure 9) provides a fast charge of the stray capacitance, yielding a rise time within the ISO7816-3 specifications.

The typical waveform provided in Figure 10 shows how the accelerator operates. Two distinct slew rates are observed. From 0V to approximately VCC/2, the slew rate is the RC time constant of the pull-up resistor and the stray capacitance. When the input slope crosses the VCC/2 threshold, the edge rate accelerator is activated, resulting in the faster slew rate from approximately VCC/2 to  $V_{\text{CC}}$  as depicted in Figure 10.

Figure 9. Basic I/O Line Interface

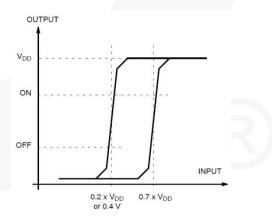

Figure 11. Typical Schmitt Trigger Characteristics

### **Applications Information** (Continued)

### **Input Schmitt Triggers**

All the logic input pins (except I/O\_H and I/O\_C) have built-in Schmitt trigger circuits to prevent uncontrolled operation. Typical dynamic characteristics of the related pins are depicted in Figure 11.

The output signal is guaranteed to go HIGH when the input voltage is above  $0.7 \times V_{DD}$  and go LOW when the input voltage is below 0.4V. See Electrical Characteristics section.

### **Shutdown Operating**

To save power, it is possible to put the FXLP4555 in Shutdown Mode by setting the pin EN LOW. The device enters Shutdown Mode automatically when  $V_{\text{CCA}}$  goes lower than 1.1V typically.

### **ESD Protection**

The FXLP4555 SIM interface features an HBM ESD voltage protection in excess of 7kV for all the SIM pins (IO\_C, CLK\_C, RST\_C, VCC\_C and GND). All the other pins (Host side) sustain at least 2kV. The HBM ESD voltage required by the ISO7816 standard is 4kV.

### **Printed Circuit Board (PCB) Layout**

Careful layout routing should be applied to achieve efficient operating of the device in its mobile or portable environment and to fully exploit its performance.

The bypass capacitors must be connected as close as possible to the device pins (VCC\_C, VCCA, or VBAT) to reduce possible parasitic behaviors (ripple and noise). It is recommended to use ceramic capacitors.

The exposed pad should be connected to ground as well as the unconnected pins (NC). A relatively large ground plane is recommended.

### **Clock Stop**

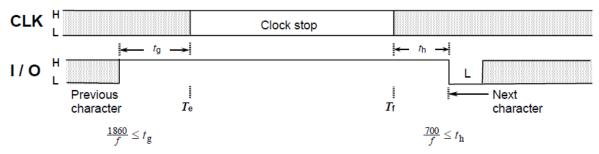

Section 6.3.2 of ISO7816-3 identifies the "Power Management" feature of Clock Stop. For cards supporting Clock Stop, when the interface device expects no transmission from the card and when I/O has remained at state H for at least 1,860 clock cycles (delay  $t_{\rm g}$ ), then according to Figure 13, the interface device may stop the clock on CLK (at time  $t_{\rm e}$ ) while the SIM card  $V_{\rm CC}$  remains powered and RST at state H.

Figure 12. Clock Stop

When the clock is stopped (from time  $t_e$  to time  $t_f$ ), CLK shall be maintained either at state H or at state L, according to the clock stop indicator X defined in section 8.3 of the ISO7816-3 specification.

At time  $t_f$ , the interface device restarts the clock and the information exchange on I/O may continue after at least 700 clock cycles (at time  $t_f + t_h$ ).

The FXLP4555 supports the above description of Clock Stop per ISO7816-3 specifications.

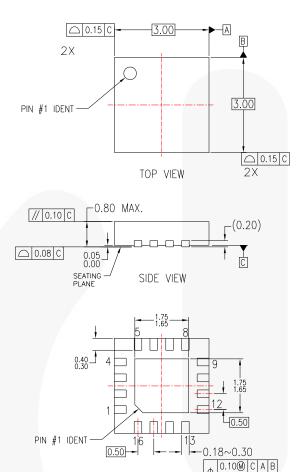

### **Physical Dimensions**

(1.75) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2.16) (2

RECOMMENDED LAND PATTERN

BOTTOM VIEW

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-220, VARIATION WEED-Pending, DATED pending

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

- D. DIMENSIONS ARE EXCLUSIVE OF BURS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

MLP16BrevB

Figure 13. 16-Lead, Molded Leadless Package (MLP), QUAD, JEDEC MO-220, 3mm Square

0.05(M) C

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/MLP16B.html">http://www.fairchildsemi.com/packaging/MLP16B.html</a>.

For current tape and reel specifications, visit Fairchild Semiconductor's online packaging area: <a href="http://www.fairchildsemi.com/packaging/3x3MLP16">http://www.fairchildsemi.com/packaging/3x3MLP16</a> Pack TNR.pdf.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

Power-SPM™

AccuPower™ Auto-SPM™ AX-CAP™ BitSiC<sup>®</sup> Build it Now™ CorePLUS™ CorePOV/ER\*\* CROSSVOLT" CTLTM

Current Transfer Logic™ DEUXPEED<sup>®</sup> Dual Cool™ EcoSPARK® EfficientMax™

ESBC™ **F**® Fairchild® Fairchild Semiconductor® FACT Quiet Series™

FastvCore™ FETBench™ FlashWriter®\*

FACT®

F\_PESTM PowerTrench® FRFET® PowerXS™ Programmable Active Droop™ QFET® Global Power ResourcesM Green EPS™ Green FPS™ e-Series™ OSTM

FPSTM

Gmax™ Quiet Series™ GTO™ RapidConfigure™ IntelliMAX\*\* ISOPLANAR™

MegaBuck™ SignalWise™ MICROCOUPLER" SmartMax™ MicroFET™

MicroPak™ SPM® MicroPak2™ STEALTH™ MillerDrive™ SuperFET<sup>6</sup> MotionMax™ Motion-SPM™ mWSaver™ OptoHiT'\* SupreMOS® OPTOLOGIC® SyncFET™ OPTOPLANAR® Sync-Lock™ SYSTEM ..

Saving our world, 1mWWW/kW at a time™ SMART START™ SuperSOT\*\*-3 SuperSOT™-6 SuperSOT™-8

The Power Franchise®

The Right Technology for Your Success™

p wer

TinyBoost**™** TinyBuck™ TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO\*\* TinyPower™ TinyPWM™ TinyWire™ TranSiC® TriFault Detect™ TRUECURRENT®\* μSerDes™

UHC Ultra FRFET™ UniFET™ **VCXTM** VisualMax™ XS™

PDP SPM™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy, Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification                                                                                                                                                                      | Product Status           | Definition                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information                                                                                                                                                                           | Formative /<br>In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

|                                                                                                                                                                                               |                          | Datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed Full Production Datasheet contains final specifications. Fairchild Semiconductor reserves the right to mal changes at any time without notice to improve the design. |                          | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete Not In Production Datasheet contains specifications on a product that is disconfined that is disconfined to the datasheet is for reference information only.                         |                          | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev 154

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.