#### **CTLDM7590**

### SURFACE MOUNT P-CHANNEL ENHANCEMENT-MODE SILICON MOSFET

#### **APPLICATIONS:**

- Load/Power Switches

- Boost/Buck Converters

- Battery Charging/Power Management

| MAXIMUM RATINGS: (T <sub>A</sub> =25°C)    |

|--------------------------------------------|

| Drain-Source Voltage                       |

| Gate-Source Voltage                        |

| Continuous Drain Current (Steady State)    |

| Pulsed Drain Current, tp=10µs              |

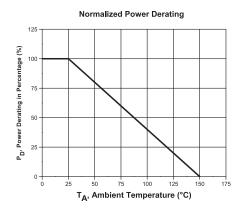

| Power Dissipation                          |

| Operating and Storage Junction Temperature |

| Thermal Resistance                         |

www.centralsemi.com

#### **DESCRIPTION:**

The CENTRAL SEMICONDUCTOR CTLDM7590 is an enhancement-mode P-channel MOSFET designed for applications including high speed pulsed amplifiers and drivers. This MOSFET has beneficially low rDS(ON), low threshold voltage, and very low gate charge characteristics.

**MARKING CODE: 2**

#### **FEATURES:**

- ESD protection up to 2kVPower dissipation: 125mW

- Low rDS(ON)

- Low threshold voltage

- Ultra small, ultra low profile 0.6mm x 0.8mm x 0.4mm TLM™ leadless surface mount package

| SYMBOL                            |             | UNITS |

|-----------------------------------|-------------|-------|

| $V_{DS}$                          | 20          | V     |

| $V_{GS}$                          | 8.0         | V     |

| ID                                | 140         | mA    |

| $I_{D}$                           | 600         | mA    |

| $P_{D}$                           | 125         | mW    |

| T <sub>J</sub> , T <sub>stg</sub> | -65 to +150 | °C    |

| $\Theta_{JA}$                     | 1000        | °C/W  |

|                                   |             |       |

| ELECTRICAL | CHARACTERISTICS: ( | T <sub>A</sub> =25°C unless | otherwise not | ed) |

|------------|--------------------|-----------------------------|---------------|-----|

|            |                    |                             |               |     |

| SYMBOL                                | TEST CONDITIONS                               | MIN | TYP  | MAX | UNITS |

|---------------------------------------|-----------------------------------------------|-----|------|-----|-------|

| I <sub>GSSF</sub> , I <sub>GSSR</sub> | $V_{GS}$ =5.0V, $V_{DS}$ =0                   |     |      | 100 | nA    |

| I <sub>DSS</sub>                      | $V_{DS}$ =5.0V, $V_{GS}$ =0                   |     |      | 50  | nA    |

| IDSS                                  | $V_{DS}$ =16V, $V_{GS}$ =0                    |     |      | 100 | nA    |

| BV <sub>DSS</sub>                     | V <sub>GS</sub> =0, I <sub>D</sub> =250μA     | 20  |      |     | V     |

| V <sub>GS(th)</sub>                   | $V_{DS}=V_{GS}$ , $I_{D}=250\mu A$            | 0.4 |      | 1.0 | V     |

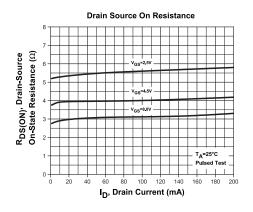

| r <sub>DS(ON)</sub>                   | V <sub>GS</sub> =4.5V, I <sub>D</sub> =100mA  |     | 4.0  | 5.0 | Ω     |

| rDS(ON)                               | $V_{GS}$ =2.5V, $I_D$ =50mA                   |     | 5.5  | 7.0 | Ω     |

| rDS(ON)                               | V <sub>GS</sub> =1.8V, I <sub>D</sub> =20mA   |     | 8.0  | 10  | Ω     |

| r <sub>DS(ON)</sub>                   | $V_{GS}$ =1.5V, $I_D$ =10mA                   |     | 11   | 17  | Ω     |

| rDS(ON)                               | V <sub>GS</sub> =1.2V, I <sub>D</sub> =1.0mA  |     | 20   |     | Ω     |

| Q <sub>g(tot)</sub>                   | $V_{DS}$ =10V, $V_{GS}$ =4.5V, $I_{D}$ =100mA |     | 0.50 |     | nC    |

| Qgs                                   | $V_{DS}$ =10V, $V_{GS}$ =4.5V, $I_{D}$ =100mA |     | 0.17 |     | nC    |

| $Q_{gd}$                              | $V_{DS}$ =10V, $V_{GS}$ =4.5V, $I_{D}$ =100mA |     | 0.11 |     | nC    |

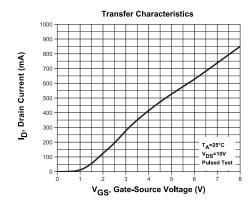

| 9FS                                   | $V_{DS}$ =5.0V, $I_{D}$ =125mA                |     | 140  |     | mS    |

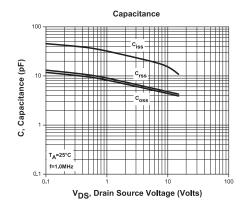

| C <sub>rss</sub>                      | $V_{DS}$ =15V, $V_{GS}$ =0, f=1.0MHz          |     | 4.0  |     | pF    |

| C <sub>iss</sub>                      | $V_{DS}$ =15V, $V_{GS}$ =0, f=1.0MHz          |     | 10   |     | pF    |

| Coss                                  | $V_{DS}$ =15V, $V_{GS}$ =0, f=1.0MHz          |     | 3.7  |     | pF    |

| t <sub>on</sub>                       | $V_{DD}$ =10V, $V_{GS}$ =4.5V, $I_{D}$ =200mA |     | 35   |     | ns    |

| <sup>t</sup> off                      | $V_{DD}$ =10V, $V_{GS}$ =4.5V, $I_{D}$ =200mA |     | 100  |     | ns    |

R3 (21-September 2012)

#### CTLDM7590

# SURFACE MOUNT P-CHANNEL ENHANCEMENT-MODE SILICON MOSFET

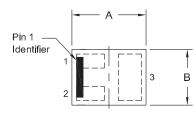

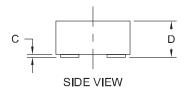

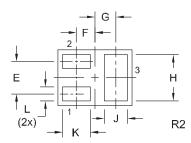

#### TLM3D6D8 CASE - MECHANICAL OUTLINE

TOP VIEW

BOTTOM VIEW

| DIMENSIONS          |       |       |        |       |

|---------------------|-------|-------|--------|-------|

|                     | INC   | HES   | MILLIM | ETERS |

| SYMBOL              | MIN   | MAX   | MIN    | MAX   |

| Α                   | 0.029 | 0.034 | 0.75   | 0.85  |

| В                   | 0.021 | 0.026 | 0.55   | 0.65  |

| С                   | 0.000 | 0.002 | 0.00   | 0.05  |

| D                   | 0.012 | 0.016 | 0.31   | 0.40  |

| Е                   | 0.014 |       | 0.     | 35    |

| F                   | 0.008 |       | 0.:    | 20    |

| G                   | 0.009 |       | 0.2    | 225   |

| Н                   | 0.017 | 0.022 | 0.45   | 0.55  |

| J                   | 0.008 | 0.012 | 0.20   | 0.30  |

| K                   | 0.010 | 0.014 | 0.25   | 0.35  |

| L                   | 0.004 | 0.008 | 0.10   | 0.20  |

| TLM3D6D8 (PEV/: P2) |       |       |        |       |

TLM3D6D8 (REV: R2)

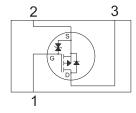

### PIN CONFIGURATION (Bottom View)

#### LEAD CODE:

- 1) Gate

- 2) Source

- 3) Drain

MARKING CODE: 2

#### CTLDM7590

## SURFACE MOUNT P-CHANNEL ENHANCEMENT-MODE SILICON MOSFET

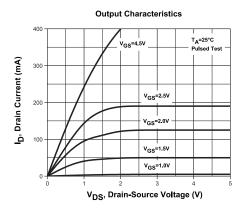

#### TYPICAL ELECTRICAL CHARACTERISTICS

R3 (21-September 2012)

#### **OUTSTANDING SUPPORT AND SUPERIOR SERVICES**

#### PRODUCT SUPPORT

Central's operations team provides the highest level of support to insure product is delivered on-time.

- Supply management (Customer portals)

- · Inventory bonding

- · Consolidated shipping options

- · Custom bar coding for shipments

- · Custom product packing

#### **DESIGNER SUPPORT/SERVICES**

Central's applications engineering team is ready to discuss your design challenges. Just ask.

- Free guick ship samples (2<sup>nd</sup> day air)

- Online technical data and parametric search

- SPICE models

- · Custom electrical curves

- · Environmental regulation compliance

- · Customer specific screening

- · Up-screening capabilities

- Special wafer diffusions

- PbSn plating options

- · Package details

- Application notes

- · Application and design sample kits

- · Custom product and package development

#### REQUESTING PRODUCT PLATING

- 1. If requesting Tin/Lead plated devices, add the suffix "TIN/LEAD" to the part number when ordering (example: 2N2222A TIN/LEAD).

- 2. If requesting Lead (Pb) Free plated devices, add the suffix "PBFREE" to the part number when ordering (example: 2N2222A PBFREE).

#### **CONTACT US**

#### Corporate Headquarters & Customer Support Team

Central Semiconductor Corp. 145 Adams Avenue Hauppauge, NY 11788 USA

Main Tel: (631) 435-1110 Main Fax: (631) 435-1824

Support Team Fax: (631) 435-3388

www.centralsemi.com

Worldwide Field Representatives: <a href="https://www.centralsemi.com/wwreps">www.centralsemi.com/wwreps</a>

**Worldwide Distributors:**

www.centralsemi.com/wwdistributors

For the latest version of Central Semiconductor's **LIMITATIONS AND DAMAGES DISCLAIMER**, which is part of Central's Standard Terms and Conditions of sale, visit: <a href="https://www.centralsemi.com/terms">www.centralsemi.com/terms</a>

www.centralsemi.com (001)

### Product End of Life Notification

| PDN ID:            | PDN01006 |

|--------------------|----------|

| Notification Date: | 10/21/15 |

| Last Buy Date:     | 4/21/16  |

| Last Shipment Date | 10/21/16 |

Summary: All devices manufactured in the TLM3D6D8 package are discontinued and is now classified as End of Life (EOL).

Although Central Semiconductor Corp. makes every effort to continue to produce devices that have been proclaimed EOL (End of Life) by various manufacturers, it is an accepted industry practice to discontinue certain devices when customer demand falls below a minimum level of sustainability. Accordingly, the following product(s) have been transitioned to End of Life status as part of Central's Product Management Process. Any replacement product will be noted below. The effective date for placing the last purchase order will be six(6) months from the date of this notice and twelve(12) months from the notice date for final shipments; this may be extended if inventory is available.

| Central Part Number | Replacement |

|---------------------|-------------|

| CTLDM3590 BK        | N/Ā         |

| CTLDM3590 TR        | N/A         |

| CTLDM7590 BK        | N/A         |

| CTLDM7590 TR        | N/A         |

Central would be happy to assist you by providing additional information or technical data to help locate an alternate source if we have no replacement available. Please email your requests to engineering@centralsemi.com.

DISCLAIMER: This End of Life (EOL) notification is in accordance with JEDEC standard JESD48 - Product Discontinuance. Central Semiconductor Corp. will make every effort to offer life-time buy (LTB) opportunities and/or offer replacement devices to existing customers for discontinued devices, however, one or both may not be possible for all devices. Please contact your local Central Semiconductor sales representative for LTB opportunities/additional information.

CCC785 REV 002