MPU 800-1 MPU 800-4 PRELIMINARY

# High-Performance Low-Power Microprocessor

#### **FEATURES**

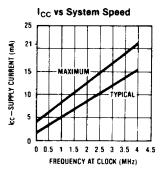

Variable Power Supply: 2.4V - 6.0V Fully Compatible Wth Z80° Instruction Set Pin-Compatible With NSC800 Powerful Set of 158 Instructions 10 Addressing Modes 22 Internal Registers Low Power: 50 mW at 5 V Vcc Multiplexed Bus Structure On Chip Bus Controller and Clock Generator On-Chip 8 bit Dynamic RAM Refresh Circuitry Three Speed Versions: MPU800-4 4 MHz 2.5 MHz MPU800 MPU800-1 1 MHz Capable of addressing 64 k bytes of memory, and 256 I/O devices Five interrupt request lines on-chip Schmitt trigger input on reset Power-Save Feature

# **PIN CONFIGURATION**

| A8                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A9   2   39   PS   A10   3   38   WAIT   A11   4   37   RESET OUT   A12   5   36   BREO   A13   6   35   BREO   A14   7   34   10/M   A15   8   33   RESET IN   CLK   9   32   RD   XOUT   10   31   WR   XIN   11   30   ALE   ADO   12   29   SO   AD1   13   28   RESH   AD2   14   27   S1   AD3   15   26   INTA   AD4   16   25   INTA   AD5   17   24   RESTE   AD6   18   23   RESTE |

| A10   3   38   WAIT  A11   4   37   RESET OUT  A12   5   36   BREO  A13   6   35   BACK  A14   7   34   10/M  A15   8   33   RESET IN  CLK   9   32   RD  XOUT   10   31   WR  XIN   11   30   ALE  ADO   12   29   SO  AD1   13   28   RESET  AD2   14   27   S1  AD3   15   26   INTA  AD4   16   25   INTA  AD5   17   24   RESTE                                                         |

| A11                                                                                                                                                                                                                                                                                                                                                                                          |

| A12     5   36   BREO   A13     6   35   BACK   A14     7   34   10/M   A15     8   33   RESET IN   CLK   9   32   RD   XOUT   10   31   WR   XIN     11   30   ALE   ADO     12   29   SO   AD1     13   28   RFSH   AD2     14   27   S1   AD3     15   26   INTA   AD4     16   25   INTA   AD5     17   24   RSTC   AD6     18   23   RSTE                                               |

| A13   6 35   BACK A14   7 34   10/M A15   8 33   RESET IN CLK   9 32   RD XOUT   10 31   WR XIN   11 30   ALE ADO   12 29   SO AD1   13 28   RESH AD2   14 27   S1 AD3   15 26   INTA AD4   16 25   INTA AD5   17 24   RSTC AD6   18 23   RSTE                                                                                                                                               |

| A14   7                                                                                                                                                                                                                                                                                                                                                                                      |

| A15   8 33   RESET IN CLK   9 32   RD XOUT   10 31   WR XIN   11 30   ALE ADO   12 29   SO AD1   13 28   RFSH AD2   14 27   S1 AD3   15 26   INTA AD4   16 25   INTA AD5   17 24   RSTC AD6   18 23   RSTB                                                                                                                                                                                   |

| CLK   9   32   FD   NOT    XOUT   10   31   WF    XIN   11   30   ALE    ADO   12   29   SO    AD1   13   28   RFSH    AD2   14   27   S1    AD3   15   26   NTA    AD4   16   25   NTA    AD5   17   24   RSTC    AD6   18   23   RSTE                                                                                                                                                      |

| XOUT   10   31   WF<br>XIN   11   30   ALE<br>ADO   12   29   3   SO<br>AD1   13   28   AFSH<br>AD2   14   27   S1<br>AD3   15   26   INTA<br>AD4   16   25   INTR<br>AD5   17   24   ASTE<br>AD6   18   23   ASTE                                                                                                                                                                           |

| XIN   11                                                                                                                                                                                                                                                                                                                                                                                     |

| ADO   12 29 SO AD1   13 28 PRSH AD2   14 27 S1 AD3   15 26 PNTA AD4   16 25 PNTA AD5   17 24 PRSTE AD6   18 23 PRSTE                                                                                                                                                                                                                                                                         |

| AD1   13                                                                                                                                                                                                                                                                                                                                                                                     |

| AD2   14 27   S1<br>AD3   15 26   INTA<br>AD4   16 25   INTA<br>AD5   17 24   RSTC<br>AD6   18 23   RSTB                                                                                                                                                                                                                                                                                     |

| AD3   15 26   INTA<br>AD4   16 25   INTA<br>AD5   17 24   RSTC<br>AD6   18 23   RSTB                                                                                                                                                                                                                                                                                                         |

| AD4 C 16 25 NTTR<br>AD5 C 17 24 RSTC<br>AD6 C 18 23 PSTB                                                                                                                                                                                                                                                                                                                                     |

| AD5   17   24   RSTC<br>AD6   18   23   RSTB                                                                                                                                                                                                                                                                                                                                                 |

| AD6 ☐ 18 23 ☐ RSTB                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                              |

| AD7 D 19 22 D RSTA                                                                                                                                                                                                                                                                                                                                                                           |

| GND 20 21 NMI                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                              |

# **GENERAL DESCRIPTION**

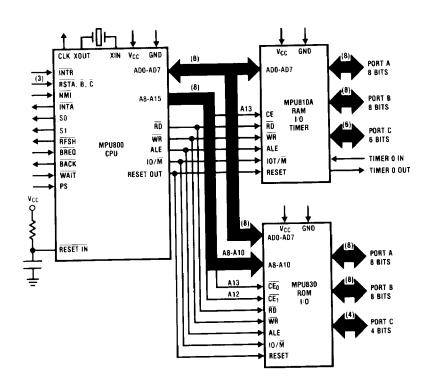

The MPU800 is an 8 bit microprocessor that functions as the central processing unit (CPU) in Standard Microsystems MPU800 microcomputer family. The device is fabricated in double-poly CMOS to combine high performance with the low-power of CMOS.

Many system functions are incorporated on the device

including: vectored priority interrupts, refresh control, power save, and interrupt acknowledge.

Dedicated peripherals (MPU810 Ram I/O Timer, MPU830 ROM I/O Timer, and (MPU831 I/O Timer) have on-chip logic for direct interface to the MPU800.

# **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO      | NAME                       | SYMBOL              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40          | + 5 Volt                   | Vcc                 | + 5 volt supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 20          | Ground                     | GND                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10          | Crystal Out                | XOUT                | Crystal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11          | Crystal In                 | XIN                 | Crystal connection; XIN may be used as an external clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Input/Outp  | ut Signals                 |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12-19       | Address/Data               | AD0-AD7             | Multiplexed Address/Data. Active high At RD Time: Input data to CPU. At WR Time: Output data from CPU. At Falling Edge of ALE Time: Least significant byte of address during memory reference cycle. 8-bit port address during I/O puring BREQ/ reference cycle.  BACK Cycle: High impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Input Signa |                            | DECETIN             | Active low. Sets A (8-15) and AD (0-7) to TRI-STATE® (high impedance).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 33          | Reset In                   | RESET IN            | Clears the contents of PC, I and R registers, disables interrupts, and causes a reset output to be activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 36          | Bus Request                | BREQ                | Active low. Used when another device is requesting the system bus. BREQ is recognized at the end of the current machine cycle, then A(8-15), AD(0-7), IO/M, RD, and WR are set to the high impedance mode and the request is acknowledged via the BACK output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21          | Non-Maskable<br>Interrupt  | NMI                 | Active low. The non-maskable interrupt, generated by the peripheral device(s), is the highest priority interrupt request line. The interrupt is edge sensitive and only a pulse is required to set an internal flip-flop which generates the internal interrupt request. Since the NMI flip-flop is monitored on the same clock edge as the other interrupts, it must also meet the minimum set-up time spec for the interrupt to be accepted in the current machine instruction. Once the interrupt is accepted the flip-flop is reset automatically, its execution is independent of the interrupt enable flip-flop. NMI execution involves saving the PC on the stack and automatic branching to restart address X'0066 in memory. |

| 22-4        | Restart Interrupt<br>A,B,C | RSTA, RSTB,<br>RSTC | Active low level sensitive. Restarts generated by the peripherals are recognized at the end of the current instruction if their respective interrupt enable bits and master enable bit are set. Execution is identical to NMI except interrupts are enabled for the following restart addresses:    Name   Restart                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 25          | Interrupt Request          | INTR                | Active low level sensitive. An interrupt request input generated by a peripheral device is recognized at the end of the current instruction provided that the interrupt enable and master interrupt enable bits are set INTR is the lowest priority interrupt request input. Under program control, INTR can be executed in three distinct modes in conjunction with the INTA output.                                                                                                                                                                                                                                                                                                                                                 |

| 38          | Wait                       | WAIT                | Active low. When set low during RD, WR or INTA machine cycles, the CPU extends its machine cycle in increments of t (wait) states. The wait machine cycle continues until the WAIT input returns high.  The wait strobe input will be accepted only during machine cycles that have RD, WR or INTA strobes and during the machine cycle immediately after an interrupt has been accepted by the CPU. The later cycle has its RD strobe suppressed but it will still accept the wait.                                                                                                                                                                                                                                                  |

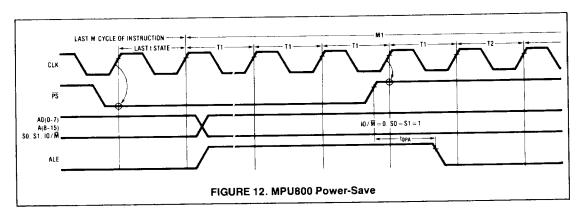

| 39          | Power Save                 | PS                  | Active low. PS is sampled at the end of the current instruction cycle When PS is low, the CPU stops executing at the end of current instruction and keeps itself in the low-power mode. Normal operation resumes when PS is returned high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

TRI-STATE\* is a registered trademark of National Semiconductor Corporation.

| PIN NO      | NAME                  | SYMBOL    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FUNC                                  | TION                                |                                   |                       |                         |

|-------------|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------|-----------------------------------|-----------------------|-------------------------|

| Output Sign |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |                                     |                                   |                       |                         |

| 35          | Bus Acknowledge       | BACK      | Active low. BACK indicates to the bus requesting device that the CPU bus and its control signals are in the TRI-STATE mode. The requesting device may then take control of the bus and its control signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |                                     |                                   |                       | questing                |

| 1-8         | Address Bits 8-15     | A8-A15    | Active high. These are the most significant 8 bits of the memory address during a memory instruction. During an I/O instruction, the port address on the lower 8 bits of address get duplicated onto these 8 bits. During a BREQ/BACK cycle, the A (8-15) bus is in the TRI-STATE mode.                                                                                                                                                                                                                                                                                                                                                                                       |                                       |                                     |                                   |                       |                         |

| 37          | Reset Out             | RESET OUT | Active high. When RESET reset. The signal is norma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | lly used to                           | reset th                            | e periphe                         | ral device            | es.                     |

| 34          | Input/Output/Memory   | IO/M      | An active high on the IO/<br>cycle is relative to an input<br>put signifies that the curre<br>TRI-STATE during BREQ/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | output de<br>ent machi<br>BACK cyc    | vice. An<br>ne cycle<br>les.        | active lov                        | on the leto men       | O/M out-<br>nory. It is |

| 28          | Refresh               | RFSH      | Active low. The refresh ou<br>cycle is in progress. RFSh<br>cycles. During the refresh<br>A(8-15) indicates the intern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d goes lov<br>cycle, Al<br>rupt vecto | v during<br>D(0-7) ha<br>ir registe | T3 and Tels<br>s the refr<br>r l. | 4 states<br>esh add   | of all M1<br>ress and   |

| 30          | Address Latch Enable  | ALE       | ALE is active only during the M1 cycles. The high to lememory/I-0/refresh addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ow transi<br>ss is avail              | tion of A<br>able on t              | LE indic<br>he AD(0-7             | ates tha<br>7) lines. | t a valid               |

| 32          | Read Strobe           | RD        | Active low. On the trailing evia the AD(0-7) lines. The FBREQ/BACK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RD line is i                          | n the TRI                           | I-STATE IT                        | node dur              | ing<br>                 |

| 31          | Write Strobe          | WR        | While the WR line is low, v lines. The WR line is in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TRI-STAT                              | E mode d                            | luring BRI                        | EQ/BAC                | K cycles                |

| 9           | Clock                 | CLK       | CLK is an output provided square wave at one half the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ne input fr                           | equency                             |                                   |                       |                         |

| 26          | Interrupt Acknowledge | INTA      | Active low. The interrupt acknowledge output is activated in the M1 cycle (S) immediately following the t state in which the INTR input is recognized. [Output is normally used to gate the interrupt response vector from the peripheral controller onto the AD(0-7) lines.] It is used in two of the three interrupt modes. In mode 0, an instruction is gated onto the AD (0-7) line during INTA. There will be from 1 to 4 INTA strobes issued for each mode 0 interrupt. The amount of INTA strobes issued is instruction dependent. In mode 2, a single interrupt response vector is gated onto the data bus. In mode 1, INTA is not used. In this mode, INTA functions |                                       |                                     |                                   |                       |                         |

| 29, 27      | Status                | SO, S1    | like the restart interrupts.  Bus status outputs indicat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e encode                              | d informa                           | ation rega                        | rding the             | ensuing                 |

|             |                       |           | M cycle as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                                     |                                   |                       |                         |

|             |                       |           | Machine Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |                                     | tus                               |                       | trol                    |

|             |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SO                                    | <u>Ş1</u>                           | 10/M<br>0                         | RD<br>0               | WR 1                    |

|             |                       |           | Opcode Fetch<br>Memory Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 0                                   | 1 1                                 | 0                                 | 0                     |                         |

|             |                       | 1         | Memory Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | ò                                   | 0                                 | 1                     | 0                       |

|             |                       |           | I/O Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                     | 1                                   | 1 1                               | 0                     | 1                       |

|             |                       |           | I/0 Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 0                                   | 0                                   | 1 0                               | 0                     | 0                       |

|             |                       |           | Halt* Internal Operation*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                     | 1                                   | 0                                 | 1                     | ;                       |

|             |                       |           | Acknowledge of Int**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                     | 1                                   | 0                                 | 1                     | 1                       |

|             |                       |           | *ALE is not suppressed in this **This is the cycle that occurs in (RSTA, RSTB, ASTC, INTR,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nmediately                            | after the                           | CPU accep                         | ots an inte           | rrupt                   |

|             |                       | •         | Note 1: During halt, CPU continues to do dummy opcode fetch from location following the halt instruction with a halt status. This is so CPU can continue to do its dynamic RAM refresh.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |                                     |                                   |                       |                         |

| I .         | i                     |           | Note 2: No early status is pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ovided for i                          | nterrunt o                          | r hardware                        | ractarte              |                         |

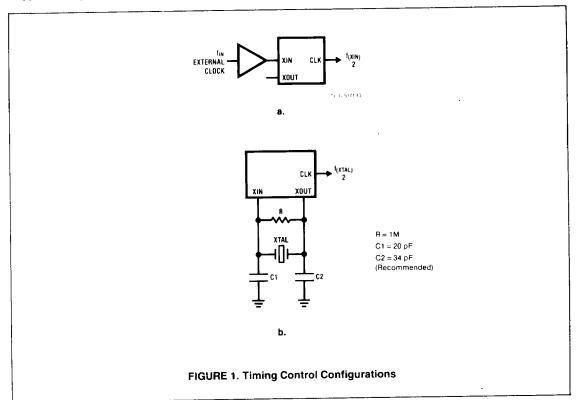

### **TIMING CONTROL**

All necessary timing signals are provided by a single state inverter oscillator contained on the MPU800 chip. The chip operation frequency is equal to one half of the frequency of this oscillator. The oscillator frequency can be controlled by one of the following methods:

- Leaving the XOUT pin unterminated and driving the XIN pin with an externally generated clock as shown in Figure 1a. When driving XIN with a square wave, the minimum duty cycle is 30%-70%, either high or low.

- Connecting a crystal with the proper biasing network between XIN and XOUT as shown in Figure 1b. Recommended crystal is a parallel resonance AT cut crystal.

Resistor capacitor feedback network described in earlier data sheets will not oscillate due to gain of internal inverter circuit. A modification of this circuit by adding two inverters in series between the RC network and XIN will work.

The CPU has a minimum clock frequency input (@ XIN) of 32 kHz, which results in 16 kHz system clock speed. All registers internal to the chip are static, however there is dynamic logic which limits the minimum clock speed. The input clock can be stopped without fear of losing any data or damaging the part. You stop it in the phase of the clock that has XIN low and CLK OUT high. When restarting the CPU, precautions must be taken so that the input clock meets minimum specification. Once started, the CPU will continue operation from the same location at which it was stopped. During DC operation of the CPU, typical current

drain will be 2mA. This current drain can be reduced by placing the CPU in a wait state during an opcode fetch cycle then stopping the clock.

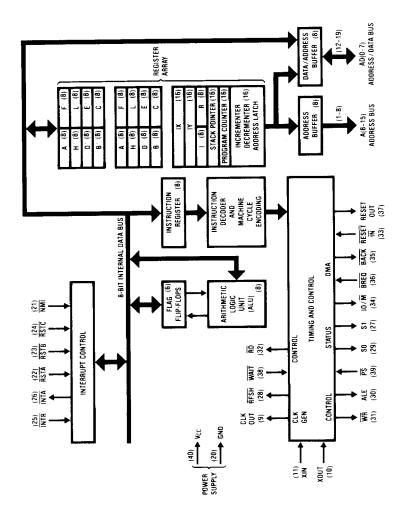

# **FUNCTIONAL DESCRIPTION**

The MPU800 is an 8-bit general purpose microprocessor designed for stand-alone and DMA (direct memory access) applications. A minimum system can be constructed with an MPU800, and MPU810 (RAMI/O Timer) and an 27C16 (EPROM).

MPU800 uses a multiplexed bus for data and addresses. The 16-bit address bus is divided into a high-order 8-bit address bus that handles bits 8-15 of the address, and a low-order 8-bit mulitplexed address/data bus that handles bits 0-7 of the address and bits 0-7 of the data. Strobe outputs from the MPU800 (ALE, RD and WR) indicate when a valid address or data is present on the bus. IO/M indicates whether the ensuing cycle accesses memory or I/O.

During an input or output instruction, the CPU duplicates the lower half of the address [AD(0-7)] onto the upper half [A(8-15)]. The eight bits of address will stay on A(8-15) for the entire machine cycle.

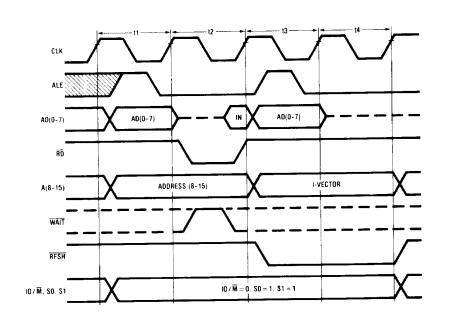

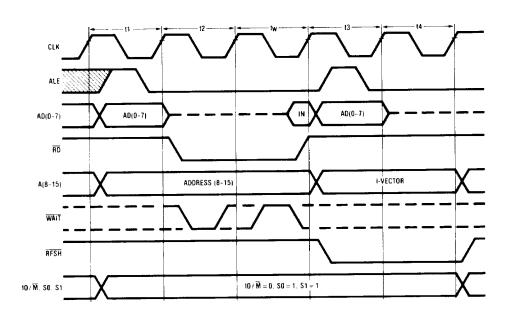

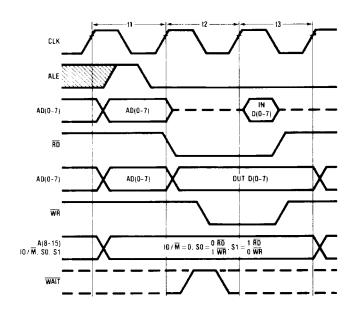

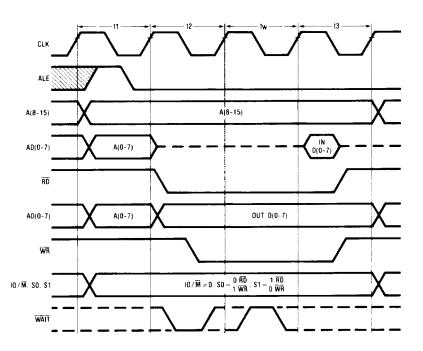

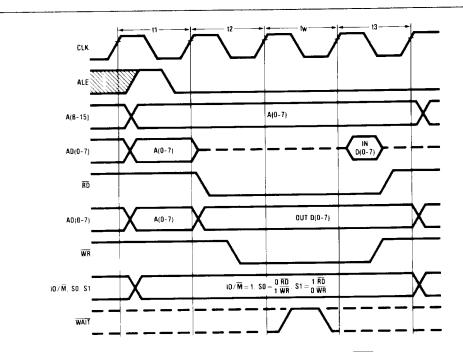

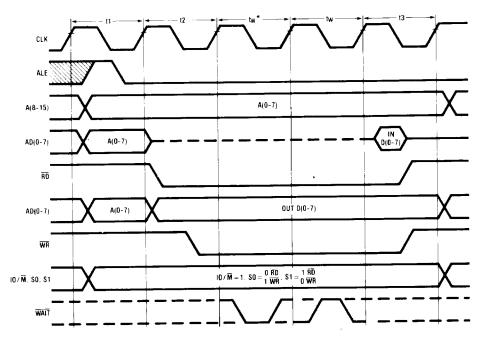

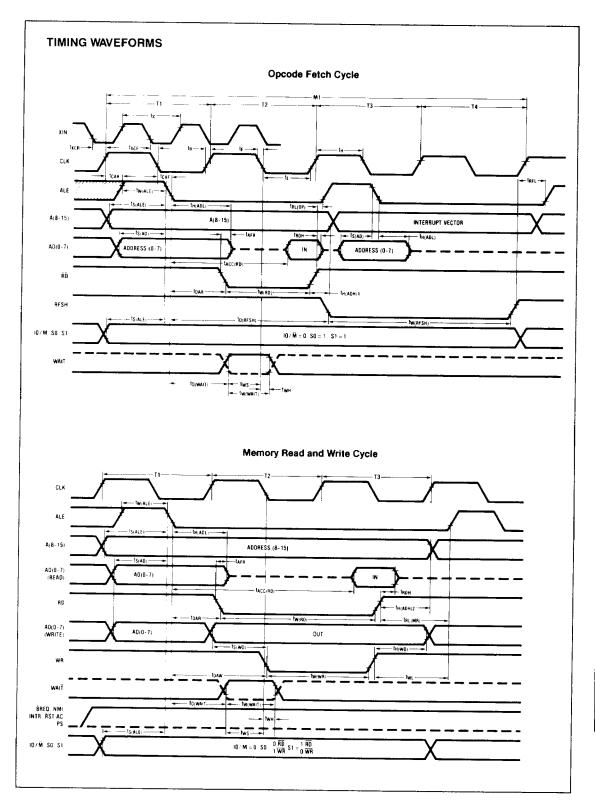

Figure 2 illustrates the timing relationship for opcode fetch cycles with and without a wait state. Figure 3 illustrates the timing relationship for memory read and write cycles with and without a wait state. Input/output cycles with and without wait state are shown in Figure 4. One wait state is automatically inserted into each I/O instruction.

FIGURE 2a. Opcode Fetch Cycles without WAIT States

FIGURE 2b. Opcode Fetch Cycles with WAIT States

FIGURE 3a. Memory Read/Write Cycles without WAIT States

FIGURE 3b. Memory Read and Write with WAIT States

FIGURE 4a. Input and Output Cycles without WAIT States

\*WAIT state automatically inserted during IO operation.

FIGURE 4b. Input and Output Cycles with WAIT States

#### INITIALIZATION

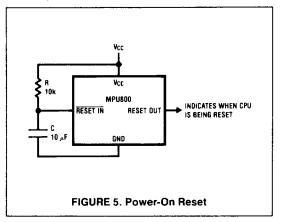

The MPU800 and its peripheral components are initialized by RESET IN and RESET OUT. RESET IN input is associated with an on-chip Schmitt trigger that facilitates using an R-C network power-on reset scheme (Figure 5).

To ensure proper power-up conditions for the NSC800, the following power-up and initialization procedure is recommended:

- Apply power (V<sub>cc</sub> and GND) and set RESET IN active (low). Allow sufficient time (approximately 100 ms if crystal used) for the oscillator and internal clocks to stabilize. RESET IN must remain low for at least 3t state (CLK) times. RESET OUT, following the clock stabilization period, responds by going high, indicating to the system that the MPU800 is being reset. RESET OUT signal becomes available to reset the peripherals.

- 2. Set RESET IN high, following which the RESET OUT goes low and the CPU initiates the first opcode fetch cycle.

NOTE: The MPU800 initialization includes: Clear PC to X'0000 (the first opcode fetch, therefore, is from memory location X'0000). Clear registers I (Interrupt Vector Base) and R (Refresh Counter) to X'00. Clear interrupt control register bits IEA, IEB and IEC. The interrupt control bit IEI is set to 1 to maintain INS8080A/Z80A compatibility (see INTERRUPTS for more details). Maskable interrupts are disabled and the CPU enters Interrupt Mode 0. While RESET IN is active (low), the A(8-15) and AD(0-7) lines go to high impedance (TRI-STATE) and all CPU strobes go to the inactive state.

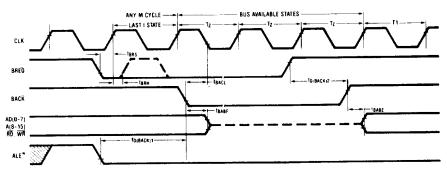

#### **BUS ACCESS CONTROL**

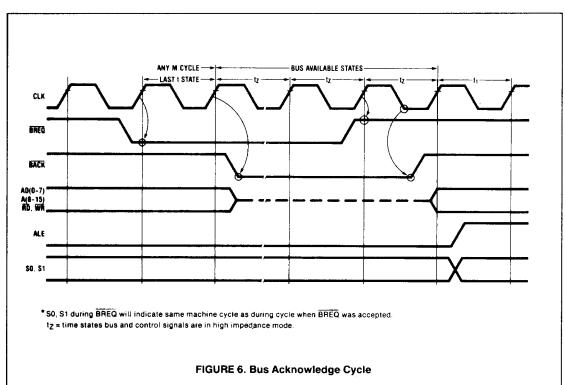

Figure 6 illustrates bus access control in the MPU800. The external device controller produces an active BREQ signal that requests the bus. When the CPU responds with BACK then the bus and related control strobes go to high impedance (TRI-STATE). It should be noted that (1) BREQ is sampled at the last t state of any M machine cycle only. (2) the MPU800 will not acknowledge any interrupt/restart requests, and will not perform any dynamic RAM refresh functions until after BREQ input signal is inactive high. (3) BREQ signal has priority over all interrupt request signals, should BREQ and interrupt request become active simultaneously.

# REGISTER CONFIGURATION

The MPU800 contains 22 programmable registers as shown in *Figure 7*. The CPU working registers are arranged in two 8-register configurations, each of which includes an 8-bit accumulator, a flag register, and six general purpose 8-bit registers. Only one 8-bit register set may be active at any given moment. However, simple instructions exist that allow the programmer to exchange the active and alternate register sets.

It should also be noted that the six 8-bit general purpose registers (B, C, D, E, H, and L) can be accessed as 16-bit registers (BC, DE, and HL). The functions of these become apparent in the instruction set description.

|               |        | ing Register S | et<br>/o\  |

|---------------|--------|----------------|------------|

| Accumulator   | (8)    |                | (8)<br>(8) |

| Register B    | (8)    |                | (8)        |

| Register D    |        | Register E     |            |

| Register H    | (8)    | Register L     | (8)        |

| CPU Altern    | ate W  | orking Registe | r Set      |

| Accumulator A |        |                | (8)        |

| Register B'   | (8)    | Register C'    | (8)        |

| Register D'   | (8)    | Register E'    | (8)        |

| Register H'   | (8)    |                | (8)        |

| CPU [         | Dedica | ited Registers |            |

| Index Regis   |        | (16            | 5)         |

| Index Regis   |        | (16            |            |

| Interrupt Ve  |        | `              | •          |

| Register I    |        | (8)            | )          |

| Memory Re     | fresh  | <b>V</b> -7    |            |

| Register R    |        | (8)            | )          |

| Stack Point   | er SP  | (16            |            |

| Program       | .c. o. | (              | ,          |

| Counter PC    | :      | (16            | 6)         |

| Counter C     | ,      | (              | • •        |

# **DEDICATED REGISTERS:**

Program Counter (PC): The program counter contains the 16-bit address of the current instruction being fetched from memory. The PC is incremented after its contents have been transferred to the address lines. When a program jump occurs, the new address is placed in the PC, overriding the incrementer.

Stack Pointer (SP): The stack pointer contains the 16-bit address of the current top of a stack located in external system RAM memory. The external stack memory is organized as a last-in, first-out (LIFO) file. The stack allows simple implementation of multiple level interrupts, virtually unlimited subroutine nesting and simplification of many types of data manipulation.

Index Registers (IX and IY): The two 16-bit index registers hold a 16-bit base address used in indexed addressing modes. In this mode, an index register is used as a base to point to a region in memory from which data is to be stored or retrieved. An additional byte is included in indexed instructions to specify a displacement from this base. This displacement is specified as a two's complement signed integer.

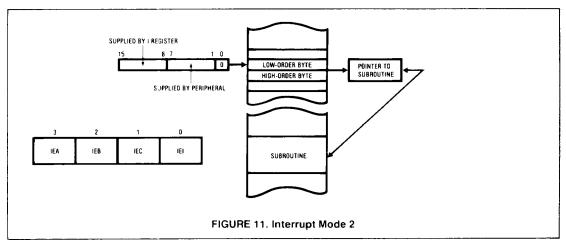

Interrupt Page Address Register (I): The MPU800 CPU can indirectly call any memory location in response to a mode 2 interrupt. The I register is used to store the highorder 8 bits of the address. The low-order 8 bits are supplied by the interrupting peripheral. This feature allows interrupt routines to be dynamically located anywhere in memory with minimal access time to the routine.

Memory Refresh Register (R): The MPU800 CPU contains a memory refresh counter to enable dynamic memories to be used with the same ease as static memories. This 8-bit register is automatically incremented after each instruction fetch. The data in the refresh counter is sent out on the lower portion of the address bus along with a refresh control signal while the CPU is decoding and executing the fetched instruction. This mode of refresh is totally transparent to the programmer and does not slow down CPU operation. The programmer can load the R register for testing purposes, but this register is normally not used by the programmer.

# **ACCUMULATORS AND FLAG REGISTERS**

The CPU includes two 8-bit accumulators and two associated 8-bit flag registers. The accumulator holds the results of 8-bit arithmetic or logical operation. The flag register indicates specific conditions for 8-bit or 16-bit operations.

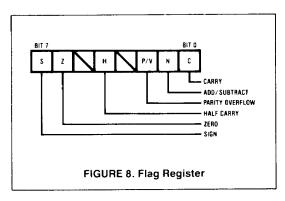

# FLAG REGISTERS (F, F')

The two MPU800 flag registers each contain six status bits that are set or reset (cleared) by various CPU operations (Figure 8). Four of these bits (carry, zero, sign, and parity/overflow flags) can be tested by the programmer. The descriptions of the flags follow.

Carry Flag (C): This flag is set by the carry from the highest order bit of the accumulator during an add instruction or a borrow generated during a subtraction instruction. Specific shift and rotate instructions also affect this bit.

**Zero Flag (Z):** This flag is set when a zero is loaded into the accumulator as a result of an operation. Otherwise it remains clear.

**Sign Flag (S):** This flag stores the state of bit 7 (the sign bit) in the accumulator after an arithmetic operation. This flag is intended to be used with signed numbers.

Parity/Overflow Flag (P/V): During logical operations this flag is set when the parity of the result is even and reset when it is odd. It represents overflow when signed two's complement arithmetic operations are performed. An overflow occurs when the resultant of a two's complement operation (in the accumulator) is out of range.

The two non-testable flag register bits used for BCD arithmetic are:

Half Carry (H): The flag indicates a BCD carry or borrow result from the least significant four bits of an operation; when using the DAA (Decimal Adjust Accumulator Instruction), it is used to correct the result of a previously packed decimal add or subtract.

Add/Subtract Flag (N): Since the algorithm for correcting BCD operations is different for addition or subtraction, this flag specifies what type of instruction was executed last in order that the DAA operation will be correct for either operation

#### INTERRUPTS

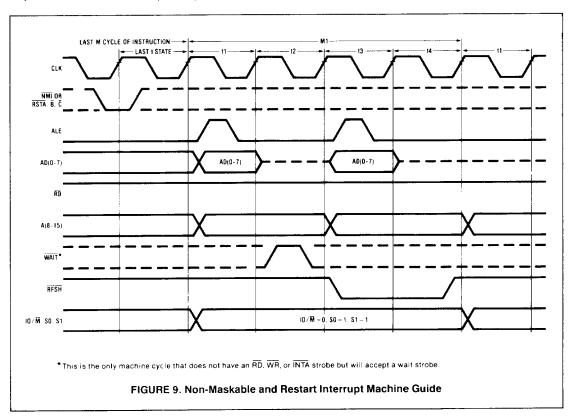

The MPU800 has five interrupt/restart inputs, four are maskable (RSTA, RSTB, RSTC, and INTR) and one is non-maskable (NMI). NMI, having the highest priority of all interrupts, is always serviced and cannot be disabled by the user. After recognizing an active input on NMI, the CPU stops before the next instruction, pushes the PC onto the stack, and jumps to address X'0066, where the user's interrupt service routine is located (i.e., restart to memory location X'0066). NMI is intended for interrupts requiring immediate attention, such as power-down, control panel, etc. RSTA, RSTB and RSTC are restart inputs, which, if enabled, execute a restart to memory location X'003C, X'0034, and X'002C, respectively. Note that the CPU response to the NMI and RST (A, B, C) request input is

basically identical. Unlike NMI, however, restart request inputs must be enabled.

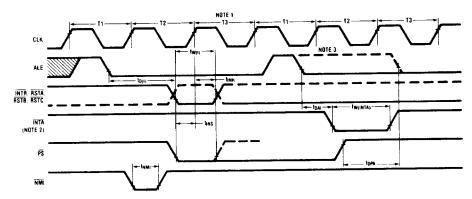

Figure 9 illustrates NMI and RST interrupt machine cycles. M1 cycle will be a dummy opcode fetch cycle followed by M2 and M3 which are stack push operations. The following instruction will then start from the interrupts restart location.

The MPU800 also provides one more general purpose interrupt request input, INTR. When enabled, the CPU responds to INTR in one of the three modes defined by instruction IM0, IM1, and IM2 for modes 0, 1 and 2, respectively. Following reset, the CPU automatically sets itself in mode).

Interrupt (INTR) Mode 0; Similar to INS8080A mode. The CPU responds to an interrupt request by providing an INTA (interrupt acknowledge) strobe, which can be used to gate an instruction from a peripheral onto the data bus. Two wait states are automatically inserted by the CPU during the first INTA cycle to allow the interrupting device (or its controller) ample time to gate the instruction and determine external priorities. (Figure 10). This can be any instruction from one to four bytes. The most popular instruction would be a one-byte call (restart instruction) or a three-byte call (CALL NN instruction). If it is a three-byte call, the CPU issues a total of three INTA strobes. The last two read NN (which do not include wait states).

Interrupt (INTR) Mode 1: Similar to the restart interrupts except the restart location is X'0038 (Figure 9).

Interrupt (INTR) Mode 2: With this mode, the programmer maintains a table that contains the 16-bit starting address of every interrupt service routine. This table may be located anywhere in memory. When the mode 2 interrupt is accepted (Figure 11), a 16-bit pointer must be formed to obtain the desired interrupt service routine starting address from the table. The upper 8 bits of this pointer are from the contents of the I register, which has been previously loaded with the desired value by the programmer. The lower 8 bits of the pointer are supplied by the interrupting device with the low-order bit forced to zero. The pointer is used to get two adjacent bytes from the interrupt service routine starting address table to complete the 16-bit service routine starting address. The first byte of each entry in the table is the least significant (low-order) portion of the address. The programmer must obviously fill this table with the desired addresses before any interrupts are to be accepted.

Note that this table can be changed at any time to allow peripherals to be serviced by different service routines. Once the interrupting device supplies the lower portion of the pointer, the CPU automatically pushes the program counter onto the stack, obtains the starting address from the table and does a jump to this address.

The interrupts have fixed priorities built into the MPU800 as:

| NMI          | (Highest Priority) |

|--------------|--------------------|

| RSTA<br>RSTB |                    |

| RSTC         |                    |

| INTR         | (Lowest Priority)  |

# **ENABLING INTERRUPTS**

NMI, being a non-maskable interrupt request, is executed as it occurs and can never be disabled.

The maskable interrupt inputs (RSTA, RSTB, RSTC, and INTR) are enabled under program control through the use of the interrupt control register and enable/disable interrupt instruction.

The appropriate interrupt control bits in 4-bit control register (IEA, IEB, IEC, and IEI) must be enabled in conjunction with IFF1 and IFF2, before the maskable INTR and RST Å, B, C can be accepted by the CPU.

The interrupt control register is an on-chip write only output port located at port address X'BB. It can only be written to by either the OUT (C), r or OUT (N), A instructions (for example OUTI instruction will not affect Interrupt Control Register). Its contents are:

| Bit | Name |         |        |          |      |

|-----|------|---------|--------|----------|------|

| 0   | ΙEΙ  | Interru | pt Ena | able for | INTR |

| 1   | IEC  | ,,      | ,,     | 13       | RSTC |

| 2   | IEB  | **      | **     | **       | RSTB |

| 3   | IEA  | ,,      | 11     | 1,1      | RSTA |

For example: In order to enable RSTB, CPU interrupts must be enabled and IEB must be set.

At reset, IEI bit is set and other mask bits, IEA, IEB, IEC are cleared. This maintains the software compatibility between MPU800 and INS8080A (or Z80A).

Execution of an IO block move instruction will not affect the state of the interrupt control bits. The only two instructions that will modify this write only register are OUT (C), r and OUT (N), A.

#### **POWER-SAVE FEATURE**

The MPU800 provides a unique power-save mode by the means of the PS pin. PS input is sampled at the last t state of the last M cycle of an instruction. After recognizing an active (low) level on PS, the MPU800 stops its internal clocks, thereby reducing its power dissipation to one half of operating power, yet maintaining all register values and internal control status. The MPU800 keeps its oscillator running, and makes the CLK signal available to the system. When in power-save the ALE strobe will be stopped high and the address lines [AD(0-7), A(8-15)] will indicate the next machine address. When PS is returned high, the opcode fetch (or M1 cycle) of the CPU begins in a normal manner. Note this M1 cycle could also be an interrupt acknowledge cycle if the MPU800 was interrupted simultaneously with PS. Figure 12 illustrates the power-save feature.

In the event BREQ is asserted (low) at the end of an instruction cycle and PS is active simultaneously, the following occurs:

- 1. The MPU800 will go into BACK cycle

- Upon completion of BACK cycle if PS is still active the CPU will go into power-save mode.

#### INSTRUCTION SET

In the following instruction set listing, the notation used is shown below.

- b: Used in instructions employing bit mode addressing to designate one bit in a register or memory location.

- cc: Designates condition codes used in conditional Jumps, Calls, and Return instructions; may be

NZ = Non Zero (Z Flag = 0)

Z = Zero (Z Flag = 1)

NC = Non Carry (C Flag = 0)

C = Carry (C Flag = 1)

PO = Parity Odd or No Overflow (P/V = 0)

PE = Parity Even or Overflow (P/V = 1)

P = Positive (S = 0)

M = Negative (S = 1)

- d: Used in instructions employing relative or indexed modes of addressing to designate 8-bit signed 2's complement displacement.

- kk: Subset of cc condition codes used in conjunction with conditional relative jumps; may be NZ, Z, NC or C.

- m1: Used in instructions employing register indirect or indexed modes of addressing; may be (HL), (IX + d) or (IY + d).

- m2: Used in instructions employing register indirect or direct modes of addressing; may be (BC), (DE), or (nn).

- n: Any 8-bit binary number.

- nn: Any 16-bit binary number.

- pp: Used in 16-bit arithmetic instructions employing register modes of addressing; may be BC, DE, SP, or register designated as destination operand.

- qq: Used in instructions employing register modes of addressing; may be BC, DE, HL, AF, IX, or IY.

- r: Used in instructions employing register mode of addressing; may be A, B, C, D, E, H, or L.

- rr: Used in instructions employing register mode of addressing; may be BC, DE, HL, SP, IX, or IY.

- ss: Used in instructions employing register mode of addressing; may be HL, IX, or IY.

- T: Used to restart instructions employing modified page zero addressing mode; may take on hex values of 0, 8, 10, 18, 20, 28, 30, or 38.

- X<sub>L</sub>: Subscript L indicates the high order byte of a 16-bit register.

- X<sub>H</sub>: Subscript H indicates the high-order byte of a 16-bit register.

- ( ): Parentheses indicate the contents are considered a pointer to a memory or I/O location.

#### 8-BIT LOADS

#### REGISTER TO REGISTER

| Mnemonic      | Description                                      | Operation            |

|---------------|--------------------------------------------------|----------------------|

| $LD r_a, r_s$ | Load register r <sub>d</sub> with r <sub>s</sub> | $r_d \leftarrow r_s$ |

| LD A.I        | Load ACC with register                           | A←I                  |

| LD I. A       | Load register I with ACC                         | I⊷A                  |

| LD A, r       | Load AČC with register<br>R                      | A←r                  |

| LD r, A       | Load register R with ACC                         | r⊷A                  |

| LD r, n       | Load register r with immediate data n            | r←n                  |

#### REGISTER TO MEMORY

| Mnemonic<br>LD m1, r | <b>Description</b> Load memory from | Operation<br>m1←r |

|----------------------|-------------------------------------|-------------------|

| LD, m2, A            | register r<br>Load memory from ACC  | m2←A              |

| LD m1, n             | Load memory with                    | m1←n              |

#### MEMORY TO REGISTER

| Mnemonic | Description                    | Operation |

|----------|--------------------------------|-----------|

| LD r, m1 | Load register r from           | r←m1      |

| LD A, m2 | memory<br>Load ACC from memory | A←m2      |

| 16-BIT LO   | ADS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  | NEG                         | Negate ACC (2's                                 | A0-A                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------------------------------|--------------------------------|

| REGISTER    | TO REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                  | CCF                         | complement) Complement carry flag               | CY←CY<br>CY←1                  |

| Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operation                                        | SCF                         | Set carry flag                                  | O1←1                           |