Now

Reference Community Design

TPS65023, TPS65023B

SLVS670L-JUNE 2006-REVISED MAY 2018

#### TPS65023x Power Management IC (PMIC) With 3 DC/DCs, 3 LDOs, I<sup>2</sup>C Interface and DVS

#### 1 Features

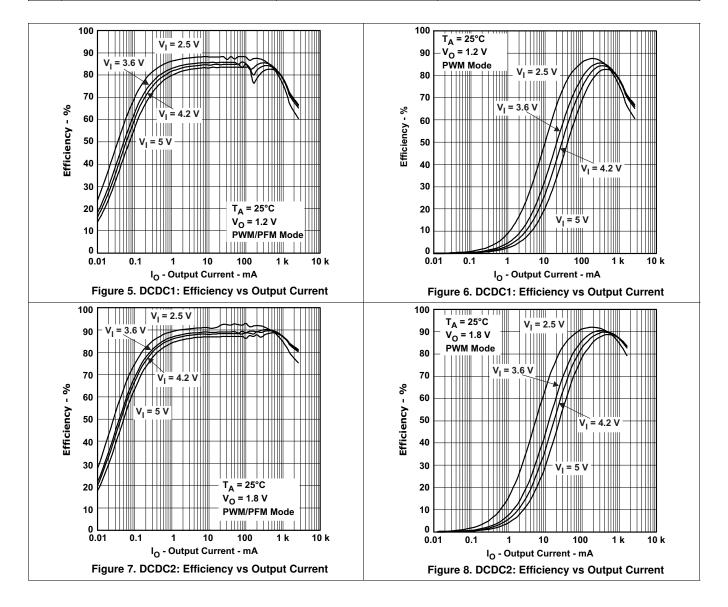

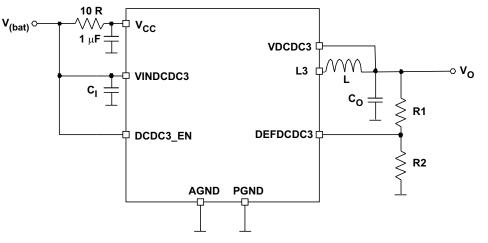

- 1.7-A, 90% Efficient Step-Down Converter for Processor Core (VDCDC1)

- 1.2-A, Up to 95% Efficient Step-Down Converter for System Voltage (VDCDC2)

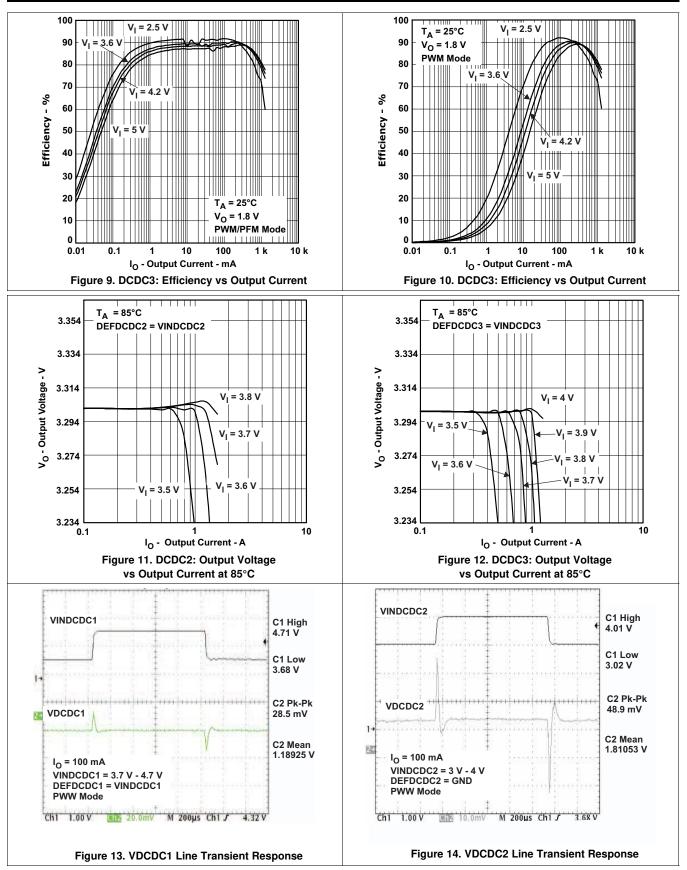

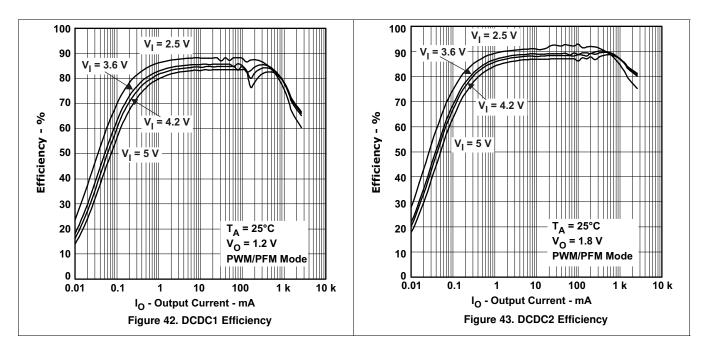

- 1.0-A, 92% Efficient Step-Down Converter for Memory Voltage (VDCDC3)

- 30-mA LDO and Switch for Real Time Clock (VRTC)

- 2 × 200-mA General-Purpose LDO

- Dynamic Voltage Management for Processor Core

- Preselectable LDO Voltage Using Two Digital Input Pins

- Externally Adjustable Reset Delay Time

- Battery Backup Functionality

- Separate Enable Pins for Inductive Converters

- I<sup>2</sup>C-Compatible Serial Interface

- $I^2C^{TM}$  Setup and Hold Timing:

- TPS65023: 300 ns

- TPS65023B: 100 ns

- 85-µA Quiescent Current

- Low Ripple PFM Mode

- **Thermal Shutdown Protection**

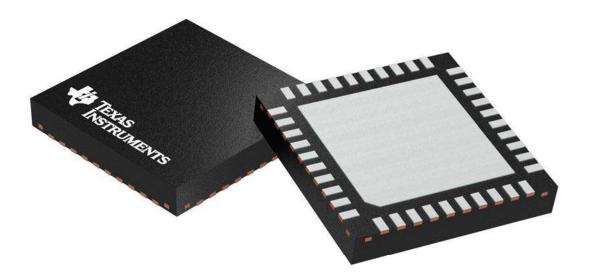

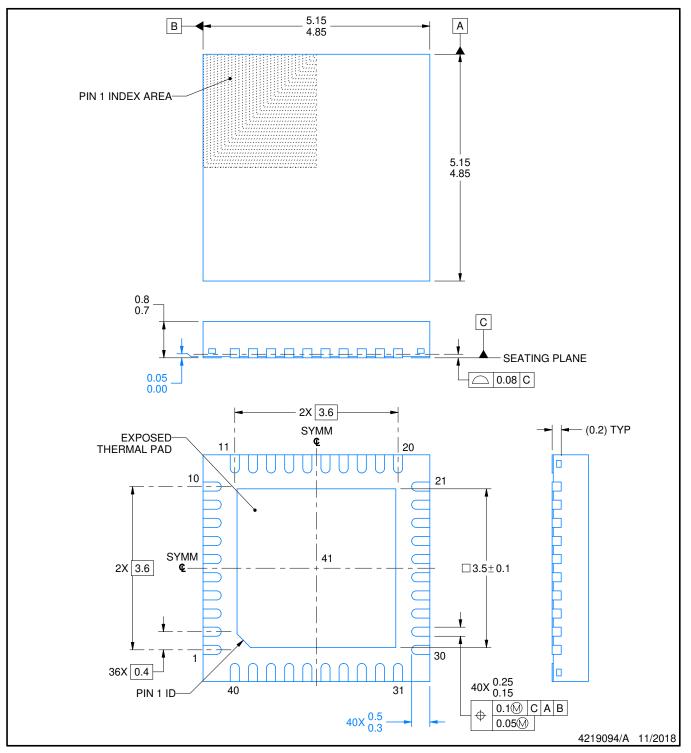

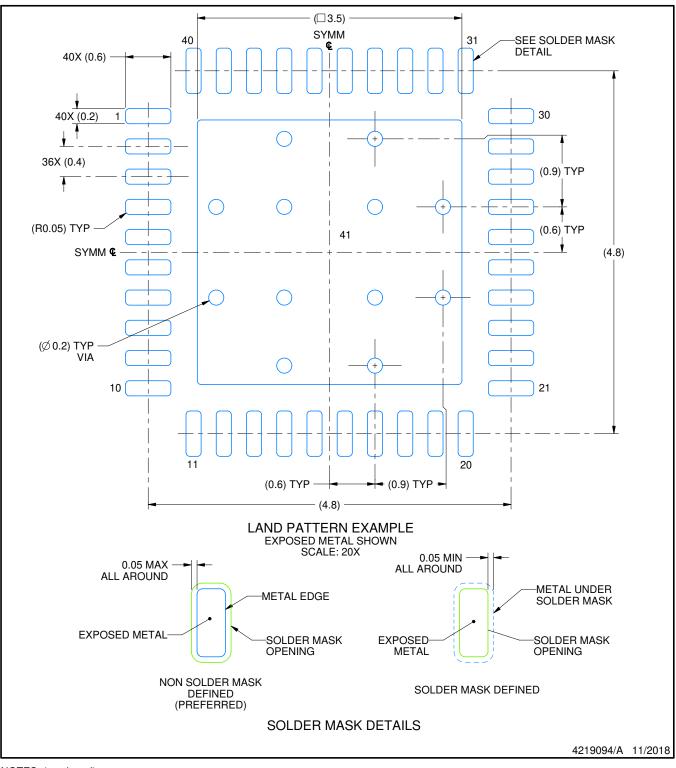

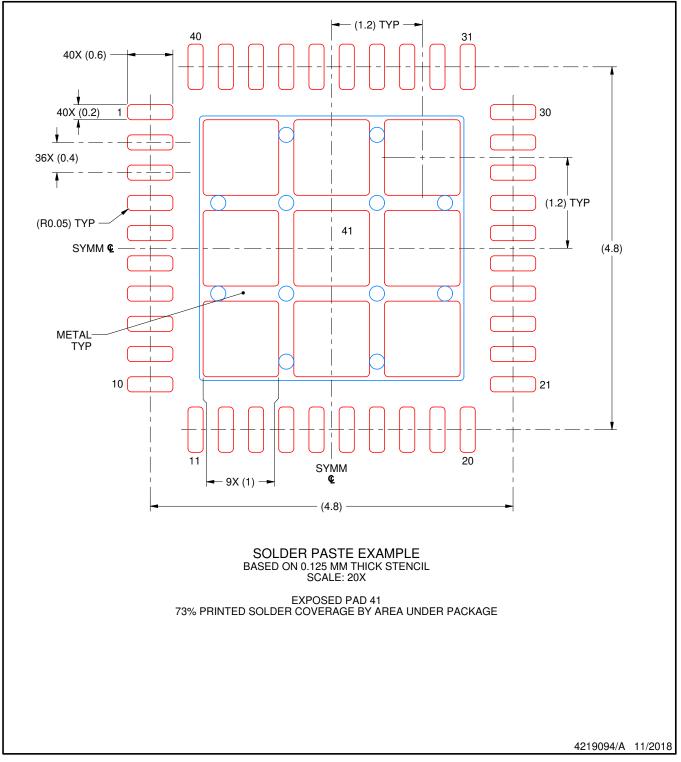

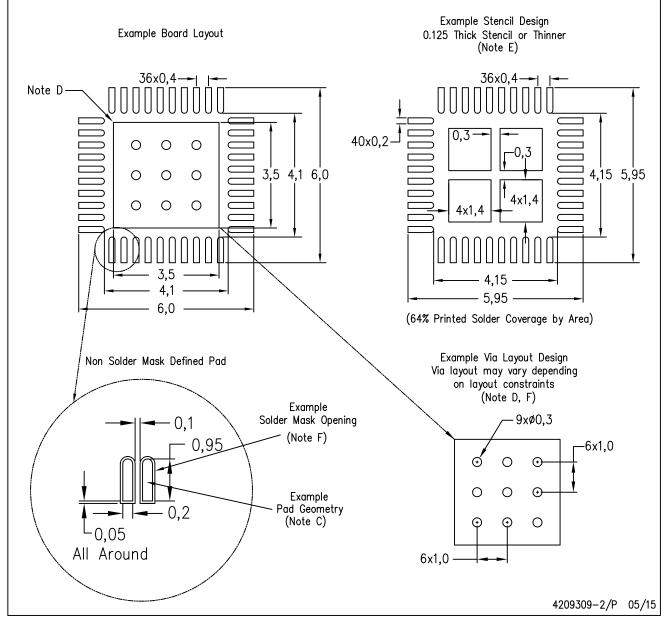

- 40-Pin, 5-mm × 5-mm WQFN Package

#### 2 Applications

- **Digital Media Players**

- Internet Audio Players

- **Digital Still Cameras**

- Smart Phones

- Supply DaVinci<sup>™</sup> DSP Family Solutions

#### 3 Description

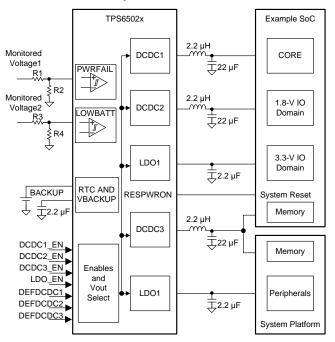

The TPS65023x device is an integrated power management IC for applications powered by one Li-Ion or Li-Polymer cell, which require multiple power rails. The TPS65023x provides three highly efficient, step-down converters targeted at providing the core voltage, peripheral, I/O, and memory rails in a processor-based system. The core converter allows for on-the-fly voltage changes through serial interface, allowing the system to implement dynamic power savings. All three step-down converters enter a low-power mode at light load for maximum efficiency across the widest possible range of load currents.

The TPS65023x also integrates two general-purpose 200-mA LDO voltage regulators, which are enabled with an external input pin. Each LDO operates with an input voltage range from 1.5 V to 6.5 V, thus allowing them to be supplied from one of the stepdown converters or directly from the battery. The default output voltage of the LDOs can be digitally set to 4 different voltage combinations using the DEFLDO1 and DEFLDO2 pins. The serial interface can be used for dynamic voltage scaling, masking interrupts, or for disabling or enabling and setting the LDO output voltages. The interface is compatible with both the fast and standard mode I<sup>2</sup>C specifications, allowing transfers at up to 400 kHz. The TPS65023x is available in a 40-pin WQFN package, and operates over a free-air temperature of -40°C to 85°C.

Support &

<u>A</u>2

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)        |

|-------------|-----------|------------------------|

| TPS65023    | WQFN (40) | <b>5 00 mm 5 00 mm</b> |

| TPS65023B   |           | 5.00 mm × 5.00 mm      |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

#### **Table of Contents**

| 1 | Fea  | tures 1                                                                      |

|---|------|------------------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                                  |

| 3 | Des  | cription 1                                                                   |

| 4 | Rev  | ision History 2                                                              |

| 5 | Pin  | Configuration and Functions 5                                                |

| 6 | Spe  | cifications7                                                                 |

|   | 6.1  | Absolute Maximum Ratings 7                                                   |

|   | 6.2  | ESD Ratings7                                                                 |

|   | 6.3  | Recommended Operating Conditions 7                                           |

|   | 6.4  | Thermal Information 8                                                        |

|   | 6.5  | Electrical Characteristics                                                   |

|   | 6.6  | Electrical Characteristics: Supply Pins VCC,<br>VINDCDC1, VINDCDC2, VINDCDC3 |

|   | 6.7  | Electrical Characteristics: Supply Pins VBACKUP,<br>VSYSIN, VRTC, VINLDO     |

|   | 6.8  | Electrical Characteristics: VDCDC1 Step-Down<br>Converter                    |

|   | 6.9  | Electrical Characteristics: VDCDC2 Step-Down<br>Converter                    |

|   | 6.10 | Electrical Characteristics: VDCDC3 Step-Down<br>Converter                    |

|   | 6.11 | I <sup>2</sup> C Timing Requirements for TPS65023B 13                        |

|   | 6.12 | 2 Typical Characteristics 16                                                 |

| 7 | Deta | ailed Description 21                                                         |

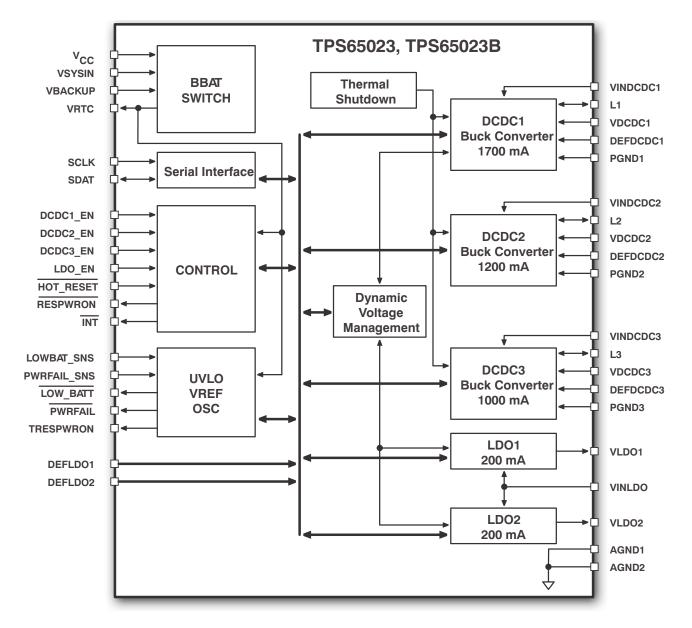

|    | 7.1  | Overview                                     | 21   |

|----|------|----------------------------------------------|------|

|    | 7.2  | Functional Block Diagram                     | 22   |

|    | 7.3  | Feature Description                          | 22   |

|    | 7.4  | Device Functional Modes                      | 27   |

|    | 7.5  | Programming                                  | 28   |

|    | 7.6  | Register Maps                                | 31   |

| 8  | App  | lication and Implementation                  | . 37 |

|    | 8.1  | Application Information                      |      |

|    | 8.2  | Typical Application                          | 39   |

| 9  | Pow  | er Supply Recommendations                    | . 44 |

|    | 9.1  | Requirements for Supply Voltages Below 3.0 V |      |

| 10 | Lave | out                                          | . 45 |

|    | 10.1 | Layout Guidelines                            |      |

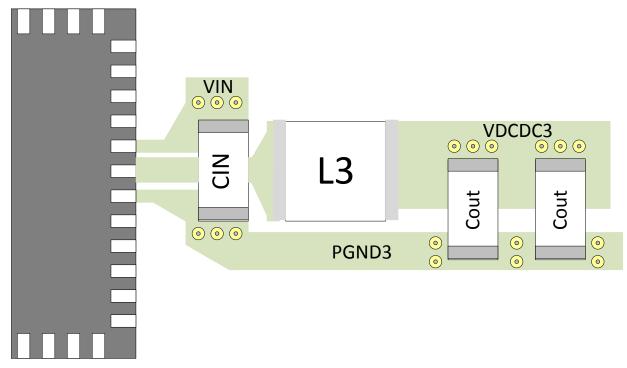

|    | 10.2 | Layout Example                               |      |

| 11 | Dev  | ice and Documentation Support                | . 46 |

|    | 11.1 |                                              |      |

|    | 11.2 |                                              |      |

|    | 11.3 |                                              |      |

|    | 11.4 | Community Resources                          | . 46 |

|    | 11.5 |                                              |      |

|    | 11.6 | Electrostatic Discharge Caution              | 47   |

|    | 11.7 |                                              |      |

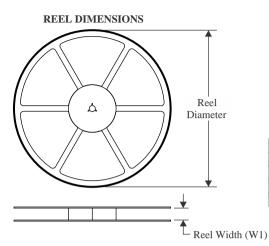

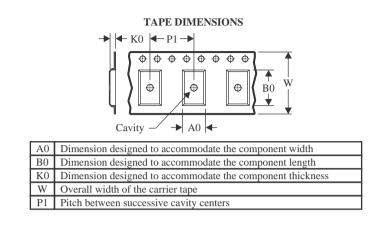

| 12 | Mec  | hanical, Packaging, and Orderable            |      |

|    |      | mation                                       | . 47 |

|    |      |                                              |      |

2

Submit Documentation Feedback

**4 Revision History** NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | nanges from Revision K (December 2015) to Revision L                                                                                                                                                                                                                                | Page |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed the title of the data sheet                                                                                                                                                                                                                                                 | 1    |

| • | Replaced references of TI PowerPAD IC package with thermal pad                                                                                                                                                                                                                      | 6    |

| • | Added the Device Support and Documentation Support sections                                                                                                                                                                                                                         | 46   |

| • | Changed the Electrostatic Discharge Caution statement                                                                                                                                                                                                                               | 46   |

| C | nanges from Revision J (September 2011) to Revision K                                                                                                                                                                                                                               | Page |

| • | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

| C | nanges from Revision I (July 2010) to Revision J                                                                                                                                                                                                                                    | Page |

| • | Added Thermal Information Table and deleted Dissipation Ratings Table                                                                                                                                                                                                               | 8    |

| C | nanges from Revision H (December 2009) to Revision I                                                                                                                                                                                                                                | Page |

| • | Added I <sup>2</sup> C Compatible Serial Interface to Features list                                                                                                                                                                                                                 | 1    |

| • | Added TPS65023B device specs                                                                                                                                                                                                                                                        | 1    |

| • | Added ordering info for TPS65023B device.                                                                                                                                                                                                                                           |      |

| • | Added specs for TPS65023B device                                                                                                                                                                                                                                                    | 8    |

NSTRUMENTS

Texas

TEXAS INSTRUMENTS

#### www.ti.com

| • | Changed "VBACKUP threshold" test condition typographical error from "VBACKUP falling" to "VBACKUP rising" | . 11 |

|---|-----------------------------------------------------------------------------------------------------------|------|

| • | Added specs for TPS65023B device                                                                          | 13   |

| • | Added Differences table for TPS65023 and TPS65023B devices                                                | 39   |

#### Changes from Revision G (October 2008) to Revision H

#### Page

Page

Page

Page

Page

| • | Changed I <sub>O(DCDC1)</sub> MAX from: 1500 mA to: 1700 mA                                                                       | 7  |

|---|-----------------------------------------------------------------------------------------------------------------------------------|----|

| • | Added High level input voltage for the SDAT pin                                                                                   | 8  |

| • | Changed I <sub>O</sub> from:1500 mA MIN to 1700 mA                                                                                | 11 |

| • | Changed I <sub>O</sub> maximum from:1.5 A to: 1.7 A for VDCDC1 fixed and adjustable output voltage test condition specs           | 11 |

| • | Changed I <sub>O</sub> maximum from: 1500 mA to: 1700 mA for VDCDC1 Load Regulation test condition                                | 11 |

| • | Changed VDCDC1 "soft-start ramp time" spec to: "t <sub>Start</sub> and t <sub>Ramp</sub> " specifications with MIN TYP MAX values | 11 |

| • | Changed VDCDC2 "soft-start ramp time" spec To: "t <sub>Start</sub> and t <sub>Ramp</sub> " specifications with MIN TYP MAX values | 12 |

| • | Changed VDCDC3 "soft-start ramp time" spec To: "t <sub>Start</sub> and t <sub>Ramp</sub> " specifications with MIN TYP MAX values | 13 |

| • | Changed FBD graphic to show 1700 mA for DCDC1 Buck Converter                                                                      | 22 |

| • | Changed text string from: "1.2 V or 1.8 V" to: "1.2 V to 1.6 V" in the STEP-DOWN CONVERTERS., VDCDC1 description.                 | 24 |

| • | Changed graphic entity to the one used in the Application Note SLVA273                                                            | 39 |

|   |                                                                                                                                   |    |

#### Changes from Revision F (July 2007) to Revision G

| • ( | Changed the Interrupt Management and the INT Pin section |

|-----|----------------------------------------------------------|

|-----|----------------------------------------------------------|

#### Changes from Revision E (January 2007) to Revision F

| • | Changed text string from: "If it is tied to VCC, the default | is 2.5 V" To: "If it is tied to VCC, the default is 3.3 V" 24   |

|---|--------------------------------------------------------------|-----------------------------------------------------------------|

| - |                                                              | 13 2.5  V 10. If it is tied to $1000$ , the default is $0.5  V$ |

#### Changes from Revision D (December 2006) to Revision E

| • | Changed LDO1 output voltage range from: 3.3 to: 3.3                                                             | . 9 |

|---|-----------------------------------------------------------------------------------------------------------------|-----|

| • | Changed text string from: "VDCDC2 converter defaults to 1.8 V or 2.5 V" to: "VDCDC2 converter defaults to 1.8 V |     |

|   | or 3.3 V"                                                                                                       | 24  |

# Changes from Revision C (October 2006) to Revision D Page • Changed Typical Configuration for Ti DaVinci Processors 39

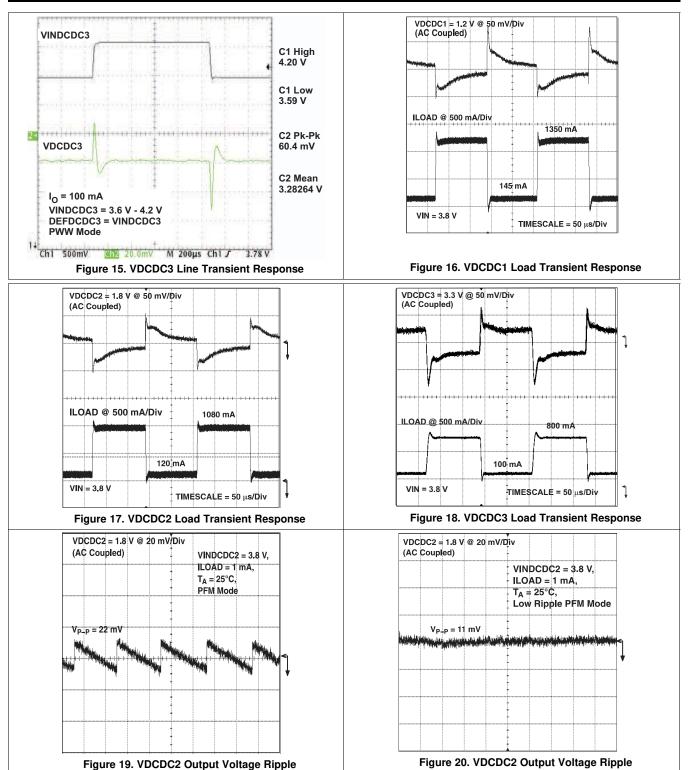

# Changes from Revision B (June 2006) to Revision C Page • Changed from: AD Coupled to: AD Coupled - Figure 16 17 • Changed from: AD Coupled to: AD Coupled - Figure 17 18

### Changes from Revision A (June 2006) to Revision B

| • | Changed from: 1.5A and 97% Efficient Step-Down to: 1.7A and 90% Efficient Step-Down | . 1 |

|---|-------------------------------------------------------------------------------------|-----|

| • | Changed from: 6 mm × 6 mm QFN Package to: 5 mm × 5 mm QFN Package                   | . 1 |

| • | Changed from: RHA package to: RSB package                                           | 1   |

| • | Changed from: <sub>O(DCDC2)</sub> to: I <sub>O(DCDC1)</sub>                         | 7   |

| • | Changed Forward current limit - removed TBD and added values                        | 11  |

|   |                                                                                     |     |

#### TEXAS INSTRUMENTS

#### TPS65023, TPS65023B

SLVS670L-JUNE 2006-REVISED MAY 2018

#### www.ti.com

| • | Changed Fixed output voltage - removed TBD and added values                                                       | 11 |

|---|-------------------------------------------------------------------------------------------------------------------|----|

| • | Changed Fixed output voltage - removed TBD and added values                                                       | 12 |

| • | Added VINDCDC3 = 3.6 V to Maximum output current                                                                  | 12 |

| • | Changed Fixed output voltage - removed TBD and added values                                                       | 13 |

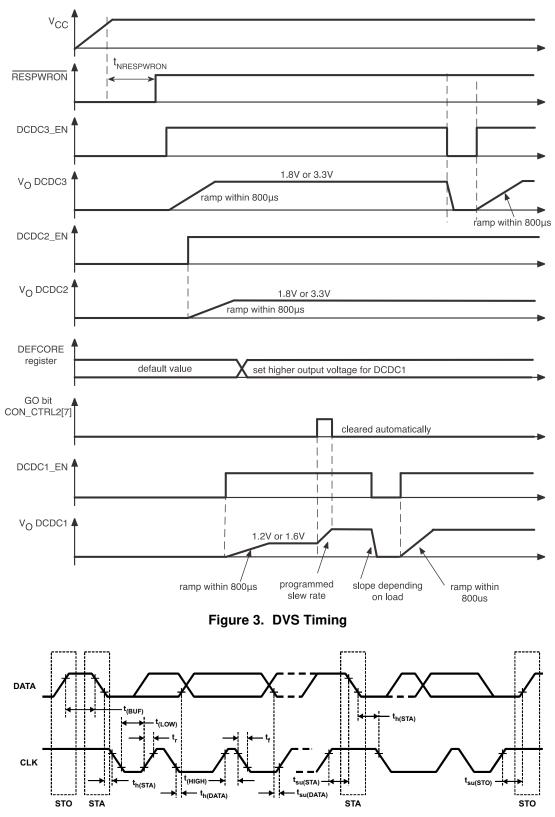

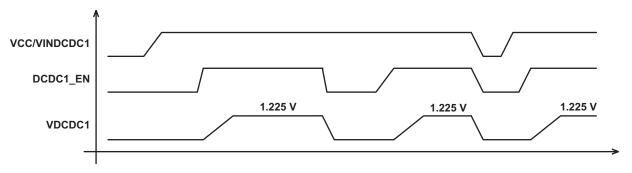

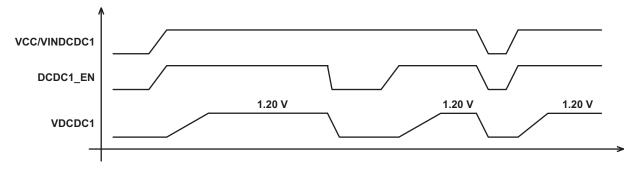

| • | Changed Figure 3 (DVS Timing)                                                                                     | 15 |

| • | Changed Figure 11 (Graph - DCDC2: OUTPUT VOLTAGE)                                                                 | 17 |

| • | Added Figure 12 (Graph - DCDC3: OUTPUT VOLTAGE )                                                                  | 17 |

| • | Changed Figure 20 (Graph - VDCDC2 OUTPUT VOLTAGE RIPPLE)                                                          | 18 |

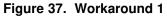

| • | Added Reset Condition of DCDC1 Information                                                                        | 37 |

| • | Changed Typical Configuration for Ti DaVinci Processors                                                           | 39 |

| • | Changed from: TPS65023 typically use a 3.3 µH output inductor to: TPS65023 typically use a 2.2 µH output inductor | 40 |

| • | Changed from: VDCDC3 to: VDCDC1                                                                                   | 41 |

| • | Changed from: VDEFDCDC3 to: DEFDCDC1                                                                              | 41 |

| • | Changed from: 2.5 V to 3.3 V (Table 20)                                                                           | 41 |

#### Changes from Original (May 2006) to Revision A

#### Page

| • | Changed Electrical Characteristics: VDCDC1 Step-Down Converter                  | 11 |

|---|---------------------------------------------------------------------------------|----|

| • | Changed Electrical Characteristics: VDCDC3 Step-Down Converter                  | 12 |

| • | Changed CON_CTRL Register Address - Column B0 default value changed from 1 to 0 | 33 |

| • | Changed VDCDC# to VDCDC1                                                        | 35 |

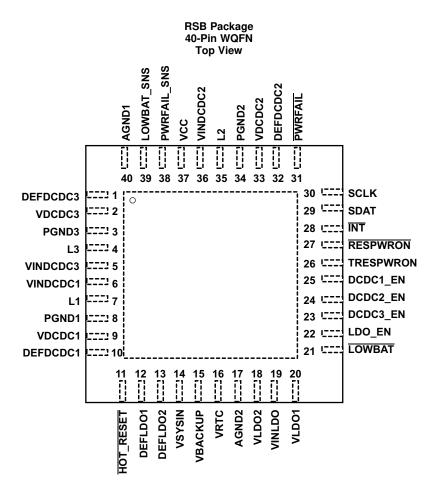

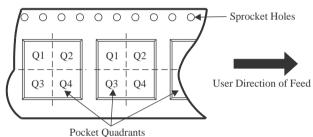

#### 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN           |                            | I/O | DECODIDION                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|---------------|----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| NAME          | NO.                        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| SWITCHING REG | WITCHING REGULATOR SECTION |     |                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| AGND1         | 40                         | —   | Analog ground. All analog ground pins are connected internally on the chip.                                                                                                                                                                    |  |  |  |  |  |  |  |

| AGND2         | 17                         | —   | Analog ground. All analog ground pins are connected internally on the chip.                                                                                                                                                                    |  |  |  |  |  |  |  |

| DCDC1_EN      | 25                         | I   | VDCDC1 enable pin. A logic high enables the regulator, a logic low disables the regulator.                                                                                                                                                     |  |  |  |  |  |  |  |

| DCDC2_EN      | 24                         | I   | VDCDC2 enable pin. A logic high enables the regulator, a logic low disables the regulator.                                                                                                                                                     |  |  |  |  |  |  |  |

| DCDC3_EN      | 23                         | I   | VDCDC3 enable pin. A logic high enables the regulator, a logic low disables the regulator.                                                                                                                                                     |  |  |  |  |  |  |  |

| DEFDCDC1      | 10                         | I   | Input signal indicating default VDCDC1 voltage, $0 = 1.2$ V, $1 = 1.6$ V DEFDCDC1 can also be connected to a resistor divider between VDCDC1 and GND, if the output voltage of the DCDC1 converter is set in a range from 0.6 V to VINDCDC1 V. |  |  |  |  |  |  |  |

| DEFDCDC2      | 32                         | I   | Input signal indicating default VDCDC2 voltage, $0 = 1.8$ V, $1 = 3.3$ V DEFDCDC2 can also be connected to a resistor divider between VDCDC2 and GND, if the output voltage of the DCDC2 converter is set in a range from 0.6 V to VINDCDC2 V. |  |  |  |  |  |  |  |

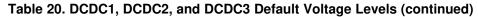

| DEFDCDC3      | 1                          | I   | Input signal indicating default VDCDC3 voltage, $0 = 1.8$ V, $1 = 3.3$ V DEFDCDC3 can also be connected to a resistor divider between VDCDC3 and GND, if the output voltage of the DCDC3 converter is set in a range from 0.6 V to VINDCDC3 V. |  |  |  |  |  |  |  |

| L1            | 7                          | —   | Switch pin of VDCDC1 converter. The VDCDC1 inductor is connected here.                                                                                                                                                                         |  |  |  |  |  |  |  |

| L2            | 35                         | _   | Switch pin of VDCDC2 converter. The VDCDC2 inductor is connected here.                                                                                                                                                                         |  |  |  |  |  |  |  |

| L3            | 4                          | _   | Switch pin of VDCDC3 converter. The VDCDC3 inductor is connected here.                                                                                                                                                                         |  |  |  |  |  |  |  |

| PGND1         | 8                          | —   | Power ground for VDCDC1 converter                                                                                                                                                                                                              |  |  |  |  |  |  |  |

**TPS65023, TPS65023B** SLVS670L – JUNE 2006 – REVISED MAY 2018

www.ti.com

NSTRUMENTS

Texas

#### Pin Functions (continued)

| PIN           |         |     |                                                                                                                                                                                                                               |

|---------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.     | I/O | DESCRIPTION                                                                                                                                                                                                                   |

| PGND2         | 34      | -   | Power ground for VDCDC2 converter                                                                                                                                                                                             |

| PGND3         | 3       | _   | Power ground for VDCDC3 converter                                                                                                                                                                                             |

| VCC           | 37      | I   | Power supply for digital and analog circuitry of VDCDC1, VDCDC2, and VDCDC3 DC-DC converters. VCC must be connected to the same voltage supply as VINDCDC3, VINDCDC1, and VINDCDC2. VCC also supplies serial interface block. |

| VDCDC1        | 9       | Ι   | VDCDC1 feedback voltage sense input. Connect directly to VDCDC1                                                                                                                                                               |

| VDCDC2        | 33      | Ι   | VDCDC2 feedback voltage sense input. Connect directly to VDCDC2                                                                                                                                                               |

| VDCDC3        | 2       | I   | VDCDC3 feedback voltage sense input. Connect directly to VDCDC3                                                                                                                                                               |

| VINDCDC1      | 6       | I   | Input voltage for VDCDC1 step-down converter. VINDCDC1 must be connected to the same voltage supply as VINDCDC2, VINDCDC3, and VCC.                                                                                           |

| VINDCDC2      | 36      | I   | Input voltage for VDCDC2 step-down converter. VINDCDC2 must be connected to the same voltage supply as VINDCDC1, VINDCDC3, and VCC.                                                                                           |

| VINDCDC3      | 5       | I   | Input voltage for VDCDC3 step-down converter. VINDCDC3 must be connected to the same voltage supply as VINDCDC1, VINDCDC2, and VCC.                                                                                           |

| Thermal Pad   | _       | _   | Connect the power pad to analog ground                                                                                                                                                                                        |

| LDO REGULATO  | R SECTI | ON  |                                                                                                                                                                                                                               |

| DEFLD01       | 12      | Ι   | Digital input. DEFLD01 sets the default output voltage of LDO1 and LDO2.                                                                                                                                                      |

| DEFLD02       | 13      | I   | Digital input. DEFLD02 sets the default output voltage of LDO1 and LDO2.                                                                                                                                                      |

| LDO_EN        | 22      | Ι   | Enable input for LDO1 and LDO2. A logic high enables the LDOs and a logic low disables the LDOs.                                                                                                                              |

| VBACKUP       | 15      | Ι   | Connect the backup battery to this input pin                                                                                                                                                                                  |

| VINLDO        | 19      | Ι   | Input voltage for LDO1 and LDO2                                                                                                                                                                                               |

| VLDO1         | 20      | 0   | Output voltage of LDO1                                                                                                                                                                                                        |

| VLDO2         | 18      | 0   | Output voltage of LDO2                                                                                                                                                                                                        |

| VRTC          | 16      | 0   | Output voltage of the LDO and switch for the real time clock                                                                                                                                                                  |

| VSYSIN        | 14      | Ι   | Input of system voltage for VRTC switch                                                                                                                                                                                       |

| CONTROL AND I | C SECT  | ION |                                                                                                                                                                                                                               |

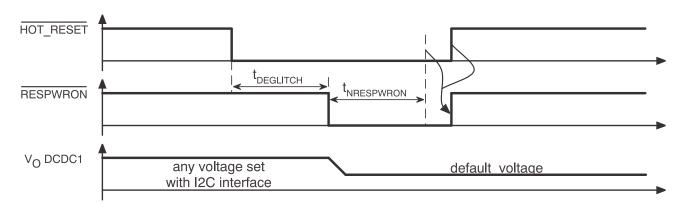

| HOT_RESET     | 11      | Ι   | Push button input that reboots or wakes up the processor through the RESPWRON output pin.                                                                                                                                     |

| INT           | 28      | 0   | Open-drain output                                                                                                                                                                                                             |

| LOW_BAT       | 21      | 0   | Open-drain output of LOW_BAT comparator                                                                                                                                                                                       |

| LOWBAT_SNS    | 39      | I   | Input for the comparator driving the LOW_BAT output.                                                                                                                                                                          |

| PWRFAIL       | 31      | 0   | Open-drain output. Active low when PWRFAIL comparator indicates low VBAT condition.                                                                                                                                           |

| PWRFAIL_SNS   | 38      | Ι   | Input for the comparator driving the PWRFAIL output                                                                                                                                                                           |

| RESPWRON      | 27      | 0   | Open-drain system reset output                                                                                                                                                                                                |

| SCLK          | 30      | I   | Serial interface clock line                                                                                                                                                                                                   |

| SDAT          | 29      | I/O | Serial interface data and address                                                                                                                                                                                             |

| TRESPWRON     | 26      | I   | Connect the timing capacitor to TRESPWRON to set the reset delay time: 1 nF $\rightarrow$ 100 ms                                                                                                                              |

|               |         | *   |                                                                                                                                                                                                                               |

Copyright © 2006–2018, Texas Instruments Incorporated

#### Specifications 6

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                          | MIN        | MAX           | UNIT |

|------------------|--------------------------------------------------------------------------|------------|---------------|------|

| VI               | Input voltage on all pins except AGND and PGND pins with respect to AGND | -0.3       | 7             | V    |

|                  | Current at VINDCDC1, L1, PGND1, VINDCDC2, L2, PGND2, VINDCDC3, L3, PGND3 |            | 2000          | mA   |

|                  | Peak current at all other pins                                           |            | 1000          | mA   |

|                  | Continuous total power dissipation                                       | See Therma | I Information |      |

| T <sub>A</sub>   | Operating free-air temperature                                           | -40        | 85            | °C   |

| TJ               | Maximum junction temperature                                             |            | 125           | °C   |

| T <sub>stg</sub> | Storage temperature                                                      | -65        | 150           | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                                            |  |                                                                                | VALUE | UNIT |

|--------------------------------------------|--|--------------------------------------------------------------------------------|-------|------|

| V                                          |  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge |  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. (1)

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                                                                        | MIN | NOM | MAX       | UNIT |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|------|

| V <sub>CC</sub>         | Input voltage step-down converters<br>(VINDCDC1, VINDCDC2, VINDCDC3); pins need to be tied to the same<br>voltage rail | 2.5 |     | 6         | V    |

|                         | Output voltage for VDCDC1 step-down converter <sup>(1)</sup>                                                           | 0.6 |     | VINDCDC1  |      |

| Vo                      | Output voltage for VDCDC2 step-down converter <sup>(1)</sup>                                                           | 0.6 |     | VINDCDC2  | V    |

|                         | Output voltage for VDCDC3 step-down converter <sup>(1)</sup>                                                           | 0.6 |     | VINDCDC3  |      |

| VI                      | Input voltage for LDOs (VINLDO1, VINLDO2)                                                                              | 1.5 |     | 6.5       | V    |

| Vo                      | Output voltage for LDOs (VLDO1, VLDO2)                                                                                 | 1   |     | VINLDO1-2 | V    |

| I <sub>O(DCDC1)</sub>   | Output current at L1                                                                                                   |     |     | 1700      | mA   |

|                         | Inductor at L1 <sup>(2)</sup>                                                                                          | 1.5 | 2.2 |           | μH   |

| CI(DCDC1)               | Input capacitor at VINDCDC1 <sup>(2)</sup>                                                                             | 10  |     |           | μF   |

| C <sub>O(DCDC1)</sub>   | Output capacitor at VDCDC1 (2)                                                                                         | 10  | 22  |           | μF   |

| I <sub>O(DCDC2)</sub>   | Output current at L2                                                                                                   |     |     | 1200      | mA   |

|                         | Inductor at L2 <sup>(2)</sup>                                                                                          | 1.5 | 2.2 |           | μH   |

| C <sub>I(DCDC2)</sub>   | Input capacitor at VINDCDC2 <sup>(2)</sup>                                                                             | 10  |     |           | μF   |

| C <sub>O(DCDC2)</sub>   | Output capacitor at VDCDC2 (2)                                                                                         | 10  | 22  |           | μF   |

| I <sub>O(DCDC3)</sub>   | Output current at L3                                                                                                   |     |     | 1000      | mA   |

|                         | Inductor at L3 <sup>(2)</sup>                                                                                          | 1.5 | 2.2 |           | μH   |

| C <sub>I(DCDC3)</sub>   | Input capacitor at VINDCDC3 <sup>(2)</sup>                                                                             | 10  |     |           | μF   |

| C <sub>O(DCDC3)</sub>   | Output capacitor at VDCDC3 (2)                                                                                         | 10  | 22  |           | μF   |

| C <sub>I(VCC)</sub>     | Input capacitor at VCC (2)                                                                                             | 1   |     |           | μF   |

| C <sub>i(VINLDO)</sub>  | Input capacitor at VINLDO (2)                                                                                          | 1   |     |           | μF   |

| C <sub>O(VLDO1-2)</sub> | Output capacitor at VLDO1, VLDO2 (2)                                                                                   | 2.2 |     |           | μF   |

When using an external resistor divider at DEFDCDC3, DEFDCDC2, and DEFDCDC1 (1)See Application Information section for more information.

Copyright © 2006–2018, Texas Instruments Incorporated

(2)

#### **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                               | MIN | NOM | MAX | UNIT |

|-------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>O(VLDO1-2)</sub> | Output current at VLDO1, VLDO2                                                |     |     | 200 | mA   |

| C <sub>O(VRTC)</sub>    | Output capacitor at VRTC <sup>(2)</sup>                                       | 4.7 |     |     | μF   |

| T <sub>A</sub>          | Operating ambient temperature                                                 | -40 |     | 85  | °C   |

| TJ                      | Operating junction temperature                                                | -40 |     | 125 | °C   |

|                         | Resistor from VINDCDC3, VINDCDC2, VINDCDC1 to VCC used for filtering $^{(3)}$ |     | 1   | 10  | Ω    |

(3) Up to 3 mA can flow into V<sub>CC</sub> when all 3 converters are running in PWM. This resistor causes the UVLO threshold to be shifted accordingly.

#### 6.4 Thermal Information

|                       |                                              | TPS65023x  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSB (WQFN) | UNIT |

|                       |                                              | 40 PINS    |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 32.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 15.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 13.6       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.1        | °C/W |

| ΨJB                   | Junction-to-board characterization parameter | 5.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.1        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.5 Electrical Characteristics

$VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V, T_A = -40^{\circ}C \text{ to } 85^{\circ}C \text{ (unless otherwise noted)}$

|                       | PARAMETER                                      | TEST CONDITIONS                                                                             | MIN  | <b>TYP</b> <sup>(1)</sup> | MAX             | UNIT |

|-----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|------|---------------------------|-----------------|------|

| CONTROL SIG           | NALS: SCLK, SDAT (INPUT) FOR TPS65023          |                                                                                             |      |                           |                 |      |

| V <sub>IH</sub>       | High level input voltage (except the SDAT pin) | Resistor pullup at SCLK = 4.7 k $\Omega$ , pulled to VRTC                                   | 1.3  |                           | V <sub>cc</sub> | V    |

| V <sub>IH</sub>       | High level input voltage for the SDAT pin      | Resistor pullup at SDAT = 4.7 k $\Omega$ , pulled to VRTC                                   | 1.45 |                           | $V_{\text{CC}}$ | V    |

| VIL                   | Low level input voltage                        | Resistor pullup at SCLK and SDAT = 4.7 k $\Omega$ , pulled to VRTC                          | 0    |                           | 0.4             | V    |

| I <sub>H</sub>        | Input bias current                             |                                                                                             |      | 0.01                      | 0.1             | μA   |

| CONTROL SIG           | NALS: SCLK, SDAT (INPUT) FOR TPS65023B         |                                                                                             |      |                           |                 |      |

| VIH                   | High level input voltage for the SCLK pin      | Rpullup at SCLK = 4.7 k\Omega, pulled to VRTC; For V <sub>CC</sub> = 2.5 V to 5.25 V        | 1.4  |                           | V <sub>cc</sub> | V    |

| V <sub>IH</sub>       | High level input voltage for the SDAT pin      | Rpullup at SDAT = 4.7 k $\Omega$ , pulled to VRTC;<br>For V <sub>CC</sub> = 2.5 V to 5.25 V | 1.69 |                           | V <sub>CC</sub> | V    |

| V <sub>IH</sub>       | High level input voltage for the SDAT pin      | Rpullup at SDAT = 4.7 k\Omega, pulled to VRTC; For V <sub>CC</sub> = 2.5 V to 4.5 V         | 1.55 |                           | V <sub>CC</sub> | V    |

| V <sub>IL</sub>       | Low level input voltage                        | Rpullup at SCLK and SDAT = 4.7 k $\Omega$ , pulled to VRTC                                  | 0    |                           | 0.35            | V    |

| I <sub>H</sub>        | Input bias current                             |                                                                                             |      | 0.01                      | 0.1             | μA   |

| CONTROL SIG           | NALS: HOT_RESET, DCDC1_EN, DCDC2_EN, DCE       | DC3_EN, LDO_EN, DEFLDO1, DEFLDO2                                                            |      |                           |                 |      |

| V <sub>IH</sub>       | High-level input voltage                       |                                                                                             | 1.3  |                           | $V_{CC}$        | V    |

| V <sub>IL</sub>       | Low-level input voltage                        |                                                                                             | 0    |                           | 0.4             | V    |

| I <sub>IB</sub>       | Input bias current                             |                                                                                             |      | 0.01                      | 0.1             | μA   |

| t <sub>deglitch</sub> | Deglitch time at HOT_RESET                     |                                                                                             | 25   | 30                        | 35              | ms   |

(1) Typical values are at  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### **Electrical Characteristics (continued)**

VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V,  $T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                          | PARAMETER                                               | TEST CONDITIONS                                                               | MIN   | TYP <sup>(1)</sup> | MAX   | UNIT     |

|--------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|-------|--------------------|-------|----------|

| CONTROL SIGNALS: L       | OWBAT, PWRFAIL, RESPWRON, INT, SDA                      | AT (OUTPUT)                                                                   |       |                    |       |          |

| V <sub>OH</sub>          | High-level output voltage                               |                                                                               |       |                    | 6     | V        |

| V <sub>OL</sub>          | Low-level output voltage                                | I <sub>IL</sub> = 5 mA                                                        | 0     |                    | 0.3   | V        |

|                          | Duration of low pulse at RESPWRON                       | External capacitor 1 nF                                                       |       | 100                |       | ms       |

| ICONST                   | Internal charge / discharge current on pin TRESPWRON    | Used for generating RESPWRON delay                                            | 1.7   | 2                  | 2.3   | μA       |

| TRESPWRON_LOWTH          | Internal lower comparator threshold on<br>pin TRESPWRON | Used for generating RESPWRON delay                                            | 0.225 | 0.25               | 0.275 | V        |

| TRESPWRON_UPTH           | Internal upper comparator threshold on<br>pin TRESPWRON | Used for generating RESPWRON delay                                            | 0.97  | 1                  | 1.103 | V        |

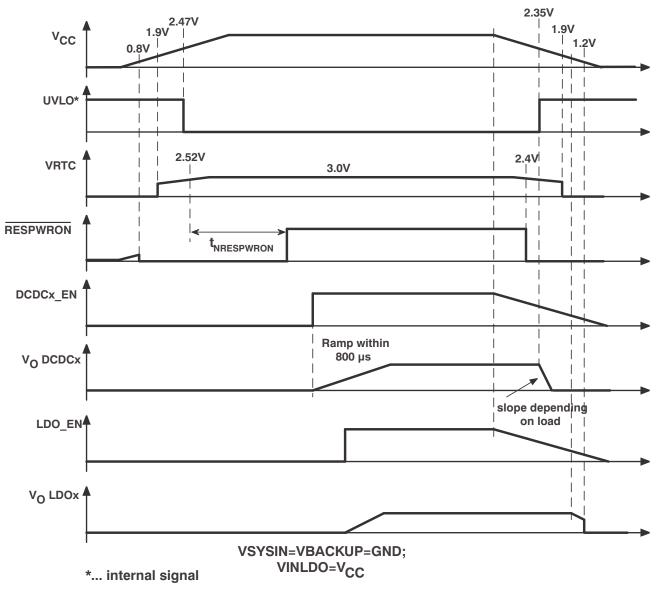

|                          | Resetpwron threshold                                    | VRTC falling                                                                  | -3%   | 2.4                | 3%    | V        |

|                          | Resetpwron threshold                                    | VRTC rising                                                                   | -3%   | 2.52               | 3%    | V        |

| I <sub>LK</sub>          | Leakage current                                         | Output inactive high                                                          |       |                    | 0.1   | μA       |

|                          | W DROPOUT REGULATORS                                    |                                                                               |       |                    | I     |          |

| VI                       | Input voltage range for LDO1, 2                         |                                                                               | 1.5   |                    | 6.5   | V        |

| V <sub>O(LD01)</sub>     | LDO1 output voltage range                               |                                                                               | 1     |                    | 3.15  | V        |

| V <sub>O(LDO2)</sub>     | LDO2 output voltage range                               |                                                                               | 1     |                    | 3.3   | V        |

| 0(2002)                  | Maximum output current for LDO1,                        | V <sub>I</sub> = 1.8 V, V <sub>O</sub> = 1.3 V                                | 200   |                    |       |          |

| lo                       | LDO2                                                    | $V_{l} = 1.5 \text{ V}, V_{O} = 1.3 \text{ V}$                                |       | 120                |       | mA       |

| I <sub>(SC)</sub>        | LDO1 and LDO2 short-circuit current limit               | $V_{(LDO1)} = GND, V_{(LDO2)} = GND$                                          |       |                    | 400   | mA       |

|                          |                                                         | I <sub>O</sub> = 50 mA, VINLDO = 1.8 V                                        |       |                    | 120   |          |

|                          | Minimum voltage drop at LDO1, LDO2                      | $I_0 = 50 \text{ mA}, \text{VINLDO} = 1.5 \text{ V}$                          |       | 65                 | 150   | mV       |

|                          |                                                         | $I_0 = 200 \text{ mA}, \text{VINLDO} = 1.8 \text{ V}$                         |       |                    | 300   |          |

|                          | Output voltage accuracy for LDO1, LDO2                  | $I_{\rm O} = 10 \text{ mA}$                                                   | -2%   |                    | 1%    |          |

|                          | Line regulation for LDO1, LDO2                          | VINLDO1, 2 = VLDO1,2 + 0.5 V<br>(min. 2.5 V) to 6.5 V, I <sub>O</sub> = 10 mA | -1%   |                    | 1%    |          |

|                          | Load regulation for LDO1, LDO2                          | $I_{O} = 0 \text{ mA to } 50 \text{ mA}$                                      | -1%   |                    | 1%    |          |

|                          | Regulation time for LDO1, LDO2                          | Load change from 10% to 90%                                                   |       | 10                 |       | μS       |

| ANALOGIC SIGNALS D       | DEFDCDC1, DEFDCDC2, DEFDCDC3                            | -                                                                             |       |                    |       |          |

| V <sub>IH</sub>          | High-level input voltage                                |                                                                               | 1.3   |                    | VCC   | V        |

| V <sub>IL</sub>          | Low-level input voltage                                 |                                                                               | 0     |                    | 0.1   | V        |

|                          | Input bias current                                      |                                                                               |       | 0.001              | 0.05  | μA       |

| THERMAL SHUTDOWN         | · · · · · · · · · · · · · · · · · · ·                   |                                                                               |       |                    |       |          |

| T <sub>(SD)</sub>        | Thermal shutdown                                        | Increasing junction temperature                                               |       | 160                |       | °C       |

| (00)                     | Thermal shutdown hysteresis                             | Decreasing junction temperature                                               |       | 20                 |       | °C       |

| INTERNAL UNDERVOL        |                                                         |                                                                               |       |                    |       |          |

| UVLO                     | Internal UVLO                                           | VCC falling                                                                   | -2%   | 2.35               | 2%    | V        |

| V <sub>(UVLO_HYST)</sub> | Internal UVLO comparator hysteresis                     |                                                                               |       | 120                |       | mV       |

| VOLTAGE DETECTOR         |                                                         | 1                                                                             | I     | -                  |       |          |

|                          | Comparator threshold<br>(PWRFAIL SNS, LOWBAT SNS)       | Falling threshold                                                             | -1%   | 1                  | 1%    | V        |

|                          | Hysteresis                                              |                                                                               | 40    | 50                 | 60    | mV       |

|                          | Propagation delay                                       | 25-mV overdrive                                                               |       |                    | 10    | μS       |

| POWER-GOOD               | · · · · · · · · · · · · · · · · · · ·                   |                                                                               | [     |                    |       | <u> </u> |

| V <sub>(PGOODF)</sub>    |                                                         | VDCDC1, VDCDC2, VDCDC3, VLDO1,<br>VLDO2, decreasing                           | -12%  | -10%               | -8%   |          |

| V <sub>(PGOODR)</sub>    |                                                         | VDCDC1, VDCDC2, VDCDC3, VLDO1,<br>VLDO2, increasing                           | -7%   | -5%                | -3%   |          |

#### 6.6 Electrical Characteristics: Supply Pins VCC, VINDCDC1, VINDCDC2, VINDCDC3

VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V,  $T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS                                                                 |                                                                                                                                                      | MIN | <b>TYP</b> <sup>(1)</sup> | MAX | UNIT       |

|------------------|-------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-----|------------|

|                  |                                     | All 3 DCDC converters enabled, zero load, and no switching, LDOs enabled        | $\label{eq:VCC} \begin{array}{l} VCC = 3.6 \ V, \ VBACKUP = 3 \ V; \\ V_{(VSYSIN)} = 0 \ V \end{array}$                                              |     | 85                        | 100 |            |

|                  | Operating guisesent                 | All 3 DCDC converters enabled, zero load, and no switching, LDOs off            | $ \begin{array}{l} \mbox{VCC} = 3.6 \mbox{ V}, \mbox{VBACKUP} = 3 \mbox{ V}; \\ \mbox{V}_{(VSYSIN)} = 0 \mbox{ V} \end{array} $                      |     | 78                        | 90  |            |

| I <sub>(q)</sub> | Operating quiescent<br>current, PFM | DCDC1 and DCDC2 converters<br>enabled, zero load, and no switching,<br>LDOs off | $ \begin{array}{l} \mbox{VCC} = 3.6 \mbox{ V}, \mbox{VBACKUP} = 3 \mbox{ V}; \\ \mbox{V}_{(\mbox{VSYSIN})} = 0 \mbox{ V} \end{array} $               |     | 57                        | 70  | μA         |

|                  |                                     | DCDC1 converter enabled, zero load, and no switching, LDOs off                  | $\label{eq:VCC} \begin{array}{l} VCC = 3.6 \; V, \; VBACKUP = 3 \; V; \\ V_{(VSYSIN)} = 0 \; V \end{array}$                                          |     | 43                        | 55  |            |

|                  |                                     | All 3 DCDC converters enabled and<br>running in PWM, LDOs off                   | $\label{eq:VCC} \begin{array}{l} VCC = 3.6 \ V, \ VBACKUP = 3 \ V; \\ V_{(VSYSIN)} = 0 \ V \end{array}$                                              |     | 2                         | 3   |            |

| I                | Current into VCC; PWM               | DCDC1 and DCDC2 converters<br>enabled and running in PWM, LDOs<br>off           | $ \begin{array}{l} \text{VCC} = 3.6 \text{ V}, \text{ VBACKUP} = 3 \text{ V}; \\ \text{V}_{(\text{VSYSIN})} = 0 \text{ V} \end{array} $              |     | 1.5                       | 2.5 | mA         |

|                  |                                     | DCDC1 converter enabled and running in PWM, LDOs off                            | $ \begin{array}{l} \mbox{VCC} = 3.6 \mbox{ V}, \mbox{VBACKUP} = 3 \mbox{ V}; \\ \mbox{V}_{(VSYSIN)} = 0 \mbox{ V} \end{array} $                      |     | 0.85                      | 2   |            |

|                  |                                     |                                                                                 | $\label{eq:VCC} \begin{array}{l} VCC = 3.6 \ V, \ VBACKUP = 3 \ V; \\ V_{(VSYSIN)} = 0 \ V \end{array}$                                              |     | 23                        | 33  | μA         |

| I <sub>(q)</sub> | Quiescent current                   | All converters disabled, LDOs off                                               | $\label{eq:VCC} \begin{array}{l} \text{VCC} = 2.6 \text{ V}, \text{ VBACKUP} = 3 \text{ V}; \\ \text{V}_{(\text{VSYSIN})} = 0 \text{ V} \end{array}$ |     | 3.5                       | 5   | μA         |

|                  |                                     |                                                                                 | $ \begin{array}{l} VCC = 3.6 \ V, \ VBACKUP = 0 \ V; \\ V_{(VSYSIN)} = 0 \ V \end{array} $                                                           |     |                           | 43  | μ <b>A</b> |

(1) Typical values are at  $T_A = 25^{\circ}$ C, unless otherwise noted.

#### 6.7 Electrical Characteristics: Supply Pins VBACKUP, VSYSIN, VRTC, VINLDO

VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V,  $T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                   | PARAMETER                                          | TEST CONDITIONS                                                     | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|-------------------|----------------------------------------------------|---------------------------------------------------------------------|------|--------------------|------|------|

| VBAC              | KUP, VSYSIN, VRTC                                  |                                                                     |      |                    |      |      |

| I <sub>(q)</sub>  | Operating quiescent current                        | VBACKUP = 3 V, VSYSIN = 0 V;<br>VCC = 2.6 V, current into VBACKUP   |      | 20                 | 33   | μA   |

| I <sub>(SD)</sub> | Operating quiescent current                        | VBACKUP < V_VBACKUP, current into VBACKUP                           |      | 2                  | 3    | μA   |

|                   | VRTC LDO output voltage                            | VSYSIN = VBACKUP = 0 V, I <sub>O</sub> = 0 mA                       |      | 3                  |      | V    |

| lo                | Output current for VRTC                            | VSYSIN < 2.57 V and VBACKUP < 2.57 V                                |      |                    | 30   | mA   |

|                   | VRTC short-circuit current limit                   | VRTC = GND; VSYSIN = VBACKUP = 0 V                                  |      |                    | 100  | mA   |

|                   | Maximum output current at VRTC for<br>RESPWRON = 1 | VRTC > 2.6 V, $V_{CC} = 3 V$ ;<br>VSYSIN = VBACKUP = 0 V            | 30   |                    |      | mA   |

| Vo                | Output voltage accuracy for VRTC                   | VSYSIN = VBACKUP = 0 V; I <sub>O</sub> = 0 mA                       | -1%  |                    | 1%   |      |

|                   | Line regulation for VRTC                           | VCC = VRTC + 0.5 V to 6.5 V, $I_0 = 5 \text{ mA}$                   | -1%  |                    | 1%   |      |

|                   | Load regulation VRTC                               | $I_{O} = 1 \text{ mA to } 30 \text{ mA};$<br>VSYSIN = VBACKUP = 0 V | -3%  |                    | 1%   |      |

|                   | Regulation time for VRTC                           | Load change from 10% to 90%                                         |      | 10                 |      | μS   |

| l <sub>lkg</sub>  | Input leakage current at VSYSIN                    | VSYSIN < V_VSYSIN                                                   |      |                    | 2    | μA   |

|                   | r <sub>DS(on)</sub> of VSYSIN switch               |                                                                     |      |                    | 12.5 | Ω    |

|                   | r <sub>DS(on)</sub> of VBACKUP switch              |                                                                     |      |                    | 12.5 | Ω    |

|                   | Input voltage range at VBACKUP <sup>(2)</sup>      |                                                                     | 2.73 |                    | 3.75 | V    |

|                   | Input voltage range at VSYSIN <sup>(2)</sup>       |                                                                     | 2.73 |                    | 3.75 | V    |

|                   | VSYSIN threshold                                   | VSYSIN falling                                                      | -3%  | 2.55               | 3%   | V    |

(1) Typical values are at  $T_A = 25^{\circ}C$ , unless otherwise noted.

(2) Based on the requirements for the Intel PXA270 processor.

#### Electrical Characteristics: Supply Pins VBACKUP, VSYSIN, VRTC, VINLDO (continued)

VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V,  $T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                   | PARAMETER                   | TEST CONDITIONS                                     | MIN | <b>TYP</b> <sup>(1)</sup> | MAX | UNIT |

|-------------------|-----------------------------|-----------------------------------------------------|-----|---------------------------|-----|------|

|                   | VSYSIN threshold            | VSYSIN rising                                       | -3% | 2.65                      | 3%  | V    |

|                   | VBACKUP threshold           | VBACKUP falling                                     | -3% | 2.55                      | 3%  | V    |

|                   | VBACKUP threshold           | VBACKUP rising                                      | -3% | 2.65                      | 3%  | V    |

| VINLDO            | )                           |                                                     |     |                           |     |      |

| I <sub>(q)</sub>  | Operating quiescent current | Current per LDO into VINLDO<br>for LDO_CTRL = 0x0   |     | 16                        | 30  | μA   |

| I <sub>(SD)</sub> | Shutdown current            | Total current for both LDOs into VINLDO, VLDO = 0 V |     | 0.1                       | 1   | μA   |

#### 6.8 Electrical Characteristics: VDCDC1 Step-Down Converter

VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V,  $T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                     | PARAMETER                                                                     |            | TEST CONDITIONS                                                                                                                                                     | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|---------------------|-------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

| VI                  | Input voltage range, VINDCDC1                                                 |            |                                                                                                                                                                     | 2.5  |                    | 6    | V    |

| I <sub>O</sub>      | Maximum output current                                                        |            |                                                                                                                                                                     | 1700 |                    |      | mA   |

| I <sub>(SD)</sub>   | Shutdown supply current i                                                     | n VINDCDC1 | DCDC1_EN = GND                                                                                                                                                      |      | 0.1                | 1    | μA   |

| r <sub>DS(on)</sub> | P-channel MOSFET on-re                                                        | sistance   | $VINDCDC1 = V_{(GS)} = 3.6 V$                                                                                                                                       |      | 125                | 261  | mΩ   |

| l <sub>lkg</sub>    | P-channel leakage current                                                     | t          | VINDCDC1 = 6 V                                                                                                                                                      |      |                    | 2    | μA   |

| r <sub>DS(on)</sub> | N-channel MOSFET on-re                                                        | sistance   | $VINDCDC1 = V_{(GS)} = 3.6 V$                                                                                                                                       |      | 130                | 260  | mΩ   |

| l <sub>lkg</sub>    | N-channel leakage current                                                     | t          | V <sub>(DS)</sub> = 6 V                                                                                                                                             |      | 7                  | 10   | μA   |

|                     | Forward current limit (P-channel and N-channel)                               |            | 2.5 V < V <sub>I(MAIN)</sub> < 6 V                                                                                                                                  | 1.94 | 2.19               | 2.44 | А    |

| f <sub>S</sub>      | Oscillator frequency                                                          |            |                                                                                                                                                                     | 1.95 | 2.25               | 2.55 | MHz  |

|                     | Fixed output voltage<br>FPWMDCDC1 = 0                                         |            | VINDCDC1 = 2.5 V to 6 V;<br>0 mA $\leq$ I <sub>O</sub> $\leq$ 1.7 A                                                                                                 | -2%  |                    | 2%   |      |

|                     | Fixed output voltage<br>FPWMDCDC1 = 1                                         | All VDCDC1 | VINDCDC1 = 2.5 V to 6 V;<br>0 mA $\leq$ I <sub>O</sub> $\leq$ 1.7 A                                                                                                 | -1%  |                    | 1%   |      |

|                     | Adjustable output voltage<br>at DEFDCDC1; FPWMDC                              |            | $ \begin{array}{l} \mbox{VINDCDC1} = \mbox{VDCDC1} + 0.5 \mbox{ V} \mbox{ (min 2.5 V)} \\ \mbox{to 6 V; 0 mA } \leq \mbox{I}_{O} \ \leq \mbox{1.7 A} \end{array} $  | -2%  |                    | 2%   |      |

|                     | Adjustable output voltage with resistor divider<br>at DEFDCDC1; FPWMDCDC1 = 1 |            | $ \begin{array}{l} \mbox{VINDCDC1} = \mbox{VDCDC1} + 0.5 \mbox{ V} \mbox{ (min 2.5 V)} \\ \mbox{to 6 V; 0 mA } \leq \mbox{I}_{O} \ \leq 1.7 \mbox{ A} \end{array} $ | -1%  |                    | 1%   |      |

|                     | Line Regulation                                                               |            | $ \begin{array}{l} \mbox{VINDCDC1} = \mbox{VDCDC1} + 0.3 \mbox{ V (min. 2.5 V)} \\ \mbox{to 6 V; } \mbox{I}_{O} = 10 \mbox{ mA} \end{array} $                       |      | 0%                 |      | V    |

|                     | Load Regulation                                                               |            | I <sub>O</sub> = 10 mA to 1700 mA                                                                                                                                   |      | 0.25%              |      | А    |

| t <sub>Start</sub>  | Start-up time                                                                 |            | Time from active EN to start switching                                                                                                                              | 145  | 175                | 200  | μs   |

| t <sub>Ramp</sub>   | V <sub>OUT</sub> ramp-up time                                                 |            | Time to ramp from 5% to 95% of $V_{\mbox{OUT}}$                                                                                                                     | 400  | 750                | 1000 | μs   |

|                     | Internal resistance from L1 to GND                                            |            |                                                                                                                                                                     |      | 1                  |      | MΩ   |

|                     | VDCDC1 discharge resistance                                                   |            | DCDC1 discharge = 1                                                                                                                                                 |      | 300                |      | Ω    |

(1) Typical values are at  $T_A = 25^{\circ}C$ , unless otherwise noted.

STRUMENTS

EXAS

#### 6.9 Electrical Characteristics: VDCDC2 Step-Down Converter

VINDCDC1 = VINDCDC2 = VINDCDC3 = VCC = VINLDO = 3.6 V, VBACKUP = 3 V, T<sub>A</sub> =  $-40^{\circ}$ C to  $85^{\circ}$ C (unless otherwise noted)

|                     | PARAMETE                                                                   | R                | TEST CONDITIONS                                                          | MIN  | <b>TYP</b> <sup>(1)</sup> | MAX  | UNIT |

|---------------------|----------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------|------|---------------------------|------|------|

| VI                  | Input voltage range, VINDCDC2                                              |                  |                                                                          | 2.5  |                           | 6    | V    |

|                     |                                                                            |                  | DEFDCDC2 = GND                                                           | 1200 |                           |      |      |

| lo                  |                                                                            |                  | VINDCDC2 = 3.6 V;<br>3.3 V - 1% ≤ VDCDC2 ≤ 3.3V + 1%                     | 1000 |                           |      | mA   |

| I <sub>(SD)</sub>   | Shutdown supply curre                                                      | ent in VINDCDC2  | DCDC2_EN = GND                                                           |      | 0.1                       | 1    | μA   |

| r <sub>DS(on)</sub> | P-channel MOSFET or                                                        | n-resistance     | $VINDCDC2 = V_{(GS)} = 3.6 V$                                            |      | 140                       | 300  | mΩ   |

| l <sub>lkg</sub>    | P-channel leakage cur                                                      | rent             | VINDCDC2 = 6 V                                                           |      |                           | 2    | μA   |

| r <sub>DS(on)</sub> | N-channel MOSFET o                                                         | n-resistance     | $VINDCDC2 = V_{(GS)} = 3.6 V$                                            |      | 150                       | 297  | mΩ   |

| l <sub>lkg</sub>    | N-channel leakage cur                                                      | rrent            | $V_{(DS)} = 6 V$                                                         |      | 7                         | 10   | μA   |

| I <sub>LIMF</sub>   | Forward current limit (I channel)                                          | P-channel and N- | 2.5 V < VINDCDC2 < 6 V                                                   | 1.74 | 1.94                      | 2.12 | А    |

| f <sub>S</sub>      | Oscillator frequency                                                       |                  |                                                                          | 1.95 | 2.25                      | 2.55 | MHz  |

|                     | Fixed output voltage                                                       | VDCDC2 = 1.8 V   | VINDCDC2 = 2.5 V to 6 V;<br>0 mA $\leq$ I <sub>O</sub> $\leq$ 1.2 A      | -2%  |                           | 2%   |      |

|                     | FPWMDCDC2=0                                                                | VDCDC2 = 3.3 V   | VINDCDC2 = 3.7 V to 6 V;<br>0 mA $\leq$ I <sub>O</sub> $\leq$ 1.2 A      | -1%  |                           | 1%   |      |

|                     | Fixed output voltage                                                       | VDCDC2 = 1.8 V   | VINDCDC2 = 2.5 V to 6 V;<br>0 mA $\leq$ I <sub>O</sub> $\leq$ 1.2 A      | -2%  |                           | 2%   |      |

|                     | FPWMDCDC2=1                                                                | VDCDC2 = 3.3 V   | VINDCDC2 = 3.7 V to 6 V;<br>0 mA $\leq$ I <sub>O</sub> $\leq$ 1.2 A      | -1%  |                           | 1%   |      |

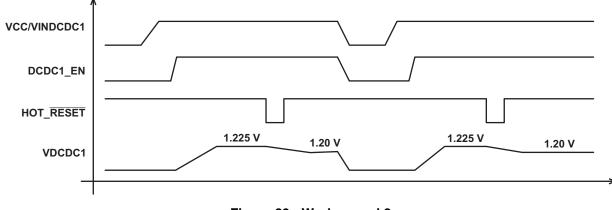

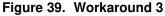

|                     | Adjustable output voltage with resistor<br>divider at DEFDCDC2 FPWMDCDC2=0 |                  | VINDCDC2 = VDCDC2 + 0.3 V (min 2.5 V) to 6 V; 0 mA $\leq I_{O} \leq 1$ A | -2%  |                           | 2%   |      |