# **AMMP-5024**

# 30kHz – 40 GHz Traveling Wave Amplifier

# **Data Sheet**

## **Description**

Avago Technologies' AMMP-5024 is a broadband PHEMT GaAs MMIC TWA designed for medium output power and high gain over the full 30 KHz to 40 GHz frequency range. The design employs a 9-stage, cascade-connected FET structure to ensure flat gain and power as well as uniform group delay. E-beam lithography is used to produce uniform gate lengths of 0.15um and MBE technology assures precise semiconductor layer control.

# **Functional Block Diagram**

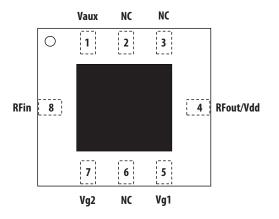

| Function                |

|-------------------------|

| V <sub>aux</sub>        |

| Not Used                |

| Not Used                |

| RF <sub>out</sub> / Vdd |

| $V_{g1}$                |

| Not Used                |

| $V_{g2}$                |

| RF <sub>in</sub>        |

|                         |

#### **RoHS-Exemption**

Please refer to Hazardous substances table on page 8.

#### **Features**

- Surface Mount Package 5.0 x 5.0 x 2.0 mm

- Wide Frequency Range 30kHz 40GHz

- High Gain: 14.8 dB Typical @ 22GHz

- Output P1dB: 22 dBm Typical @ 22GHz

- 50 Ohm Input and Output Match

# Applications [1]

• Broadband Test and Measurement Applications

# **Package Diagram**

Attention: Observe precautions for handling electrostatic sensitive devices.

ESD Machine Model (Class A): 40V

ESD Human Body Model (Class 0): 150V

Refer to Avago Application Note A004R:

Electrostatic Discharge Damage and Control.

Note: MSL Rating = Level 2A

# **Electrical Specifications**

- 1. Specifications are derived from measurements in a 50 Ohm test environment at Freq = 22GHz, Vdd = 7V, Idd = 200mA, TA = 25°C. Aspects of the amplifier performance may be improved over a narrower bandwidth by application of additional conjugate, linearity, or low noise matching.

- 2. All tested parameters guaranteed with measurement accuracy  $\pm$  0.5 dB for gain.

- 3. Specifications are derived from measurements in a 50 Ohm test environment at Freq = 22GHz, Vdd = 4V, Idd = 160mA, TA = 25°C. Aspects of the amplifier performance may be improved over a narrower bandwidth by application of additional conjugate, linearity, or low noise matching.

- 4. All tested parameters guaranteed with measurement accuracy  $\pm$  0.5 dB for gain.

**Table 1. RF Electrical Characteristics**

| Parameter                                                  | Min  | Тур. | Max  | Unit |

|------------------------------------------------------------|------|------|------|------|

| Small-signal Gain, Ga                                      | 12.5 | 14.8 | 16.5 | dB   |

| Noise Figure, NF                                           |      | 4.6  |      | dB   |

| Output Power at 1dB Gain Compression, P-1dB                |      | 22   |      | dBm  |

| Third Order Intercept Point;<br>Δf=100MHz; Pin=-5dBm, OIP3 |      | 25   |      | dBm  |

| nput Return Loss, RLin                                     |      | 13   |      | dB   |

| Output Return Loss, Rlout                                  |      | 14   |      | dB   |

| Reverse Isolation, Isol                                    |      | 30   |      | dB   |

**Table 2. RF Electrical Characteristics**

| Parameter                                                  | Min | Typ. | Max | Unit |  |

|------------------------------------------------------------|-----|------|-----|------|--|

| Small-signal Gain, Ga                                      |     | 15   |     | dB   |  |

| Noise Figure, NF                                           |     | 4.6  |     | dB   |  |

| Output Power at 1dB Gain Compression, P-1dB                |     | 19   |     | dBm  |  |

| Third Order Intercept Point;<br>Δf=100MHz; Pin=-5dBm, OIP3 |     | 18.5 |     | dBm  |  |

| Input Return Loss, RLin                                    |     | 13   |     | dB   |  |

| Output Return Loss, Rlout                                  |     | 14   |     | dB   |  |

| Reverse Isolation, Isol                                    |     | 27   |     | dB   |  |

## **Table 3. Recommended Operating Range**

(Vdd=7V, Vg2=open, Ta= 25°C, otherwise specified)

|                                                | Specifications |         |      |      |                         |

|------------------------------------------------|----------------|---------|------|------|-------------------------|

| Description                                    | Min.           | Typical | Max. | Unit | Comments                |

| Drain Supply Voltage, Vd                       |                | 7       |      | V    |                         |

| Total Drain Supply Current, Idd                |                | 200     |      | mA   | Vg1 set for typical Idd |

| First Gate Voltage, Vg1                        | -3.5           | -3.0    | -2.5 | V    | Vdd=7V, Idd=200mA       |

| Saturated Drain Current, Idss                  |                | 350     |      | mA   | Vg1=0V                  |

| First Gate Minimum Drain Current, Idsmin (Vg1) |                | 80      |      | mA   | Vg1=-7V                 |

**Table 4. Thermal Properties**

| Parameter                 | Test Conditions | Value                     |

|---------------------------|-----------------|---------------------------|

| Thermal Resistance, θch-b |                 | $\theta$ ch-b = 16.2 °C/W |

#### Note:

# **Absolute Minimum and Maximum Ratings**

**Table 5. Minimum and Maximum Ratings**

|                              |          | Specifications |      |      |            |

|------------------------------|----------|----------------|------|------|------------|

| Description                  | Pin      | Min.           | Max. | Unit | Comments   |

| Drain Supply Voltage         | Rfin/Vdd |                | 10   | V    |            |

| Drain Current                |          |                | 380  | mA   |            |

| First Gate Voltage           | Vg1      | -9.5           | 0    | V    |            |

| First Gate Current           |          | -38            | 1    | mA   |            |

| Second Gate Voltage          | Vg2      | -3.5           | 4    | V    |            |

| Second Gate Current          |          | -20            |      | mA   |            |

| RF Input Power (Pin)         | RFIN     |                | 17   | dBm  | CW         |

| Channel Temperature          |          |                | +150 | °C   |            |

| Storage Temperature          |          | -65            | +150 | °C   |            |

| Maximum Assembly Temperature |          |                | +260 | °C   | 20 sec Max |

#### Notes:

<sup>1.</sup> Channel-to-board Thermal Resistance is measured using QFI method.

<sup>1.</sup> Operation in excess of any one of these conditions may result in permanent damage to this device. The absolute maximum ratings for DC and Power parameters were determined at an ambient temperature of 25°C unless noted otherwise.

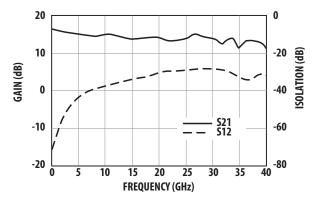

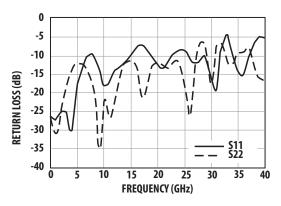

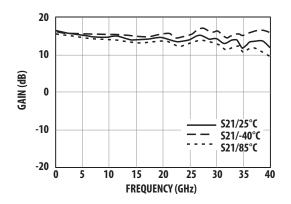

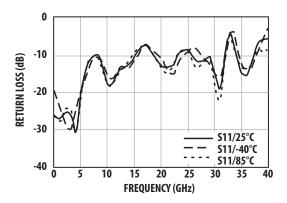

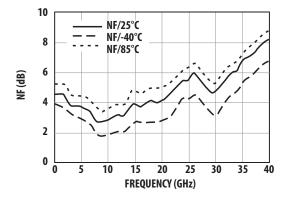

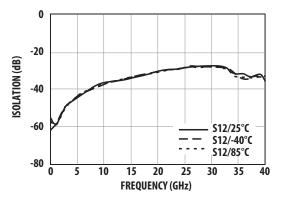

# Selected performance plots

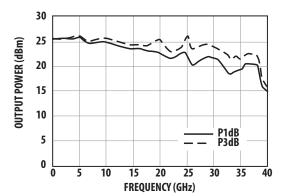

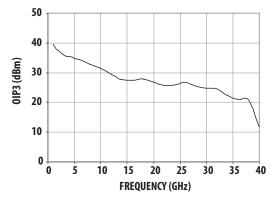

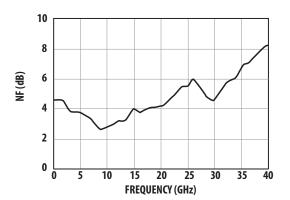

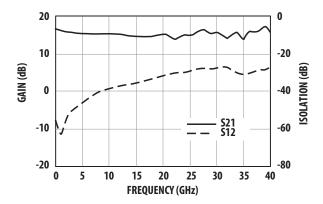

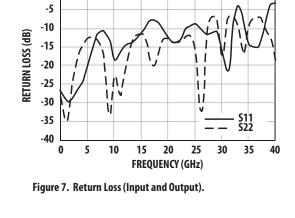

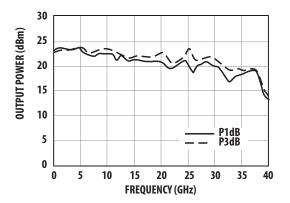

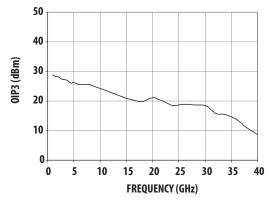

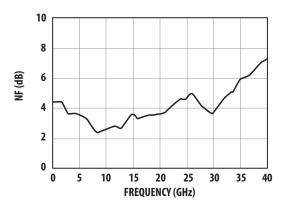

These measurements are in  $50\Omega$  test environment at Vdd = 7V, Idd = 200mA, Vg2 = Open, TA = 25°C.

Figure 1. Gain and Reverse Isolation

Figure 2. Return Loss (Input and Output).

Figure 3. Output Power (P1dB and P3dB)

Figure 4. Output IP3

Figure 5. Npise Figure

These measurements are in  $50\Omega$  test environment at Vdd = 4V, Idd = 160mA, Vg2 = Open, TA = 25°C

0

Figure 6. Gain and Reverse Isolation

Figure 8. Output Power (P1dB and P3dB)

Figure 9. Output IP3

Figure 10. Noise Figure

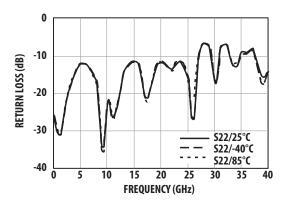

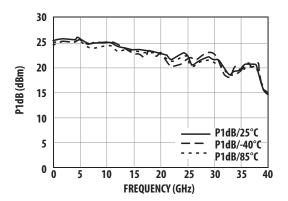

# **Over Temperature Performance Plots**

These measurements are in  $50\Omega$  test environment at Vdd = 7V, Idd = 200mA

Figure 11. Gain and Temperature.

Figure 13. Input Return Loss and Temperature.

Figure 15. Noise Figure and Temperature.

Figure 12. Isolation and Temperature.

Figure 14. Output Return Loss and Temperature.

Figure 16. P1dB and Temperature.

## **Typical Scattering Parameters**

Please refer to <a href="http://www.avagotech.com">http://www.avagotech.com</a> for typical scattering parameters data.

#### **Biasing and Operation**

AMMP-5024 is biased with a single positive drain supply (Vdd) a negative gate supply (Vg1) and has a positive control gate supply (Vg2). For best overall performance the recommended bias condition for the AMMP-5024 is Vdd =7V and Idd = 200 mA. To achieve this drain current level, Vg1 is typically between -2.5 to -3.5V. Typically, DC current flow for Vg1 is -10 mA. Open circuit is the default setting for Vg2 when not utilizing gain control.

Using the simplest form of assembly, the device is capable of delivering flat gain over a 2–40 GHz range. However, this device is designed with DC coupled RF I/O ports, and operation may be extended to lower frequencies (<2 GHz) through the use of off-chip low-frequency extension circuitry and proper external biasing components. With low frequency bias extension it may be used in a variety of time domain applications (through 40 Gb/s).

When bypass capacitors are connected to the AUX pads, the low frequency limit is extended down to the corner frequency determined by the bypass capacitor and the combination of the on-chip 50 ohm load and small de-queing resistor. At this frequency the small signal gain will increase in magnitude and stay at this elevated level down to the point where the Caux bypass

capacitor acts as an open circuit, effectively rolling off the gain completely. The low frequency limit can be approximated from the following equation:

$$f_{Caux} = \frac{1}{2\pi Caux (Ro + R_{DEQ})}$$

where:

**Ro** is the  $50\Omega$  gate or drain line termination resistor.

**RDEQ** is the small series dequeing resistor and  $10\Omega$ .

**Caux** is the capacitance of the bypass capacitor connected to the AUX Drain and AUX Gate pad in farads.

With the external bypass capacitors connected to the AUX gate and AUX drain pads, gain will show a slight increase between 1.0 and 1.5 GHz. This is due to a series combination of Caux and the on-chip resistance but is exaggerated by the parasitic inductance (Lc) of the bypass capacitor and the inductance of the bond wire (Ld).

Input and output RF ports are DC coupled; therefore, DC decoupling capacitors are required if there are DC paths. (Do not attempt to apply bias to these pads.)

### Package Dimension, PCB Layout and Tape and Reel information

Please refer to Avago Technologies Application Note 5520, AMxP-xxxx production Assembly Process (Land Pattern A)

## **Ordering Information**

|                | Davisas nav              |                |

|----------------|--------------------------|----------------|

| Part Number    | Devices per<br>Container | Container      |

| AMMP-5024-BLKG | 10                       | Antistatic Bag |

| AMMP-5024-TR1G | 100                      | 7" Reel        |

| AMMP-5024-TR2G | 500                      | 7" Reel        |

# Names and Contents of the Toxic and Hazardous Substances or Elements in the Products 产品中有毒有害物质或元素的名称及含量

| Part Name       | Toxic and Hazardous Substances or Elements<br>有毒有害物质或元素                                  |   |   |   |   |   |  |

|-----------------|------------------------------------------------------------------------------------------|---|---|---|---|---|--|

| 部件名称            | Lead<br>(Pb) 铅Mercury (Hg) 汞<br>(Hg) 汞Cadmium (Cd) 镉<br>(Cd) 镉Hexavalent (Cr(VI)) 六价<br> |   |   |   |   |   |  |

| 100pF capacitor | ×                                                                                        | 0 | 0 | 0 | 0 | 0 |  |

- o: indicates that the content of the toxic and hazardous substance in all the homogeneous materials of the part is below the concentration limit requirement as described in SJ/T 11363-2006.

- x: indicates that the content of the toxic and hazardous substance in at least one homogeneous material of the part exceeds the concentration limit requirement as described in SJ/T 11363-2006.

- (The enterprise may further explain the technical reasons for the "x" indicated portion in the table in accordance with the actual situations.)

- o:表示该有毒有害物质在该部件所有均质材料中的含量均在 SJ/T 11363-2006 标准规定的限量要求以下。

- x:表示该有毒有害物质至少在该部件的某一均质材料中的含量超出 SJ/T 11363-2006 标准规定的限量要求。(企业可在此处,根据实际情况对上表中打"x"的技术原因进行进一步说明。)

Note: EU RoHS compliant under exemption clause of "lead in electronic ceramic parts (e.g. piezoelectronic devices)"