# LS7083N LS7084N

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

# QUADRATURE CLOCK CONVERTER

June 2015

#### **FEATURES:**

- x1 and x4 mode selection

- Up to 16MHz output clock frequency

- Programmable output clock pulse width

- On-chip filtering of inputs for optical or magnetic encoder applications.

- TTL and CMOS compatible I/Os

- +3V to +12V operation (VDD VSS)

- · LS7083N, LS7084N (DÌP);

LS7083NS, LS7084NS (SOIC) - See Figure 1

#### Applications:

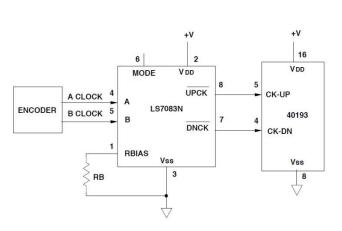

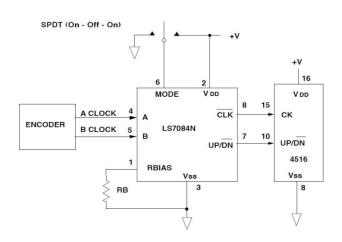

- Interface incremental encoders to Up / Down Counters (See Figure 6A and Figure 6B)

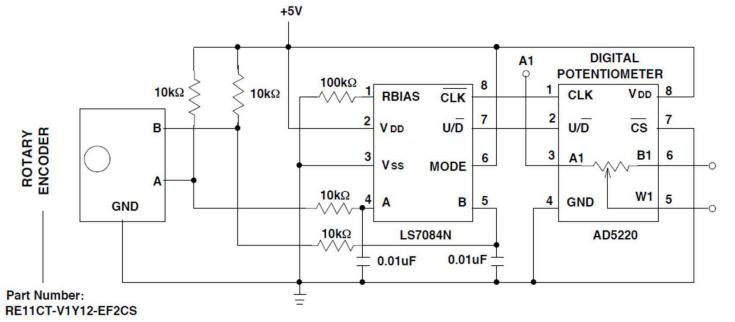

- Interface rotary encoders to Digital Potentiometers (See Figure 7)

#### **DESCRIPTION:**

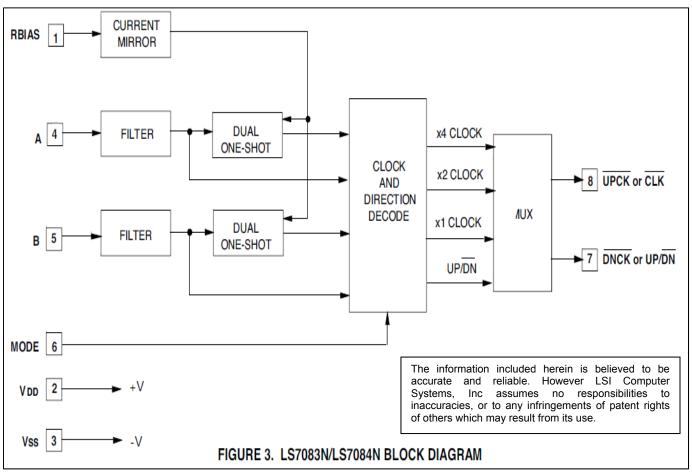

The **LS7083N** and **LS7084N** are CMOS quadrature clock converters. Quadrature clocks derived from optical or magnetic encoders, when applied to the A and B inputs of the **LS7083N** or **LS7084N**, are converted to strings of Up Clocks and Down Clocks (**LS7083N**) or to a Clock and an Up/Down direction control (**LS7084N**). These outputs can be interfaced directly with standard Up/Down counters for direction and position sensing of the encoder.

# INPUT/OUTPUT DESCRIPTION:

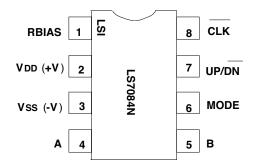

RBIAS (Pin 1)

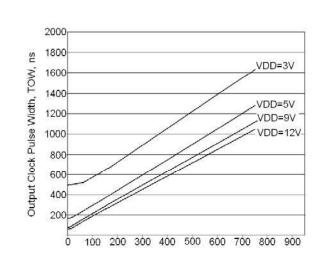

Input for external component connection. A resistor connected between this input and Vss adjusts the output clock pulse width (Tow). For proper operation, the output clock pulse width must be less than or equal to the A, B pulse separation (Tow  $\leq$  TPs).

#### VDD (Pin 2)

Supply Voltage positive terminal.

#### Vss (Pin 3)

Supply Voltage negative terminal.

#### A (Pin 4)

Quadrature Clock Input A. This input has a filter circuit to validate input logic level and eliminate encoder dither.

#### **B** (Pin 5)

Quadrature Clock Input B. This input has a filter circuit identical to input A.

### Mode (Pin 6)

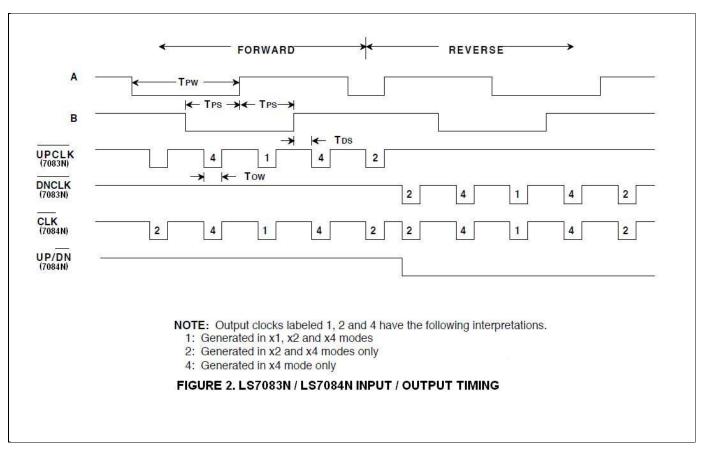

Mode is a 3-state input to select resolutions x1, x2 or x4. The selected resolution multiplies the input quadrature clock rate by 1, 2 and 4, respectively, in producing the outputs UPCK / DNCK and CLK (see Figure 2).

The Mode input logic levels selects resolutions as follows:

Logic 0 = x1 Float = x2 Logic 1 = x4

#### **PIN ASSIGNMENT - TOP VIEW**

FIGURE 1

# **LS7083N - DNCK** (Pin 7)

In **LS7083N**, this is the DOWN Clock Output. This output consists of low-going pulses generated when A input lags the B input.

#### **LS7084N - UP/DN** (Pin 7)

In **LS7084N**, this is the count direction indication output. When A input leads the B input, the  $UP/\overline{DN}$  output goes high indicating that the count direction is UP. When A input lags the B input,  $UP/\overline{DN}$  output goes low, indicating that the count direction is DOWN.

## **LS7083N - UPCK** (Pin 8)

In **LS7083N**, this is the UP Clock output. This output consists of low-going pulses generated when A input leads the B input.

#### **LS7084N - CLK** (Pin 8)

In **LS7084N**, this is the combined UP Clock and DOWN Clock <u>output</u>. The count direction at any instant is indicated by the UP/DN output (Pin 7).

**NOTE**: For the **LS7084N**, the timing of  $\overline{\text{CLK}}$  and  $\overline{\text{UP/DN}}$  requires that the <u>counter interfacing</u> with **LS7084N** counts on the rising edge of the  $\overline{\text{CLK}}$  pulses.

| ABSOLUTE MAXIMUM RATI    | NGS:                |                                |                   |                       |          |                                                                                                                                         |

|--------------------------|---------------------|--------------------------------|-------------------|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                | SYMBOL              |                                | VALUE             |                       | UNITS    |                                                                                                                                         |

| DC Supply Voltage        | $V_{DD}$ - $V_{SS}$ | 16                             |                   | ٧                     |          |                                                                                                                                         |

| Voltage at any input     | $V_{IN}$            | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 |                   |                       | ٧        |                                                                                                                                         |

| Operating temperature    | $T_A$               |                                | -20 to +85        | ;                     | ōC       |                                                                                                                                         |

| Storage temperature      | $T_{STG}$           |                                | -55 to 150        | )                     | ōC       |                                                                                                                                         |

| DC ELECTRICAL CHARACT    | ERISTICS:           | (Unless otherw                 | ise specifi       | ed $V_{DD} = 3V$ to 1 | 2V and T | $_{A}$ = -20 $^{\circ}$ C to +85 $^{\circ}$ C)                                                                                          |

| PARAMETER                | SYMBOL              | MIN                            | TYP               | MAX                   | UNITS    | CONDITION                                                                                                                               |

| Supply Voltage           | $V_{DD}$            | 3                              | -                 | 12                    | ٧        | -                                                                                                                                       |

| Supply Current           | $I_{DD}$            | -                              | 1.5               | 1.65                  | mA       | $\mbox{V}_{\mbox{\scriptsize DD}}\mbox{=}$ 12V, all input frequencies=0 Hz and $\mbox{R}_{\mbox{\scriptsize BIAS}}\mbox{=}$ 2M $\Omega$ |

| MODE INPUT:              |                     |                                |                   |                       |          |                                                                                                                                         |

| Logic 0                  | $V_{ml}$            | -                              | -                 | 0.5                   | ٧        | -                                                                                                                                       |

| Logic 1                  | $V_{mh}$            | $V_{DD}$ - 0.5                 | -                 | -                     | ٧        |                                                                                                                                         |

| Logic Float              | $V_{\rm mf}$        | $(V_{DD}/2) - 0.5$             | $V_{\text{DD}}/2$ | $(V_{DD}/2)+0.5$      | ٧        | -                                                                                                                                       |

| Logic 0 Input Current    | I <sub>ml</sub>     | -                              | 2.2               | 4.2                   | μΑ       | $V_{DD} = 3V$                                                                                                                           |

|                          | I <sub>ml</sub>     | -                              | 3.5               | 6.9                   | μΑ       | $V_{DD} = 5V$                                                                                                                           |

|                          | $I_{ml}$            | -                              | 8.3               | 16.2                  | μΑ       | $V_{DD} = 12V$                                                                                                                          |

| Logic 1 Input Current    | $I_{mh}$            | -                              | -2                | -9.8                  | μΑ       | $V_{DD} = 3V$                                                                                                                           |

|                          | $I_{mh}$            | -                              | -3.4              | -6.6                  | μΑ       | $V_{DD} = 5V$                                                                                                                           |

|                          | I <sub>mh</sub>     | -                              | -8.2              | -16                   | μΑ       | $V_{DD} = 12V$                                                                                                                          |

| A,B INPUTS:              |                     |                                |                   |                       |          |                                                                                                                                         |

| Logic 0                  | $V_{ABI}$           | -                              | -                 | $0.25V_{DD}$          | V        | -                                                                                                                                       |

| Logic 1                  | $V_{ABh}$           | $0.7V_{DD}$                    | -                 | -                     | V        | -                                                                                                                                       |

| Input Current            | I <sub>ABIk</sub>   | -                              | 0                 | 10                    | nA       | -                                                                                                                                       |

| RBIAS INPUT:             |                     |                                |                   |                       |          |                                                                                                                                         |

| External Resistor        | $R_B$               | 2K                             | -                 | 10M                   | Ω        | -                                                                                                                                       |

| ALL OUTPUTS:             |                     |                                |                   |                       |          |                                                                                                                                         |

| Sink Current             | I <sub>ol</sub>     | -                              | -3.2              | -                     | mA       |                                                                                                                                         |

|                          | I <sub>ol</sub>     | -                              | -4.8              | -                     | mA       |                                                                                                                                         |

|                          | l <sub>ol</sub>     | -                              | -7.2              | -                     | mA       |                                                                                                                                         |

| Source Current           | l <sub>oh</sub>     | -                              | 1.7               | -                     | mA       |                                                                                                                                         |

|                          | l <sub>oh</sub>     | -                              | 2.2               | -                     | mA       |                                                                                                                                         |

|                          | l <sub>oh</sub>     | -                              | 3.1               | -                     | mA       |                                                                                                                                         |

| TRANSIENT CHARACTERIS    |                     |                                |                   |                       |          | 2017                                                                                                                                    |

| PARAMETER                | SYMBOL<br>          | MIN                            | TYP               | MAX                   | UNITS    | CONDITION                                                                                                                               |

| Output Clock Pulse Width | T <sub>ow</sub>     | 540                            |                   |                       | ns       | $V_{DD} = 3V$                                                                                                                           |

|                          | T <sub>ow</sub>     | 180                            |                   |                       | ns       | V <sub>DD</sub> = 5V                                                                                                                    |

| A D INIDI ITO            | $T_{OW}$            | 60                             |                   |                       | ns       | $V_{DD} = 12V$                                                                                                                          |

| A,B INPUTS:              | <b>-</b>            |                                | 4=0               |                       |          | V 0V                                                                                                                                    |

| Validation Delay         | T <sub>VD</sub>     | -                              | 450               | -                     |          | $V_{DD} = 3V$                                                                                                                           |

|                          | T <sub>VD</sub>     | -                              | 200               | -                     |          | V <sub>DD</sub> = 5V                                                                                                                    |

| Phase Delay              | T <sub>VD</sub>     | -<br>т.т                       | 90                | -                     | _        | $V_{DD} = 12V$                                                                                                                          |

| Phase Delay              | T <sub>PS</sub>     | $T_{VD}+T_{OW}$                |                   | ∞                     | S        | -                                                                                                                                       |

| Pulse Width              | T <sub>PW</sub>     | 2T <sub>PS</sub>               | -                 | ∞<br>1//2T \          | S<br>⊔-  | -                                                                                                                                       |

| Frequency                | f <sub>A,B</sub>    | -                              | 400               | 1/(2T <sub>PW</sub> ) | Hz       | -<br>V 2V                                                                                                                               |

| Input to output Delay    | T <sub>DS</sub>     | -                              | 490               | 565                   | ns       | $V_{DD} = 3V$                                                                                                                           |

|                          | T <sub>DS</sub>     | -                              | 220               | 345                   | ns       | V <sub>DD</sub> = 5V                                                                                                                    |

|                          | $T_{DS}$            | -                              | 125               | 135                   | ns       | $V_{DD} = 12V$                                                                                                                          |

20 VDD=3V VDD=5V VDD=9V VDD=12V VDD=12

Figure 4.  $T_{OW}$  vs.  $R_{BIAS}$  (R in  $K\Omega$ )

Figure 5.  $T_{OW}$  vs.  $R_{BIAS}$  (R in  $M\Omega$ )

Figure 6A. Typical application for 7083N in x4 mode

Figure 6B. Typical application for LS7084N in x2 mode

Figure 7. Rotary encoder control of digital potentiometer