# 1ED44175N01B

Single-channel low-side IGBT gate driver IC with over-current protection

### Features

- Over-current detection with negative voltage input

- -0.246 V over-current threshold with accurate ±5% tolerance

- Single pin for fault output and enable

- Programmable fault clear time

- Under voltage lockout for IGBTs

- CMOS Schmitt-triggered inputs

- 3.3 V, 5 V and 15 V input logic compatible

- 25 V V<sub>cc</sub> voltage supply support (max)

- Output in phase with input

- -10 Vdc negative Input capability of OCP pin

- 3 kV ESD HBM

- RoHS compliant

# **Potential applications**

- Digitally controlled PFC

- Home appliances

- Air conditioner

- Industrial applications

- General purpose low-side gate driver for single-ended topologies

# Description

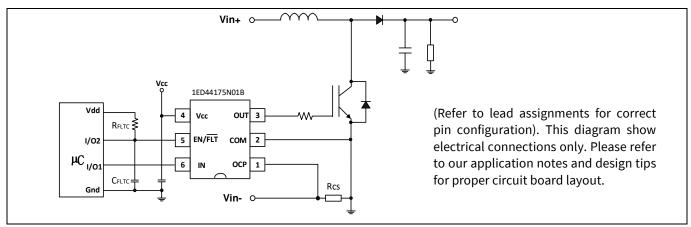

The 1ED44175N01B is a low-voltage, power IGBT, non-inverting gate driver. Proprietary latch-up immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL output. The output driver features a current buffer stage. The 1ED44175N01B has OCP pin for over current protection sense and a FAULT status output (when activivated, EN/FLT pin is internally pulled down). The EN/FLT needs to be externally pulled up to provide normal operation, pulling EN/FLT low disable the driver. Internal circuitry on V<sub>cc</sub> pin provides an under voltage lockout protection that holds output low until Vcc supply voltage is within operating range.

# Ordering information

| Product type | uct type Package Standard pack |               | Orderable part number |                   |

|--------------|--------------------------------|---------------|-----------------------|-------------------|

|              |                                | Form          | Quantity              |                   |

| 1ED44175N01B | PG-SOT23-6-3                   | Tape and Reel | 3000                  | 1ED44175N01BXTSA1 |

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC JESD47/22 and J-STD-020.

# Table of contents

| 1     | Block diagram                                      |    |

|-------|----------------------------------------------------|----|

| 2     | Pin configuration and functionality                |    |

| 2.1   | Pin configuration                                  |    |

| 2.2   | Input/output logic truth table                     |    |

| 3     | Qualification information                          | 6  |

| 4     | Electrical parameters                              |    |

| 4.1   | Absolute maximum ratings                           | 7  |

| 4.2   | Recommended operating conditions                   | 7  |

| 4.3   | Static electrical characteristics                  | 8  |

| 4.4   | Dynamic electrical characteristics                 | 8  |

| 5     | Application information and additional details     |    |

| 5.1   | IGBT gate driver                                   | 9  |

| 5.2   | Switching and timing relationships                 |    |

| 5.3   | Input logic compatibility                          |    |

| 5.4   | Undervoltage lockout (Vcc)                         |    |

| 5.5   | Over current protection (OCP)                      |    |

| 5.6   | Fault reporting and programmable fault clear timer |    |

| 5.7   | Enable input                                       |    |

| 6     | Package outline: PG-SOT23-6-3                      | 13 |

| 7     | Tape and reel details                              | 14 |

| 8     | Part marking information                           | 15 |

| 9     | Similar products                                   |    |

| 10    | Related documents                                  |    |

| Dovi  | rision history                                     |    |

| 11641 | 191011 III3tol y                                   |    |

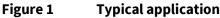

# 1 Block diagram

# 2 Pin configuration and functionality

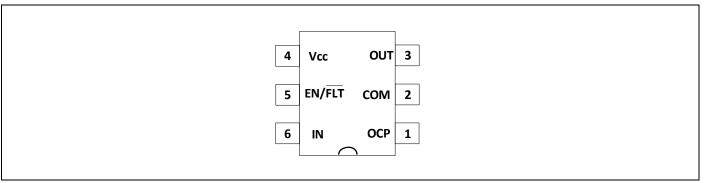

# 2.1 Pin configuration

### Table 1Pin configuration

| Pin no. | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | OCP    | Current sense input                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 2       | СОМ    | Ground                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 3       | OUT    | Gate drive output                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 4       | Vcc    | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 5       | EN/FLT | <ul> <li>Enable, fault reporting and fault clear time program pin, three functions:</li> <li>1. Logic input to enable I/O functionality. I/O logic functions when ENABLE is high.</li> <li>2. Fault reporting function like over-current or undervoltage lockout, this pin has negative logic and an open-drain output.</li> <li>3. Fault clear time program with external resistor and capacitor.</li> </ul> |  |  |  |

| 6       | IN     | Logic input for gate driver output (OUT), in phase                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

#### Figure 3 PG-SOT23-6-3 (top view)

# 2.2 Input/output logic truth table

#### Table 2Input/output logic truth table

| IN | UVLO <sup>1)</sup> | OCP <sup>2)</sup> | EN/FLT <sup>3)</sup> | OUT | Note                                                                                                                             |

|----|--------------------|-------------------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| L  | Н                  | L                 | Н                    | L   | OUT = L                                                                                                                          |

| Н  | Н                  | L                 | Н                    | Н   | OUT = H                                                                                                                          |

| х  | L                  | Х                 | L                    | L   | OUT = L, EN/FLT = L, (UVLO protection will disable input signals until EN/FLT returns to high level.)                            |

| х  | Н                  | Н                 | L                    | L   | OUT = L, EN/FLT = L, (Over current protection will disable input signals until EN/FLT returns to high level.)                    |

| х  | Н                  | Х                 | L                    | L   | OUT = L (Externally pull down EN/ $\overline{FLT}$ pin will disable I/O logic until EN/ $\overline{FLT}$ returns to high level.) |

1) UVLO "L" state is under-voltage protection.

2) OCP "H" state is over-current protection.

EN/FLT "H" state is EN/FLT pin externally pulling up and internally pull down MOSFET (QFLT) is off. (See Block Diagram.)

# **3** Qualification information

|                            |                      | Industrial <sup>1)</sup>                                   |  |

|----------------------------|----------------------|------------------------------------------------------------|--|

| Qualification level        |                      | Comments: This family of ICs has passed JEDEC's Industrial |  |

| -                          |                      | qualification. Consumer qualification level is granted by  |  |

|                            |                      | extension of the higher Industrial level.                  |  |

| Moisture sensitivity level |                      | MSL1 <sup>2)</sup> 260°C                                   |  |

|                            |                      | (per JEDEC standard J-STD-020)                             |  |

|                            | Charged device model | 1.5 kV                                                     |  |

| FCD                        | Charged device model | (per ANSI/ESDA/JEDEC standard JS-002)                      |  |

| ESD                        |                      | 3 kV                                                       |  |

|                            | Human body model     | (per ANSI/ESDA/JEDEC standard JS-001)                      |  |

| IC latch-up test           |                      | Class II, Level A                                          |  |

|                            |                      | (per JESD78)                                               |  |

| RoHS compliant             |                      | Yes                                                        |  |

1) Higher qualification ratings may be available should the user have such requirements. Please contact your Infineon sales representative for further information.

2) Higher MSL ratings may be available for the specific package types listed here. Please contact your Infineon sales representative for further information.

# 4 Electrical parameters

### 4.1 Absolute maximum ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. The device may not function or not be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. All voltage parameters are absolute voltages <u>referenced to COM</u>. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

#### Table 3Absolute maximum ratings

| Symbol                  | Definition                                           |            | Min   | Мах                  | Units |

|-------------------------|------------------------------------------------------|------------|-------|----------------------|-------|

| V <sub>cc</sub>         | Fixed supply voltage                                 |            | - 0.3 | 25                   |       |

| Vo                      | Output voltage (OUT)                                 |            | - 0.3 | V <sub>cc</sub> +0.3 |       |

| V <sub>OCP</sub>        | Voltage at current sense pin (OCP)                   |            | - 10  | V <sub>cc</sub> +0.3 | V     |

| $V_{EN}/\overline{FLT}$ | Voltage at enable and fault reporting pin $(EN/FLT)$ |            | - 0.3 | V <sub>cc</sub> +0.3 |       |

| V <sub>IN</sub>         | Logic input voltage ( IN )                           |            | - 10  | V <sub>cc</sub> +0.3 |       |

| P <sub>D</sub>          | Package power dissipation @ $T_A \le 25^{\circ}C$    | PG-SOT23-6 | —     | 0.5                  | W     |

| Rth <sub>JA</sub>       | Thermal resistance, junction to ambient              | PG-30123-0 | —     | 250                  | °C/W  |

| TJ                      | Junction temperature                                 | - 40       | 150   |                      |       |

| Ts                      | Storage temperature                                  |            | - 55  | 150                  | °C    |

| TL                      | Lead temperature (soldering, 10 seconds)             |            |       | 260                  |       |

### 4.2 Recommended operating conditions

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM unless otherwise stated in the table.

#### Table 4 Recommended operating conditions

| Symbol           | Definition                                         | Min  | Мах             | Units |

|------------------|----------------------------------------------------|------|-----------------|-------|

| Vcc              | Fixed supply voltage                               | 12.7 | 20              |       |

| Vo               | Output voltage                                     | СОМ  | Vcc             |       |

| V <sub>OCP</sub> | Voltage at current sense pin (OCP)                 | -5   | V <sub>cc</sub> | V     |

| Ven/FLT          | Voltage at enable and fault reporting pin (EN/FLT) | 0    | V <sub>cc</sub> |       |

| V <sub>IN</sub>  | Logic input voltage ( IN )                         | - 5  | Vcc             |       |

| T <sub>A</sub>   | Ambient temperature                                | - 40 | 125             | °C    |

### 4.3 Static electrical characteristics

$V_{CC} = 15V$ ,  $T_A = 25^{\circ}C$  unless otherwise specified. The  $V_{INL}$ ,  $V_{INH}$ ,  $V_{ENL}$ ,  $V_{ENH}$ ,  $V_{OCTH}$ , and  $I_{IN}$ , IFLT parameters are referenced to COM and are applicable to input leads: IN, OCP and EN/FLT. The  $V_0$  and  $I_0$  parameters are referenced to COM and are applicable to the output lead: OUT.

#### Table 5 Static electrical characteristics

| Symbol             | Definition                                                   | Min  | Тур  | Мах  | Units | <b>Test Conditions</b>                                              |

|--------------------|--------------------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|

| V <sub>CCUV+</sub> | Vcc supply undervoltage positive going threshold             | 11.2 | 11.9 | 12.7 |       |                                                                     |

| V <sub>CCUV-</sub> | Vcc supply undervoltage negative going threshold             | 10.3 | 11   | 11.8 |       |                                                                     |

| V <sub>CCUVH</sub> | Vcc supply undervoltage lockout hysteresis                   | _    | 0.9  | _    |       |                                                                     |

| VINL               | Logic "0" input voltage (OUT = LO)                           | 0.8  | 1.0  | 1.2  |       |                                                                     |

| VINH               | Logic "1" input voltage (OUT = HI)                           | 1.9  | 2.1  | 2.3  | V     |                                                                     |

| $V_{\text{ENL}}$   | Logic "0" disable voltage                                    | 0.8  | 1.0  | 1.2  |       |                                                                     |

| V <sub>ENH</sub>   | Logic "1" enable voltage                                     | 1.9  | 2.1  | 2.3  |       |                                                                     |

| V <sub>OH</sub>    | High level output voltage, V <sub>cc</sub> -V <sub>out</sub> |      | 0.02 | 0.1  |       | I <sub>0</sub> = 2 mA                                               |

| Vol                | Low level output voltage, V <sub>OUT</sub>                   | _    | 0.02 | 0.1  |       | I <sub>0</sub> = 2 mA                                               |

| V <sub>OCTH</sub>  | Current limit threshold voltage                              | -259 | -246 | -233 | mV    |                                                                     |

| I <sub>IN+</sub>   | Logic "1" input bias current IN pin                          | 35   | 50   | 70   |       | V <sub>IN</sub> = 5 V                                               |

| I <sub>IN-</sub>   | Logic "0" input bias current IN pin                          | -10  | - 6  | —    | μA    | $V_{IN} = 0 V$                                                      |

| I <sub>QCC</sub>   | Quiescent V <sub>cc</sub> supply current                     |      | 700  | 1200 |       | $V_{IN} = 0 V \text{ or } 5 V$                                      |

| I <sub>O+</sub>    | Output sourcing short circuit pulsed current                 | 2    | 2.6  | _    | ^     | V₀=0V, PW ≤ 2 µs                                                    |

| I <sub>O-</sub>    | Output sinking short circuit pulsed current                  |      | 2.6  | _    | A     | $V_0 = 15 V$ , PW $\leq 2 \mu s$                                    |

| FLT                | EN/FLT pull down sinking current                             | 18   | _    | _    | mA    | $V_{EN}/\overline{FLT} = 0.4 V$                                     |

| V <sub>ACTSD</sub> | Active shut down voltage                                     | _    | 2.0  | 2.3  | V     | V <sub>cc</sub> = open,<br>I <sub>out-</sub> /I <sub>o-</sub> = 0.1 |

### 4.4 Dynamic electrical characteristics

$V_{CC}$  = 15 V,  $T_{A}$  = 25°C, and  $C_{L}$  = 1000 pF unless otherwise specified.

#### Table 6Dynamic electrical characteristics

| Symbol             | Definition                                | Min | Тур | Мах | Units | <b>Test Conditions</b>                                                                                   |

|--------------------|-------------------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------------------------------------------|

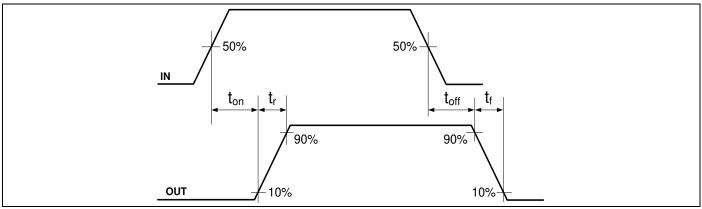

| t <sub>on</sub>    | Turn-on propagation delay                 |     | 50  | 75  |       |                                                                                                          |

| t <sub>off</sub>   | Turn-off propagation delay                | —   | 50  | 75  |       | Figure 6                                                                                                 |

| tr                 | Turn-on rise time                         | —   | 5   |     |       | V <sub>IN</sub> pulse = 5 V                                                                              |

| t <sub>f</sub>     | Turn-off fall time                        | —   | 5   |     |       |                                                                                                          |

| t <sub>DISA</sub>  | Disable propagation delay                 | _   | 50  | 75  | ns    | Figure 12<br>V <sub>EN</sub> pulse = 5 V                                                                 |

| tocpdel            | Over current protection propagation delay | _   | 230 | 350 |       | Figure 9, Figure 10                                                                                      |

| tocpflt            | OCP to low level EN/FLT signal delay      | _   | 200 | 320 |       | $R_{EN} = 10 \text{ k}\Omega \text{ to } V_{CC}$<br>$V_{OCP} \text{ pulse} = -0.5 \text{ V}$             |

| t <sub>fltc</sub>  | FAULT clear time                          | 80  | 103 | 130 | μs    | Figure 9, Figure 10<br>$V_{cc}$ = 3.3 V<br>$R_{FLTC}$ = 1M $\Omega$ to Vdd,<br>$C_{FLTC}$ = 150pF to COM |

| t <sub>BLK</sub>   | Over current protection blanking time     | 100 | 180 | 250 | ns    | $R_{FLT} = 0 \Omega, C_{FLT} = NC$<br>$V_{OCP}$ pulse = - 0.5 V                                          |

| tv <sub>ccuv</sub> | V <sub>cc</sub> supply UVLO filter time * | _   | 2   | _   | μs    | Figure 8                                                                                                 |

\*Parameter verified by design, not tested in production.

# 5 Application information and additional details

Information regarding the following topics is included as subsections within this section of the datasheet.

- IGBT gate driver

- Switching and timing relationships

- Input logic compatibility

- Undervoltage lockout protection

- Over current protection (OCP)

- Fault reporting and programmable fault clear timer

- Enable input

See the **1ED44175N01B application note AN2019-37** Low - side driver with over current protection and fault/enable (negative current sense) for interface circuit examples and recommended layout guidelines.

# 5.1 IGBT gate driver

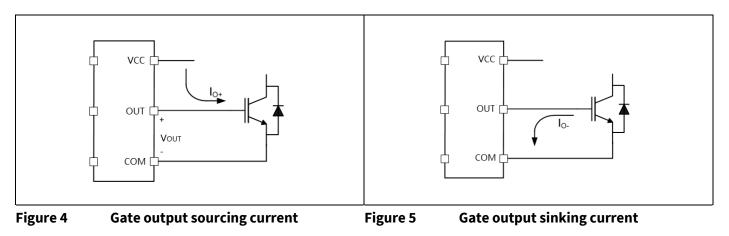

The 1ED44175N01B is designed to drive IGBT power devices. Figure 4 and Figure 5 illustrate several parameters associated with the gate driver functionality of the driver. The output current of the driver, used to drive the gate of the power switch, is defined as  $I_0$ . The voltage that drives the gate of the external power switch is defined as  $V_{OUT}$ .

# 5.2 Switching and timing relationships

The relationships between the input and output signals of the 1ED44175N01B are illustrated below Figure 6. From the figure, we can see the definitions of several timing parameters (i.e.  $t_{on}$ ,  $t_{off}$ ,  $t_r$ , and  $t_f$ ) associated with this device.

# 5.3 Input logic compatibility

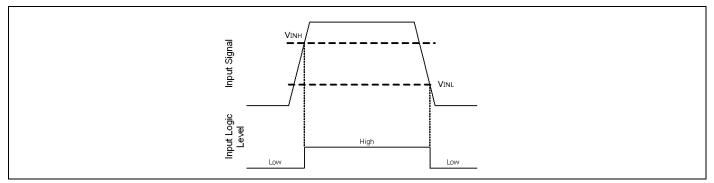

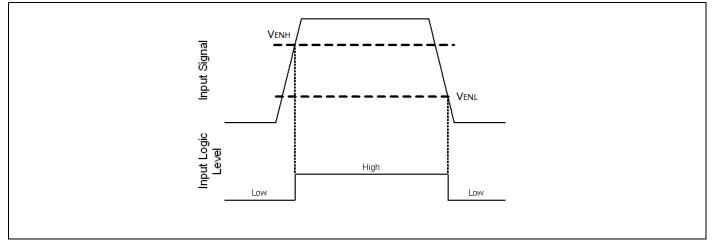

The input of this IC is compatible with standard CMOS and TTL outputs. The 1ED44175N01B has been designed to be compatible with 3.3 V, 5 V and 15 V logic-level signals. The input high threshold ( $V_{INH}$ ) is typ. 2.1 V and low threshold ( $V_{INL}$ ) is typ. 1 V. Input hysteresis offers enhanced noise immunity. The 1ED44175N01B includes an important feature: wherein, whenever the input pin is in a floating condition, the output is held in the low state. This is achieved using GND pull-down resistors on the input pin. Figure 7 illustrates an input signal to the 1ED44175N01B, its input threshold values, and the logic state of the IC as a result of the input signal.

Figure 7 IN input thresholds

# 5.4 Undervoltage lockout (V<sub>cc</sub>)

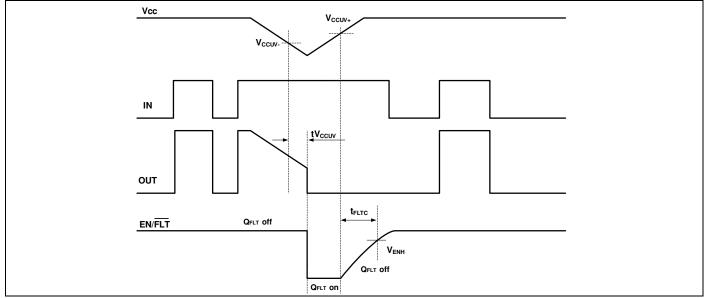

The 1ED44175N01B has internal UVLO protection feature on the  $V_{cc}$  pin supply circuit blocks. When  $V_{cc}$  bias voltage keeps lower than the  $V_{ccUV}$  threshold more than UVLO filter time ( $t_{vccUV}$ ), the  $V_{cc}$  UVLO feature holds the output low, regardless of the status of the IN input.

At the same time, the internal MOSFET  $Q_{FLT}$  turns on and the EN/FLT pin is internally pulled down to COM. The EN/FLT output stays in the low state until the UVLO has been removed; once the UVLO is removed, the internal MOSFET  $Q_{FLT}$  turns off, and the voltage on the EN/FLT pin is charged up by external voltage Vdd. The length of the fault clear time period ( $t_{FLTC}$ ) is determined by exponential charging characteristics of the capacitor where the time constant is set by  $R_{FLTC}$  and  $C_{FLTC}$ .

And when V<sub>CC</sub> is higher than V<sub>CCUV+</sub> and longer than fault clear time (t<sub>FLTC</sub>), the OUT still keeps low until next input signal IN is high. (See Figure 8)

The filter time ( $t_{vccuv}$ ) of about 2  $\mu$ s helps to suppress noise from the UVLO circuit, so that negative going voltage spikes at the supply pin will avoid parasitic UVLO events.

Figure 8 V<sub>cc</sub> under voltage protection waveform definitions

# 5.5 Over current protection (OCP)

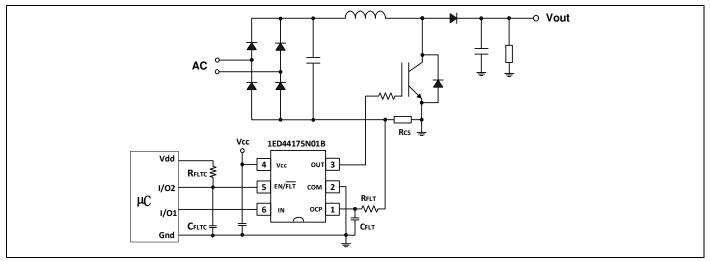

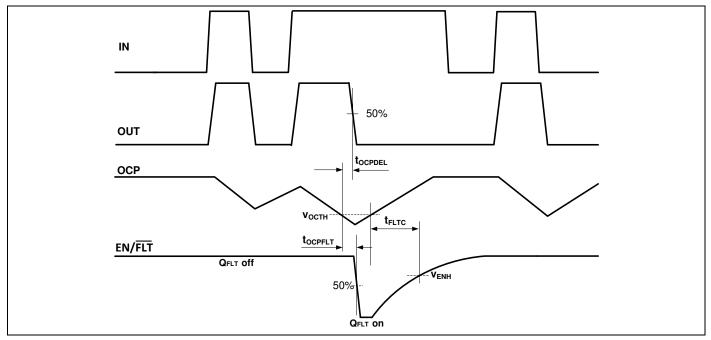

The 1ED44175N01B has a function of over current protection with a threshold  $V_{CSTH}$  at the OCP pin input. The voltage at this pin is the negative voltage drop sensed across the system current sense resistor. It is up to minus 10 VDC negative input capability of OCP pin. To avoid false tripping due to the fast high current switch on transient that occurs at the switch on of IGBT resulting from the circuit parasitic capacitors, there is a blanking interval which disables over current detection for the period of  $t_{BLK}$  (Additional RC filter is recommended, if internal  $t_{BLK}$  is not enough in the very noisy circuit.). After  $t_{BLK}$  and the voltage of OCP pin is over  $V_{CSTH}$ , the 1ED44175N01B causes fault logic to initiate a fault shutdown sequence. This sequence starts with the generation of a fault signal and internal MOSFET  $Q_{FLT}$  is turned on and EN/FLT pin is pulled down.

At the same time the 1ED44175N01B terminates the present cycle, and the gate output is immediately pulled down with internal propagation delay (t<sub>ocPDEL</sub>), see the Figure 9 and Figure 10.

Figure 9 is the diagram of 1ED44175N01B in boost application. And Figure 10 is the typical waveforms of the application. If the OCP fault condition is removed, the internal pull down NMOS of EN/FLT is released and EN/FLT will be pull up again with Vdd, but the output still keeps low until the next input signal IN is high.

Figure 9 1ED44175N01B in Boost application

Figure 10 OCP fault detection and fault clear waveforms one

### 5.6 Fault reporting and programmable fault clear timer

The 1ED44175N01B provides an integrated fault reporting output and an adjustable fault clear timer. There are two situations that would cause the driver to report a fault via the  $EN/\overline{FLT}$  pin. The first is an under voltage condition of V<sub>cc</sub> and the second is if the OCP pin recognizes a fault. Once the fault condition occurs, the  $EN/\overline{FLT}$  pin is internally pulled to COM. The  $EN/\overline{FLT}$  output stays in the low state until the fault condition has been removed and the internal pull down NMOS Q<sub>FLT</sub> turns off, the voltage on the  $EN/\overline{FLT}$  pin is charged up with external pull-up voltage.

The length of the fault clear time period ( $t_{FLTC}$ ) is determined by exponential charging characteristics of the capacitor where the time constant is set by  $R_{FLTC}$  and  $C_{FLTC}$ . Figure 9 shows that  $R_{FLTC}$  is connected between the external supply (Vdd) and the  $EN/\overline{FLT}$  pin, while  $C_{FLTC}$  is placed between the  $EN/\overline{FLT}$  and COM pins.  $EN/\overline{FLT}$  is weakly pulled up to 3.3 V reference voltage with 2.15 M resistor internally. So the length of the fault clear time period can be determined by using the formula below (If Vdd = 3.3 V).

$$t_{FLTC} = -\left(\frac{R_{FLTC} \times 2.15M}{R_{FLTC} + 2.15M}\right) \times C_{FLTC} \times \ln\left(1 - \frac{V_{ENH}}{V_{dd}}\right)$$

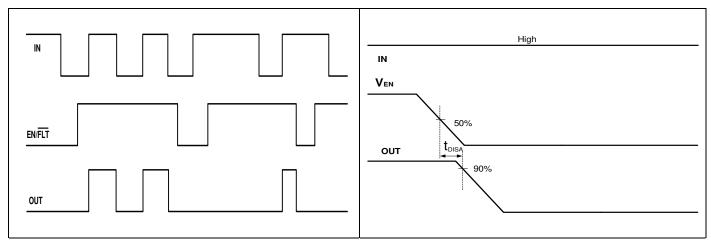

### 5.7 Enable input

1ED44175N01B provides an enable functionality that allows to shutdown or to enable the output. When EN/FLT is pulled up (the enable voltage is higher than  $V_{ENH}$ ) the output is able to operate normally, pulling EN/FLT low (the enable voltage is lower than  $V_{ENL}$ ) the output is disable. The relationships between the input, output and enable signals of the 1ED44175N01B are illustrated below in Figure 11~13. From these figures, we can see the definitions of several timing parameters and threshold voltages (i.e.  $t_{DISA}$ ,  $V_{ENH}$  and  $V_{ENL}$ ) associated with this device.

Figure 11 Input/output/enable pins timing diagram Figure 12 EN pin switching time waveform

Figure 13 EN input thresholds

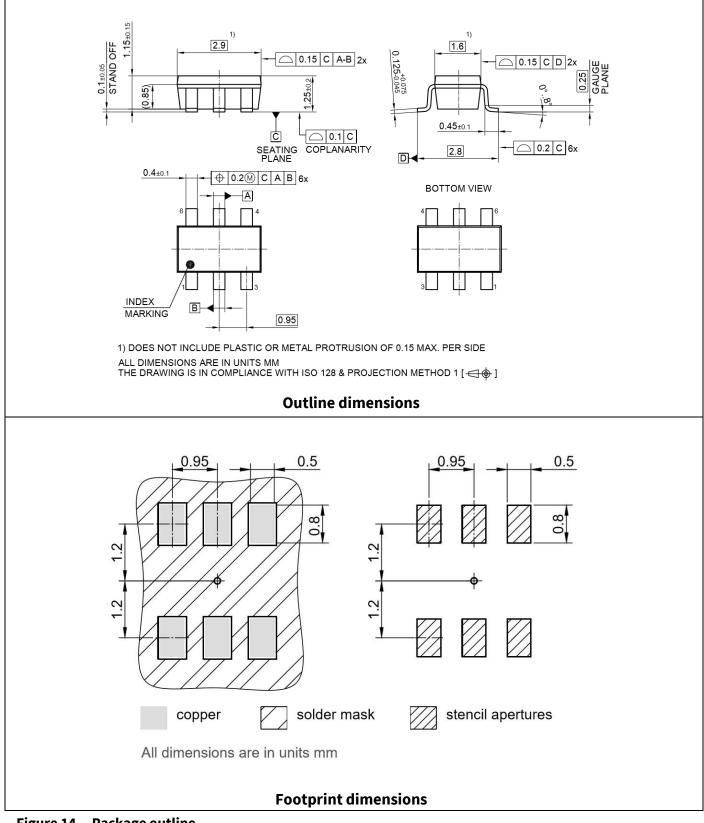

# 6 Package outline: PG-SOT23-6-3

Figure 14 Package outline

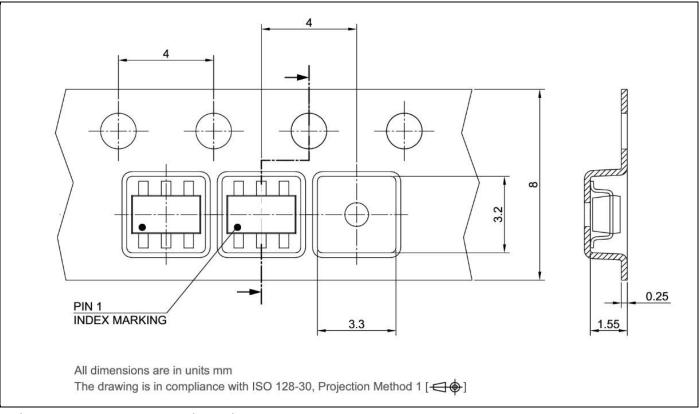

# 7 Tape and reel details

Figure 15 Tape and reel dimensions

Notes: For further details, please visit <u>www.infineon.com/packages</u>

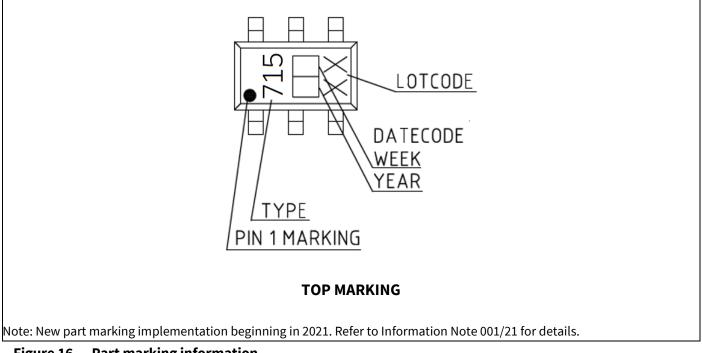

# 8 Part marking information

### Figure 16 Part marking information

# 9 Similar products

| Channels | Typ. gate<br>drive<br>(Io+/Io-) | Part<br>number | Max<br>supply<br>voltage | UVLO<br>(on/off) | Typ.<br>prop.<br>delay<br>(on/off) | Logic and features                                       | Package<br>options |

|----------|---------------------------------|----------------|--------------------------|------------------|------------------------------------|----------------------------------------------------------|--------------------|

|          | Α                               |                | V                        | V                | ns                                 |                                                          |                    |

|          | 1.5/1.5                         | IR44273L       | 20                       | 5 / 4.15         | 50 / 50                            | Single non-inverting channel<br>Dual OUT pins            | SOT23-5L           |

| 1        | 0.8/1.75                        | 1ED44176       | 25                       | 11.9/11.4        | 50 / 50                            | Single positive current sense OCP, fault out and ENABLE  | PG-DSO-8           |

|          | 2.6/2.6                         | 1ED44173       | 25                       | 8/7.3            | 34 / 34                            | Single negative current sense OCP, fault out and ENABLE  | SOT23-6-3          |

|          |                                 | IRS4426S       | 25                       |                  | 50 / 50                            | Dual inverting channels                                  | SOIC-8L            |

|          | 2.3 / 3.3                       | IRS44262S      | 20                       | 10.2 / 9.2       | 50 / 50                            | Dual inverting channels                                  | SOIC-8L            |

| 2        | 2.5 / 3.3                       | IRS4427S       | 25                       |                  | 50 / 50                            | Dual non-inverting channels                              | SOIC-8L            |

|          |                                 | IRS4428S       | 25                       |                  | 50 / 50                            | Single inverting channel<br>Single non-inverting channel | SOIC-8L            |

|          | 10/10                           | 2ED24427       | 24                       | 11.5/10          | 40 / 55                            | Dual non-inverting channels with ENABLE                  | Power Pad<br>DSO-8 |

# **10** Related documents

- 1. AN2019-37 Low side IGBT driver with over current protection and fault/enable (negative current sense)

- 2. Datasheet of **1ED44173N01B** and **1ED44176N01B**

# **Revision history**

| Document<br>version | Date of release | Description of changes                                                                                                                                         |

|---------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                 | Oct. 15, 2019   | Final Datasheet                                                                                                                                                |

| 1.1                 | Apr. 15, 2020   | Modified the formula of t <sub>FLTC</sub> on page 12 (Added negative sign)                                                                                     |

| 1.2                 | Jul. 22, 2021   | Updated the marking, adding a line for lot code to improve traceability.<br>Updated the table of similar products (Deleted Gen.7 parts and added<br>2ED24427). |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-07-22

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

**Document reference**

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.