# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# LMV721/LMV722 10MHz, Low Noise, Low Voltage, and Low Power Operational Amplifier

## **General Description**

The LMV721 (Single) and LMV722 (Dual) are low noise, low voltage, and low power op amps, that can be designed into a wide range of applications. The LMV721/LMV722 has a unity gain bandwidth of 10MHz, a slew rate of 5V/us, and a quiescent current of 930uA/amplifier at 2.2V.

The LMV721/722 are designed to provide optimal performance in low voltage and low noise systems. They provide rail-to-rail output swing into heavy loads. The input commonmode voltage range includes ground, and the maximum input offset voltage are 3.5mV (Over Temp.) for the LMV721/LMV722. Their capacitive load capability is also good at low supply voltages. The operating range is from 2.2V to 5.5V.

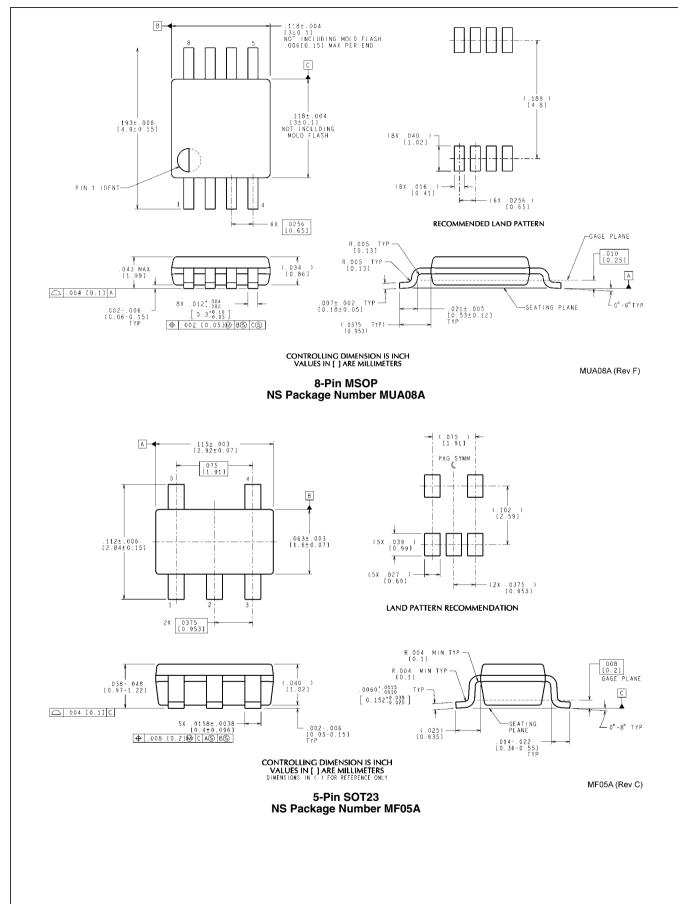

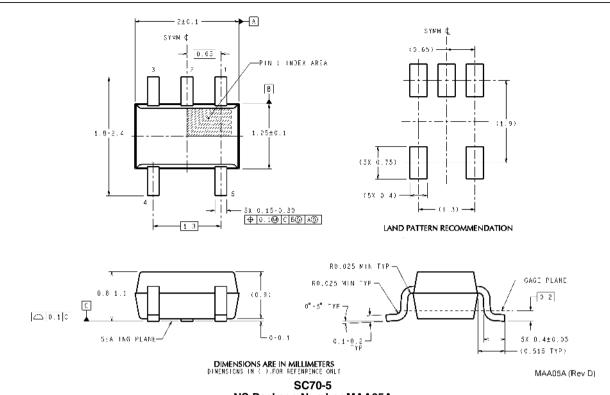

The chip is built with National's advanced Submicron Silicon-Gate BiCMOS process. The single version, LMV721, is available in 5 pin SOT23-5 and a SC-70 (new) package. The dual version, LMV722, is available in a SO-8, MSOP-8 and 8-pin LLP package.

### **Features**

(For Typical, 5 V Supply Values; Unless Otherwise Noted)

- Guaranteed 2.2V and 5.0V Performance

- Low Supply Current LMV721/2 930µA/amplifier @2.2V

- High Unity-Gain Bandwidth 10MHz

- Rail-to-Rail Output Swing

@600Ω load 120mV from either rail at 2.2V

@2kΩ load 50mV from either rail at 2.2V

- Input Common Mode Voltage Range Includes Ground

- Silicon Dust<sup>™</sup>, SC70-5 Package 2.0x2.0x1.0 mm

- Miniature packaging: LLP-8 2.5mm × 3mm × 0.8mm

- Input Voltage Noise 9 nV/√Hz @ f = 1KHz

## **Applications**

- Cellular an Cordless Phones

- Active Filter and Buffers

- Laptops and PDAs

- Battery Powered Electronics

# **Typical Application**

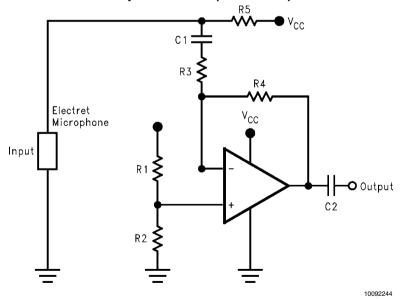

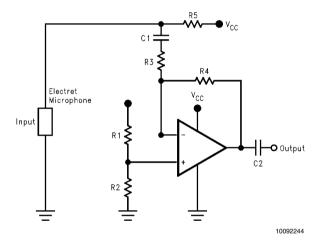

#### A Battery Powered Microphone Preamplifier

Silicon Dust™ is a trademark of National Semiconductor Corporation

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

ESD Tolerance (Note 2)

$\begin{array}{lll} \mbox{Human Body Model} & 2000\mbox{V} \\ \mbox{Machine Model} & 100\mbox{V} \\ \mbox{Differential Input Voltage} & \pm \mbox{Supply Voltage} \end{array}$

Supply Voltage  $(V^+ - V^-)$ Soldering Information

Infrared or Convection (20 sec.) 235°C

Storage Temp. Range -65°C to 150°C Junction Temperature (Note 4) 150°C

## **Operating Ratings** (Note 3)

Supply Voltage 2.2V to 5.5V Temperature Range  $-40^{\circ}\text{C} \leq \text{T}_{\perp} \leq 85^{\circ}\text{C}$

Thermal Resistance  $(\theta_{JA})$

Silicon Dust SC70-5 Pkg 440°C/W

Tiny SOT23-5 Pkg 265 °C/W

SO Pkg, 8-pin Surface Mount 190°C/W

MSOP Pkg, 8-Pin Mini Surface 235 °C/W

Mount

SO Pkg, 14-Pin Surface Mount 145°C/W LLP pkg, 8-Pin 58.2°C/W

## 2.2V DC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J$  = 25°C.  $V^+$  = 2.2V,  $V^-$  = 0V,  $V_{CM}$  = V+/2,  $V_O$  = V+/2 and  $R_L$  > 1  $M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                          | Condition                                            | Typ<br>(Note 5) | Limit<br>(Note 6)     | Units     |

|-------------------|------------------------------------|------------------------------------------------------|-----------------|-----------------------|-----------|

| V <sub>OS</sub>   | Input Offset Voltage               |                                                      | 0.02            | 3                     | mV        |

| 03                |                                    |                                                      |                 | 3.5                   | max       |

| TCV <sub>os</sub> | Input Offset Voltage Average Drift |                                                      | 0.6             |                       | μV/°C     |

| I <sub>B</sub>    | Input Bias Current                 |                                                      | 260             |                       | nA        |

| I <sub>os</sub>   | Input Offset Current               |                                                      | 25              |                       | nA        |

| CMRR              | Common Mode Rejection Ratio        | $0V \le V_{CM} \le 1.3V$                             | 88              | 70<br><b>64</b>       | dB<br>min |

| PSRR              | Power Supply Rejection Ratio       | $2.2V \le V^{+} \le 5V$ , $V_{O} = 0$ $V_{CM} = 0$   | 90              | 70<br><b>64</b>       | dB<br>min |

| V <sub>CM</sub>   | Input Common-Mode Voltage Range    | For CMRR ≥ 50dB                                      | -0.30           |                       | V         |

|                   |                                    |                                                      | 1.3             |                       | V         |

| $\overline{A_V}$  | Large Signal Voltage Gain          | $R_L = 600\Omega$<br>$V_O = 0.75V \text{ to } 2.00V$ | 81              | 75<br><b>60</b>       | dB<br>min |

|                   |                                    | $R_L = 2k\Omega$<br>$V_O = 0.50V$ to 2.10V           | 84              | 75<br><b>60</b>       | dB<br>min |

| Vo                | Output Swing                       | $R_L = 600\Omega$ to V+/2                            | 2.125           | 2.090<br><b>2.065</b> | V<br>min  |

|                   |                                    |                                                      | 0.071           | 0.120<br><b>0.145</b> | V<br>max  |

|                   |                                    | $R_L = 2k\Omega$ to V+/2                             | 2.177           | 2.150<br><b>2.125</b> | V<br>min  |

|                   |                                    |                                                      | 0.056           | 0.080<br><b>0.105</b> | V<br>max  |

| Io                | Output Current                     | Sourcing, $V_O = 0V$<br>$V_{IN}(diff) = \pm 0.5V$    | 14.9            | 10.0<br><b>5.0</b>    | mA<br>min |

|                   |                                    | Sinking, $V_O = 2.2V$<br>$V_{IN}(diff) = \pm 0.5V$   | 17.6            | 10.0<br><b>5.0</b>    | mA<br>min |

| I <sub>S</sub>    | Supply Current                     | LMV721                                               | 0.93            | 1.2<br><b>1.5</b>     | mA        |

|                   |                                    | LMV722                                               | 1.81            | 2.2<br><b>2.6</b>     | max       |

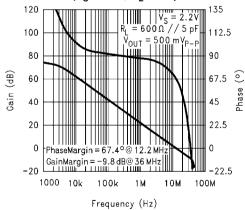

## 2.2V AC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J$  = 25°C.  $V^+$  = 2.2V,  $V^-$  = 0V,  $V_{CM}$  = V+/2,  $V_O$  = V+/2 and  $R_L$  > 1  $M\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                    | Conditions                                                                   | Typ<br>(Note 5) | Units     |

|----------------|------------------------------|------------------------------------------------------------------------------|-----------------|-----------|

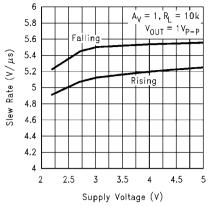

| SR             | Slew Rate                    | (Note 7)                                                                     | 4.9             | V/µs      |

| GBW            | Gain-Bandwidth Product       |                                                                              | 10              | MHz       |

| Φ <sub>m</sub> | Phase Margin                 |                                                                              | 67.4            | Deg       |

| G <sub>m</sub> | Gain Margin                  |                                                                              | -9.8            | dB        |

| e <sub>n</sub> | Input-Referred Voltage Noise | f = 1 kHz                                                                    | 9               | nV<br>√Hz |

| i <sub>n</sub> | Input-Referred Current Noise | f = 1 kHz                                                                    | 0.3             | pA<br>√Hz |

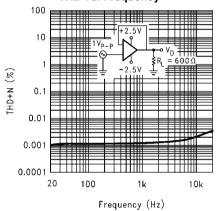

| THD            | Total Harmonic Distortion    | $f = 1 \text{ kHz } A_V = 1$<br>$R_L = 600\Omega, V_O = 500 \text{ mV}_{PP}$ | 0.004           | %         |

## **5V DC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $V_O = V^+/2$  and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                          | Condition                                            | Typ<br>(Note 5) | Limit<br>(Note 6)     | Units     |

|-------------------|------------------------------------|------------------------------------------------------|-----------------|-----------------------|-----------|

| V <sub>os</sub>   | Input Offset Voltage               |                                                      | -0.08           | 3                     | mV        |

|                   |                                    |                                                      |                 | 3.5                   | max       |

| TCV <sub>os</sub> | Input Offset Voltage Average Drift |                                                      | 0.6             |                       | μV/°C     |

| I <sub>B</sub>    | Input Bias Current                 |                                                      | 260             |                       | nA        |

| os                | Input Offset Current               |                                                      | 25              |                       | nA        |

| CMRR              | Common Mode Rejection Ratio        | 0V ≤ V <sub>CM</sub> ≤ 4.1V                          | 89              | 70<br><b>64</b>       | dB<br>min |

| PSRR              | Power Supply Rejection Ratio       | $2.2V \le V^+ \le 5.0V, V_0 = 0 V_{CM} = 0$          | 90              | 70<br><b>64</b>       | dB<br>min |

| V <sub>CM</sub>   | Input Common-Mode Voltage Range    | For CMRR ≥ 50dB                                      | -0.30           |                       | V         |

|                   |                                    |                                                      | 4.1             |                       | V         |

| A <sub>V</sub>    | Large Signal Voltage Gain          | $R_L = 600\Omega$<br>$V_O = 0.75V \text{ to } 4.80V$ | 87              | 80<br><b>70</b>       | dB<br>min |

|                   |                                    | $R_L = 2k\Omega$ ,<br>$V_O = 0.70V$ to 4.90V,        | 94              | 85<br><b>70</b>       | dB<br>min |

| Vo                | Output Swing                       | $R_L = 600\Omega \text{ to V+/2}$                    | 4.882           | 4.840<br><b>4.815</b> | V<br>min  |

|                   |                                    |                                                      | 0.134           | 0.190<br><b>0.215</b> | V<br>max  |

|                   |                                    | $R_L = 2k\Omega$ to V+/2                             | 4.952           | 4.930<br><b>4.905</b> | V<br>min  |

|                   |                                    |                                                      | 0.076           | 0.110<br><b>0.135</b> | V<br>max  |

| I <sub>o</sub>    | Output Current                     | Sourcing, $V_O = 0V$<br>$V_{IN}(diff) = \pm 0.5V$    | 52.6            | 25.0<br><b>12.0</b>   | mA<br>min |

|                   |                                    | Sinking, $V_O = 5V$<br>$V_{IN}(diff) = \pm 0.5V$     | 23.7            | 15.0<br><b>8.5</b>    | mA<br>min |

| I <sub>S</sub>    | Supply Current                     | LMV721                                               | 1.03            | 1.4<br><b>1.7</b>     | mA        |

|                   |                                    | LMV722                                               | 2.01            | 2.4<br><b>2.8</b>     | max       |

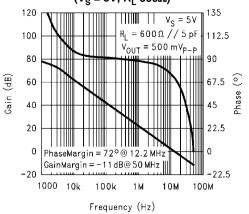

### **5V AC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ ,  $V_O = V^+/2$  and  $R_L > 1$  M $\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                    | Conditions                                            | Typ<br>(Note 5) | Units     |

|----------------|------------------------------|-------------------------------------------------------|-----------------|-----------|

| SR             | Slew Rate                    | (Note 7)                                              | 5.25            | V/µs      |

| GBW            | Gain-Bandwidth Product       |                                                       | 10.0            | MHz       |

| Φ <sub>m</sub> | Phase Margin                 |                                                       | 72              | Deg       |

| G <sub>m</sub> | Gain Margin                  |                                                       | -11             | dB        |

| e <sub>n</sub> | Input-Related Voltage Noise  | f = 1 kHz                                             | 8.5             | nV<br>√Hz |

| i <sub>n</sub> | Input-Referred Current Noise | f = 1 kHz                                             | 0.2             | pA<br>√Hz |

| THD            | Total Harmonic Distortion    | $f = 1kHz, A_V = 1$ $R_L = 600\Omega, V_O = 1 V_{PP}$ | 0.001           | %         |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human body model, 1.5 k $\Omega$  in series with 100 pF. Machine model,  $200\Omega$  in series with 100 pF.

**Note 3:** Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of 30 mA over long term may adversely affect reliability.

Note 4: The maximum power dissipation is a function of  $T_{J(max)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(max)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

Note 5: Typical Values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Connected as voltage follower with 1V step input. Number specified is the slower of the positive and negative slew rate.

# **Typical Performance Characteristics**

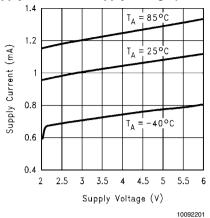

#### Supply Current vs. Supply Voltage (LMV721)

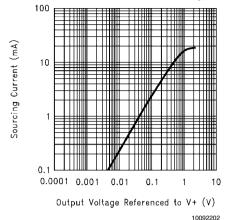

### Sourcing Current vs. Output Voltage ( $V_S = 2.2V$ )

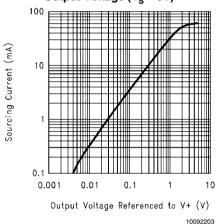

# Sourcing Current vs. Output Voltage $(V_S = 5V)$

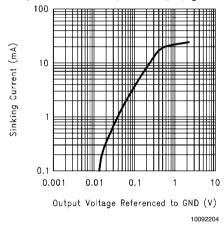

## Sinking Current vs. Output Voltage (V<sub>S</sub> = 2.2V)

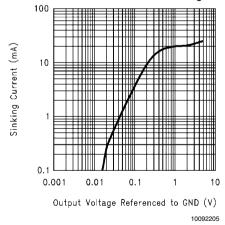

## Sinking Current vs. Output Voltage $(V_S = 5V)$

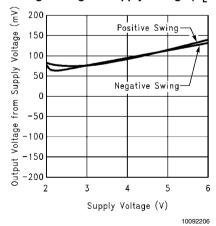

### Output Voltage Swing vs. Supply Voltage ( $R_1 = 600\Omega$ )

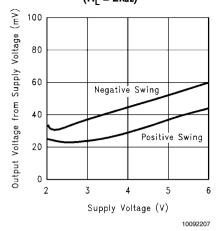

# Output Voltage Swing vs. Suppy Voltage $(R_1 = 2k\Omega)$

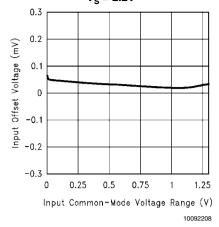

# Input Offset Voltage vs. Input Common-Mode Voltage Range $\rm V_S = 2.2V$

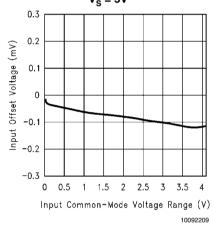

# Input Offset Voltage vs. Input Common-Mode Voltage Range $V_S = 5V$

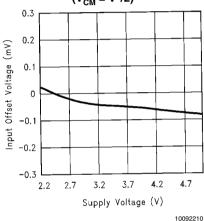

# Input Offset Voltage vs. Supply Voltage $(V_{CM} = V^{+}/2)$

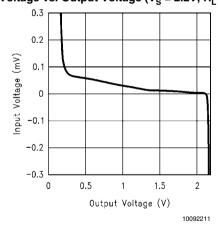

Input Voltage vs. Output Voltage ( $V_S = 2.2V$ ,  $R_L = 2k\Omega$ )

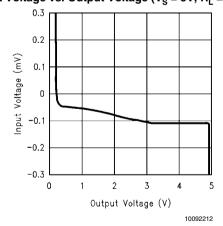

## Input Voltage vs. Output Voltage ( $V_S = 5V$ , $R_L = 2k\Omega$ )

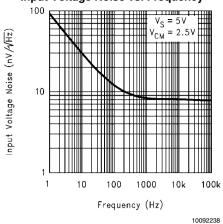

### Input Voltage Noise vs. Frequency

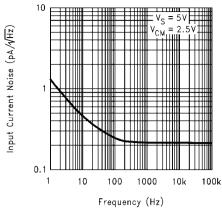

## Input Current Noise vs. Frequency

10092232

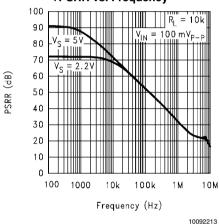

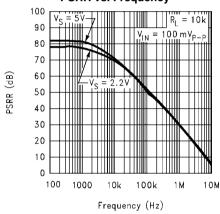

### +PSRR vs. Frequency

### -PSRR vs. Frequency

10092214

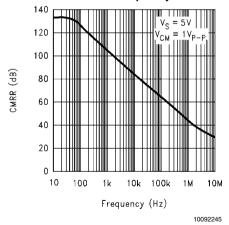

#### CMRR vs. Frequency

# Gain and Phase Margin vs. Frequency ( $V_S = 2.2V, R_L 600\Omega$ )

10092215

# Gain and Phase Margin vs. Frequency ( $V_S$ = 5V, $R_L$ 600 $\Omega$ )

10092216

### THD vs. Frequency

10092242

### Slew Rate vs. Supply Voltage

10092217

## **Application Notes**

#### 1.0 BENEFITS OF THE LMV721/722 SIZE

The small footprints of the LMV721/722 packages save space on printed circuit boards, and enable the design of smaller electronic products, such as cellular phones, pagers, or other portable systems. The low profile of the LMV721/722 make them possible to use in PCMCIA type III cards.

**Signal Integrity.** Signals can pick up noise between the signal source and the amplifier. By using a physically smaller amplifier package, the LMV721/722 can be placed closer to the signal source, reducing noise pickup and increasing signal integrity.

**Simplified Board Layout.** These products help you to avoid using long pc traces in your pc board layout. This means that no additional components, such as capacitors and resistors, are needed to filter out the unwanted signals due to the interference between the long pc traces.

Low Supply Current. These devices will help you to maximize battery life. They are ideal for battery powered systems.

**Low Supply Voltage.** National provides guaranteed performance at 2.2V and 5V. These guarantees ensure operation throughout the battery lifetime.

Rail-to-Rail Output. Rail-to-rail output swing provides maximum possible dynamic range at the output. This is particularly important when operating on low supply voltages.

**Input Includes Ground.** Allows direct sensing near GND in single supply operation.

Protection should be provided to prevent the input voltages from going negative more than -0.3V (at 25°C). An input clamp diode with a resistor to the IC input terminal can be used.

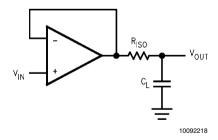

#### 2.0 CAPACITIVE LOAD TOLERANCE

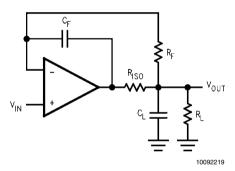

The LMV721/722 can directly drive 4700pF in unity-gain without oscillation. The unity-gain follower is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers. The combination of the amplifier's output impedance and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation. To drive a heavier capacitive load, circuit in Figure 1 can be used.

FIGURE 1. Indirectly Driving A capacitive Load Using Resistive Isolation

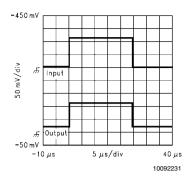

In Figure 1, the isolation resistor  $R_{\rm ISO}$  and the load capacitor  $C_L$  form a pole to increase stability by adding more phase margin to the overall system. the desired performance depends on the value of  $R_{\rm ISO}$ . The bigger the  $R_{\rm ISO}$  resistor value, the more stable  $V_{\rm OUT}$  will be. Figure 2 is an output waveform of Figure 1 using  $100 k\Omega$  for  $R_{\rm ISO}$  and  $2000 \mu F$  for  $C_L$ .

FIGURE 2. Pulse Response of the LMV721 Circuit in Figure 1

The circuit in Figure 3 is an improvement to the one in Figure 1 because it provides DC accuracy as well as AC stability. If there were a load resistor in Figure 1, the output would be voltage divided by  $R_{\rm ISO}$  and the load resistor. Instead, in Figure 3,  $R_{\rm F}$  provides the DC accuracy by using feed-forward techniques to connect  $V_{\rm IN}$  to  $R_{\rm L}$ . Caution is needed in choosing the value of  $R_{\rm F}$  due to the input bias current of the LMV721/722.  $C_{\rm F}$  and  $R_{\rm ISO}$  serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier's inverting input, thereby preserving phase margin in the overall feedback loop. Increased capacitive drive is possible by increasing the value of  $C_{\rm E}$ . This in turn will slow down the pulse response.

FIGURE 3. Indirectly Driving A Capacitive Load with DC Accuracy

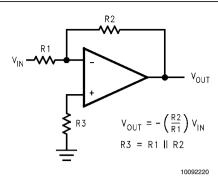

#### 3.0 INPUT BIAS CURRENT CANCELLATION

The LMV721/722 family has a bipolar input stage. The typical input bias current of LMV721/722 is 260nA with 5V supply. Thus a  $100 k\Omega$  input resistor will cause 26mV of error voltage. By balancing the resistor values at both inverting and noninverting inputs, the error caused by the amplifier's input bias current will be reduced. The circuit in Figure 4 shows how to cancel the error caused by input bias current.

FIGURE 4. Cancelling the Error Caused by Input Bias Current

#### 4.0 TYPICAL SINGLE-SUPPLY APPLICATION CIRCUITS

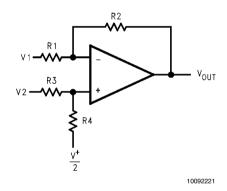

#### 4.1 Difference Amplifier

The difference amplifier allows the subtraction of two voltages or, as a special case, the cancellation of a signal common to two inputs. It is useful as a computational amplifier, in making a differential to single-ended conversion or in rejecting a common mode signal.

$$\begin{split} &V_{OUT} = \left(\frac{R1 + R2}{R3 + R4}\right)\frac{R4}{R1}V_2 - \frac{R2}{R1}V_1 + \left(\frac{R1 + R2}{R3 + R4}\right)\frac{R3}{R1} \cdot \frac{V^+}{2} \\ &\text{for R1} = R3 \text{ and } R2 = R4 \\ &V_{OUT} = \frac{R2}{R1}\left(V_2 - V_1\right) + \frac{V^+}{2} \end{split}$$

FIGURE 5. Difference Application

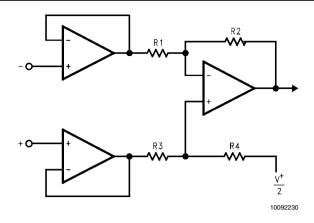

#### 4.2 Instrumentation Circuits

The input impendance of the previous difference amplifier is set by the resistor  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$ . To eliminate the problems of low input impendance, one way is to use a voltage follower ahead of each input as shown in the following two instrumentation amplifiers.

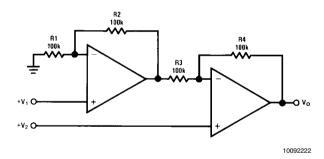

#### 4.2.1 Three-op-amp Instrumentation Amplifier

The LMV721/722 can be used to build a three-op-amp instrumentation amplifier as shown in Figure 6

FIGURE 6. Three-op-amp Instrumentation Amplifier

The first stage of this instrumentation amplifier is a differential-input, differential-output amplifier, with two voltage followers. These two voltage followers assure that the input impedance is over  $100 M\Omega$ . The gain of this instrumentation amplifier is set by the ratio of  $R_2/R_1,\ R_3$  should equal  $R_1$  and  $R_4$  equal  $R_2.$  Matching of  $R_3$  to  $R_1$  and  $R_4$  to  $R_2$  affects the CMRR. For good CMRR over temperature, low drift resistors should be used. Making  $R_4$  slightly smaller than  $R_2$  and adding a trim pot equal to twice the difference between  $R_2$  and  $R_4$  will allow the CMRR to be adjusted for optimum.

#### 4.2.2 Two-op-amp Instrumentation Amplifier

A two-op-amp instrumentation amplifier can also be used to make a high-input impedance DC differential amplifier (Figure 7). As in the two-op-amp circuit, this instrumentation amplifier requires precise resistor matching for good CMRR.  $R_4$  should equal to  $R_1$  and  $R_3$  should equal  $R_2$ .

$$V_{O} = \left(1 + \frac{R4}{R3}\right) \left(V_{2} - V_{1}\right)$$

, where R1 = R4 and R2 = R3 As shown:  $V_{O} = 2 \left(V_{2} - V_{1}\right)$

FIGURE 7. Two-op-amp Instrumentation Amplifier

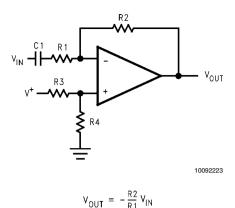

#### 4.3 Single-Supply Inverting Amplifier

There may be cases where the input signal going into the amplifier is negative. Because the amplifier is operating in single supply voltage, a voltage divider using  $R_3$  and  $R_4$  is implemented to bias the amplifier so the input signal is within the input common-common voltage range of the amplifier. The capacitor  $C_1$  is placed between the inverting input and resistor  $R_1$  to block the DC signal going into the AC signal source,  $V_{IN}$ . The values of  $R_1$  and  $C_1$  affect the cutoff frequency, fc =  $\frac{1}{2}\pi$   $R_1C_1$ .

As a result, the output signal is centered around mid-supply (if the voltage divider provides V+/2 at the non-inverting input).

The output can swing to both rails, maximizing the signal-tonoise ratio in a low voltage system.

FIGURE 8. Single-Supply Inverting Amplifier

#### 4.4 Active Filter

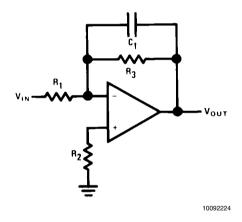

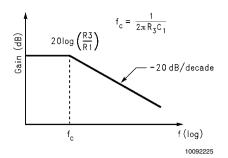

#### 4.4.1 Simple Low-Pass Active Filter

The simple low-pass filter is shown in Figure 9. Its low-pass frequency gain  $(\omega \to o)$  is defined by  $-R_3/R_1$ . This allows low-frequency gains other than unity to be obtained. The filter has a -20dB/decade roll-off after its corner frequency fc.  $R_2$  should be chosen equal to the parallel combination of  $R_1$  and  $R_3$  to minimize error due to bias current. The frequency response of the filter is shown in Figure 10.

$A_{L} = -\frac{R_{3}}{R_{1}}$   $f_{c} = \frac{1}{2\pi R_{3}C_{1}}$   $R_{2} = R_{1} || R_{3}$

FIGURE 9. Simple Low-Pass Active Filter

FIGURE 10. Frequency Response of Simple Low-pass Active Filter in Figure 9

Note that the single-op-amp active filters are used in to the applications that require low quality factor,  $Q(\le 10)$ , low frequency ( $\le 5 \text{KHz}$ ), and low gain ( $\le 10$ ), or a small value for the product of gain times  $Q(\le 100)$ . The op amp should have an open loop voltage gain at the highest frequency of interest at least 50 times larger than the gain of the filter at this frequency. In addition, the selected op amp should have a slew rate that meets the following requirement:

Slew Rate  $\geq$  0.5 x ( $\omega_{H}$  V  $_{OPP})$  X 10  $^{-6}\text{V/}\mu\text{sec}$

Where  $\omega_{\text{H}}$  is the highest frequency of interest, and  $V_{\text{OPP}}$  is the output peak-to-peak voltage.

FIGURE 11. A Battery Powered Microphone Preamplifier

Here is a LMV721 used as a microphone preamplifier. Since the LMV721 is a low noise and low power op amp, it makes it an ideal candidate as a battery powered microphone preamplifier. The LMV721 is connected in an inverting configuration. Resistors,  $R_1=R_2=4.7 \mathrm{k}\Omega$ , sets the reference half way between  $V_{CC}=3V$  and ground. Thus, this configures the op amp for single supply use. The gain of the preamplifier, which is 50 (34dB), is set by resistors  $R_3=10\mathrm{k}\Omega$  and  $R_4=500\mathrm{k}\Omega$ . The gain bandwidth product for the LMV721 is 10 MHz. This is sufficient for most audio application since the audio range is typically from 20 Hz to 20kHz. A resistor  $R_5=5\mathrm{k}\Omega$  is used to bias the electret microphone. Capacitors  $C_1=C_2=4.7\mu\mathrm{F}$  placed at the input and output of the op amp to block out the DC voltage offset.

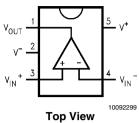

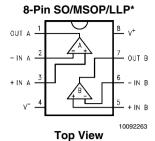

# **Connection Diagrams**

### 5-Pin SC-70/SOT23-5

**Note:** LLP-8 exposed DAP can be electrically connected to ground for improved thermal performance.

# **Ordering Information**

| Package                 | Temperature Range Industrial -40°C to +85°C | Package Marking | Transport Media          | NSC Drawing |  |

|-------------------------|---------------------------------------------|-----------------|--------------------------|-------------|--|

| 8-Pin Small Outline     | LMV722M                                     | LMV722M         | Rails                    | M08A        |  |

| o-Fili Siliali Oullille | LMV722MX                                    | LIVI V / ZZIVI  | 2.5k Units Tape and Reel |             |  |

| 0 : 14000               | LMV722MM                                    | LMV722          | 1k Units Tape and Reel   | MUA08A      |  |

| 8-pin MSOP              | LMV722MMX                                   | LIVI V 7 ZZ     | 3.5k Units Tape and Reel |             |  |

| 8-pin LLP               | LMV722LD                                    | L22             | 1k Units Tape and Reel   | LDA08C      |  |

| ο-μιτ LLF               | LMV722LDX                                   | LZZ             | 3.5k Units Tape and Reel |             |  |

| 5-Pin SOT23             | LMV721M5                                    | A20A            | 1k Units Tape and Reel   | MF05A       |  |

| 5-1111 50123            | LMV721M5X                                   | A30A            | 3k Units Tape and Reel   | INIFUSA     |  |

| 5-Pin SC-70             | LMV721M7                                    | A20             | 1k Units Tape and Reel   | MAA05A      |  |

| 5-FIII 5C-70            | LMV721M7X                                   |                 | 3k Units Tape and Reel   | ACUANIVI    |  |

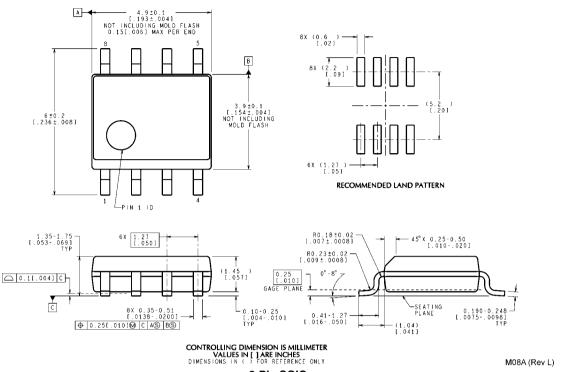

# Physical Dimensions inches (millimeters) unless otherwise noted

8-Pin SOIC NS Package Number M08A

(2.3) (8X 0.5) DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS IN ( ) FOR REFERENCE ONLY (8X 0.25) (6X 0.5) RECOMMENDED LAND PATTERN 1:1 RATIO WITH PKG SOLDER PADS -C - 0.8 MAX - (0.1) ALL LEADS PIN 1 INDEX AREA-- (0.2) (0.25)(0.2)0 1.2±0.1 PIN 1 ID 0 - 2.5±0.1 -A 2X 1.5 LDA08C (Rev B)

8-Pin LLP NS Package Number LDA08C

Ь

**NS Package Number MAA05A**

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: ion.feedback@nsc.com