AP65552

#### 5A, 18V, 650kHz ADAPTIVE CCM/COT STEP-DOWN CONVERTER

## **Description**

The AP65552 is an adaptive, constant on-time mode synchronous buck converter providing high efficiency, excellent transient response and high DC output accuracy for low-voltage regulation in digital TVs and monitors.

The constant-on-time control scheme handles wide input/output voltage ratios and provides low external component count. The internal proprietary circuit enables the device to adopt both low equivalent series resistance (ESR) Output Capacitors, such as SP-CAP or POSCAP and ultra-low ESR ceramic capacitors.

The AP65552 features programmable soft-start, UVLO, OTP and OCP to protect the circuit.

This IC is available in SO-8EP package.

### **Features**

- Fixed-Frequency Emulated Constant On-Time Control

- Good Stability Independent of the Output Capacitor ESR

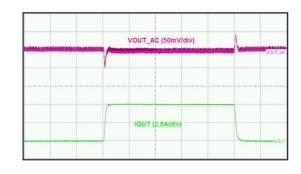

- Fast Load Transient Response

- Synchronous Rectification: 65mΩ Internal High-Side Switch and 36mΩ Internal Low-Side Switch

- Wide Input Voltage Range: 4.5V to 18V

- Output Voltage Range: 0.76V to 6V

- 5A Continuous Output Current

- 650kHz Switching Frequency

- Built-in Overcurrent Limit

- Built-in Thermal Shutdown Protection

- Programmable Soft-Start

- Pre-biased Start-Up

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

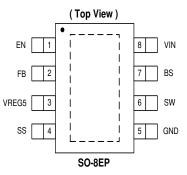

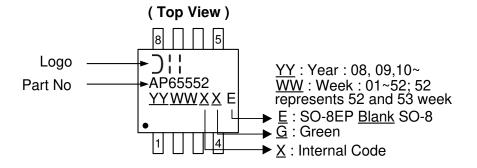

### **Pin Assignments**

# **Applications**

- Gaming Consoles

- Flat Screen TV Sets and Monitors

- Set Top Boxes

- Distributed Power Systems

- Home Audio

- Consumer Electronics

- Network Systems

- FPGA, DSP and ASIC Supplies

- Green Electronics

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

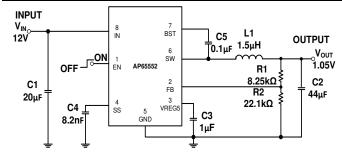

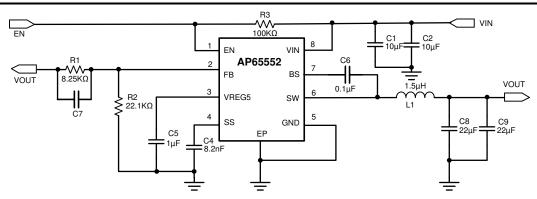

# **Typical Applications Circuit**

**Figure 1 Typical Application Circuit**

# **Pin Descriptions**

| Pin   | Pin Number | Function                                                                                                                                                                                                                            |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name  | SO-8EP     | runction                                                                                                                                                                                                                            |

| EN    | 1          | Enable input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on the regulator, drive it low to turn off. Pull up with 100kΩ resistor for automatic startup.                                        |

| FB    | 2          | Feedback Input. FB senses the output voltage and regulates it. Drive FB with a resistive voltage divider connected to it from the output voltage.                                                                                   |

| VREG5 | 3          | Internal power supply output pin to connect an additional capacitor. Connect a 1µF (typical) capacitor as close as possible to the VREG5 and GND. This pin is not active when EN is low.                                            |

| SS    | 4          | Soft-start control input pin. SS controls the soft start period. Connect a capacitor from SS to GND to set the soft-start period.                                                                                                   |

| GND   | 5          | Ground pin is the main power ground for the switching circuit.                                                                                                                                                                      |

| SW    | 6          | Power Switching Output. SW is the switching node that supplies power to the output. Connect the output LC filter from SW to the output load. Note that a capacitor is required from SW to BS to power the high-side switch.         |

| BS    | 7          | Bootstrap pin. A bootstrap capacitor is connected between the BS pin and SW pin. The voltage across the bootstrap capacitor drives the internal high-side NMOS switch. A 0.1µF (typical) capacitor is required for proper operation |

| VIN   | 8          | Supply input pin. A capacitor should be connected between the VIN pin and GND pin to keep the DC input voltage constant.                                                                                                            |

| EP    | _          | Connect the exposed thermal pad to GND on the PCB                                                                                                                                                                                   |

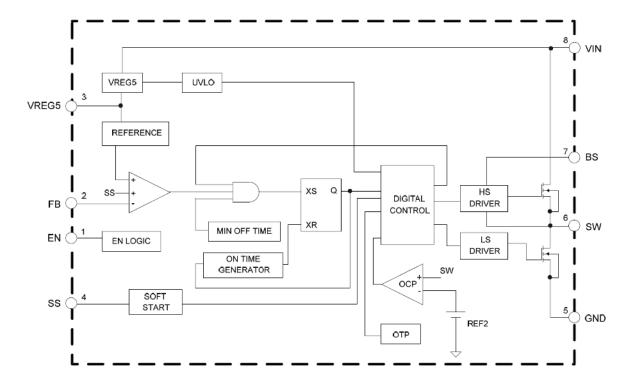

# **Functional Block Diagram**

Figure 2 Functional Block Diagram

# Absolute Maximum Ratings (Note 4) (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol             | Parameter            | Rating                       | Unit |

|--------------------|----------------------|------------------------------|------|

| V <sub>IN</sub>    | Supply Voltage       | -0.3 to +20                  | V    |

| $V_{REG5}$         | VREG5 Pin Voltage    | -0.3V to +6.0                | V    |

| V <sub>SW</sub>    | Switch Node Voltage  | -1.0 to V <sub>IN</sub> +0.3 | V    |

| $V_{BS}$           | Bootstrap Voltage    | -0.3 to V <sub>SW</sub> +6.0 | V    |

| $V_{FB}$           | Feedback Voltage     | -0.3V to +6.0                | V    |

| V <sub>EN</sub>    | Enable/UVLO Voltage  | -0.3V to +6.0                | V    |

| V <sub>SS</sub>    | Soft-Start PIN       | -0.3V to +6.0                | V    |

| $V_{GND}$          | GND Pin Voltage      | -0.3 to +0.3                 | V    |

| T <sub>ST</sub>    | Storage Temperature  | -65 to +150                  | °C   |

| TJ                 | Junction Temperature | +160                         | °C   |

| T <sub>L</sub>     | Lead Temperature     | +260                         | °C   |

| ESD Susceptibility | (Note 5)             | •                            | ·    |

| HBM                | Human Body Model     | 2                            | kV   |

| MM                 | Machine Model        | 200                          | V    |

Notes:

# Thermal Resistance (Note 6)

| Symbol          | Parameter           | Rat    | ing  | Unit |

|-----------------|---------------------|--------|------|------|

| $\theta_{JA}$   | Junction to Ambient | SO-8EP | 39.4 | °C/W |

| θ <sub>JC</sub> | Junction to Case    | SO-8EP | 8.6  | °C/W |

# Recommended Operating Conditions (Note 7) (@TA = +25°C, unless otherwise specified.)

| Symbol                                              | Parameter | Min | Max  | Unit |

|-----------------------------------------------------|-----------|-----|------|------|

| V <sub>IN</sub> Supply Voltage                      |           | 4.5 | 18.0 | V    |

| T <sub>J</sub> Operating Junction Temperature Range |           | -40 | +125 | °C   |

| T <sub>A</sub> Operating Ambient Temperature Range  |           | -40 | +85  | °C   |

Notes:

<sup>4.</sup> Stresses greater than the 'Absolute Maximum Ratings' specified above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability may be affected by exposure to absolute maximum rating conditions for extended periods of time.

Semiconductor devices are ESD sensitive and may be damaged by exposure to ESD events. Suitable ESD precautions should be taken when handling and transporting these devices.

<sup>6.</sup> Test condition: SO-8: Device mounted on 2" x 2" FR-4 substrate PC board, 2oz copper with minimum recommended pad layout.

<sup>7.</sup> The device function is not guaranteed outside of the recommended operating conditions.

#

| Parameter                      | Parameter Symbol Conditions                  |                                                            | Min   | Тур   | Max   | Unit |

|--------------------------------|----------------------------------------------|------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY VOLTAGE (VIN PIN)       | •                                            | <u> </u>                                                   |       | •     |       |      |

| Input Voltage                  | V <sub>IN</sub>                              | _                                                          | 4.5   | _     | 18    | V    |

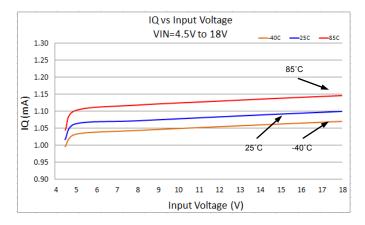

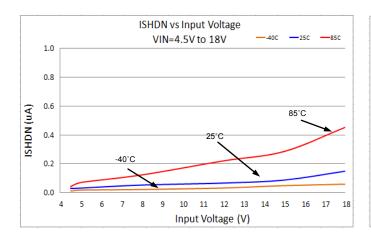

| Quiescent Current              | ΙQ                                           | V <sub>FB</sub> = 0.85V                                    | _     | 0.9   | _     | mA   |

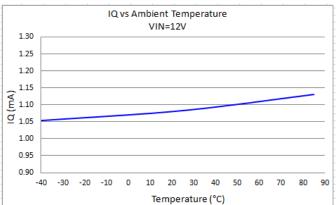

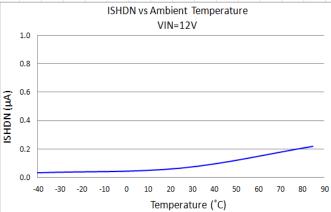

| Shutdown Supply Current        | I <sub>SHDN</sub>                            | V <sub>EN</sub> = 0V                                       | _     | 3.6   | 10    | μΑ   |

| UNDERVOLTAGE LOCKOUT           | •                                            | <u> </u>                                                   |       | •     |       |      |

| UVLO Threshold                 | V <sub>UVLO</sub>                            | V <sub>IN</sub> Rising Test VREG5 Voltage                  | 3.45  | 3.75  | 4.05  | V    |

| UVLO Hysteresis                | V <sub>HYS</sub>                             | V <sub>IN</sub> Falling Test VREG5 Voltage                 | 0.19  | 0.32  | 0.45  | V    |

| ENABLE (EN PIN)                | •                                            | <u> </u>                                                   |       | •     |       |      |

| EN High-Level Input Voltage    | V <sub>ENH</sub>                             | _                                                          | 1.9   | _     | _     | V    |

| EN Low-Level Input Voltage     | V <sub>ENL</sub>                             | _                                                          | _     | _     | 0.6   | V    |

| VOLTAGE REFERENCE (FB PIN)     |                                              |                                                            |       |       |       |      |

| Feedback Voltage               | $V_{FB}$                                     | V <sub>OUT</sub> = 1.05V                                   | 0.753 | 0.765 | 0.777 | V    |

| Feedback Bias Current          | I <sub>FB</sub>                              | V <sub>FB</sub> = 0.8V                                     | -0.1  | 0     | 0.1   | μΑ   |

| VREG5 OUTPUT                   |                                              |                                                            |       |       |       |      |

| VREG5 Output Voltage           | V <sub>VREG5</sub>                           | 6.0V <v<sub>IN&lt;18V 0<i<sub>VREG5&lt;5mA</i<sub></v<sub> | 4.7   | 5.1   | 5.5   | V    |

| Source Current Capability      | _                                            | V <sub>IN</sub> = 6V, V <sub>VREG5</sub> = 4V              | _     | 110   | _     | mA   |

| Load Regulation                | _                                            | 0 <i<sub>VREG5&lt;5mA</i<sub>                              | _     | _     | 60    | mV   |

| Line Regulation                | _                                            | 6.0V <vin<18v i<sub="">VREG5 = 5mA</vin<18v>               |       | _     | 20    | mV   |

| MOSFET                         |                                              |                                                            |       |       | •     | •    |

| High-side Switch On-Resistance | R <sub>DSONH</sub>                           | _                                                          | _     | 0.065 | _     | Ω    |

| Low-side Switch On-Resistance  | R <sub>DSONL</sub>                           | _                                                          | _     | 0.036 | _     | Ω    |

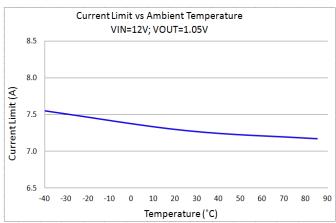

| CURRENT LIMIT                  |                                              |                                                            |       |       |       |      |

| High Level Current Limit       | I <sub>LIM-H</sub>                           | L=1.5µH                                                    | 5.6   | 6.4   | 7.9   | Α    |

| ON-TIME TIMER                  |                                              |                                                            |       |       |       |      |

| On Time                        | ton                                          | V <sub>IN</sub> =12V, VOUT=1.05V                           | _     | 150   | _     | ns   |

| Minimum Off Time               | toff-min                                     | V <sub>FB</sub> =0.7V                                      |       | 260   | 310   | ns   |

| THERMAL SHUTDOWN               |                                              |                                                            |       |       | •     | •    |

| Thermal Shutdown               | T <sub>OTSD</sub>                            | _                                                          |       | +160  | _     | °C   |

| Thermal Shutdown Hysteresis    | Thermal Shutdown Hysteresis T <sub>HYS</sub> |                                                            |       | +30   | _     | °C   |

| SOFT START (SS PIN)            |                                              |                                                            |       |       |       |      |

| Soft-Start Source Current      | I <sub>SS-SOURCE</sub>                       | V <sub>SS</sub> = 1.2V                                     | 4.2   | 6.0   | 7.8   | μΑ   |

| Soft-Start Discharge Current   | I <sub>SS-DISCHARGE</sub>                    | V <sub>SS</sub> =0.5V                                      | 0.1   | 0.2   | _     | mA   |

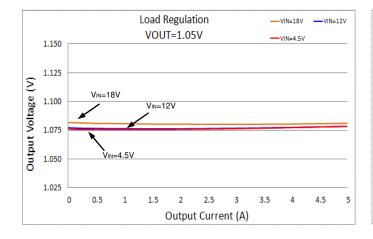

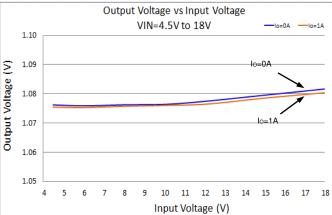

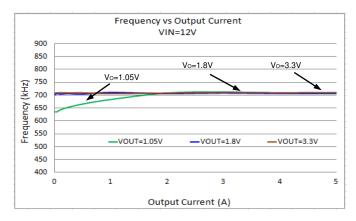

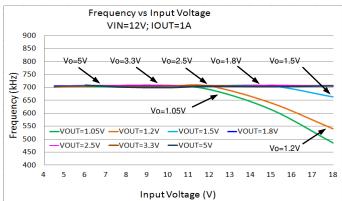

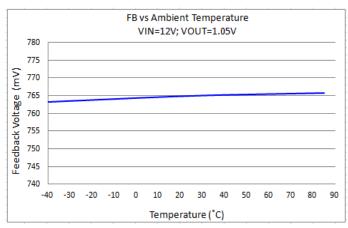

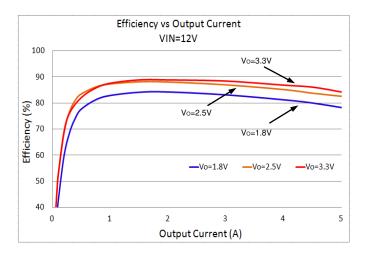

# $\textbf{Typical Performance Characteristics} \ (@T_A = +25^{\circ}C,\ V_{IN} = 12V,\ V_{OUT} = 1.05V,\ unless \ otherwise \ specified.)$

# $\hline \textbf{Typical Performance Characteristics} \text{ (continued) } (@T_A = +25^{\circ}\text{C}, V_{\text{IN}} = 12\text{V}, V_{\text{OUT}} = 1.05\text{V}, \text{ unless otherwise specified.)}$

### **Typical Performance Characteristics** (cont.)

$(@T_A = +25^{\circ}C, V_{IN} = 12V, V_{OUT} = 1.05V, L = 1.5\mu H, C1 = 20\mu F, C2 = 44\mu F, unless otherwise specified.)$

### **Application Information**

Figure 3. Typical Application of AP65552

#### **PWM Operation and Adaptive On-time Control**

The AP65552 is synchronous step-down converters with internal power MOSFETs. Adaptive, constant on-time (COT) control is employed to provide fast transient response and easy loop stabilization. At the beginning of each cycle, the high-side MOSFET is turned on. This MOSFET is turned off after an internal one shot timer expires. This one shot is set by the converter input voltage (V<sub>IN</sub>), and the output voltage (V<sub>OUT</sub>) to maintain a pseudo-fixed frequency over the input voltage range, hence it is called adaptive on-time control. The output voltage variation is sensed by FB voltage. The one-shot timer is reset and the high-side MOSFET is turned on again when FB voltage falls below the 0.76V.

AP65552 uses an adaptive on-time control scheme and does not have a dedicated in board oscillator. It runs with a pseudo-constant frequency of 650kHz by using the input voltage and output voltage to set the on-time one-shot timer. The on-time is inversely proportional to the input voltage and proportional to the output voltage. It can be calculated using the following equation:

$$T_{ON} = \frac{V_{OUT}}{V_{INI} \times f}$$

$V_{\text{OUT}}$  is the output voltage  $V_{\text{IN}}$  is the input voltage f is the switching frequency

After an ON-time period, the AP65552 goes into the OFF-time period. The OFF-time period length depends on VFB in most cases. It will end when the FB voltage decreases below 0.76V then the ON-time period is triggered. If the OFF-time period is less than the minimum OFF time, the minimum OFF time will be applied, which is about 260ns typical.

#### Enable

Above the 'EN high-level input voltage', the internal regulator is turned on and the quiescent current can be measured above this threshold. The enable (EN) input allows the user to control turning on or off the regulator. To enable the AP65552, EN must be pulled above the 'EN high-level input voltage' and to disable the AP65552, EN must be pulled below 'EN low-level input voltage'.

In Figure 3, EN has a positive voltage through a 100KΩ pull-up to VIN. No supply input is required for EN.

#### Soft-Start

The soft-start time of the AP65552 is programmable by selecting a different  $C_{SS}$  value. When the EN pin becomes high, the  $C_{SS}$  is charged by a 6µA current source, generating a ramp signal fed into non-inverting input of the error comparator. Reference voltage  $V_{REF}$  or the internal soft-start voltage SS, (whichever is smaller), dominates the behavior of the non-inverting inputs of the error amplifier. Accordingly, the output voltage will follow the SS signal and ramp up smoothly to its target level. The capacitor value required for a given soft-start ramp time can be expressed as:

$$t_{SS} = \frac{C_{SS} \times V_{FB}}{I_{SS}}$$

Where CSS is the required capacitor between SS pin and GND, tSS is the desired soft-start time and VFB is the feedback voltage.

### **Application Information** (continued)

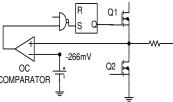

#### **Overcurrent Protection (OCP)**

Figure 4 shows the overcurrent protection (OCP) scheme of AP65552. In each switching cycle, the inductor current is sensed by monitoring the low-side MOSFET in the OFF period. When the voltage between GND pin and SW pin is smaller than the overcurrent trip level, the OCP will be triggered and the controller maintains the OFF state. A new switching cycle will begin when the measured voltage is larger than the limit voltage. The internal counter is incremented when OCP is triggered. After sixteen sequential cycles, the internal OCL (Overcurrent Logic) threshold is set to a lower level, reducing the available output current. When a switching cycle occurs where the switch current is below the lower OCL threshold, the counter is reset and the OCL limit is returned to a higher value.

Because the  $R_{DS(ON)}$  of MOSFET increases with temperature,  $V_{Limit}$  has xppm/°C temperature coefficient to compensate this temperature dependency of  $R_{DS(ON)}$ .

Figure 4 Overcurrent Protection Scheme

#### **Undervoltage Lockout**

The AP65552 provides an undervoltage lockout circuit to prevent it from undefined status during startup. The UVLO circuit shuts down the device when  $V_{IN}$  drops below 3.45V. The UVLO circuit has 320mV hysteresis, which means the device starts up again when  $V_{REG}$  rise to 3.75V(non-latch).

#### Thermal Shutdown

If the junction temperature of the device reaches the thermal shutdown limit of 160°C, the AP65552 shuts itself off, and both HMOS and LMOS will be turned off. The output is discharged with the internal transistor. When the junction cools to the required level (130°C nominal), the device initiates soft-start as during a normal power-up cycle.

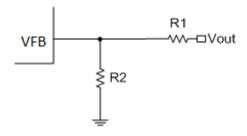

#### **Setting the Output Voltage**

The output voltage can be adjusted from 1.000 to 5V using an external resistor divider. Table 1 shows a list of resistor selections for common output voltages. Resistor R1 is selected based on a design tradeoff between efficiency and output voltage accuracy. For high values of R1 there is less current consumption in the feedback network. However the tradeoff is output voltage accuracy due to the bias current in the error amplifier. R1 can be determined by the following equation:

$$R_1 = R_2 \cdot \left( \frac{V_{OUT}}{0.765} - 1 \right)$$

Figure 5 Feedback Divider Network

| Output Voltage (V) | R1 (kΩ) | R2 (kΩ) |

|--------------------|---------|---------|

| 1                  | 6.81    | 22.1    |

| 1.05               | 8.25    | 22.1    |

| 1.2                | 12.7    | 22.1    |

| 1.5                | 21.5    | 22.1    |

| 1.8                | 30.1    | 22.1    |

| 2.5                | 49.9    | 22.1    |

| 3.3                | 73.2    | 22.1    |

| 5                  | 124     | 22.1    |

**Table 1 Resistor Selection for Common Output**

## **Application Information (cont.)**

#### Inductor

Calculating the inductor value is a critical factor in designing a buck converter. For most designs, the following equation can be used to calculate the inductor value:

$$L = \frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{V_{IN} \cdot \Delta I_L \cdot f_{SW}}$$

Where  $\Delta I_L$  is the inductor ripple current.

And f<sub>SW</sub> is the buck converter switching frequency.

Choose the inductor ripple current to be 30% of the maximum load current. The maximum inductor peak current is calculated from:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

Peak current determines the required saturation current rating, which influences the size of the inductor. Saturating the inductor decreases the converter efficiency while increasing the temperatures of the inductor and the internal MOSFETs. Hence, choosing an inductor with appropriate saturation current rating is important.

A 1µH to 3.3µH inductor with a DC current rating of at least 25% higher than the maximum load current is recommended for most applications. For highest efficiency, the inductor's DC resistance should be less than 100mΩ. Use a larger inductance for improved efficiency under light load

The phase boost can be achieved by adding an additional feed forward capacitor (C7) in parallel with R1.

| Output Voltage (V) | C7(pF) | L1(μH)    | C8+C9(μF) |

|--------------------|--------|-----------|-----------|

| 1                  | _      | 1.0 - 1.5 | 22-68     |

| 1.05               | _      | 1.0 - 1.5 | 22-68     |

| 1.2                | _      | 1.0 - 1.5 | 22-68     |

| 1.5                | _      | 1.5       | 22-68     |

| 1.8                | 5 - 22 | 1.5       | 22-68     |

| 2.5                | 5 - 22 | 2.2       | 22-68     |

| 3.3                | 5 - 22 | 2.2       | 22-68     |

| 5                  | 5 - 22 | 3.3       | 22-68     |

**Table 2 Recommended Component Selection**

#### **Input Capacitor**

The input capacitor reduces the surge current drawn from the input supply and the switching noise from the device. The input capacitor has to sustain the ripple current produced during the on time on the upper MOSFET. It must hence have a low ESR to minimize the losses.

The RMS current rating of the input capacitor is a critical parameter that must be higher than the RMS input current. As a rule of thumb, select an input capacitor which has an RMS rating that is greater than half of the maximum load current.

Due to large dl/dt through the input capacitors, electrolytic or ceramics should be used. If a tantalum must be used, it must be surge protected, otherwise, capacitor failure could occur. For most applications, a ceramic capacitor greater than 10µF is sufficient.

#### **Output Capacitor**

The Output Capacitor keeps the output voltage ripple small, ensures feedback loop stability and reduces the overshoot of the output voltage. The Output Capacitor is a basic component for the fast response of the power supply. In fact, during load transient, for the first few microseconds it supplies the current to the load. The converter recognizes the load transient and sets the duty cycle to maximum, but the current slope is limited by the inductor value.

10 of 13 August 2015 www.diodes.com Document number: DS37306 Rev. 3 - 2 © Diodes Incorporated

August 2015

# **Application Information (cont.)**

#### Output Capacitor (cont.)

Maximum capacitance required can be calculated from the following equation:

ESR of the Output Capacitor dominates the output voltage ripple. The amount of ripple can be calculated from the equation below:

$$Vout_{capacitor} = \Delta I_{inductor} * ESR$$

An Output Capacitor with ample capacitance and low ESR is the best option. For most applications, a 22µF to 68µF ceramic capacitor will be sufficient.

$$C_{o} = \frac{L(I_{out} + \frac{\Delta I_{inductor}}{2})^{2}}{(\Delta V + V_{out})^{2} - V_{out}^{2}}$$

Where  $\Delta V$  is the maximum output voltage overshoot.

#### **Bootstrap Capacitor**

To ensure the proper operation, a ceramic capacitor must be connected between the VBST and SW pin. A 0.1µF ceramic capacitor is sufficient.

#### **VREG5 Capacitor**

To ensure the proper operation, a ceramic capacitor must be connected between the VREG5 and GND pin. A 1µF ceramic capacitor is sufficient.

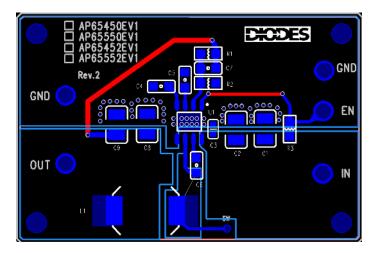

#### **PC Board Layout**

- The AP65552 works at 5A load current, heat dissipation is a major concern in layout the PCB. A 2oz Copper in both the top and bottom layers is recommended.

- Provide sufficient vias in the thermal exposed pad for heat dissipate to the bottom layer. 2.

- 3. Provide sufficient vias in the Output Capacitor GND side to dissipate heat to the bottom layer.

- Make the bottom layer under the device as GND layer for heat dissipation. The GND layer should be as large as possible to provide better thermal effect.

- 5. Make the Vin capacitors as close to the device as possible.

- Make the VREG5 capacitor as close to the device as possible. 6.

- The thermal pad of the device should be soldered directly to the PCB exposed copper plane to work as a heatsink. The thermal vias in the exposed copper plane increase the heat transfer to the bottom layer.

Figure 6 PC Board Layout

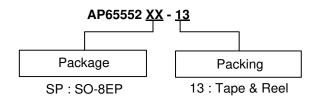

# **Ordering Information**

| Part Number  | Bookege Code | ode Part Marking | Identification Code | Tape and Reel |                    |  |

|--------------|--------------|------------------|---------------------|---------------|--------------------|--|

| Part Number  | Package Code |                  |                     | Quantity      | Part Number Suffix |  |

| AP65552SP-13 | SP           | SO-8EP           | _                   | 2,500         | -13                |  |

## **Marking Information**

(1) SO-8EP

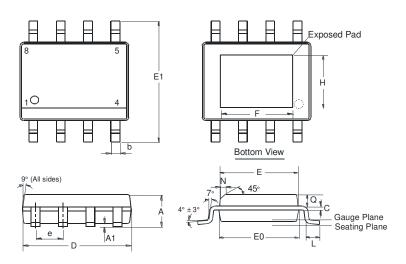

### Package Outline Dimensions (All dimensions in mm.)

Please see AP02002 at http://www.diodes.com/datasheets/ap02002.pdf for the latest version.

| SO-8EP (SOP-8L-EP)   |      |      |      |  |  |

|----------------------|------|------|------|--|--|

| Dim                  | Min  | Max  | Тур  |  |  |

| Α                    | 1.40 | 1.50 | 1.45 |  |  |

| <b>A</b> 1           | 0.00 | 0.13 | -    |  |  |

| b                    | 0.30 | 0.50 | 0.40 |  |  |

| O                    | 0.15 | 0.25 | 0.20 |  |  |

| D                    | 4.85 | 4.95 | 4.90 |  |  |

| Е                    | 3.80 | 3.90 | 3.85 |  |  |

| E0                   | 3.85 | 3.95 | 3.90 |  |  |

| E1                   | 5.90 | 6.10 | 6.00 |  |  |

| е                    | -    | -    | 1.27 |  |  |

| F                    | 2.75 | 3.35 | 3.05 |  |  |

| Н                    | 2.11 | 2.71 | 2.41 |  |  |

| L                    | 0.62 | 0.82 | 0.72 |  |  |

| N                    | -    | -    | 0.35 |  |  |

| Ø                    | 0.60 | 0.70 | 0.65 |  |  |

| All Dimensions in mm |      |      |      |  |  |

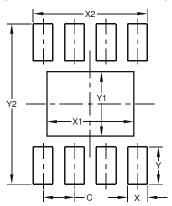

### **Suggested Pad Layout**

Please see AP02001 at http://www.diodes.com/datasheets/ap02001.pdf for the latest version.

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 1.270            |

| Х          | 0.802            |

| X1         | 3.502            |

| X2         | 4.612            |

| Υ          | 1.505            |

| Y1         | 2.613            |

| Y2         | 6.500            |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### **LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

www.diodes.com