### PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES SEPTEMBER 7, 2016

DATA SHEET

The MPC9330 is a 3.3 V compatible, 1:6 PLL based clock generator targeted for high performance low-skew clock distribution in mid-range to high-performance telecomm, networking and computing applications. With output frequencies up to 120 MHz and output skews less than 150 ps, the device meets the needs of the most demanding clock applications. The MPC9330 is specified for the temperature range of 0°C to +70°C.

#### **Features**

- 1:6 PLL Based Low-Voltage Clock Generator

- 3.3 V Power Supply

- Generates Clock Signals Up to 120 MHz

- Maximum Output Skew of 150 ps

- On-Chip Crystal Oscillator Clock Reference

- Alternative LVCMOS PLL Reference Clock Input

- Internal and External PLL Feedback

- PLL Multiplies the Reference Clock by 4x, 3x, 2x, 1x, 4/3x, 3/2x, 2/3x, x/2, x/3, or x/4

- Supports Zero-Delay Operation in External Feedback Mode

- Synchronous Output Clock Stop in Logic Low Eliminates Output Runt Pulses

- Power Down Feature Reduces Output Clock Frequency

- Drives Up to 12 Clock Lines

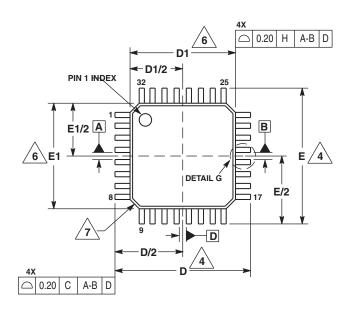

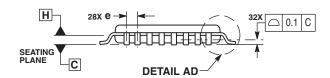

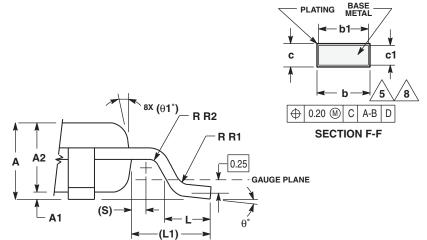

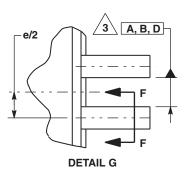

- 32-Lead LQFP Packaging

- 32-Lead Pb-Free Package

- Ambient Temperature Range 0°C to +70°C

- Internal Power-Up Reset

- Pin and Function Compatible to the MPC930

- For functional replacement use 8T49N285A

# MPC9330

3.3 V 1:6 LVCMOS PLL CLOCK GENERATOR

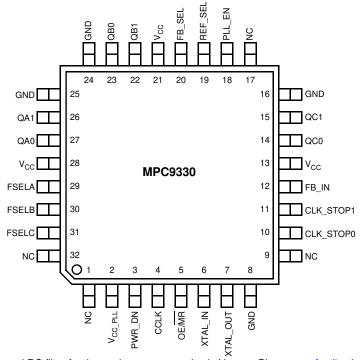

**AC SUFFIX** 32-LEAD LQFP PACKAGE **Pb-FREE PACKAGE CASE 873A-03**

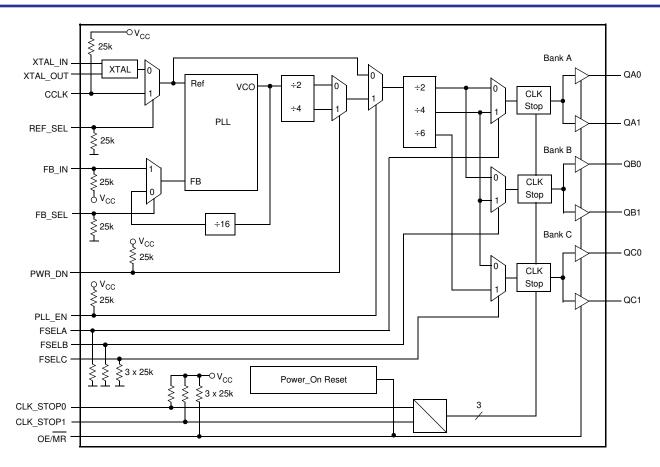

#### **Functional Description**

The MPC9330 utilizes PLL technology to frequency lock its outputs onto an input reference clock. Normal operation of the MPC9330 requires either the selection of internal PLL feedback or the connection of one of the device outputs to the feedback input to close the PLL feedback path in external feedback mode. The reference clock frequency and the divider for the feedback path determine the VCO frequency. Both must be selected to match the VCO frequency range. In external PLL feedback configuration and with the available post-PLL dividers (divide-by-2, divide-by-4 and divide-by-6), the internal VCO of the MPC9330 is running at either 4x, 8x, 12x, 16x, or 24x of the reference clock frequency. In internal feedback configuration (divide-by-16) the internal VCO is running 16x of the reference frequency. The frequency of the QA, QB, QC output banks is a division of the VCO frequency and can be configured independently for each output bank using the FSELA. FSELB and FSELC pins, respectively. The available output to input frequency ratios are 4x, 3x, 2x, 1x, 4/3x, 3/2x, 2/3x, x/2, x/3, or x/4.

The REF SEL pin selects the internal crystal oscillator or the LVCMOS compatible input as the reference clock signal. The PLL EN control selects the PLL bypass configuration for test and diagnosis. In this configuration, the selected input reference clock is routed directly to the output dividers bypassing the PLL. The PLL bypass is fully static and the minimum clock frequency specification and all other PLL characteristics do not apply.

The outputs can be disabled (high-impedance) by deasserting the OE/MR pin. In the PLL configuration with external feedback selected. deasserting OE/MR causes the PLL to loose lock due to missing feedback signal presence at FB IN. Asserting OE/MR will enable the outputs and close the phase locked loop, enabling the PLL to recover to normal operation. The MPC9330 output clock stop control allows the outputs to start and stop synchronously in the logic low state, without the potential generation of runt pulses.

The MPC9330 is fully 3.3 V compatible and requires no external loop filter components. All inputs (except XTAL) accept LVCMOS signals while the outputs provide LVCMOS compatible levels with the capability to drive terminated 50  $\Omega$  transmission lines. For series terminated transmission lines, each of the MPC9330 outputs can drive one or two traces giving the devices an effective fanout of 1:12. The device is packaged in a 7x7 mm<sup>2</sup> 32-lead LQFP package.

Figure 1. MPC9330 Logic Diagram

It is recommended to use an external RC filter for the analog power supply pin  $V_{\text{CC\_PLL}}$ . Please see Applications Information section for details.

Figure 2. MPC9330 32-Lead Package Pinout (Top View)

Table 1. Pin Configuration

| Pin                 | I/O    | Туре            | Function                                                                                                                                                                                                 |

|---------------------|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCLK                | Input  | LVCMOS          | PLL reference clock signal                                                                                                                                                                               |

| XTAL_IN, XTAL_OUT   | Input  | Analog          | Crystal oscillator interface                                                                                                                                                                             |

| FB_IN               | Input  | LVCMOS          | PLL feedback signal input, connect to an output                                                                                                                                                          |

| FB_SEL              | Input  | LVCMOS          | Feedback select                                                                                                                                                                                          |

| REF_SEL             | Input  | LVCMOS          | Reference clock select                                                                                                                                                                                   |

| PWR_DN              | Input  | LVCMOS          | Output frequency and power down select                                                                                                                                                                   |

| FSELA               | Input  | LVCMOS          | Frequency divider select for bank A outputs                                                                                                                                                              |

| FSELB               | Input  | LVCMOS          | Frequency divider select for bank B outputs                                                                                                                                                              |

| FSELC               | Input  | LVCMOS          | Frequency divider select for bank C outputs                                                                                                                                                              |

| PLL_EN              | Input  | LVCMOS          | PLL enable/disable                                                                                                                                                                                       |

| CLK_STOP0-1         | Input  | LVCMOS          | Clock output enable/disable                                                                                                                                                                              |

| OE/MR               | Input  | LVCMOS          | Output enable/disable (high-impedance tristate) and device reset                                                                                                                                         |

| QA0-1, QB0-1, QC0-1 | Output | LVCMOS          | Clock outputs                                                                                                                                                                                            |

| GND                 | Supply | Ground          | Negative power supply                                                                                                                                                                                    |

| V <sub>CC_PLL</sub> | Supply | V <sub>CC</sub> | PLL positive power supply (analog power supply). It is recommended to use an external RC filter for the analog power supply pin $V_{CC\_PLL}$ . Please see Applications Information section for details. |

| V <sub>CC</sub>     | Supply | V <sub>CC</sub> | Positive power supply for I/O and core. All $V_{\rm CC}$ pins must be connected to the positive power supply for correct operation.                                                                      |

Table 2. Function Table

| Control       | Default      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                           |

|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| REF_SEL       | 0            | The crystal oscillator output is the PLL reference clock                                                                                                                                                                                                                                                                                                                                                                                                                              | CCLK is the PLL reference clock                                             |

| FB_SEL        | 0            | Internal PLL feedback of 16. f <sub>VCO</sub> = 16 * f <sub>ref</sub>                                                                                                                                                                                                                                                                                                                                                                                                                 | External feedback. Zero-delay operation enabled for CCLK as reference clock |

| PLL_EN        | 1            | Test mode with PLL disabled. The reference clock is substituted for the internal VCO output. MPC9330 is fully static and no minimum frequency limit applies. All PLL related AC characteristics are not applicable.                                                                                                                                                                                                                                                                   | Normal operation mode with PLL enabled.                                     |

| PWR_DN        | 1            | VCO ÷ 2 (High output frequency range)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VCO ÷ 4 (Low output frequency range)                                        |

| FSELA         | 0            | Output divider ÷ 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output divider ÷ 4                                                          |

| FSELB         | 0            | Output divider ÷ 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output divider ÷ 4                                                          |

| FSELC         | 0            | Output divider ÷ 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output divider ÷ 6                                                          |

| CLK_STOP[0:1] | 11           | See Table 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                             |

| OE/MR         | 1            | Outputs disabled (high-impedance state) and reset of the device. During reset in external feedback configuration, the PLL feedback loop is open. The VCO is tied to its lowest frequency. The MPC9330 requires reset after any loss of PLL lock. Loss of PLL lock may occur when the external feedback path is interrupted. The length of the reset pulse should be greater than one reference clock cycle (CCLK). Reset does not affect PLL lock in internal feedback configuration. | Outputs enabled (active)                                                    |

| PWR [         | ON, FSELA, F | SELB and FSELC control the operating PLL frequency range an                                                                                                                                                                                                                                                                                                                                                                                                                           | d input/output frequency ratios.                                            |

PWR\_DN, FSELA, FSELB and FSELC control the operating PLL frequency range and input/output frequency ratios.

See Table 8 through Figure 10 for supported frequency ranges and output to input frequency ratios.

Table 3. Clock Output Synchronous Disable (CLK\_STOP) Function Table<sup>(1)</sup>

| CLK_STOP0 | CLK_STOP1 | QA[0:1]                  | QB[0:1]                  | QC[0:1]                  |  |

|-----------|-----------|--------------------------|--------------------------|--------------------------|--|

| 0         | 0         | Active                   | Stopped in logic L state | Stopped in logic L state |  |

| 0         | 1         | Active                   | Stopped in logic L state | Active                   |  |

| 1         | 0         | Stopped in logic L state | Stopped in logic L state | Active                   |  |

| 1         | 1         | Active                   | Active                   | Active                   |  |

<sup>1.</sup> Output operation for  $OE/\overline{MR}=1$  (outputs enabled).  $OE/\overline{MR}=0$  will disable (high-impedance state) all outputs independent on  $CLK\_STOP[0:1]$ .

Table 4. General Specifications

| Symbol          | Characteristics                   | Min  | Тур                 | Max | Unit | Condition  |

|-----------------|-----------------------------------|------|---------------------|-----|------|------------|

| V <sub>TT</sub> | Output Termination Voltage        |      | V <sub>CC</sub> ÷ 2 |     | V    |            |

| MM              | ESD Protection (Machine Model)    | 200  |                     |     | ٧    |            |

| HBM             | ESD Protection (Human Body Model) | 2000 |                     |     | ٧    |            |

| LU              | Latch-Up Immunity                 | 200  |                     |     | mA   |            |

| C <sub>PD</sub> | Power Dissipation Capacitance     |      | 10                  |     | pF   | Per output |

| C <sub>IN</sub> | Input Capacitance                 |      | 4.0                 |     | pF   | Inputs     |

Table 5. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Characteristics     | Min         | Max                  | Unit |

|------------------|---------------------|-------------|----------------------|------|

| V <sub>CC</sub>  | Supply Voltage      | -0.3        | 3.9                  | V    |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3        | V <sub>CC</sub> +0.3 | V    |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3        | V <sub>CC</sub> +0.3 | V    |

| I <sub>IN</sub>  | DC Input Current    |             | ±20                  | mA   |

| I <sub>OUT</sub> | DC Output Current   |             | ±50                  | mA   |

| T <sub>S</sub>   | Storage Temperature | <b>–</b> 65 | 125                  | °C   |

<sup>1.</sup> Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

Table 6. DC Characteristics ( $V_{CC} = 3.3 \text{ V} \pm 5\%$ ,  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ )

| Symbol              | Characteristics                  | Min | Тур     | Max                   | Unit   | Condition                                          |

|---------------------|----------------------------------|-----|---------|-----------------------|--------|----------------------------------------------------|

| V <sub>IH</sub>     | Input High Voltage               | 2.0 |         | V <sub>CC</sub> + 0.3 | V      | LVCMOS                                             |

| V <sub>IL</sub>     | Input Low Voltage                |     |         | 0.8                   | ٧      | LVCMOS                                             |

| V <sub>OH</sub>     | Output High Voltage              | 2.4 |         |                       | V      | I <sub>OH</sub> = -24 mA <sup>(1)</sup>            |

| V <sub>OL</sub>     | Output Low Voltage               |     |         | 0.55<br>0.30          | V<br>V | I <sub>OL</sub> = 24 mA<br>I <sub>OL</sub> = 12 mA |

| Z <sub>OUT</sub>    | Output Impedance                 |     | 14 – 17 |                       | Ω      |                                                    |

| I <sub>IN</sub>     | Input Current <sup>(2)</sup>     |     |         | ±100                  | μА     | V <sub>IN</sub> = V <sub>CC</sub> or GND           |

| I <sub>CC_PLL</sub> | Maximum PLL Supply Current       |     | 5.0     | 10                    | mA     | V <sub>CC_PLL</sub> Pin                            |

| I <sub>CCQ</sub>    | Maximum Quiescent Supply Current |     | 5.0     | 10                    | mA     | All V <sub>CC</sub> Pins                           |

<sup>1.</sup> The MPC9330 is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up to two 50  $\Omega$  series terminated transmission lines.

<sup>2.</sup> Inputs have pull-down or pull-up resistors affecting the input current.

Table 7. AC Characteristics (V<sub>CC</sub> = 3.3 V  $\pm$  5%, T<sub>A</sub> = 0°C to 70°C)<sup>(1)</sup>

| Symbol                          | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Min                                       | Тур                                                  | Max                                      | Unit                                          | Condition     |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------|------------------------------------------|-----------------------------------------------|---------------|

| f <sub>ref</sub>                | Input Reference Frequency <sup>(2)</sup> PLL mode, external feedback  ÷ 8 feedback  ÷ 12 feedback  ÷ 16 feedback  † 24 feedback  PLL mode, internal feedback    16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   16 feedback   17 feedback   17 feedback   18 fe | 50<br>25<br>16.67<br>12.5<br>8.33<br>12.5 |                                                      | 120<br>60<br>40<br>30<br>20<br>30<br>TBD | MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz | PLL locked    |

| f <sub>VCO</sub>                | VCO Lock Frequency Range <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 200                                       |                                                      | 480                                      | MHz                                           |               |

| f <sub>XTAL</sub>               | Crystal Interface Frequency Range <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                        |                                                      | 25                                       | MHz                                           |               |

| f <sub>MAX</sub>                | Output Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>25<br>16.67<br>12.5<br>8.33         |                                                      | 120<br>60<br>40<br>30<br>20              | MHz<br>MHz<br>MHz<br>MHz<br>MHz               | PLL locked    |

| f <sub>refDC</sub>              | Reference Input Duty Cycle<br>Minimum Input Reference Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25<br>2                                   |                                                      | 75                                       | %<br>ns                                       |               |

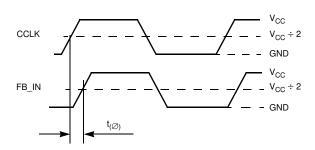

| t <sub>r</sub> , t <sub>f</sub> | CCLK Input Rise/Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |                                                      | 1.0                                      | ns                                            | 0.8 to 2.0 V  |

| t <sub>(∅)</sub>                | Propagation Delay (SPO) $^{(7)}$ for the $-$ entire $f_{ref}$ range $ f_{ref} = 8.33$ MHz $ f_{ref} = 50.0$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1.2<br>-400<br>-70                       |                                                      | +1.2<br>+400<br>+70                      | ps<br>ps                                      |               |

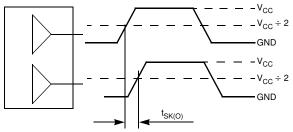

| t <sub>sk(o)</sub>              | Output-to-Output Skew <sup>(8)</sup> (within output bank) (any output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                                                      | 50<br>150                                | ps<br>ps                                      |               |

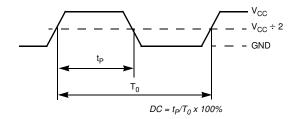

| DC                              | Output Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                        | 50                                                   | 55                                       | %                                             |               |

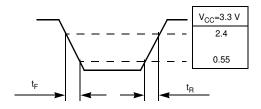

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.1                                       |                                                      | 1.0                                      | ns                                            | 0.55 to 2.4 V |

| t <sub>PLZ, HZ</sub>            | Output Disable Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                                      | 10                                       | ns                                            |               |

| t <sub>PZL, LZ</sub>            | Output Enable Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                                                      | 10                                       | ns                                            |               |

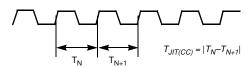

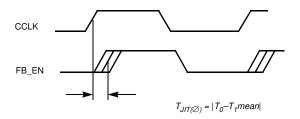

| t <sub>JIT(CC)</sub>            | Cycle-to-cycle jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           | 50                                                   | 300                                      | ps                                            |               |

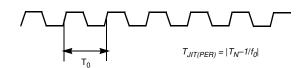

| t <sub>JIT(PER)</sub>           | Period Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | 35                                                   | 250                                      | ps                                            |               |

| t <sub>JIT(∅)</sub>             | I/O Phase Jitter RMS (1σ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           | 10                                                   | 70                                       | ps                                            |               |

| BW                              | PLL closed loop bandwidth <sup>(9)</sup> PLL mode, external feedback  ÷ 4 feedback  ÷ 8 feedback  ÷ 12 feedback  ÷ 16 feedback  ÷ 24 feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           | 0.8-5.0<br>0.5-2.0<br>0.3-1.0<br>0.25-0.6<br>0.2-0.5 |                                          | MHz<br>MHz<br>MHz<br>MHz<br>MHz               |               |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |                                                      | 10                                       | ms                                            |               |

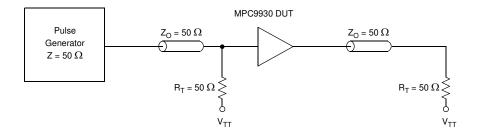

- 1. AC characteristics apply for parallel output termination of 50  $\Omega$  to  $V_{TT}.$

- 2. PLL mode requires PLL\_EN = 0 to enable the PLL.

- 3. ÷4 feedback (FB) can be accomplished by setting PWR\_DN = 0 and the connection of one ÷2 output to FB\_IN. See Table 3 to Table 5 for other feedback configurations.

- 4. In bypass mode, the MPC9330 divides the input reference clock.

- 5. The input frequency  $f_{ref}$  on CCLK must match the VCO frequency range divided by the feedback divider ratio FB:  $f_{ref} = f_{VCO} \div FB$ .

- 6. The usable crystal frequency range depends on the VCO lock frequency and the PLL feedback ratio.

- 7. SPO is the static phase offset between CCLK and FB\_IN (FB\_SEL=1 and PLL locked).  $t_{sk(o)}$  [ps] =  $t_{sk(o)}$  [°] B(fref ÷ 360°)

- 8. Skew data applicable for equally loaded outputs only.

- 9. -3 dB point of PLL transfer characteristics.

#### **APPLICATIONS INFORMATION**

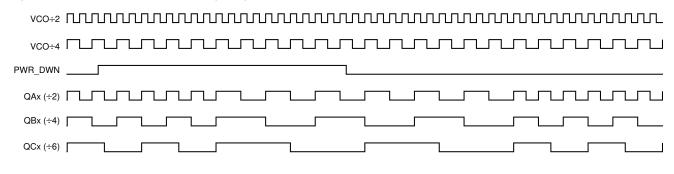

# Output Power Down (PWR\_DN) Timing Diagram

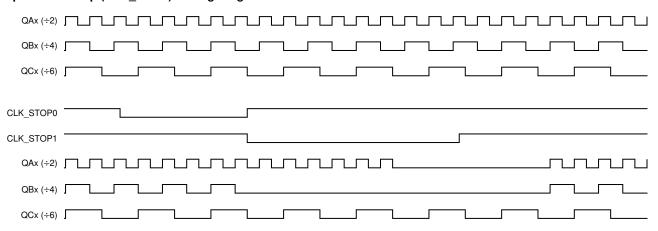

# Output Clock Stop (CLK\_STOP) Timing Diagram

#### **Programming the MPC9330**

The MPC9330 supports output clock frequencies from 8.33 to 120 MHz. Different feedback and output divider configurations can be used to achieve the desired input to output frequency relationship. The feedback frequency and divider should be used to situate the VCO in the frequency lock range between 200 and 480

MHz for stable and optimal operation. The FSELA, FSELB, FSELC and PWR\_DN pins select the desired output clock frequencies. Possible frequency ratios of the reference clock input to the outputs are 1:4, 1:3, 1:2, 1:1, 2:3, 4:3 and 3:2. Table 8 through Table 10 illustrate the various output configurations and frequency ratios supported by the MPC9330.

Table 8. MPC9330 Example Configurations (Internal Feedback: FB\_SEL = 0)

| fref <sup>(1)</sup> [MHz] | PWR_DN | FSELA | FSELB | FSELC | QA[0     | :1]:fref ratio | QB       | [0:1]:fref ratio | QC[0:                 | 1]:fref ratio |

|---------------------------|--------|-------|-------|-------|----------|----------------|----------|------------------|-----------------------|---------------|

| 12.5–30.0                 | 0      | 0     | 0     | 0     | fref · 4 | (50-120 MHz)   | fref · 4 | (50-120 MHz)     | fref · 2              | (25-60 MHz)   |

|                           | 0      | 0     | 0     | 1     | fref · 4 | (50-120 MHz)   | fref · 4 | (50-120 MHz)     | fref ⋅4 ÷ 3           | (16.6-40 MHz) |

|                           | 0      | 0     | 1     | 0     | fref · 4 | (50-120 MHz)   | fref · 2 | (25-60 MHz)      | fref · 2              | (25-60 MHz)   |

|                           | 0      | 0     | 1     | 1     | fref · 4 | (50-120 MHz)   | fref · 2 | (25-60 MHz)      | $fref \cdot 4 \div 3$ | (16.6-40 MHz) |

|                           | 0      | 1     | 0     | 0     | fref · 2 | (25-60 MHz)    | fref · 4 | (50-120 MHz)     | fref · 2              | (25-60 MHz)   |

|                           | 0      | 1     | 0     | 1     | fref · 2 | (25-60 MHz)    | fref · 4 | (50-120 MHz)     | $fref \cdot 4 \div 3$ | (16.6-40 MHz) |

|                           | 0      | 1     | 1     | 0     | fref · 2 | (25-60 MHz)    | fref · 2 | (25-60 MHz)      | fref · 2              | (25-60 MHz)   |

|                           | 0      | 1     | 1     | 1     | fref · 2 | (25-60 MHz)    | fref · 2 | (25-60 MHz)      | $fref \cdot 4 \div 3$ | (16.6-40 MHz) |

|                           | 1      | 0     | 0     | 0     | fref · 2 | (25-60 MHz)    | fref · 2 | (25-60 MHz)      | fref                  | (12.5-30 MHz) |

|                           | 1      | 0     | 0     | 1     | fref · 2 | (25-60 MHz)    | fref · 2 | (25-60 MHz)      | $fref \cdot 2 \div 3$ | (8.33-20 MHz) |

|                           | 1      | 0     | 1     | 0     | fref · 2 | (25-60 MHz)    | fref     | (12.5-30 MHz)    | fref                  | (12.5-30 MHz) |

|                           | 1      | 0     | 1     | 1     | fref · 2 | (25-60 MHz)    | fref     | (12.5-30 MHz)    | $fref \cdot 2 \div 3$ | (8.33-20 MHz) |

|                           | 1      | 1     | 0     | 0     | fref     | (12.5-30 MHz)  | fref · 2 | (25-60 MHz)      | fref                  | (12.5-30 MHz) |

|                           | 1      | 1     | 0     | 1     | fref     | (12.5-30 MHz)  | fref · 2 | (25-60 MHz)      | $fref \cdot 2 \div 3$ | (8.33-20 MHz) |

|                           | 1      | 1     | 1     | 0     | fref     | (12.5-30 MHz)  | fref     | (12.5-30 MHz)    | fref                  | (12.5-30 MHz) |

|                           | 1      | 1     | 1     | 1     | fref     | (12.5-30 MHz)  | fref     | (12.5-30 MHz)    | $fref\cdot 2 \div 3$  | (8.33-20 MHz) |

<sup>1.</sup> fref is the input clock reference frequency (CCLK or XTAL).

Table 9. MPC9330 Example Configurations (External Feedback and PWR\_DN = 0)

| PLL<br>Feedback         | fref <sup>(1)</sup><br>[MHz] | FSELA | FSELB | FSELC | ELC QA[0:1]:fref ratio |              | A[0:1]:fref ratio QB[0:1]:fref ratio |              | QC[0:      | 1]:fref ratio |

|-------------------------|------------------------------|-------|-------|-------|------------------------|--------------|--------------------------------------|--------------|------------|---------------|

| VCO ÷ 4 <sup>(2)</sup>  | 50-120                       | 0     | 0     | 0     | fref                   | (50-120 MHz) | fref                                 | (50-120 MHz) | fref ÷ 2   | (25-60 MHz)   |

|                         |                              | 0     | 0     | 1     | fref                   | (50-120 MHz) | fref                                 | (50-120 MHz) | fref ÷ 3   | (16.6-40 MHz) |

|                         |                              | 0     | 1     | 0     | fref                   | (50-120 MHz) | fref ÷ 2                             | (25-60 MHz)  | fref ÷ 2   | (25-60 MHz)   |

|                         |                              | 0     | 1     | 1     | fref                   | (50-120 MHz) | fref ÷ 2                             | (25-60 MHz)  | fref ÷ 3   | (16.6-40 MHz) |

| VCO ÷ 8 <sup>(3)</sup>  | 25–60                        | 1     | 0     | 0     | fref                   | (25-60 MHz)  | fref · 2                             | (50-120 MHz) | fref       | (25-60 MHz)   |

|                         |                              | 1     | 0     | 1     | fref                   | (25-60 MHz)  | fref · 2                             | (50-120 MHz) | fref 2 ÷ 3 | (16.6-40 MHz) |

|                         |                              | 1     | 1     | 0     | fref                   | (25-60 MHz)  | fref                                 | (25-60 MHz)  | fref       | (25-60 MHz)   |

|                         |                              | 1     | 1     | 1     | fref                   | (25-60 MHz)  | fref                                 | (25-60 MHz)  | fref 2 ÷ 3 | (16.6-40 MHz) |

| VCO ÷ 12 <sup>(4)</sup> | 16.67-40                     | 0     | 0     | 1     | fref · 3               | (50-120 MHz) | fref · 3                             | (50-120 MHz) | fref       | (16.6-40 MHz) |

|                         |                              | 0     | 1     | 1     | fref · 3               | (50-120 MHz) | $fref \cdot 3 \div 2$                | (25-60 MHz)  | fref       | (16.6-40 MHz) |

|                         |                              | 1     | 0     | 1     | $fref \cdot 3 \div 2$  | (25-60 MHz)  | fref · 3                             | (50-120 MHz) | fref       | (16.6-40 MHz) |

|                         |                              | 1     | 1     | 1     | $fref \cdot 3 \div 2$  | (25-60 MHz)  | $fref \cdot 3 \div 2$                | (25-60 MHz)  | fref       | (16.6-40 MHz) |

<sup>1.</sup> fref is the input clock reference frequency (CCLK or XTAL).

Table 10. MPC9330 Example Configurations (External Feedback and PWR\_DN = 1)

| PLL<br>Feedback         | fref <sup>(1)</sup><br>[MHz] | FSELA | FSELB | FSELC | QA[      | QA[0:1]:fref ratio |          | QB[0:1]:fref ratio |            | QC[0:1]:fref ratio |  |

|-------------------------|------------------------------|-------|-------|-------|----------|--------------------|----------|--------------------|------------|--------------------|--|

| VCO ÷ 16 <sup>(2)</sup> | 12.5–30                      | 1     | 0     | 0     | fref     | (12.5-30 MHz)      | fref 2   | (25-60 MHz)        | fref       | (12.5-30 MHz)      |  |

|                         |                              | 1     | 0     | 1     | fref     | (12.5-30 MHz)      | fref 2   | (25-60 MHz)        | fref 2 ÷ 3 | (8.33-20 MHz)      |  |

|                         |                              | 1     | 1     | 0     | fref     | (12.5-30 MHz)      | fref     | (12.5-30 MHz)      | fref       | (12.5-30 MHz)      |  |

|                         |                              | 1     | 1     | 1     | fref     | (12.5-30 MHz)      | fref     | (12.5-30 MHz)      | fref 2 ÷ 3 | (8.33-20 MHz)      |  |

| VCO ÷ 24 <sup>(3)</sup> | 8.33-20                      | 0     | 0     | 1     | fref 3   | (25-60 MHz)        | fref 3   | (25-60 MHz)        | fref       | (8.33-20 MHz)      |  |

|                         |                              | 0     | 1     | 1     | fref 3   | (25-60 MHz)        | fref 3 ÷ | 2 (12.5-30 MHz)    | fref       | (8.33-20 MHz)      |  |

|                         |                              | 1     | 0     | 1     | fref 3 ÷ | 2 (12.5-30 MHz)    | fref 3   | (25-60 MHz)        | fref       | (8.33-20 MHz)      |  |

|                         |                              | 1     | 1     | 1     | fref 3 ÷ | 2 (12.5-30 MHz)    | fref 3 ÷ | 2 (12.5-30 MHz)    | fref       | (8.33-20 MHz)      |  |

<sup>1.</sup> fref is the input clock reference frequency (CCLK or XTAL).

<sup>2.</sup> QAx connected to FB\_IN and FSELA=0, PWR\_DN=0.

<sup>3.</sup> QAx connected to FB\_IN and FSELA=1, PWR\_DN=0.

<sup>4.</sup> QCx connected to FB\_IN and FSELC=1, PWR\_DN=0.

<sup>2.</sup> QAx connected to FB\_IN and FSELA=1, PWR\_DN=1.

<sup>3.</sup> QCx connected to FB\_IN and FSELC=1, PWR\_DN=1.

#### APPLICATIONS INFORMATION

#### **Power Supply Filtering**

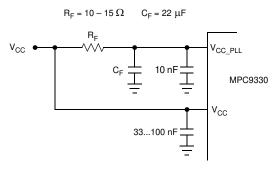

The MPC9330 is a mixed analog/digital product. Its analog circuitry is naturally susceptible to random noise, especially if this noise is seen on the power supply pins. Random noise on the V<sub>CC PLI</sub> power supply impacts the device characteristics, for instance, I/O jitter. The MPC9330 provides separate power supplies for the output buffers (V<sub>CC</sub>) and the phase-locked loop (V<sub>CC PLL</sub>) of the device. The purpose of this design technique is to isolate the high switching noise digital outputs from the relatively sensitive internal analog phase-locked loop. In a digital system environment where it is more difficult to minimize noise on the power supplies, a second level of isolation may be required. The simple but effective form of isolation is a power supply filter on the V<sub>CC PLL</sub> pin for the MPC9330. Figure 3 illustrates a typical power supply filter scheme. The MPC9330 frequency and phase stability is most susceptible to noise with spectral content in the 100 kHz to 20 MHz range. Therefore the filter should be designed to target this range. The key parameter that needs to be met in the final filter design is the DC voltage drop across the series filter resistor R<sub>F</sub>. From the data sheet, the  $I_{CC\ PLL}$  current (the current sourced through the  $V_{CC\ PLL}$  pin) is typically 5 mA (10 mA maximum), assuming that a minimum of 2.985 V must be maintained on the  $V_{CC\ PLL}$  pin. The resistor  $R_F$ shown in Figure 3 should have a resistance of 10–15  $\Omega$  to meet the voltage drop criteria.

Figure 3. V<sub>CC PLL</sub> Power Supply Filter

The minimum values for  $R_{\text{F}}$  and the filter capacitor  $C_{\text{F}}$  are defined by the required filter characteristics: the RC filter should provide an attenuation greater than 40 dB for noise whose spectral content is above 100 kHz. In the example RC filter shown in Figure 3, the filter cut-off frequency is around 3-5 kHz, and the noise attenuation at 100 kHz is better than 42 dB.

As the noise frequency crosses the series resonant point of an individual capacitor, its overall impedance begins to look inductive and, thus, increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the bandwidth of the PLL. Although the MPC9330 has several design features to minimize the susceptibility to power supply noise (isolated power and grounds and fully differential PLL), there still may be applications in which overall performance is being degraded due to system power supply noise. The power supply filter schemes discussed in this section should be adequate to eliminate power supply noise related problems in most designs.

#### **Driving Transmission Lines**

The MPC9330 clock driver was designed to drive high-speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user, the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of less than 20  $\Omega$ , the drivers can drive either parallel or series terminated transmission lines. For more information on transmission lines, the reader is referred to Freescale application note AN1091. In most high performance clock networks, point-to-point distribution of signals is the method of choice. In a point-to-point scheme, either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a 50  $\Omega$  resistance to  $V_{CC}\div 2$ .

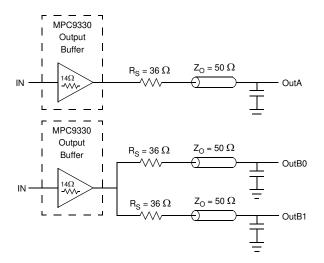

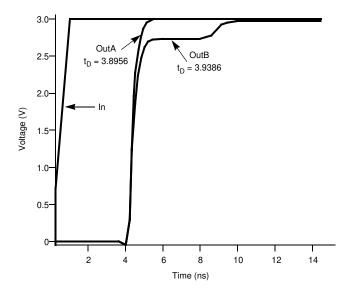

This technique draws a fairly high level of DC current and thus only a single terminated line can be driven by each output of the MPC9330 clock driver. For the series terminated case, however, there is no DC current draw, thus the outputs can drive multiple series terminated lines. Figure 4 illustrates an output driving a single series terminated line versus two series terminated lines in parallel. When taken to its extreme, the fanout of the MPC9330 clock driver is effectively doubled due to its capability to drive multiple lines.

Figure 4. Single versus Dual Transmission Lines

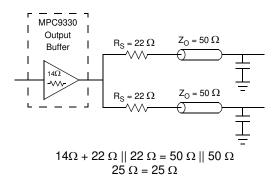

The waveform plots in Figure 4 show the simulation results of an output driving a single line versus two lines. In both cases, the drive capability of the MPC9330 output buffer is more than sufficient to drive 50  $\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations, a delta of only 43 ps exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output-to-output skew of the MPC9330. The output waveform in Figure 5 shows a step in the waveform; this step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the 36  $\Omega$  series resistor plus the output impedance does not match the parallel combination of the line impedances. The voltage wave launched down the two lines will equal:

$$\begin{split} &V_L = V_S \; (\; Z_0 \div (R_S + R_0 + Z_0)) \\ &Z_0 = 50 \; \Omega \; || \; 50 \; \Omega \\ &R_S = 36 \; \Omega \; || \; 36 \; \Omega \\ &R_0 = 14 \; \Omega \\ &V_L = 3.0 \; (25 \div (18 + 14 + 25)) \\ &= 1.31 \; V \end{split}$$