# SigmaDSP Digital Audio Processor

Data Sheet ADAU1472

#### **FEATURES**

270 MHz, 32-bit Cadence Tensilica HiFi 4 Audio DSP

Quad 32-bit × 32-bit MAC support per cycle

Single IEEE floating-point multiplier

320 kB L1 SRAM and 160 kB L1 cache

Large 2 MB L2 system SRAM

Accelerated math instruction extensions

C/C++ programmable with complete development toolkit

Software compatible with the HiFi DSP family

Voice detector with low power always listening mode and

DSP core wake up

Low latency audio path

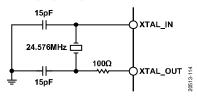

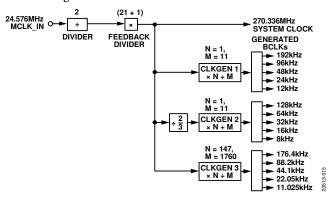

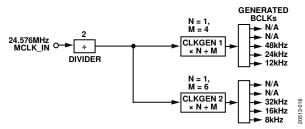

4 stereo asynchronous sample rate converters Clock oscillator for generating master clock from crystal Integer PLL and flexible clock generators

On-chip regulator for generating 1.2 V from IOVDD supply 6 digital audio input and output ports (serial ports) with 32-bit digital input/output supporting 8 kHz to 192 kHz operation Flexible serial data configuration with I<sup>2</sup>S, TDM, left and right

justified formats, pulse-code modulation (PCM), and bidirectional modes

S/PDIF receiver and transmitter—up to 96 kHz sample rate 14 digital PDM microphone input channels

2 stereo PDM output ports

SPI flash memory interface—up to 2 GB quad input/output serial flash

SPI control interfaces—slave and master with single, dual, and quad modes

I<sup>2</sup>C master interface

JTAG debug port

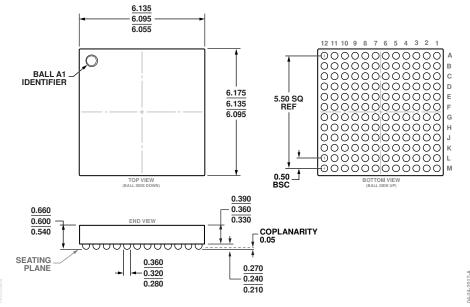

Boot ROM with self boot from serial memory 8 multipurpose pins for digital controls and outputs Dedicated event manager for host/driver communication 144-ball, 0.5 mm pitch, 6.095 mm × 6.135 mm WLCSP 0°C to 85°C temperature range

#### **APPLICATIONS**

Far field voice interface devices

Audio source separation

Embedded deep learning for audio

Commercial and professional audio processing

#### **GENERAL DESCRIPTION**

The ADAU1472 is a high quality SigmaDSP® digital audio processor with a large internal memory, enabling efficient audio source separation, far field voice capture, speech processing, deep learning, and advanced audio signal processing. The processor combines the highly optimized Cadence® Tensilica® HiFi® 4 audio/voice processor with custom Analog Devices, Inc., instruction extensions for math acceleration (shown in Table 20 and Table 21), and a flexible input and output architecture. The HiFi 4 processor supports four 32-bit × 32-bit multiplier accumulators (MACs) per cycle with 72-bit accumulators, dual 64-bit memory load, and a native Institute of Electrical and Electronics Engineers (IEEE) single precision, floating-point multiplier.

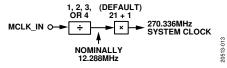

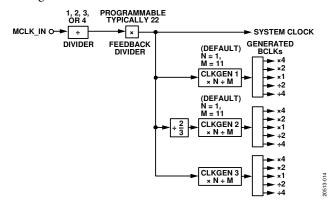

The ADAU1472 processor offers performance up to 270.336 MHz, supports low latency, sample by sample audio processing, and block by block processing paradigms in parallel. The integer phase-locked loop (PLL) and flexible clock generator hardware can generate up to 15 audio sample rates simultaneously (8 kHz to 192 kHz). These clock generators, along with the on-board asynchronous sample rate converters (ASRCs) and flexible hardware audio routing matrix, greatly simplify the design of complex audio systems.

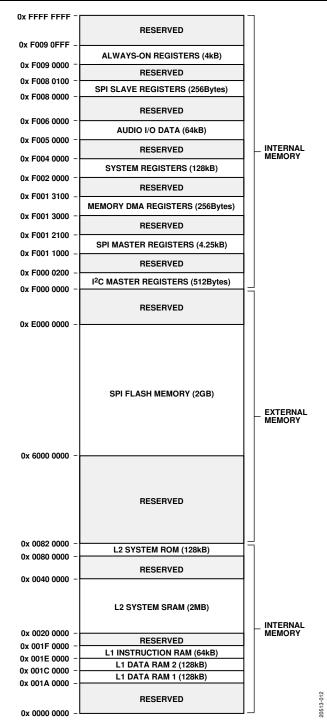

The HiFi 4 digital signal processor (DSP) core has 480 kB of L1 memory running at the DSP core clock rate, which consists of 256 kB data random access memory (RAM), 64 kB instruction RAM, 128 kB data cache, and 32 kB instruction cache, along with 2 MB of L2 system static random access memory (SRAM) running at one half of the DSP core clock rate. The processor also supports up to 2 GB of external flash memory to enable the storage of large data tables and self boot code.

Dual on-chip power domains allow low power operation, including the capability of routing audio through a flexible audio routing matrix with IOVDD as the only active supply. The configurable voice detection hardware can detect human speech onset while operating in a low power state and can generate both internal DSP and external wake-up signals.

Continued on Page 4

# **► ADI Sublime** Audio™

# **TABLE OF CONTENTS**

| Processor Reliability Features                        | 25 |

|-------------------------------------------------------|----|

| Timers                                                | 25 |

| Serial Ports                                          | 25 |

| ASRCs                                                 | 26 |

| Digital PDM Microphone Interface                      | 26 |

| PDM Outputs                                           | 26 |

| S/PDIF Interface                                      | 26 |

| SPI                                                   | 27 |

| Clock and Power Management                            | 27 |

| Pin Drive Strength, Slew Rate, and Pull Configuration | 29 |

| Power Supplies, Voltage Regulator, and Hardware Reset | 29 |

| Initialization                                        | 31 |

| System Debug                                          | 31 |

| Development Tools                                     | 31 |

| Applications Information                              | 32 |

| PCB Design Considerations                             | 32 |

| PCB Manufacturing Guidelines                          | 32 |

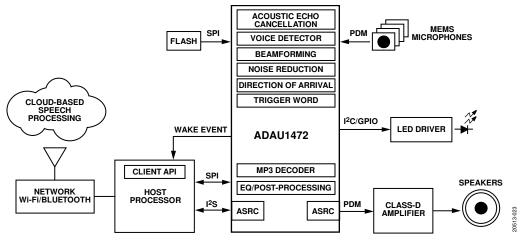

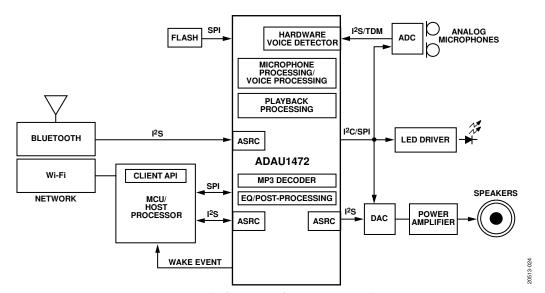

| Typical Applications Block Diagrams                   | 33 |

| Outline Dimensions                                    | 34 |

| Ordering Guide                                        | 34 |

#### **REVISION HISTORY**

11/2020—Revision 0: Initial Version

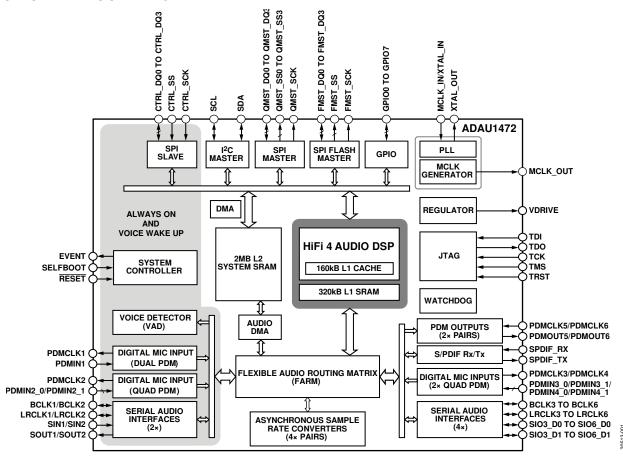

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The ADAU1472 interfaces with a wide range of analog-to-digital converters (ADCs), digital-to-analog converters (DACs), digital audio devices, amplifiers, and control circuitry due to its highly configurable serial ports, Sony/Philips digital interface format (S/PDIF) interfaces, and multipurpose input/output pins. The device can also directly interface with up to 14 pulse density modulated (PDM) output microphones due to integrated decimation filters specifically designed for that purpose. The PDM outputs with integrated interpolation filters provide direct connectivity to PDM input Class D amplifiers.

The processor has two serial peripheral interface (SPI) bus master control ports that allow the device to communicate with multiple SPI-compatible devices including support for single, dual, and quad input/output operation. In addition, the SPI flash port allows direct memory mapped read access with minimal central processing unit (CPU) overhead and standalone self boot operation.

The combined high performance DSP core, large RAM, and small footprint make the ADAU1472 an ideal replacement for large, general-purpose DSPs that consume more power for the same processing load.

**Table 1. Processor Features**

| Processor Feature | Value | Unit |

|-------------------|-------|------|

| Core Clock        | 270   | MHz  |

| L1 SRAM           | 320   | kB   |

| L1 Cache          | 160   | kB   |

| L2 System SRAM    | 2     | MB   |

Multifunction pin names may be referenced by their relevant function only.

# **SPECIFICATIONS**

#### **OPERATING CONDITIONS**

DVDD = 1.2 V  $\pm$  5%, PVDD = 1.2 V  $\pm$  5%, IOVDD = 1.8 V - 5% to 3.3 V + 10%, CVDD = 1.2 V  $\pm$  5%,  $T_A$  = 25°C, MCLK\_IN/XTAL\_IN = 24.576 MHz, core clock frequency ( $f_{CORE}$ ) = 270.336 MHz, and input/output pins set to low drive setting, unless otherwise noted.

Table 2.

| Parameter                           | Min  | Тур  | Max    | Unit | Test Conditions/Comments                                             |

|-------------------------------------|------|------|--------|------|----------------------------------------------------------------------|

| POWER                               |      |      |        |      |                                                                      |

| Supply Voltage                      |      |      |        |      |                                                                      |

| Digital Voltage (DVDD)              | 1.14 | 1.2  | 1.26   | V    | Supply for digital circuitry, DSP core, ASRCs, and signal routing    |

| PLL Voltage (PVDD)                  | 1.14 | 1.2  | 1.26   | V    | Supply for PLL circuitry                                             |

| Input/Output Voltage (IOVDD)        | 1.71 | 3.3  | 3.63   | V    | Supply for input/output circuitry, including pads and level shifters |

| Memory Core Voltage (CVDD)          |      |      |        |      |                                                                      |

| Operation State <sup>1</sup>        | 1.14 | 1.2  | 1.26   | V    | Supply for memory circuitry and retention                            |

| Power-Down State                    | 0.74 | 8.0  | 1.26   | V    | Supply for memory retention in power-down state                      |

| Supply Current                      |      |      |        |      |                                                                      |

| PLL Current (PVDD)                  |      | 480  |        | μΑ   | 24.576 MHz clock frequency with default PLL settings                 |

| Idle State                          |      | 30   |        | μΑ   | Power applied, PLL not configured                                    |

| Reset State                         |      | 7    |        | μΑ   | Power applied, RESET held low                                        |

| Input/Output Current (IOVDD)        |      |      |        |      | Dependent on active serial ports, clock pins, and external loads     |

| Operation State                     |      | 20   |        | mA   | IOVDD = 3.3 V, all serial ports are clock masters                    |

| Reset State                         |      | 0.6  |        | mA   | IOVDD = 3.3 V, RESET held low                                        |

| Digital Current (DVDD) <sup>1</sup> |      |      |        |      |                                                                      |

| Maximum Program                     |      | 210  |        | mA   | 100% CPU utilization, PLL = 270.336 MHz                              |

| Typical Program                     |      | 140  |        | mA   | 60% CPU utilization, PLL = 270.336 MHz                               |

| Idle State                          |      | 40   |        | mA   | Power applied, DSP idle (WAITI) <sup>2</sup> , PLL = 270.336 MHz     |

| Minimal Program                     |      | 25   |        | mA   | 60% CPU utilization, direct MCLK 24.576 MHz                          |

| Reset State                         |      | 5    |        | mA   | Power applied, RESET held low                                        |

| Circuit Voltage (CVDD)1             |      |      |        |      |                                                                      |

| Operation State                     |      | 100  |        | μΑ   |                                                                      |

| Memory Retention State              |      | 690  |        | μΑ   | CVDD = 1.2 V                                                         |

|                                     |      | 590  |        | μΑ   | CVDD = 0.8 V, power-down state with IOVDD not powered                |

| ASRCs                               |      |      |        |      |                                                                      |

| Dynamic Range                       |      | 139  |        | dB   | A-weighted, 20 Hz to 20 kHz                                          |

| Input/Output Sample Rate            | 8    |      | 192    | kHz  |                                                                      |

| Input/Output Sample Rate Ratio      | 1:8  |      | 7.75:1 |      |                                                                      |

| Total Harmonic Distortion Plus      |      |      | -120   | dB   |                                                                      |

| Noise (THD + N)                     |      |      |        |      |                                                                      |

| REGULATOR                           |      |      |        |      |                                                                      |

| DVDD Voltage                        | 1.14 | 1.2  |        | V    | Regulator maintains typical output voltage up to a maximum           |

|                                     |      |      |        |      | 800 mA load                                                          |

| CRYSTAL OSCILLATOR                  |      | 4    | 40.5   |      |                                                                      |

| Transconductance                    | 9.5  | 11.7 | 13.8   | mS   |                                                                      |

<sup>&</sup>lt;sup>1</sup> CVDD must remain powered when supplying DVDD or it may cause permanent damage to the device. The ADAU1472 supports a low power, memory retention mode. To use memory retention, disconnect DVDD and supply CVDD only with either 1.2 V or 0.8 V.

<sup>&</sup>lt;sup>2</sup> WAITI is the assembly language command that tells the processor to power down and wait for an interrupt. In this case, WAITI describes that the chip was set to DSP idle by using the WAITI command.

#### **ELECTRICAL CHARACTERISTICS**

Table 3.

| Parameter                         | Symbol          | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                           |

|-----------------------------------|-----------------|------|-----|------|------|----------------------------------------------------------------------------------------------------|

| DIGITAL INPUT/OUTPUT              |                 |      |     |      |      |                                                                                                    |

| Input Voltage <sup>1</sup>        |                 |      |     |      |      |                                                                                                    |

| High Level                        | V <sub>IH</sub> | 1.70 |     | 3.3  | V    | IOVDD = 3.3 V                                                                                      |

|                                   |                 | 0.96 |     | 1.8  | V    | IOVDD = 1.8 V                                                                                      |

| Low Level                         | V <sub>IL</sub> | 0    |     | 1.65 | ٧    | IOVDD = 3.3 V                                                                                      |

|                                   |                 | 0    |     | 0.88 | V    | IOVDD = 1.8 V                                                                                      |

| Output Voltage                    |                 |      |     |      |      |                                                                                                    |

| High Level                        | $V_{OH}$        | 3.09 |     | 3.3  | V    | $IOVDD = 3.3 V$ , high output current ( $I_{OH}$ ) = 1 mA                                          |

|                                   |                 | 1.45 |     | 1.8  | V    | IOVDD = 1.8 V                                                                                      |

| Low Level                         | V <sub>OL</sub> | 0    |     | 0.26 | V    | IOVDD = 3.3 V, I <sub>OH</sub> = 1 mA                                                              |

|                                   |                 | 0    |     | 0.33 | V    | IOVDD = 1.8 V                                                                                      |

| Input Leakage                     |                 |      |     |      |      |                                                                                                    |

| High Level                        | I <sub>IH</sub> |      |     |      |      |                                                                                                    |

|                                   |                 | -2   |     | +2   | μΑ   | Digital input pins with pull-up resistor <sup>2</sup>                                              |

|                                   |                 | 1    |     | 12   | μΑ   | Digital input pins with pull-down resistor <sup>2</sup>                                            |

|                                   |                 | -2   |     | +2   | μΑ   | Digital input pins with no pull resistor <sup>2</sup>                                              |

|                                   |                 | -2   |     | +2   | μΑ   | MCLK_IN/XTAL_IN                                                                                    |

|                                   |                 | 48   |     | 120  | μΑ   | SPDIF_RX                                                                                           |

| Low Level                         | I <sub>IL</sub> |      |     |      |      |                                                                                                    |

|                                   |                 | -12  |     | -3   | μΑ   | Digital input pins with pull-up resistor at 0 V <sup>2</sup>                                       |

|                                   |                 | -2   |     | +2   | μΑ   | Digital input pins with pull-down resistor at 0 V                                                  |

|                                   |                 | -2   |     | +2   | μΑ   | Digital input pins with no pull resistor at 0 V <sup>2</sup>                                       |

|                                   |                 | -2   |     | +2   | μΑ   | MCLK_IN/XTAL_IN at 0 V                                                                             |

|                                   |                 | -125 |     | -49  | μΑ   | SPDIF_RX at 0 V                                                                                    |

| Input Capacitance                 | C <sub>IN</sub> |      | 2   |      | рF   | Guaranteed by design, T <sub>A</sub> = 25°C                                                        |

| Digital Output Drive <sup>3</sup> |                 |      |     | 2    |      | Driving low impedance printed circuit board (PCB traces into a high impedance digital input buffer |

| IOVDD = 1.8 V                     |                 |      |     |      |      |                                                                                                    |

| Lowest Drive Strength Setting     |                 |      |     | 1    | mA   |                                                                                                    |

| Low Drive Strength Setting        |                 |      |     | 2    | mA   |                                                                                                    |

| High Drive Strength Setting       |                 |      |     | 3    | mA   |                                                                                                    |

| Highest Drive Strength Setting    |                 |      |     | 5    | mA   |                                                                                                    |

| IOVDD = 3.3 V                     |                 |      |     |      |      |                                                                                                    |

| Lowest Drive Strength Setting     |                 |      |     | 2    | mA   |                                                                                                    |

| Low Drive Strength Setting        |                 |      |     | 5    | mA   |                                                                                                    |

| High Drive Strength Setting       |                 |      |     | 10   | mA   |                                                                                                    |

| Highest Drive Strength Setting    |                 |      |     | 15   | mA   |                                                                                                    |

$<sup>^{\</sup>mbox{\tiny 1}}$  Digital input pins except SPDIF\_RX, which is not a standard digital input.

<sup>&</sup>lt;sup>2</sup> The digital input pins include the following: BCLKx, MCLK\_IN/XTAL\_IN, PDMIN1, LRCLKx, SINx, SPDIF\_RX, RESET, CTRL\_DQx, CTRL\_SCK, CTRL\_SS, PDMIN2\_x, SELFBOOT, TRST, TRST\_DEBUG, GPIOx, TMS, SIO3\_Dx, TMS\_DEBUG, SIO5\_Dx, TDI, SIO4\_Dx, TDI\_DEBUG, SDA, TCK, TCK\_DEBUG, SCL, SIO6\_Dx, PDMIN3\_x, QMST\_DQx, PDMCLK5, PDMIN4\_x, FMST\_DQx, and PDMCLK6.

<sup>&</sup>lt;sup>3</sup> The digital output pins, or all pins listed as output or I/O in Table 19, are not designed for static current draw. Do not use these pins to drive light emitting diodes (LEDs) directly. The digital output pins include: PDMCLKx, BCLKx, SOUTx, VDRIVE, XTAL\_OUT, LRCLKx, SPDIF\_TX, CVDD\_ON, DVDD\_ON, CTRL\_DQx, MCLK\_OUT, EVENT, GPIOx, SIO3\_Dx, TDO, SIO5\_Dx, TDO\_DEBUG, SIO4\_Dx, SDA, SCL, QMST\_SSx, SIO6\_Dx, QMST\_DQx, QMST\_SCK, PDMOUT5, FMST\_DQx, FMST\_SS, PDMOUT6, and FMST\_SCK.

#### POWER CONSUMPTION CHARACTERISTICS

Table 4 details power consumption estimates for various operation use cases.  $T_A = 25$ °C, MCLK\_IN = 24.576 MHz, DVDD = 1.2 V, PVDD = 1.2 V, IOVDD = 3.3 V, and CVDD = 1.2 V, unless otherwise noted.

The estimates are only for the internal logic power consumption. Total system power consumption includes additional IOVDD current, which is highly dependent on the active pins, drive strength settings, and external loads.

**Table 4. Power Dissipation Estimates**

| Parameter                            | Min T | ур Мах | Unit | Test Conditions/Comments                                                                                                                                 |

|--------------------------------------|-------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER CONSUMPTION                    |       |        |      |                                                                                                                                                          |

| Lowest Power Voice Detect            | 1     | 0      | mW   | IOVDD supply only, DVDD supply turned off, DSP off                                                                                                       |

| Direct MCLK, 12.288 MHz              | 2     | 6      | mW   | DSP core clock domain (SYSCLK) = 12.288 MHz, memory bus clock domain (BUSCLK) = 12.288 MHz, 100% DSP utilization, PLL off (SYSCLK = master clock (MCLK)) |

| Direct MCLK, 24.576 MHz,<br>DSP Idle | 2     | 5      | mW   | SYSCLK = 24.576 MHz, BUSCLK = 24.576 MHz, DSP idle (WAITI), PLL off (SYSCLK = MCLK)                                                                      |

| Direct MCLK, 24.576 MHz              | 4     | 2      | mW   | SYSCLK = 24.576 MHz, BUSCLK = 24.576 MHz, 100% DSP utilization, PLL off (SYSCLK = MCLK), lowest power voice trigger word                                 |

| PLL, 270.336 MHz, DSP Idle           | 6     | 5      | mW   | SYSCLK = 270.336 MHz, BUSCLK = 135.183 MHz, DSP idle (WAITI), PLL on                                                                                     |

| Full DSP Utilization                 | 2     | 70     | mW   | SYSCLK = 270.336 MHz, BUSCLK = 135.183 MHz, 100% DSP utilization, PLL on, 2:1 system/bus clock ratio                                                     |

Table 5 details an estimate for worst case power consumption in a typical use case. DVDD = 1.26 V, PVDD = 1.26 V, IOVDD = 3.6 V, and CVDD = 1.26 V, unless otherwise noted. See the Total Power Dissipation section for more information.

**Table 5. Maximum Power Dissipation**

| Parameter                 | Min | Тур | Max | Unit | Test Conditions/Comments                                        |

|---------------------------|-----|-----|-----|------|-----------------------------------------------------------------|

| MAXIMUM POWER DISSIPATION |     |     |     |      |                                                                 |

| $T_A = 25$ °C             |     | 350 |     | mW   | 100% DSP utilization, all ASRCs active, all supplies at maximum |

| $T_A = 70$ °C             |     | 420 |     | mW   |                                                                 |

#### **TIMING SPECIFICATIONS**

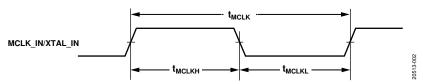

#### **Master Clock Input**

$T_A = 0$ °C to 70°C, DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%, unless otherwise noted.

Table 6.

| Parameter                            | Min                    | Тур | Max                           | Unit | Description                                       |

|--------------------------------------|------------------------|-----|-------------------------------|------|---------------------------------------------------|

| MASTER CLOCK INPUT (MCLK_IN/XTAL_IN) |                        |     |                               |      |                                                   |

| f <sub>MCLK</sub>                    | 12.288                 |     | 24.576                        | MHz  | MCLK_IN/XTAL_IN frequency, IOVDD = 1.8 V          |

|                                      | 12.288                 |     | 24.576                        | MHz  | MCLK_IN/XTAL_IN frequency, IOVDD = 3.3 V          |

| tmclk                                | 40.69                  |     | 81.38                         | ns   | MCLK_IN/XTAL_IN period                            |

| <b>t</b> MCLKD                       | 30                     |     | 70                            | %    | MCLK_IN/XTAL_IN duty cycle, not shown in Figure 2 |

| t <sub>MCLKH</sub>                   | $0.25 \times t_{MCLK}$ |     | $0.75 \times t_{\text{MCLK}}$ | ns   | MCLK_IN/XTAL_IN width high                        |

| t <sub>MCLKL</sub>                   | $0.25 \times t_{MCLK}$ |     | $0.75 \times t_{\text{MCLK}}$ | ns   | MCLK_IN/XTAL_IN width low                         |

| SYSTEM CLOCK                         |                        |     |                               |      |                                                   |

| fcore                                | 12.288                 |     | 270.336                       | MHz  | System (DSP core) clock frequency                 |

|                                      | 3.699                  |     |                               | ns   | System (DSP core) clock period                    |

Figure 2. Master Clock Input Timing Specifications

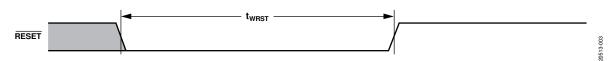

#### Reset

$T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ , DVDD = 1.2 V ± 5%, CVDD = 1.2 V ± 5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%.

#### Table 7.

| Parameter           | Min | Тур | Max | Unit | Description           |

|---------------------|-----|-----|-----|------|-----------------------|

| RESET               |     |     |     |      |                       |

| $\mathbf{t}_{WRST}$ | 500 |     |     | ns   | Reset pulse width low |

Figure 3. Reset Timing Specification

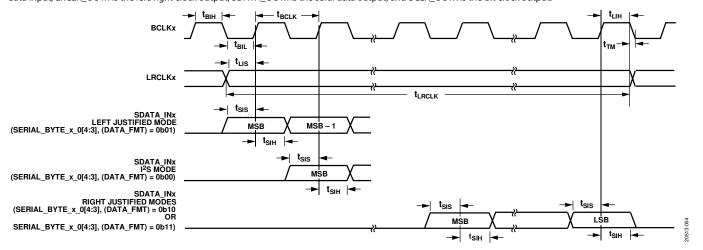

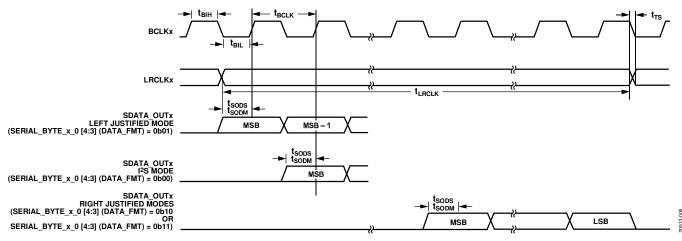

#### **Serial Ports**

$T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ , DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%, unless otherwise noted.

Table 8.

| Parameter             | Min  | Тур | Max    | Unit | Description <sup>1</sup>                                                                                                                                                                                                      |

|-----------------------|------|-----|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERIAL PORT           |      |     |        |      |                                                                                                                                                                                                                               |

| $f_{LRCLK}$           |      |     | 192    | kHz  | LRCLKx frequency, not shown in figures                                                                                                                                                                                        |

| turclk                | 5.21 |     |        | μs   | LRCLKx period                                                                                                                                                                                                                 |

| $f_{BCLK}$            |      |     | 24.576 | MHz  | BCLKx frequency, sample rate ranging from 8 kHz to 192 kHz, not shown in figures                                                                                                                                              |

| $t_{BCLK}$            | 40.7 |     |        | ns   | BCLKx period                                                                                                                                                                                                                  |

| $t_{\scriptsize BIL}$ | 10   |     |        | ns   | BCLKx low pulse width, slave mode; BCLKx frequency = 24.576 MHz; BCLKx period = 40.6 ns                                                                                                                                       |

| t <sub>BIH</sub>      | 14.5 |     |        | ns   | BCLKx high pulse width, slave mode; BCLKx frequency = 24.576 MHz; BCLKx period = 40.6 ns                                                                                                                                      |

| t <sub>LIS</sub>      | 20   |     |        | ns   | LRCLKx setup to BCLK_INx input rising edge, slave mode; LRCLKx frequency = 192 kHz                                                                                                                                            |

| t <sub>liH</sub>      | 5    |     |        | ns   | LRCLKx hold from BCLK_INx input rising edge, slave mode; LRCLKx frequency = 192 kHz                                                                                                                                           |

| $t_{\text{SIS}}$      | 5    |     |        | ns   | SDATA_INx setup to BCLK_INx input rising edge                                                                                                                                                                                 |

| t <sub>SIH</sub>      | 5    |     |        | ns   | SDATA_INx hold from BCLK_INx input rising edge                                                                                                                                                                                |

| t <sub>TS</sub>       |      |     | 10     | ns   | BCLK_OUTx output falling edge to LRCLK_OUTx output timing skew, slave                                                                                                                                                         |

| tsods                 |      |     | 35     | ns   | SDATA_OUTx delay in slave mode from BCLK_OUTx output falling edge; serial outputs function in slave mode at all valid sample rates, provided that the external circuit design provides sufficient electrical signal integrity |

| t <sub>SODM</sub>     |      |     | 10     | ns   | SDATA_OUTx delay in master mode from BCLK_OUTx output falling edge                                                                                                                                                            |

| t <sub>TM</sub>       |      |     | 5      | ns   | BCLK falling edge to LRCLK timing skew, master                                                                                                                                                                                |

<sup>&</sup>lt;sup>1</sup> BCLK\_INx is bit clock input, and x is the serial port that it is associated with. Note this is only when BCLK is configured as an input. In addition, SDATA\_INx is the serial data input, LRCLK\_OUTx is the left/right clock output, SDATA\_OUTx is the serial data output, and BCLK\_OUTx is the bit clock output.

Figure 4. Serial Input Port Timing Specifications

Figure 5. Serial Output Port Timing Specifications

#### **GPIOx Pins**

$T_A$  = 0°C to 70°C, DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%.

Table 9.

| Parameter                                                 | Min | Тур | Max | Unit | Description                                               |

|-----------------------------------------------------------|-----|-----|-----|------|-----------------------------------------------------------|

| GENERAL-PURPOSE INPUT/OUTPUT PINS (GPIOx)                 |     |     |     |      |                                                           |

| General-Purpose Frequency (f <sub>GP</sub> ) <sup>1</sup> |     |     | 1.0 | MHz  | Maximum switching rate of general-purpose input or output |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

#### **S/PDIF Transmitter**

$T_A = 0$ °C to 70°C, DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%.

Table 10.

| Parameter          | Min | Тур | Max | Unit | Description                                              |

|--------------------|-----|-----|-----|------|----------------------------------------------------------|

| S/PDIF TRANSMITTER |     |     |     |      |                                                          |

| Audio Sample Rate  | 18  |     | 96  | kHz  | Audio sample rate of data output from S/PDIF transmitter |

#### S/PDIF Receiver

$T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ , DVDD = 1.2 V ± 5%, CVDD = 1.2 V ± 5%, and IOVDD = 1.8 V – 5% to 3.3 V + 10%.

Table 11.

| Parameter         | Min | Тур | Max | Unit | Description                                        |

|-------------------|-----|-----|-----|------|----------------------------------------------------|

| S/PDIF RECEIVER   |     |     |     |      |                                                    |

| Audio Sample Rate | 18  |     | 96  | kHz  | Audio sample rate of data input to S/PDIF receiver |

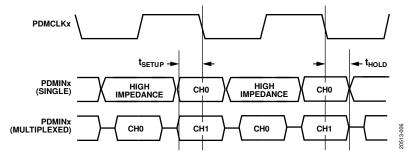

#### **PDM Inputs**

$T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ , DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%.

#### Table 12.

| Parameter           | Min | Тур | Max | Unit | Description     |

|---------------------|-----|-----|-----|------|-----------------|

| TIMING REQUIREMENTS |     |     |     |      |                 |

| tsetup              | 20  |     |     | ns   | Data setup time |

| thold               | 5   |     |     | ns   | Data hold time  |

Figure 6. PDM Input Timing Diagram

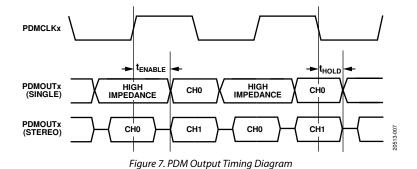

#### **PDM Outputs**

$T_{A} = 0 ^{\circ}\text{C to } 70 ^{\circ}\text{C}, DVDD = 1.2 \text{ V} \pm 5 \%, CVDD = 1.2 \text{ V} \pm 5 \%, IOVDD = 1.8 \text{ V} - 5 \% \text{ to } 3.3 \text{ V} + 10 \%, and PDMCLKx = 3.027 \text{ MHz}.$

Table 13.

| Parameter           | Min | Тур | Max | Unit | Description                  |

|---------------------|-----|-----|-----|------|------------------------------|

| TIMING REQUIREMENTS |     |     |     |      |                              |

| tenable             | 10  |     |     | ns   | Data driven after clock edge |

| t <sub>HOLD</sub>   | 5   |     | 11  | ns   | Data hold time               |

Rev. 0 | Page 10 of 34

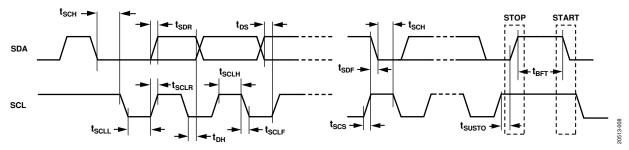

#### I<sup>2</sup>C Interface—Master

$T_A = 0$  °C to 70 °C, DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%.

Table 14.

| Parameter                    | Min | Тур | Max | Unit | Description                                   |

|------------------------------|-----|-----|-----|------|-----------------------------------------------|

| I <sup>2</sup> C MASTER PORT |     |     |     |      |                                               |

| $f_{SCL}$                    |     |     | 500 | kHz  | SCL clock frequency                           |

| <b>t</b> sclH                | 0.6 |     |     | μs   | SCL pulse width high                          |

| t <sub>SCLL</sub>            | 1.3 |     |     | μs   | SCL pulse width low                           |

| t <sub>SCS</sub>             | 0.6 |     |     | μs   | Start and repeated start condition setup time |

| t <sub>sch</sub>             | 0.6 |     |     | μs   | Start condition hold time                     |

| t <sub>DS</sub>              | 100 |     |     | ns   | Data setup time                               |

| t <sub>DH</sub>              | 0.9 |     |     | μs   | Data hold time                                |

| t <sub>SCLR</sub>            |     |     | 300 | ns   | SCL rise time                                 |

| t <sub>SCLF</sub>            |     |     | 300 | ns   | SCL fall time                                 |

| t <sub>SDR</sub>             |     |     | 300 | ns   | SDA rise time                                 |

| t <sub>SDF</sub>             |     |     | 300 | ns   | SDA fall time                                 |

| <b>t</b> <sub>BFT</sub>      | 1.3 |     |     | μs   | Bus free time between stop and start          |

| <b>t</b> susto               | 0.6 |     |     | μs   | Stop condition setup time                     |

Figure 8. I<sup>2</sup>C Master Port Timing Specifications

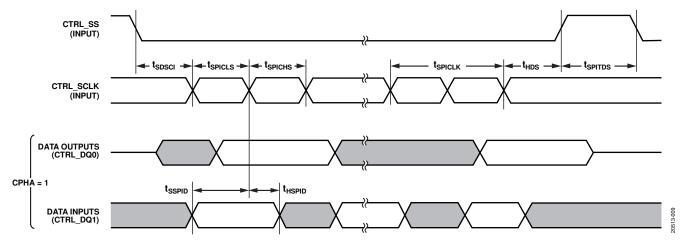

#### SPI Interface—Slave

$T_A = 0$ °C to 70°C, DVDD = 1.2 V  $\pm$  5%, CVDD = 1.2 V  $\pm$  5%, and IOVDD = 1.8 V - 5% to 3.3 V + 10%.

Table 15.

| Parameter                  | Min | Тур | Max    | Unit | Description                                                           |

|----------------------------|-----|-----|--------|------|-----------------------------------------------------------------------|

| SPI SLAVE PORT             |     |     |        |      |                                                                       |

| $f_{SCK_{WRITE}}$          | 1.7 |     | 24.576 | MHz  | CTRL_SCLK write frequency, cannot exceed MCLK frequency               |

| $f_{SCK_{READ}}$           | 1.7 |     | 12.288 | MHz  | CTRL_SCLK read frequency, cannot exceed (0.5 $\times$ MCLK) frequency |

| <b>t</b> <sub>SPICHS</sub> | 21  |     |        | ns   | CTRL_SCLK high period $(0.5 \times 1/f_{SCK} - 1)$                    |

| t <sub>SPICLS</sub>        | 6   |     |        | ns   | CTRL_SCLK low period $(0.5 \times 1/f_{SCK} - 1)$                     |

| t <sub>SPICLK</sub>        | 49  |     |        | ns   | CTRL_SCLK period (1/f <sub>SCK</sub> – 1)                             |

| t <sub>HDS</sub>           | 1   |     |        | ns   | Last CTRL_SCLK edge to CTRL_SS not asserted                           |

| <b>t</b> <sub>SPITDS</sub> | 49  |     |        | ns   | Sequential transfer delay $(1/f_{SCK} - 1)$                           |

| t <sub>SDSCI</sub>         | 10  |     |        | ns   | CTRL_SS assertion to first CTRL_SCLK edge                             |

| t <sub>SSPID</sub>         | 1   |     |        | ns   | Data input valid to CTRL_SCLK edge (data input setup)                 |

| t <sub>HSPID</sub>         | 2   |     |        | ns   | CTRL_SCLK sampling edge to data input invalid                         |

Figure 9. SPI Slave Port Timing Specification

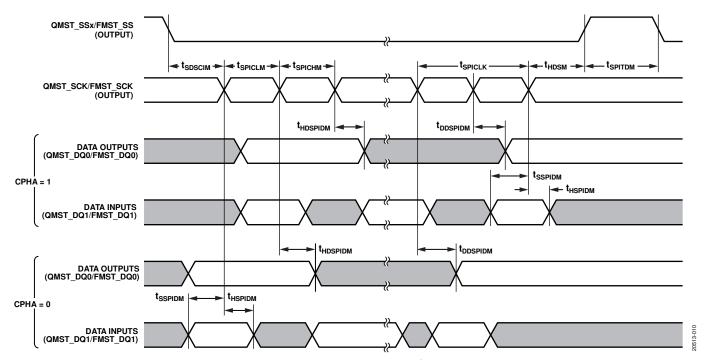

#### SPI Interface—Master

$T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ , DVDD = 1.2 V ± 5%, CVDD = 1.2 V ± 5%, and IOVDD = 1.8 V – 5% to 3.3 V + 10%.

Table 16.

| Parameter            | Min | Тур | Max    | Unit | Description                                                                    |

|----------------------|-----|-----|--------|------|--------------------------------------------------------------------------------|

| SPI MASTER PORT      |     |     |        |      |                                                                                |

| $f_{SCLK}$           |     |     | 24.576 | MHz  | SPI master clock frequency (QMST_SCK, FMST_SCK)                                |

| <b>t</b> sspidm      | 15  |     |        | ns   | Data input valid to QMST_SCK/FMST_SCK edge (data input setup)                  |

| <b>t</b> HSPIDM      | 5   |     |        | ns   | QMST_SCK/FMST_SCK sampling edge to data input invalid                          |

| t <sub>SDSCIM</sub>  | 38  |     |        | ns   | QMST_SSx/FMST_SS low to first QMST_SCK/FMST_SCK edge (1/f <sub>SCLK</sub> – 2) |

| t <sub>SPICLM</sub>  | 19  |     |        | ns   | QMST_SCK/FMST_SCK low period $(0.5 \times 1/f_{SCLK} - 1)$                     |

| <b>t</b> spichm      | 19  |     |        | ns   | QMST_SCK/FMST_SCK high period $(0.5 \times 1/f_{SCLK} - 1)$                    |

| <b>t</b> spiclk      | 39  |     |        | ns   | QMST_SCK/FMST_SCK period (1/f <sub>SCLK</sub> – 1)                             |

| t <sub>HDSM</sub>    | 38  |     |        | ns   | Last QMST_SCK/FMST_SCK edge to QMST_SSx/FMST_SS high (1/f <sub>SCLK</sub> – 2) |

| t <sub>SPITDM</sub>  | 39  |     |        | ns   | Sequential transfer delay (1/f <sub>SCLK</sub> – 1)                            |

| t <sub>HDSPIDM</sub> | 0   |     |        | ns   | QMST_SCK/FMST_SCK edge to data out valid (data out hold)                       |

| <b>t</b> ddspidm     |     |     | 5      | ns   | QMST_SCK/FMST_SCK edge to data out invalid (data out delay)                    |

Figure 10. SPI Master Port Timing Specifications

### **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings apply at 25°C, unless otherwise noted.

Table 17.

| Parameter          | Rating                        |

|--------------------|-------------------------------|

| DVDD to Ground     | 0 V to 1.4 V                  |

| CVDD to Ground     | 0 V to 1.4 V                  |

| IOVDD to Ground    | 0 V to 4.0 V                  |

| PVDD to Ground     | 0 V to 4.0 V                  |

| Digital Inputs     | DGND – 0.3 V to IOVDD + 0.3 V |

| Temperature        |                               |

| Ambient Range      | 0°C to 70°C                   |

| Junction Range     | 0°C to 85°C                   |

| Storage Range      | −65°C to +150°C               |

| Soldering (10 sec) | 300°C                         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal resistance values specified in Table 18 are simulated based on JEDEC specifications, unless specified otherwise, and must be used in compliance with JESD51-12.

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  represents the junction to ambient thermal resistance and is specified for recommended conditions, that is, a device soldered on a 4-layer circuit board with filled internal and external planes.  $\theta_{JC(TOP)}$  is junction to case (top) and  $\theta_{JB}$  is junction to board.

**Table 18. Thermal Resistance**

| Package Type          | θја   | $\theta_{\text{JC(TOP)}^2}$ | θјβ  | Ψл    | Ψјв  | Unit |

|-----------------------|-------|-----------------------------|------|-------|------|------|

| CB-144-2 <sup>1</sup> | 25.01 | 0.064                       | 1.42 | 0.024 | 1.46 | °C/W |

<sup>&</sup>lt;sup>1</sup> Using enhanced heat removal (such as PCB, heat sink, and airflow) technique improves thermal resistance values.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$  For  $\theta_{JC}$  test, 100  $\mu m$  thermal interface material (TIM) is used. TIM is assumed to have 3.6 W/mK.

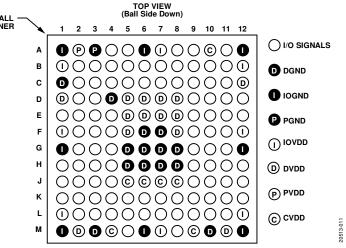

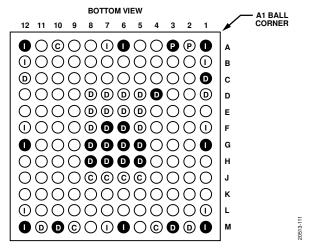

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 11. Ball Configuration, Top View (Not to Scale)

Figure 12. Ball Configuration, Bottom View (Not to Scale)

**Table 19. Ball Function Descriptions**

|          |          |                   | Internal                 |                                                                                                                                                                                                  |

|----------|----------|-------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball No. | Mnemonic | Type <sup>1</sup> | Termination <sup>2</sup> | Description                                                                                                                                                                                      |

| A1       | IOGND    | Ground            | None                     | Input/Output Ground Reference. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                    |

| A2       | PVDD     | Power             | None                     | PLL Supply, $1.2 \text{ V} \pm 5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to PGND. |

| A3       | PGND     | Ground            | None                     | PLL Ground Reference. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                             |

| A4       | PDMCLK1  | Output            | Pull-down                | PDM Input 1 Clock. Drives the PDM reference clock. The PDM inputs are always clock slaves.                                                                                                       |

| A5       | BCLK2    | I/O               | Pull-down                | Serial Port 2 Bit Clock. Data and frame clock are driven or sampled with respect to this clock. Input is in slave mode, and output is in master mode. Disconnect this ball when not in use.      |

| A6       | IOGND    | Ground            | None                     | Input/Output Ground Reference. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                    |

| A7       | IOVDD    | Power             | None                     | Input/Output Supply, $1.8V - 5\%$ to $3.3V + 10\%$ . Bypass this ball with decoupling capacitors to IOGND.                                                                                       |

| A8       | SOUT1    | Output            | Pull-down                | Serial Port 1 Output Data. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use.                                                                   |

Rev. 0 | Page 15 of 34

| Ball No. | Mnemonic        | Type <sup>1</sup> | Internal<br>Termination <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                |

|----------|-----------------|-------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A9       | BCLK1           | I/O               | Pull-down                            | Serial Port 1 Bit Clock. Data and frame clock are driven or sampled with respect to this clock. Input is in slave mode, and output is in master mode. Disconnect this ball when not in use.                                                                                                                |

| A10      | CVDD            | Power             | None                                 | Memory Circuitry Supply, $1.2 \text{ V} \pm 5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to IOGND.                                                                                             |

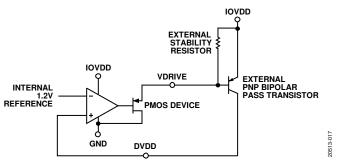

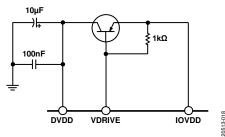

| A11      | VDRIVE          | Output            | None                                 | PNP Bipolar Junction Transistor Base Drive Bias Ball for the Digital Supply Regulator. Connect VDRIVE to the base of an external PNP pass transistor (the STD2805 is recommended). If an external supply is provided directly to DVDD, use a 10 k $\Omega$ pull-down resistor to ground on the VDRIVE pin. |

| A12      | IOGND           | Ground            | None                                 | Input/Output Ground Reference. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                                              |

| B1       | IOVDD           | Power             | None                                 | Input/Output Supply, 1.8 V – 5% to 3.3 V + 10%. Bypass this ball with decoupling capacitors to IOGND.                                                                                                                                                                                                      |

| B2       | XTAL_OUT        | Output            | None                                 | Crystal Oscillator. Circuit output. Disconnect this ball when not in use.                                                                                                                                                                                                                                  |

| B3       | MCLK_IN/XTAL_IN | Input             | None                                 | Reference Master Clock Input.                                                                                                                                                                                                                                                                              |

| B4       | PDMIN1          | Input             | Pull-down                            | PDM Input 1 Data.                                                                                                                                                                                                                                                                                          |

| B5       | LRCLK2          | I/O               | Pull-down                            | Serial Port 2 Frame Clock. Input is in slave mode, and output is in master mode.  Disconnect this ball when not in use.                                                                                                                                                                                    |

| B6       | SIN2            | Input             | Pull-down                            | Serial Port 2 Data Input. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use.                                                                                                                                                                              |

| B7       | SOUT2           | Output            | Pull-down                            | Serial Port 2 Data Output. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use.                                                                                                                                                                             |

| B8       | SIN1            | Input             | Pull-down                            | Serial Port 1 Data Input. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use.                                                                                                                                                                              |

| B9       | LRCLK1          | I/O               | Pull-down                            | Serial Port 1 Frame Clock. Input is in slave mode, and output is in master mode.  Disconnect this ball when not in use.                                                                                                                                                                                    |

| B10      | SPDIF_RX        | Input             | None                                 | S/PDIF Receiver. This ball is the input to the integrated S/PDIF receiver. Disconnect this ball when not in use. This ball is internally biased.                                                                                                                                                           |

| B11      | SPDIF_TX        | Output            | Pull-down                            | S/PDIF Transmitter. This ball is output from the integrated S/PDIF transmitter.  Disconnect this ball when not in use.                                                                                                                                                                                     |

| B12      | IOVDD           | Power             | None                                 | Input/Output Supply, 1.8 V – 5% to 3.3 V + 10%. Bypass this ball with decoupling capacitors to IOGND.                                                                                                                                                                                                      |

| C1       | DGND            | Ground            | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                                                             |

| C2       | RESET           | Input             | Pull-down                            | Active Low Reset Input. A reset is triggered on a high to low edge and exited on a low to high edge.                                                                                                                                                                                                       |

| C3       | CVDD_ON         | Output            | None                                 | External CVDD Supply Trigger. This ball requests an external supply to turn the CVDD ball power on or off (active high).                                                                                                                                                                                   |

| C4       | DVDD_ON         | Output            | None                                 | External DVDD Supply Trigger. This ball requests an external supply to turn the DVDD ball power on or off (active high).                                                                                                                                                                                   |

| C5       | CTRL_DQ3        | I/O               | Pull-down                            | SPI Slave Data 3. This ball transfers serial data in quad mode. Disconnect this ball when not in use.                                                                                                                                                                                                      |

| C6       | CTRL_DQ2        | I/O               | Pull-down                            | SPI Slave Data 2. This ball transfers serial data in quad mode. Disconnect this ball when not in use.                                                                                                                                                                                                      |

| C7       | CTRL_DQ1        | I/O               | Pull-down                            | SPI Slave Data 1. This ball transfers serial data. Master in, slave out (MISO) or dual/quad mode input/output.                                                                                                                                                                                             |

| C8       | CTRL_DQ0        | I/O               | Pull-down                            | SPI Slave Data 0. This ball transfers serial data. Master out, slave in (MOSI) or dual/quad mode input/output.                                                                                                                                                                                             |

| C9       | CTRL_SCLK       | Input             | Pull-down                            | SPI Slave Clock. This ball receives the serial clock from the master device on the SPI bus.                                                                                                                                                                                                                |

| C10      | CTRL_SS         | Input             | Pull-up                              | SPI Slave Select. This ball receives the slave select signal from the master device on the SPI bus.                                                                                                                                                                                                        |

| C11      | PDMIN2_1        | Input             | Pull-down                            | PDM Input 2 Data (D1).                                                                                                                                                                                                                                                                                     |

| Ball No. | Mnemonic   | Type <sup>1</sup> | Internal<br>Termination <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                    |

|----------|------------|-------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C12      | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| D1       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| D2       | MCLK_OUT   | Output            | Pull-down                            | Master Clock Reference Output. Drives a master clock signal to other ICs in the system and can be configured to output a divided down version of the reference clock. Disconnect this ball when not in use.                                                                                                                    |

| D3       | EVENT      | Output            | Pull-down                            | Wake-Up IRQ for External Host. Configurable polarity and output protocol (level sense, edge sense, or continuous pulse).                                                                                                                                                                                                       |

| D4       | RESERVED   | Ground            | Pull-down                            | Reserved. Connect an external pull-down resistor (1 $k\Omega$ ) from this ball to ground.                                                                                                                                                                                                                                      |

| D5       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| D6       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| D7       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| D8       | DVDD       | Power             | None                                 | Digital Supply, $1.2 \text{ V} \pm 5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                           |

| D9       | SELFBOOT   | Input             | Pull-down                            | Self Boot Select. This ball allows the device to perform a self boot from the external flash connected to the SPI flash port. When connected to IOVDD, a self boot operation is initiated on the next rising edge of $\overline{\text{RESET}}$ . This ball must be pulled up or down with a 1.0 k $\Omega$ or larger resistor. |

| D10      | TRST       | Input             | Pull-down                            | JTAG Test Reset. Joint test action group (JTAG) test access port reset. Connect a 2.0 k $\Omega$ pull-up resistor to IOVDD on the line connected to this ball. Connect this ball to DGND when not in use.                                                                                                                      |

| D11      | PDMIN2_0   | Input             | Pull-down                            | PDM Input 2 Data (D0).                                                                                                                                                                                                                                                                                                         |

| D12      | PDMCLK2    | Output            | Pull-down                            | PDM Input 2 Clock. This ball drives the PDM reference clock. The PDM inputs are always clock slaves.                                                                                                                                                                                                                           |

| E1       | BCLK3      | I/O               | Pull-down                            | Serial Port 3 Bit Clock. Data and frame clock are driven or sampled with respect to this clock. Input is in slave mode, and output is in master mode. Disconnect this ball when not in use.                                                                                                                                    |

| E2       | LRCLK3     | I/O               | Pull-down                            | Serial Port 3 Frame Clock. Input is in slave mode, and output is in master mode. Disconnect this ball when not in use.                                                                                                                                                                                                         |

| E3       | TRST_DEBUG | Input             | Pull-down                            | JTAG Debug Reset. JTAG debug port reset. Connect a 2.0 k $\Omega$ pull-up resistor to IOVDD on the line connected to this ball. Connect this ball to DGND when not in use.                                                                                                                                                     |

| E4       | GPIO5      | I/O               | Pull-down                            | General-Purpose Input/Output 5. Disconnect this ball when not in use.                                                                                                                                                                                                                                                          |

| E5       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| E6       | DVDD       | Power             | None                                 | Digital Supply, $1.2 \text{ V} \pm 5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                           |

| E7       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| E8       | DVDD       | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                                                                                      |

| Ball No. | Mnemonic  | Type <sup>1</sup> | Internal<br>Termination <sup>2</sup> | Description                                                                                                                                                                                                                                                           |

|----------|-----------|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E9       | GPIO0     | I/O               | Pull-down                            | General-Purpose Input/Output 0. Disconnect this ball when not in use.                                                                                                                                                                                                 |

| E10      | TMS       | Input             | Pull-down                            | JTAG Test Master Select. JTAG test access port mode select. Disconnect this ball when not in use.                                                                                                                                                                     |

| E11      | LRCLK5    | I/O               | Pull-down                            | Serial Port 5 Frame Clock. Input is in slave mode, and output is in master mode.  Disconnect this ball when not in use.                                                                                                                                               |

| E12      | BCLK5     | I/O               | Pull-down                            | Serial Port 5 Bit Clock. Data and frame clock are driven/sampled with respect to this clock. Input is in slave mode, and output is in master mode. Disconnect this ball when not in use.                                                                              |

| F1       | IOVDD     | Power             | None                                 | Input/Output Supply, 1.8 V – 5% to 3.3 V + 10%. Bypass this ball with decoupling capacitors to IOGND.                                                                                                                                                                 |

| F2       | SIO3_D0   | I/O               | Pull-down                            | Serial Port 3 Data Input/Output 0. Bidirectional data input/output can be configured as an output to transmit serial data, or as an input to receive serial data. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use. |

| F3       | TMS_DEBUG | Input             | Pull-down                            | JTAG Debug Master. Select JTAG debug mode select. Disconnect this ball when not in use.                                                                                                                                                                               |

| F4       | GPIO6     | I/O               | Pull-down                            | General-Purpose Input/Output 6. Disconnect this ball when not in use.                                                                                                                                                                                                 |

| F5       | DVDD      | Power             | None                                 | Digital Supply, $1.2 \text{ V} \pm 5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                  |

| F6       | DGND      | Power             | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                        |

| F7       | DGND      | Power             | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                        |

| F8       | DVDD      | Power             | None                                 | Digital Supply, $1.2V\pm5\%$ . This ball can be supplied externally or by using the internal regulator and external pass transistor. Bypass this ball with decoupling capacitors to DGND.                                                                             |

| F9       | GPIO1     | I/O               | Pull-down                            | General-Purpose Input/Output 1. Disconnect this ball when not in use.                                                                                                                                                                                                 |

| F10      | TDO       | Output            | Pull-down                            | JTAG Test Data Output. JTAG test access port data output. Disconnect this ball when not in use.                                                                                                                                                                       |

| F11      | SIO5_D0   | I/O               | Pull-down                            | Serial Port 5 Data Input/Output 0. Bidirectional data input/output can be configured as an output to transmit serial data, or as an input to receive serial data. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use. |

| F12      | IOVDD     | Power             | None                                 | Input/Output Supply, $1.8V - 5\%$ to $3.3V + 10\%$ . Bypass this ball with decoupling capacitors to IOGND.                                                                                                                                                            |

| G1       | IOGND     | Ground            | None                                 | Input/Output Ground Reference. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                         |

| G2       | SIO3_D1   | I/O               | Pull-down                            | Serial Port 3 Data Input/Output 1. Bidirectional data input/output can be configured as an output to transmit serial data, or as an input to receive serial data. This ball is configurable from one to eight channels of data. Disconnect this ball when not in use. |

| G3       | TDO_DEBUG | Output            | Pull-down                            | JTAG Test Data Output. JTAG debug port data output. Disconnect this ball when not in use.                                                                                                                                                                             |

| G4       | GPIO7     | I/O               | Pull-down                            | General-Purpose Input/Output 7. Disconnect this ball when not in use.                                                                                                                                                                                                 |

| G5       | DGND      | Ground            | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                        |

| G6       | DGND      | Ground            | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                        |

| G7       | DGND      | Ground            | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                        |

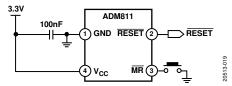

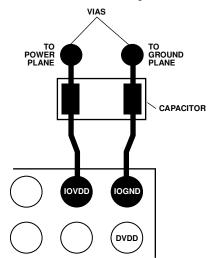

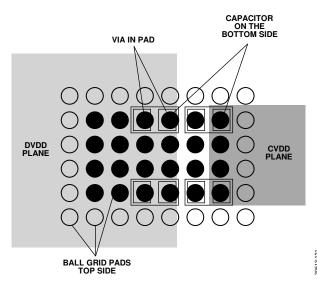

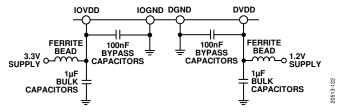

| G8       | DGND      | Ground            | None                                 | Digital Ground. Tie all DGND, IOGND, and PGND pins directly together in a common ground plane.                                                                                                                                                                        |