## **Ultra3 LVD/SE SCSI 15-Line Terminator**

### www.maxim-ic.com

### **GENERAL DESCRIPTION**

The DS2125 Ultra3 LVD/SE SCSI terminator is both a low-voltage differential (LVD) and single-ended (SE) terminator. The multimode operation enables the designer to implement LVD in current products while allowing the end user SE backward compatibility with legacy devices. If the device is connected in an LVD-only bus, the DS2125 uses LVD termination. If any SE devices are connected to the bus, the DS2125 uses SE termination, which is accomplished automatically inside the part by sensing the voltage on the SCSI bus DIFFSENS line.

For the LVD termination, the DS2125 integrates two current sources with 15 precision resistor strings. For the SE termination, one regulator and 15 precision  $110\Omega$  resistors are used. Two DS2125 terminators are needed for a wide SCSI bus.

### **APPLICATIONS**

Raid Systems SCSI Host Bus Adapter (HBA) Cards Servers SCSI Cables Network Attached Storage (NAS) Storage Area Networks (SANs)

### ORDERING INFORMATION

| PART*      | PIN-PACKAGE           | TOP MARK** |

|------------|-----------------------|------------|

| DS2125     | 48 LQFP               | DS2125     |

| DS2125+    | 48 LQFP               | DS2125     |

| DS2125/T&R | 48 LQFP/Tape and Reel | DS2125     |

| DS2125+T&R | 48 LQFP/Tape and Reel | DS2125     |

<sup>\*</sup>All devices rated over the commercial operating temperature range,  $0 \, ^{\circ}$  to +70  $^{\circ}$ C.

### **FEATURES**

- Fully Compliant with Ultra3 SCSI

- Provides Multimode Low-Voltage Differential/Single-Ended (LVD/SE) Termination for 15 Signal Line Pairs

- Auto-Selection of LVD or SE Termination

- 5% Tolerance on SE and LVD Termination Resistance

- Low 3pF Power-Down Capacitance

- On-Board Thermal-Shutdown Circuitry

- SCSI Bus Hot-Plug Compatible

- Fully Supports Actively Negated SE SCSI Signals

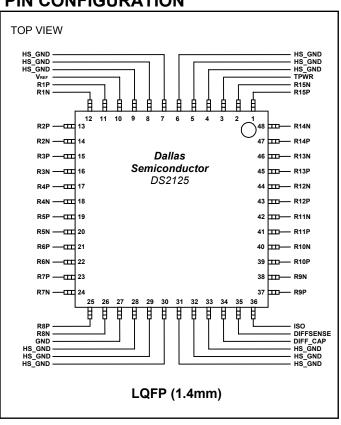

## PIN CONFIGURATION

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

1 of 7 REV: 012306

<sup>\*\*</sup>The top mark includes a "+" for lead-free packages.

<sup>+</sup>Denotes lead-free/RoHS-compliant package.

## **ABSOLUTE MAXIMUM RATINGS**

| $V_{REF}$ , ISO, GND, DIFFSENSE, DIFF_CAP, TPWR, RxP, RxN (x = 1 15) | 0.3V, +6.0V    |

|----------------------------------------------------------------------|----------------|

| V <sub>REF</sub> Continuous Output Current                           | ±200mA         |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C), 48-Pin LQFP   | 2W             |

| Operating Temperature Range                                          | 0°C to +70°C   |

| Junction Temperature                                                 | +150°C         |

| Storage Temperature Range                                            | 65°C to +160°C |

| Lead Temperature (soldering, 10s)                                    | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(TPWR = 3.3V,  $T_A = 0$ °C to +70°C, unless otherwise noted.)

| PARAMETER                                        | SYMBOL                | CONDITIONS                                                                                                                                                                                                                                                            | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| TPWR Operating Supply                            | $V_{TPWR}$            | LVD                                                                                                                                                                                                                                                                   | 2.7   |      | 5.5   | V     |

| Range                                            |                       | SE                                                                                                                                                                                                                                                                    | 4.0   |      | 5.5   | V     |

| TPWR SUPPLY CURREN                               | T                     |                                                                                                                                                                                                                                                                       |       |      |       |       |

| TPWR Supply Current<br>(All Lines Open)          | I <sub>TPWR_LVD</sub> | LVD SCSI mode                                                                                                                                                                                                                                                         |       | 20   | 32    | mA    |

|                                                  | I <sub>TPWR_SE</sub>  | SE SCSI mode                                                                                                                                                                                                                                                          |       | 1.6  | 10    | mA    |

| (All Ellies Open)                                | I <sub>TPWR_ISO</sub> | ISO mode (terminators disabled)                                                                                                                                                                                                                                       |       | 250  | 750   | μΑ    |

| LVD TERMINATION (Appl                            | ies to each line      | e pair, 1 to 15 in LVD mode)                                                                                                                                                                                                                                          |       |      |       |       |

| Differential-Mode<br>Termination Resistance      | R <sub>DM</sub>       |                                                                                                                                                                                                                                                                       | 100   |      | 110   | Ω     |

| Common-Mode<br>Termination Resistance            | R <sub>CM</sub>       | R <sub>P</sub> and R <sub>N</sub> shorted together                                                                                                                                                                                                                    | 110   |      | 165   | Ω     |

| Differential-Mode Bias                           | $V_{DM}$              | All lines open                                                                                                                                                                                                                                                        | 100   |      | 125   | mV    |

| Common-Mode Bias                                 | $V_{CM}$              | R <sub>P</sub> and R <sub>N</sub> shorted together                                                                                                                                                                                                                    | 1.15  | 1.25 | 1.35  | V     |

| SE TERMINATION (Applie                           | s to SE termin        |                                                                                                                                                                                                                                                                       |       |      |       |       |

| Single-Ended Mode<br>Termination Resistance      | R <sub>SE</sub>       | $\begin{aligned} R_{SE} &= (V_{Lx} - 0.2) \ / \ I_{Lx}, \\ \text{where } V_{Lx} &= \text{voltage at terminator} \\ \text{pin with pin unloaded and} \\ I_{Lx} &= \text{current for each terminator pin} \\ \text{with the pin forced to 0.2V (Note 2)} \end{aligned}$ | 104.5 | 110  | 115.5 | Ω     |

| Termination Current                              | I <sub>SE</sub>       | Signal level at 0.2V, all lines low                                                                                                                                                                                                                                   | -21.0 | -24  | -25.4 | mA    |

| (Note 2)                                         | ISE                   | Signal level at 0.5V                                                                                                                                                                                                                                                  | -18.0 |      | -22.4 | ША    |

| SE Voltage Reference                             | $V_{REF}$             | (Note 2)                                                                                                                                                                                                                                                              | 2.7   | 2.85 | 3.0   | V     |

| Pin Leakage                                      |                       | With ISO high                                                                                                                                                                                                                                                         |       |      | 400   | nA    |

| Single-Ended GND<br>Resistance                   | R <sub>GND</sub>      | Measured at R <sub>P</sub> pins, I = 10mA                                                                                                                                                                                                                             |       | 20   | 60    | Ω     |

| TERMINATOR PIN CAPA                              | CITANCE               |                                                                                                                                                                                                                                                                       |       |      |       |       |

| Terminator Pin Capacitance                       | C <sub>IN</sub>       | With ISO high (Note 1)                                                                                                                                                                                                                                                |       |      | 3     | pF    |

| V <sub>REF</sub> REGULATOR                       |                       |                                                                                                                                                                                                                                                                       |       |      |       | •     |

| 1.25V Regulator Output Voltage                   | V <sub>REF_LVD</sub>  |                                                                                                                                                                                                                                                                       | 1.15  | 1.25 | 1.35  | V     |

| 1.25V Regulator Short-<br>Circuit Source Current | I <sub>SOURCE</sub>   | V <sub>REF</sub> = 0V                                                                                                                                                                                                                                                 | -375  | -700 | -1000 | mA    |

| 1.25V Regulator Short-<br>Circuit Sink Current   | I <sub>SINK</sub>     | V <sub>REF</sub> = 3.3V                                                                                                                                                                                                                                               | 170   | 300  | 700   | mA    |

| 1.25V Regulator Line<br>Regulation               |                       | V <sub>REF</sub> unloaded; vary TPWR from 2.7V to 5.5V                                                                                                                                                                                                                |       | 1.0  | 2.5   | %     |

| 2.85V Regulator                                  |                       | (Note 2)                                                                                                                                                                                                                                                              | 2.7   | 2.85 | 3.0   | V     |

| 2.85V Regulator Short-<br>Circuit Source Current |                       | V <sub>REF</sub> = 0V (Note 2)                                                                                                                                                                                                                                        | -375  | -700 | -1000 | mA    |

| 2.85V Regulator Short-<br>Circuit Sink Current   |                       | V <sub>REF</sub> = 3.3V (Note 2)                                                                                                                                                                                                                                      | 170   | 300  | 700   | mA    |

# **ELECTRICAL CHARACTERISTICS (continued)**

(TPWR = 3.3V,  $T_A = 0$ °C to +70°C, unless otherwise noted.)

| PARAMETER                         | SYMBOL                  | CONDITIONS                                                         | MIN  | TYP  | MAX                     | UNITS |

|-----------------------------------|-------------------------|--------------------------------------------------------------------|------|------|-------------------------|-------|

| V <sub>REF</sub> REGULATOR        |                         |                                                                    |      |      |                         | •     |

| 2.85V Regulator Line Regulation   |                         | V <sub>REF</sub> unloaded; vary TPWR from 4.0V to 5.5V             |      | 1.0  | 2.5                     | %     |

| DIFFSENS OUTPUT                   |                         |                                                                    |      |      |                         |       |

| DIFFSENS Driver Output<br>Voltage | V <sub>DSO</sub>        | $-5mA \leq I_{DFFSENS} \leq 50 \mu A$                              | 1.2  |      | 1.4                     | V     |

| DIFFSENS Driver Source<br>Current | I <sub>DSH</sub>        | V <sub>DIFFSENS</sub> = 0V                                         | -15  |      | -5                      | mA    |

| DIFFSENS Driver Sink<br>Current   | I <sub>DSL</sub>        | V <sub>DIFFSENS</sub> = 3.3V                                       | 100  |      | 200                     | μΑ    |

| DIEESENS Lookago                  | I <sub>LEAK, LOW</sub>  | With ISO high,  V <sub>DIFFSENS</sub>   = 0.3V                     | -3   |      | +1                      |       |

| DIFFSENS Leakage<br>(Note 3)      | I <sub>LEAK, HIGH</sub> | With ISO high,  V <sub>DIFFSENS</sub> - V <sub>TPWR</sub>   = 0.3V | 1    |      | 3                       | μΑ    |

| THERMAL SHUTDOWN                  |                         |                                                                    |      |      |                         | ı     |

| Thermal-Shutdown<br>Threshold     |                         | For increasing temperature (Note 1)                                |      | 150  |                         | °C    |

| Thermal-Shutdown<br>Hysteresis    |                         | (Note 1)                                                           |      | 10   |                         | °C    |

| MODE CHANGE DELAY/F               | ILTER                   |                                                                    |      |      |                         | •     |

| Mode Change Delay                 | t <sub>DELAY</sub>      |                                                                    | 0.66 | 1.25 | 2.00                    | ms    |

| LOGICAL SIGNALS (ISO)             |                         |                                                                    |      |      |                         |       |

| Input Low Voltage                 | $V_{IL}$                |                                                                    | -0.3 |      | +0.8                    | V     |

| Input High Voltage                | V <sub>IH</sub>         |                                                                    | 2    |      | TPWR<br>+ 0.3           | V     |

| Input Current                     | I <sub>IL</sub>         | V <sub>CC</sub> = 3.3V                                             | -30  | -10  |                         | μΑ    |

| DIFF_CAP                          |                         |                                                                    |      |      |                         | _     |

| Input Current                     | Iμ                      | V <sub>IL</sub> = -0.3V                                            | -1   |      | +1                      | μΑ    |

| DIFF_CAP SE<br>Operating Range    | V <sub>SEOR</sub>       |                                                                    | -0.3 |      | +0.5                    | V     |

| DIFF_CAP LVD<br>Operating Range   | V <sub>LVDOR</sub>      |                                                                    | 0.7  |      | 1.9                     | V     |

| DIFF_CAP HVD<br>Operating Range   | V <sub>HVDOR</sub>      |                                                                    | 2.4  |      | V <sub>TPWR</sub> + 0.3 | V     |

Note 1: Guaranteed by design.

**Note 2:** TPWR = 4.0V.

Note 3: Room temperature only.

## **PIN DESCRIPTION**

| PIN                   | NAME      | FUNCTION                                                                                                                                                    |  |  |

|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 2, 11–26,<br>37–48 | RxP, RxN  | Signal Termination. Connect to SCSI bus signal lines.                                                                                                       |  |  |

| 3                     | TPWR      | Termination Power. Connect to the SCSI TERMPWR line and decouple with a $2.2\mu F$ capacitor.                                                               |  |  |

| 4–9, 28–33            | HS_GND    | Heat-Sink Ground. Internally connected to the mounting pad. This should be grounded.                                                                        |  |  |

| 10                    | $V_{REF}$ | Reference Voltage. 2.85V reference in SE mode and 1.25V reference in LVD mode; must be decoupled with a $4.7\mu F$ capacitor.                               |  |  |

| 27                    | GND       | Ground. Signal ground, 0V.                                                                                                                                  |  |  |

| 34                    | DIFF_CAP  | DIFFSENSE Capacitor. Connect a 0.1µF capacitor for the DIFFSENSE filter. Input to detect the type of device (differential or single-ended) on the SCSI bus. |  |  |

| 35                    | DIFFSENSE | DIFFSENSE. Output to drive the SCSI bus DIFFSENS line.                                                                                                      |  |  |

| 36                    | ISO       | Isolation. When pulled high, the DS2125 isolates its bus pins (RxN, RxP) from the SCSI bus.                                                                 |  |  |

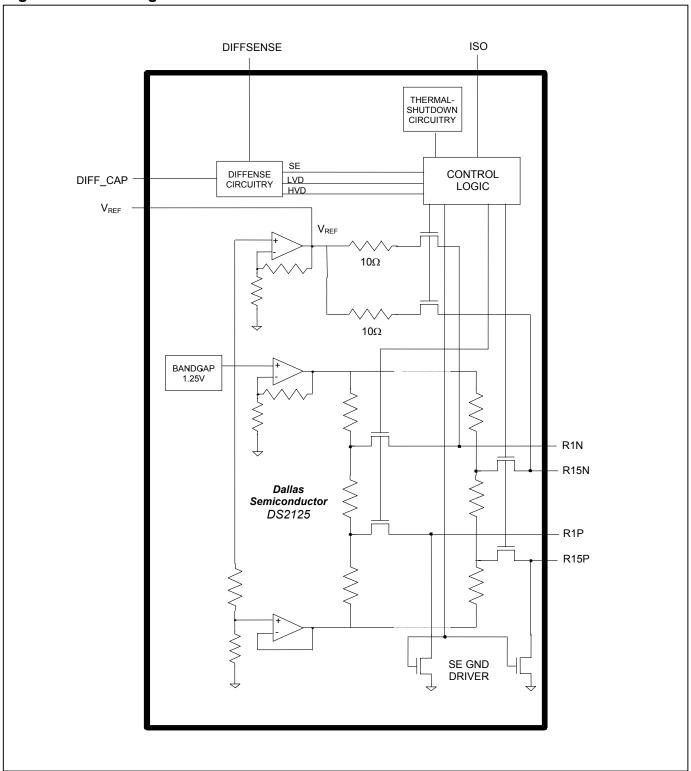

Figure 1. Block Diagram

**TERMPWR** TERMPWR **TPWR** TPWR ISO ISO CONTROL LINES (15) DIFFSENSE **DIFFSENS DIFFSENS** DIFF CAP DIFF\_CAP  $V_{REF}$  $20k\Omega$  $20k\Omega$ 0.1μF 0.1μF TPWR **TPWR** ISO ISO CONTROL LINES (15) **DIFFSENS DIFFSENS** DIFF\_CAP  $V_{REF}$ DIFF CAP

Figure 2. SCSI Bus Configuration

**Note:** The following terms are used throughout this data sheet:

DIFFSENS: Refers to the SCSI bus signal.

DIFFSENSE: Refers to the DS2125 pin name and internal circuitry capable of driving the DIFFSENS line. DIFF\_CAP: Refers to the DS2125 pin name and internal circuitry relating to monitoring the DIFFSENS line.

### **DETAILED DESCRIPTION**

The DS2125 combines LVD and SE termination with DIFFSENSE sourcing and detection. A bandgap reference is fed into two amplifiers, which creates a 1.25V reference voltage and a 2.85V reference voltage. The control logic determines which of these references are applied to the termination resistors. If the SCSI bus is in LVD mode, the 1.25V reference is used. If the SCSI bus is in SE mode, the 2.85V reference is used. That same control logic switches in/out parallel resistors to change the total termination resistance accordingly. Finally, in SE mode the  $R_{\rm p}$  pins are switched to ground.

The DIFFSENSE circuitry decodes trinary logic. There is one of three voltages on the SCSI control line called DIFFSENS. Two comparators and a NAND gate determine if the voltage is below 0.6V, above 2.15V, or in between, which indicates the mode of the bus as SE, HVD, or LVD, respectively.

The DS2125's DIFF\_CAP pin monitors the DIFFSENS line to determine the device's proper operating mode. The DIFFSENSE pin can also drive the SCSI DIFFSENS line to determine the SCSI bus-operating mode. The DS2125 switches to the termination mode that is appropriate for the bus based on the value of the DIFFSENS voltage. These modes are LVD mode, SE mode, and HVD isolation mode.

#### LVD MODE

A precision laser-trimmed resistor string with two amplifiers provides LVD termination. This configuration yields  $105\Omega$  differential and  $150\Omega$  common-mode impedance. A 112mV fail-safe bias is maintained when no drivers are connected to the SCSI bus.

### SE MODE

When the external driver for a given signal line turns off, the active terminator pulls that signal line to 2.85V (quiescent state). The terminating resistors maintain their  $110\Omega$  value.

#### **HVD ISOLATION MODE**

The DS2125 identifies that there is an HVD device on the SCSI bus and isolates the termination pins from the bus.

When ISO is pulled high, the termination pins are isolated from the SCSI bus, and  $V_{REF}$  remains active. During thermal shutdown, the termination pins are isolated from the SCSI bus, and  $V_{REF}$  becomes high impedance. The DIFFSENSE driver is shut down during either of these two events. An internal pulldown resistor assures that the DS2125 is terminating the bus if the ISO pin is left floating.

To ensure proper operation, the TPWR pin should be connected to the SCSI bus TERMPWR line. As with all analog circuitry, the TERMPWR and  $V_{DD}$  lines should be bypassed locally. A  $2.2\mu F$  capacitor and a  $0.01\mu F$  high-frequency capacitor are recommended between TPWR and ground, and placed as close as possible to the DS2125. The DS2125 should be placed as close as possible to the SCSI connector to minimize signal and power trace length, thereby resulting in less input capacitance and reflections, which can degrade the bus signals.

To maintain the specified regulation, a  $4.7\mu F$  capacitor is required between the  $V_{REF}$  pin and ground of each DS2125. A high-frequency capacitor (0.1 $\mu F$  ceramic recommended) can also be placed on the  $V_{REF}$  pin in applications that use fast rise/fall-time drivers. Figure 2 shows a typical SCSI bus configuration.

### REFERENCE DOCUMENTS

| TITLE                             | T10 PROJECT<br>DOCUMENT | T10 COMMITTEE FTP LINK                         | ANSI<br>DOCUMENT NO. |

|-----------------------------------|-------------------------|------------------------------------------------|----------------------|

| SCSI Parallel Interface 2 (SPI-2) | Project: 1142-M, 1998   | ftp://ftp.t10.org/t10/drafts/spi2/spi2r20b.pdf | X3.302:1998          |

| SCSI Parallel Interface 3 (SPI-3) | Project: 1302-D, 1999   | ftp://ftp.t10.org/t10/drafts/spi3/spi3r14.pdf  | NCITS.336:2000       |

| SCSI Parallel Interface 4 (SPI-4) | Project: 1365-D, 200x   | ftp://ftp.t10.org/t10/drafts/spi4/spi4r10.pdf  | INCITS.362:2002      |

## **SUPPLIERS**

| SUPPLIER                                     | PHONE        | WEBSITE                |

|----------------------------------------------|--------------|------------------------|

| American National Standards Institute (ANSI) | 212-642-4900 | www.ansi.org/          |

| Global Engineering Documents                 | 800-854-7179 | http://global.ihs.com/ |

### CHIP INFORMATION

TRANSISTOR COUNT: 8382 MOS and 87 BiPOLAR

PROCESS: BiCMOS

SUBSTRATE CONNECTED TO GROUND

### THERMAL INFORMATION

Theta-JA: 65°C/W

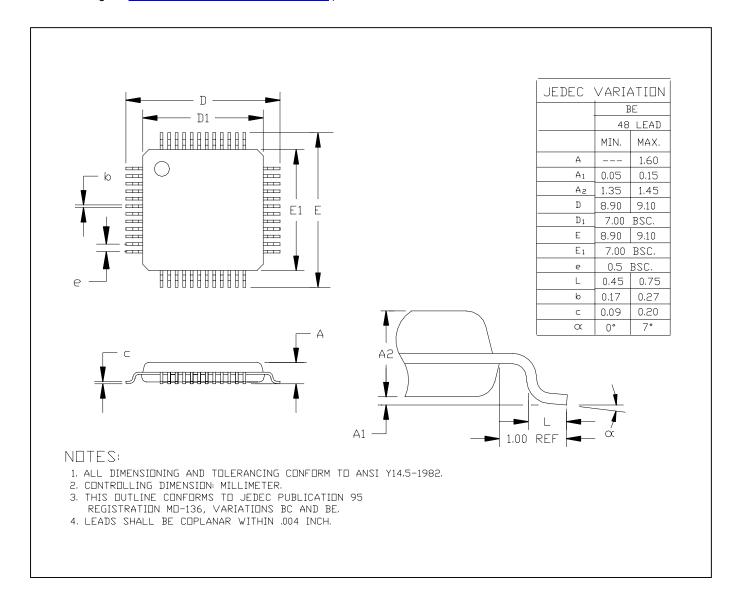

### PACKAGE INFORMATION

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/DallasPackInfo">www.maxim-ic.com/DallasPackInfo</a>.)