# **DIYAMP-SC70-EVM**

This user's guide contains support documentation for the DIYAMP-SC70 evaluation module (EVM). Included is a description of how to set up and configure the EVM, printed circuit board (PCB) layout, schematic, and bill of materials (BOM) of the DIYAMP-SC70-EVM.

### Contents

| 1      | Introduction                                                 | . 3 |

|--------|--------------------------------------------------------------|-----|

| 2      | Hardware Setup                                               |     |

| 3<br>4 | Schematic and PCB Layout                                     |     |

| 5      | Bill of Materials and Reference                              |     |

|        | List of Figures                                              |     |

| 1      | Location of Circuit Configurations                           | . 4 |

| 2      | Detach Desired Circuit Configuration                         | . 5 |

| 3      | Detach Configuration With Attached IC and Passive Components | . 5 |

| 4      | Terminal Strip (TS-132-G-AA) Broken Into 4-Pin Lengths       | . 5 |

| 5      | 4-Pin Length Terminal Strips Inserted in DIP Socket          | . 6 |

| 6      | Detached Board Configuration Position Over Terminal Pins     | . 6 |

| 7      | Fully-Assembled Circuit Configuration From DIYAMP-SC70-EVM   | . 6 |

| 8      | Silk Screen Circuit Schematic                                | . 7 |

| 9      | Single-Supply, Multiple Feedback Filter Schematic            | . 7 |

| 10     | Single-Supply, MFB Filter Top Layer                          | . 8 |

| 11     | Single-Supply, MFB Filter Bottom Layer                       | . 8 |

| 12     | Single-Supply, Sallen-Key Filter Schematic                   | . 9 |

| 13     | Single-Supply, Sallen-Key Filter Top Layer                   | . 9 |

| 14     | Single-Supply, Sallen-Key Filter Bottom Layer                |     |

| 1 | Single-Supply, Non-Inverting Amplifier Schematic               | 10 |

|---|----------------------------------------------------------------|----|

| 1 | Single-Supply, Non-Inverting Amplifier Top Layer               | 12 |

| 1 | Single-Supply, Non-Inverting Amplifier Bottom Layer            | 12 |

| 1 | Single-Supply, Inverting Amplifier Schematic                   | 12 |

| 1 | Single-Supply, Inverting Amplifier Top Layer                   | 13 |

| 2 | Single-Supply, Inverting Amplifier Bottom Layer                | 14 |

| 2 | Difference Amplifier Schematic                                 | 14 |

| 2 | Difference Amplifier Top Layer                                 | 15 |

| 2 | Difference Amplifier Bottom Layer                              | 15 |

| 2 | Dual-Supply, Multiple Feedback Filter Schematic                | 16 |

| 2 | Dual-Supply, Multiple Feedback Filter Top Layer                | 16 |

| 2 | Dual-Supply, Multiple Feedback Bottom Layer                    | 17 |

| 2 | Dual-Supply, Sallen-Key Filter Schematic                       | 17 |

| 2 | Dual-Supply, Sallen-Key Top Layer                              | 18 |

| 2 | Dual-Supply, Sallen-Key Bottom Layer                           | 18 |

| 3 | Inverting Comparator Schematic                                 | 19 |

| 3 | Inverting Comparator Top Layer                                 | 19 |

| 3 | Inverting Comparator Bottom Layer                              | 20 |

| 3 | Non-Inverting Comparator Schematic                             | 20 |

| 3 | Non-inverting Comparator Top Layer                             | 21 |

| 3 | Non-Inverting Comparator Bottom Layer                          | 21 |

| 3 | R <sub>iso</sub> with Dual-Feedback Schematic                  |    |

| 3 | Example of $f_{ZERO}$ , Where $A_{OL\_Loaded} = 20 \text{ dB}$ | 22 |

| 3 | R <sub>iso</sub> Dual-Feedback Top Layer                       | 23 |

| 3 | R <sub>iso</sub> Dual-Feedback Bottom Layer                    | 23 |

| 4 | Dual-Supply, Non-Inverting Amplifier Schematic                 | 23 |

| 4 | Dual-Supply, Non-Inverting Amplifier Top Layer                 | 24 |

| 4 | Dual-Supply, Non-Inverting Amplifier Bottom Layer              | 24 |

| 4 | Dual-Supply, Inverting Amplifier Schematic                     | 25 |

| 4 | Dual-Supply, Inverting Amplifier Top Layer                     | 26 |

| 4 | Dual-Supply, Inverting Amplifier Bottom Layer                  | 26 |

| 4 | SMA Vertical Connectors                                        | 27 |

| 4 | SMA Horizontal Connectors                                      | 27 |

| 4 | Wire Connections                                               | 27 |

| 4 | Through-Hole Test Points                                       |    |

| Ę | Input and Output Pins in Terminal Area                         | 28 |

| Ę | Wire Alternative for Terminal Area                             | 29 |

|   | List of Tables                                                 |    |

| 1 | DIYAMP-SC70-EVM Kit Contents                                   | 3  |

| 2 | Location of Circuit Legend                                     |    |

| 3 | MFB Filter Type Component Selection                            |    |

| 2 | Sallen-Key Filter Component Type Selection                     |    |

| 5 | MFB Filter Type Component Selection                            |    |

| 6 | Sallen-Key Filter Component Type Selection                     |    |

| - | Bill of Materials                                              |    |

|   |                                                                |    |

## **Trademarks**

FilterPro, TINA-TI are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

www.ti.com Introduction

#### 1 Introduction

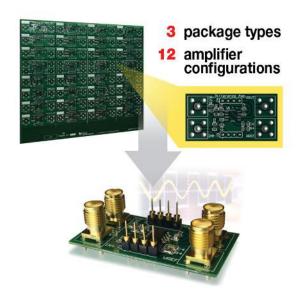

The DIYAMP-SC70-EVM is an EVM developed to give users the ability to easily evaluate their design concepts. This break-apart EVM has several popular op-amp configurations including: amplifiers, filters, and stability compensation configurations for both single and dual supply. The EVM is designed for 0805 and 0603 package size surface mount components enabling easy prototyping. This board gives the user the ability to build anything from a simple amplifier to complex signal chains by combining different configurations.

For more information about power supply voltages and input/output limitations, consult TI Precision Labs – Op Amps videos.

#### 1.1 DIYAMP-SC70-EVM Kit Contents

Table 1 details the contents included in the DIYAMP-SC70-EVM kit.

Table 1. DIYAMP-SC70-EVM Kit Contents

| Item            | Item Description                                     |   |

|-----------------|------------------------------------------------------|---|

| DIYAMP-SC70-EVM | PCB                                                  | 1 |

| Header Strip    | 100 mil (2.54 mm) spacing, 32 position, through hole | 2 |

### 1.2 EVM Features

This EVM supports the following features:

- · Multiple circuit configurations

- Dual- and single-supply configurations

- · Breadboard compatible

- · Schematic provided in silk screen on the PCB

- Multiple connector options for input and output connections: SMA, test point, and wires.

### 1.3 List of Circuits on the EVM

- Single-supply multiple feedback (MFB) filter

- Single-supply Sallen-Key filter

- Single-supply non-inverting amplifier

- Single-supply inverting amplifier

- Difference amplifier

- Dual-supply multiple feedback (MFB) filter

- · Dual-supply Sallen-Key filter

- R<sub>iso</sub> with dual feedback

- · Non-Inverting Comparator

- Inverting Comparator

- Dual-supply non-inverting amplifier

- Dual-supply inverting amplifier

Hardware Setup www.ti.com

## 2 Hardware Setup

Assembly of the DIYAMP-SC70-EVM involves identifying and breaking out the desired circuit configuration from the EVM, soldering components, header pins, and inputs and outputs connections. This section presents the details of these procedures.

### 2.1 EVM Circuit Locations

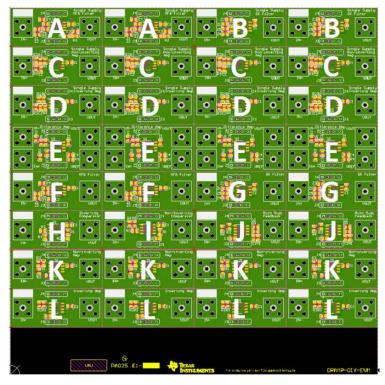

Figure 1 and Table 2 map the location of each circuit configuration on the EVM. Figure 1 labels each circuit configuration with a letter ranging from A to L. Table 2 matches the circuit configuration to a letter in Figure 1 and also provides the name of each individual circuit written in silk screen on the EVM.

Figure 1. Location of Circuit Configurations

**Table 2. Location of Circuit Legend**

| Circuit Name                           | Silk Screen Label               | Letter in Figure 1 |

|----------------------------------------|---------------------------------|--------------------|

| Single-supply multiple feedback filter | Single-Supply MFB Filter        | Α                  |

| Single-supply Sallen Key filter        | Single-Supply SK Filter         | В                  |

| Single-supply non-inverting amplifier  | Single-Supply Non-Inverting Amp | С                  |

| Single-supply inverting amplifier      | Single-Supply Inverting Amp     | D                  |

| Difference amplifier                   | Difference Amp                  | E                  |

| Dual-supply multiple feedback filter   | MFB Filter                      | F                  |

| Dual-supply Sallen Key filter          | SK Filter                       | G                  |

| Inverting comparator                   | Inverting Comparator            | Н                  |

| Non-inverting comparator               | Non-Inverting Comparator        | I                  |

| R <sub>iso</sub> with dual feedback    | Riso Dual Feedback              | J                  |

| Dual-supply non-inverting amplifier    | Non-Inverting Amp               | K                  |

| Dual-supply inverting amplifier        | Inverting Amp                   | L                  |

www.ti.com Hardware Setup

## 2.2 EVM Assembly Instructions

This section has step-by-step instructions on how to assemble a circuit configuration from the EVM.

- Step 1. Choose the desired circuit configuration. See Section 2.1 for the location of each circuit configuration.

- Step 2. Gently flex the PCB panel at the score lines to separate the desired circuit configuration from the EVM.

Figure 2. Detach Desired Circuit Configuration

Step 3. Solder device and surface mount passive components to the separated PCB.

Figure 3. Detach Configuration With Attached IC and Passive Components

Step 4. Use long-nose pliers to break header strips, provided in the EVM kit, into 4-position lengths.

Figure 4. Terminal Strip (TS-132-G-AA) Broken Into 4-Pin Lengths

Hardware Setup www.ti.com

Step 5. Insert header strips into a spare DIP socket as shown in Figure 5.

Figure 5. 4-Pin Length Terminal Strips Inserted in DIP Socket

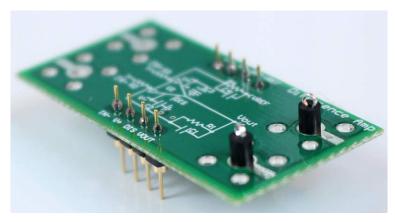

Step 6. Position separated PCB over pins and solder the connections. Carefully remove from the DIP socket.

Figure 6. Detached Board Configuration Position Over Terminal Pins

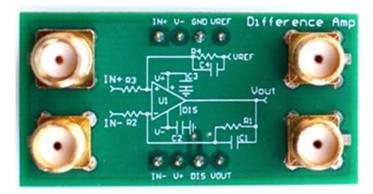

Step 7. Attach SMA connectors, test points, or wires to the input and output of the separated PCB.

Figure 7. Fully-Assembled Circuit Configuration From DIYAMP-SC70-EVM

### 3 Schematic and PCB Layout

This section provides the schematic and PCB layout of each circuit configuration provided on the EVM.

### 3.1 Schematic PCB Drawing

Each circuit board has a silk screen of its schematic for easy reference.

Figure 8. Silk Screen Circuit Schematic

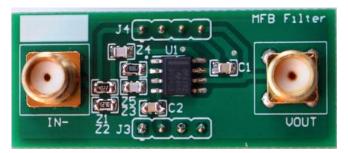

## 3.2 Single-Supply, Multiple Feedback Filter

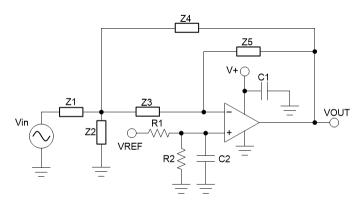

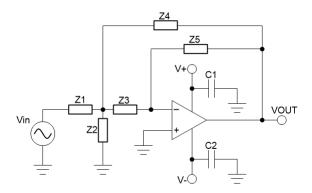

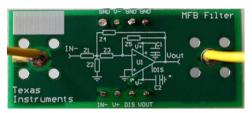

Figure 9 shows the schematic for the single-supply, multiple feedback (MFB) filter circuit configuration.

Figure 9. Single-Supply, Multiple Feedback Filter Schematic

The MFB topology (sometimes called infinite gain or Rauch) is often preferred, due to low sensitivity to component variations. The MFB topology creates an inverting second-order stage. This inversion may, or may not, be a concern in the filter application.

The single-supply, MFB filter circuit can be configured as a low-pass filter, high-pass filter, or band-pass filter based on the component selection of Z1 through Z5. Table 3 displays the type of passive component that should be chosen for Z1 through Z5 for each filter configuration.

**Table 3. MFB Filter Type Component Selection**

| Pass-Band<br>Filter Type | Type of Component (Z1) | Type of Component (Z2) | Type of Component (Z3) | Type of Component (Z4) | Type of Component (Z5) |

|--------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Low Pass                 | R1                     | C2                     | R3                     | R4                     | C5                     |

| High Pass                | C1                     | R2                     | C3                     | C4                     | R5                     |

| Band Pass                | R1                     | R2                     | C3                     | C4                     | R5                     |

For additional guidance in designing a filter, download FilterPro™ active filter design software.

Capacitor C2 provides the option to filter noise that may be introduced from the Vref input. calculates the cutoff frequency due to C2.

$$f_{c_{-}Vref} = \frac{1}{2\pi \times R_1 / / R_2 \times C_2}$$

(1)

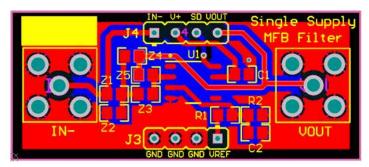

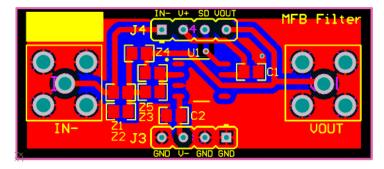

The PCB layout of the top layer of the single-supply, MFB filter configuration is displayed in Figure 10.

Figure 10. Single-Supply, MFB Filter Top Layer

The PCB layout of the bottom layer of the single-supply, MFB filter configuration is displayed in Figure 11.

Figure 11. Single-Supply, MFB Filter Bottom Layer

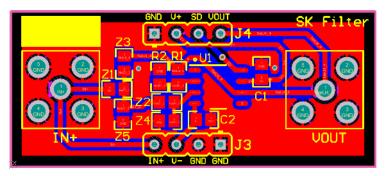

## 3.3 Single-Supply, Sallen-Key Filter

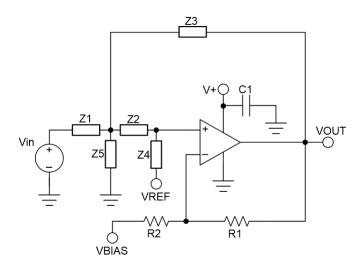

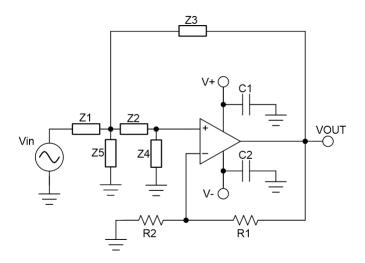

Figure 12 shows the schematic for the single-supply, Sallen-Key filter circuit configuration.

Figure 12. Single-Supply, Sallen-Key Filter Schematic

Sallen-Key is one of the most commonly applied active filter topologies. The Sallen-Key is a non-inverting, voltage-controlled, voltage-source (VCVS) able to attain larger Qs with a stable response than other filter topologies. Because Sallen-Key is non-inverting, it might be preferable over the MFB topology.

The single-supply, Sallen-Key filter can be configured as a low-pass filter, high-pass filter, or band-pass filter based on the component selection of Z1 through Z5. Table 4 displays the type of passive component that should be chosen for Z1 through Z5 for each filter configuration.

Table 4. Sallen-Key Filter Component Type Selection

| Pass-Band<br>Filter Type | Type of Component (Z1) | Type of Component (Z2) | Type of Component (Z3) | Type of Component (Z4) | Type of Component (Z5) |

|--------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Low Pass                 | R1                     | R2                     | C3                     | C4                     | Not populated          |

| High Pass                | C1                     | C2                     | R3                     | R4                     | Not populated          |

| Band Pass                | R1                     | C2                     | R3                     | R4                     | C5                     |

For additional guidance in designing a filter, download the FilterPro active filter design software.

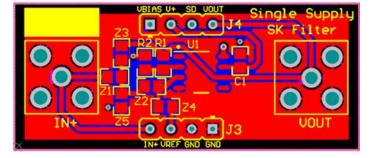

The PCB layout of the top layer of the single-supply, Sallen-Key filter circuit configuration is displayed in Figure 13.

Figure 13. Single-Supply, Sallen-Key Filter Top Layer

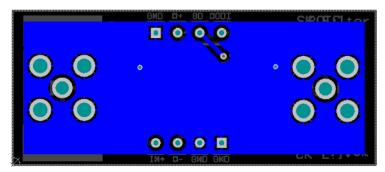

The PCB layout of the bottom layer of the single-supply, Sallen-Key filter configuration is displayed in Figure 14.

Figure 14. Single-Supply, Sallen-Key Filter Bottom Layer

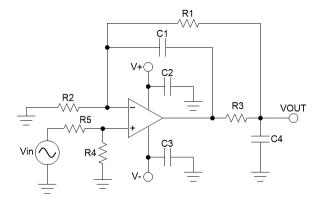

## 3.4 Single-Supply, Non-Inverting Amplifier

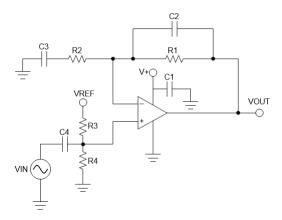

Figure 15 shows the schematic for the single-supply, non-inverting amplifier circuit configuration.

Figure 15. Single-Supply, Non-Inverting Amplifier Schematic

The non-inverting op-amp configuration takes an input signal that is applied directly to the high impedance, non-inverting input terminal and outputs a signal that is the same polarity as the input signal. The load resistance for this topology is the sum of R1 and R2. The values of the resistors in the feedback network will determine the amount of gain to amplify the input signal.

There are multiple ways to configure the single-supply, non-inverting amplifier. The following cases show three primary use case configurations for this circuit.

### Case 1: Standard non-inverting circuit

This circuit board can be configured into a standard non-inverting circuit by shorting C3 and C4 with a  $0-\Omega$  resistor and leaving R3 and R4 unpopulated.

Equation 2 displays the transfer function for the standard single-supply, non-inverting amplifier circuit configuration.

$$V_{out} = \left(1 + \frac{R_1}{R_2}\right) V_{in}$$

where

- C3 is shorted with a 0-Ω resistor

- C4 is shorted with a 0-Ω resistor

- R3 is unpopulated

Capacitor C2 provides the option to filter the output. The cutoff frequency of the filter can be calculated using Equation 3.

$$f_{\rm c} = \frac{1}{2\pi \times R_1 \times C_2} \tag{3}$$

### Case 2: AC coupled, single-supply, non-inverting circuit

This circuit board can be configured into an AC coupled non-inverting circuit by populating C3 and C4 with capacitors and populating R3 or R4 with resistors. R3 and R4 are used to set the DC output in the following two ways:

Option 1: VREF is directly applied to the input IN+

- R3 is populated with the desired biasing resistor

- R4 is unpopulated

Option 2: VREF is divided down and applied to the input IN+

R3 and R4 are populated with resistors, see Equation 4

$$V_{IN+} = \left(\frac{R_4}{R_3 + R_4}\right) V_{ref} \tag{4}$$

The AC response of the input signal is high-passed through C4, R3 + R4. The op-amp noise-gain is unity-gain until the gain begins to rise at the zero frequency defined in Equation 5.

$$F_{ZERO} = \frac{1}{2\pi \times C_3 \left(R_1 + R_2\right)} \tag{5}$$

The gain flattens off to the same gain defined in Equation 2 at the frequency defined in Equation 6.

$$\mathsf{F}_{\mathsf{pole}} = \frac{1}{2\pi \times \mathsf{C}_3 \times \mathsf{R}_2} \tag{6}$$

For more information on the AC coupled non-inverting circuit, see e2e.ti.com.

### Case 3: Non-inverting signal scaling circuit

This circuit board can be configured into a non-inverting signal scaling circuit by shorting C3 with a  $0-\Omega$  resistor and populating C4 with a resistor. This forms a 3-resistor divider with R3 and R4 on the input to scale or shift the input signal level. The op amp is typically configured as a unity-gain buffer.

Step 1. Choose a value for the resistor installed in place of C4

Step 2. Compute R3

$$R_3 = \frac{\left(1 + \frac{R_1}{R_2}\right)C_4 \times V_{ref}}{V_{offset}}$$

(7)

Step 3. Compute R2

$$R_2 = \frac{-V_{\text{offset}} \times C_4 \times R_3}{V_{\text{offset}} \times R_3 + V_{\text{offset}} \times C_4 - V_{\text{ref}} \times C_4}$$

(8)

For more information on the AC coupled non-inverting circuit, see e2e.ti.com.

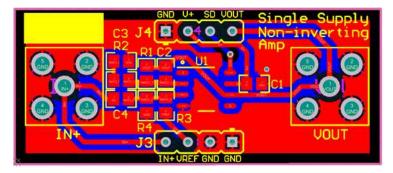

The PCB layout of the top layer of the single-supply, non-inverting circuit configuration is displayed in Figure 16.

Figure 16. Single-Supply, Non-Inverting Amplifier Top Layer

The PCB layout of the bottom layer of the single-supply, non-inverting circuit configuration is displayed in Figure 17.

Figure 17. Single-Supply, Non-Inverting Amplifier Bottom Layer

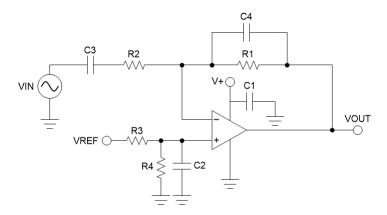

## 3.5 Single-Supply, Inverting Amplifier

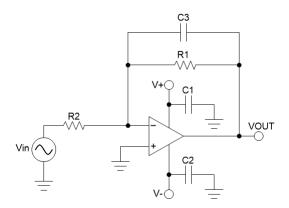

Figure 18 shows the schematic for the single-supply, inverting amplifier circuit configuration.

Figure 18. Single-Supply, Inverting Amplifier Schematic

The inverting op-amp configuration takes an input signal that is applied directly to the inverting input terminal and outputs a signal that is the opposite polarity as the input signal. The benefit of this topology is that it avoids common mode limitations. The load resistance for this topology is equal to R2. The values of the resistors in the feedback network will determine the amount of gain to amplify the input signal.

The single-supply, inverting amplifier circuit provides the option to AC couple the input, filter the output, and bias the output of the amplifier to a desired value.

Equation 9 displays the dc transfer function of the single-supply, inverting amplifier circuit configuration.

$$V_{out} = \left(-\frac{R_1}{R_2}\right)V_{in} + \left(1 + \frac{R_1}{R_2}\right)\left(\frac{R_4}{R_3 + R_4}\right)V_{ref}$$

where

• C3 is shorted with a 0-

$$\Omega$$

resistor (9)

Capacitor C3 provides the option to AC couple the input of the single-supply, inverting amplifier by creating a high-pass filter. Equation 10 displays the dc transfer function of the single-supply, inverting amplifier circuit configuration.

$$V_{out} = \left(\frac{R_4}{R_3 + R_4}\right) V_{ref}$$

where

The cutoff frequency of the high-pass filter can be calculated using Equation 11.

$$f_{\text{c\_highpass}} = \frac{1}{2\pi \times \text{C}_3 \times \text{R}_2}$$

(11)

Equation 12 displays the transfer function when the frequency of the input signal is above the cutoff frequency calculated in Equation 11.

$$V_{out} = \left(-\frac{R_1}{R_2}\right) V_{in} + \left(\frac{R_4}{R_3 + R_4}\right) V_{ref}$$

(12)

Capacitor C2 filters noise that may be introduced from the Vref input. Equation 13 calculates the cutoff frequency due to C2.

$$f_{\text{c\_Vref}} = \frac{1}{2\pi \times R_3 / / R_4 \times C_2}$$

(13)

Capacitor C4 provides the option to filter the output. The cutoff frequency of the filter can be calculated using Equation 14.

$$f_{c_{-}Vout} = \frac{1}{2\pi \times R_{1} \times C_{4}}$$

(14)

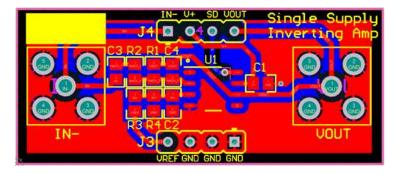

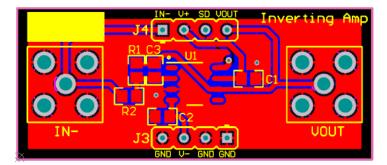

The PCB layout of the top layer of the single-supply, inverting amplifier circuit configuration is displayed in Figure 19.

Figure 19. Single-Supply, Inverting Amplifier Top Layer

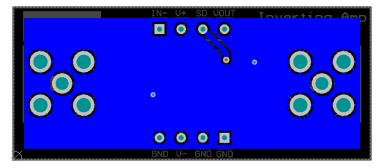

The PCB layout of the bottom layer of the single-supply, inverting amplifier circuit configuration is displayed in Figure 20.

Figure 20. Single-Supply, Inverting Amplifier Bottom Layer

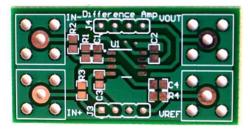

## 3.6 Difference Amplifier

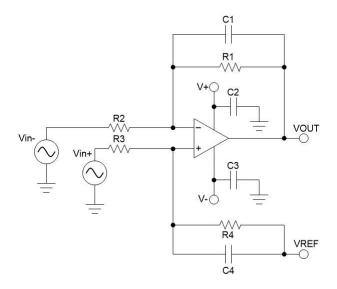

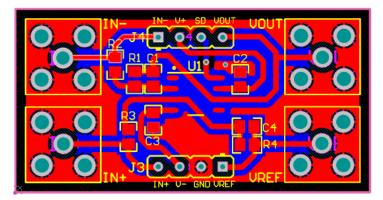

Figure 21 shows the schematic for the difference amplifier circuit configuration.

Figure 21. Difference Amplifier Schematic

The difference amplifier utilizes both inverting and non-inverting inputs and produces an output that is equal to the difference between the inputs. The gain of the difference amplifier is dependent on the ratio of the resistor values selected.

Equation 15 displays the transfer function of the difference amplifier circuit configuration.

$$V_{out} = \left(\frac{R_4}{R_3 + R_4}\right) \left(1 + \frac{R_1}{R_2}\right) V_{IN+} + \left(\frac{R_3}{R_3 + R_4}\right) \left(1 + \frac{R_1}{R_2}\right) V_{ref} + \frac{R_1}{R_2} V_{IN-}$$

(15)

If  $R_1 = R_4$  and  $R_2 = R_3$ , Equation 15 can be simplified to Equation 16.

$$V_{out} = \frac{R_1}{R_2} (V_{IN+} - V_{IN-}) + V_{ref}$$

(16)

Capacitors C1 and C4 provide the option to filter the output of the amplifier. The cutoff frequency of the filter can be calculated using Equation 17.

$$f_{\rm c} = \frac{1}{2\pi \times R_1 \times C_1}$$

where

•

$$R_1 = R_4$$

,  $R_2 = R_3$ , and  $C_1 = C_4$  (17)

The PCB layout of the top layer of the difference amplifier circuit configuration is displayed in Figure 22.

Figure 22. Difference Amplifier Top Layer

The PCB layout of the bottom layer of the difference amplifier circuit configuration is displayed in Figure 23.

Figure 23. Difference Amplifier Bottom Layer

## 3.7 Dual-Supply, Multiple Feedback Filter

Figure 24 shows the schematic for the dual-supply, multiple feedback filter circuit configuration.

Figure 24. Dual-Supply, Multiple Feedback Filter Schematic

The MFB topology (sometimes called infinite gain or Rauch) is often preferred due to low sensitivity to component variations. The MFB topology creates an inverting second-order stage. This inversion may, or may not, be a concern in the filter application.

The dual-supply, MFB filter circuit can be configured as a low-pass filter, high-pass filter, or band-pass filter based on the component selection of Z1 through Z5. Table 5 displays the type of passive component that should be chosen for Z1 through Z5 for each filter configuration.

**Table 5. MFB Filter Type Component Selection**

| Pass-Band<br>Filter Type | Type of Component (Z1) | Type of Component (Z2) | Type of Component (Z3) | Type of Component (Z4) | Type of Component (Z5) |

|--------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Low Pass                 | R1                     | C2                     | R3                     | R4                     | C5                     |

| High Pass                | C1                     | R2                     | C3                     | C4                     | R5                     |

| Band Pass                | R1                     | R2                     | C3                     | C4                     | R5                     |

For additional guidance in designing a filter, download the FilterPro active filter design software.

The PCB layout of the top layer of the dual-supply, multiple feedback filter circuit configuration is displayed in Figure 25.

Figure 25. Dual-Supply, Multiple Feedback Filter Top Layer

The PCB layout of the bottom layer of the dual-supply, multiple feedback filter circuit configuration is displayed in Figure 26.

Figure 26. Dual-Supply, Multiple Feedback Bottom Layer

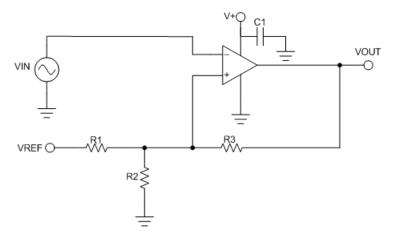

## 3.8 Dual-Supply, Sallen-Key Filter

Figure 27 shows the schematic for the dual-supply, Sallen-Key Filter circuit configuration.

Figure 27. Dual-Supply, Sallen-Key Filter Schematic

Sallen-Key is one of the most commonly applied active filter topologies. The Sallen-Key is a non-inverting, voltage-controlled, voltage-source (VCVS) able to attain larger Qs with a stable response than other filter topologies. Because Sallen-Key is non-inverting, it might be preferable over the MFB topology.

For this EVM, the Sallen-key filter can be configured for unity-gain by populating R1 with a short and leaving R2 open. Gain can be added by adding the appropriate resistors to R2 and R1 as explained in FilterPro.

The dual-supply, Sallen-Key filter can be configured as a low-pass filter, high-pass filter, or band-pass filter based on the component selection of Z1 through Z5. Table 6 displays the type of passive component that should be chosen for Z1 through Z5 for each filter configuration.

Table 6. Sallen-Key Filter Component Type Selection

| Pass-Band<br>Filter Type | Type of Component (Z1) | Type of Component (Z2) | Type of Component (Z3) | Type of Component (Z4) | Type of Component (Z5) |

|--------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Low Pass                 | R1                     | R2                     | C3                     | C4                     | Not populated          |

| High Pass                | C1                     | C2                     | R3                     | R4                     | Not populated          |

| Band Pass                | R1                     | C2                     | R3                     | R4                     | C5                     |

For additional guidance in designing a filter, download the FilterPro active filter design software.

The PCB layout of the top layer of the dual-supply, Sallen-Key filter circuit configuration is displayed in Figure 28.

Figure 28. Dual-Supply, Sallen-Key Top Layer

The PCB layout of the bottom layer of the dual-supply, Sallen-Key filter circuit configuration is displayed in Figure 29.

Figure 29. Dual-Supply, Sallen-Key Bottom Layer

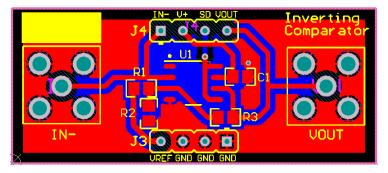

## 3.9 Inverting Comparator

Figure 30 shows the schematic for the inverting comparator circuit configuration.

Figure 30. Inverting Comparator Schematic

It is important to note that this circuit layout is meant for SC70 package op amps or push-pull output type comparators. This configuration uses a voltage divider R1 and R2 to set up the threshold voltage when no hysteresis is added. The comparator will compare the input signal (Vin) to the threshold voltage (Vth).

$$V_{th} = \left(\frac{R_2}{R_1 + R_2}\right) V_{ref}$$

where

The comparator input signal is applied to the inverting input, so the output will have an inverted polarity. When Vin > Vth, the output will drive to the negative supply (GND or logic low). When Vin < Vth, the output will drive to the positive supply (V+ or logic high).

R3 can be populated to implement hysteresis which uses two different threshold voltages to avoid the multiple transitions. The input signal must exceed the upper threshold (VH) to transition low or below the lower threshold (VL) to transition high. Equation 19 and Equation 20 will calculate the value of R2 and R3 for the two desired thresholds.

$$R_3 = \left(\frac{V_L}{V_H - V_L}\right) R_1 \tag{19}$$

$$R_2 = \left(\frac{V_L}{V_+ - V_H}\right) R_1 \tag{20}$$

The PCB layout of the top layer of the inverting comparator circuit configuration is displayed in Figure 31.

Figure 31. Inverting Comparator Top Layer

The PCB layout of the bottom layer of the inverting comparator circuit configuration is displayed in Figure 32.

Figure 32. Inverting Comparator Bottom Layer

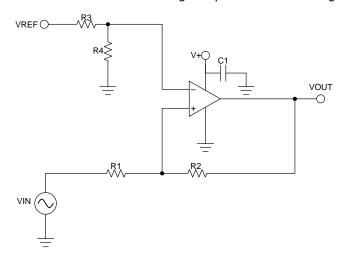

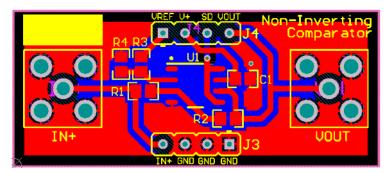

## 3.10 Non-Inverting Comparator

Figure 33 shows the schematic for the non-inverting comparator circuit configuration.

Figure 33. Non-Inverting Comparator Schematic

It is important to note that this circuit layout is meant for SC70 package op amp or push-pull output type comparators. This configuration uses a voltage divider R3 and R4 to set up the threshold voltage. The comparator will compare the input signal (Vin) to the threshold voltage (Vth).

$$V_{th} = \left(\frac{R_4}{R_3 + R_4}\right) V_{ref} \tag{21}$$

The comparator input signal is applied to the non-inverting input, so the output will have a non-inverted polarity. When Vin > Vth, the output will drive to the positive supply (V+ or logic high). When Vin < Vth, the output will drive to the negative supply (GND or logic low).

R2 can be populated to implement hysteresis which uses two different threshold voltages to avoid the multiple transitions. The input signal must exceed the upper threshold (VH) to transition high or below the lower threshold (VL) to transition low. Equation 22 and Equation 23 will calculate the value of R1 and R2 for the two desired thresholds.

$$R_1 = \frac{\left(V_h - V_{th}\right)}{V_{th}} R_2 \tag{22}$$

$$R_2 = \frac{(V_{th} + V_+)}{(V_1 - V_{th})} R_1$$

(23)

The PCB layout of the top layer of the non-inverting comparator circuit configuration is displayed in Figure 34.

Figure 34. Non-inverting Comparator Top Layer

The PCB layout of the top layer of the non-inverting comparator circuit configuration is displayed in Figure 35.

Figure 35. Non-Inverting Comparator Bottom Layer

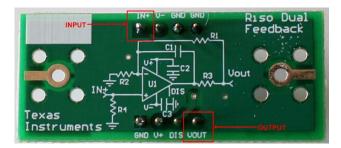

## 3.11 R<sub>iso</sub> With Dual Feedback

Figure 36 shows the schematic for the R<sub>iso</sub> with dual-feedback circuit configuration.

Figure 36. R<sub>iso</sub> with Dual-Feedback Schematic

The dc gain of the R<sub>iso</sub> with dual-feedback circuit configuration can be calculated using Equation 24.

Copyright © 2017, Texas Instruments Incorporated

$$V_{out} = \left(1 + \frac{R_1}{R_2}\right) \left(\frac{R_4}{R_4 + R_5}\right) V_{in}$$

(24)

In situations where stability is affected by capacitive loads, the R<sub>iso</sub> dual-feedback configuration has the ability to stabilize the circuit by compensating the contribution of the capacitive load to circuit instability. This capacitive load compensation technique uses an isolation resistor that compensates the circuit by adding a zero to cancel the pole from the output impedance and capacitive load. Refer to the *TI Precision Labs - Op Amps: Stability 5* video for detailed information on this technique.

The design steps for the R<sub>iso</sub> method follow:

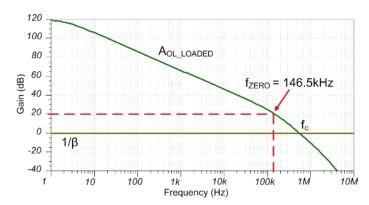

1. Use TINA-TI<sup>TM</sup> to find the zero frequency,  $f_{ZERO}$ , where  $A_{OL\ Loaded} = 20$  dB (example shown in Figure 37).

Figure 37. Example of  $f_{ZERO}$ , Where  $A_{OL\ Loaded}$  = 20 dB

2. Calculate  $R_{iso}$  to set the zero at  $f_{ZERO}$  – this will yield between 60° and 90° of phase margin

$$R_{iso} = \frac{1}{2\pi \times f_{ZERO} \times C_{Load}}$$

where

•

$$R_{iso} = R3$$

•  $C_{load} = C4$  (25)

While the  $R_{iso}$  circuit is both simple to implement and design, it has a big disadvantage in precision circuits. The voltage drop from  $R_{iso}$  is dependent on the output current or output load, and may be significant compared to the desired signal.

The second capacitive load compensation technique uses the  $R_{\rm iso}$  with dual-feedback stability compensation method. The  $R_{\rm iso}$  dual-feedback circuit solves the voltage drop disadvantage of the previously stated  $R_{\rm iso}$ . Refer to the *TI Precision Labs - Op Amps: Stability 6* video for detailed information on this technique.

Design steps for the R<sub>iso</sub> method follow:

- 1. R<sub>iso</sub> using Method 1: R<sub>iso</sub> techniques

- 2. Set R1:  $R_1 \ge (R_{iso} \times 100)$

$$3. \;\; \text{Set } C_1 \colon \frac{6R_{iso} \times C_{Load}}{R_1} \le C_1 \le \frac{10R_{iso} \times C_{Load}}{R_1}$$

Using this range ensures that the two feedback paths,  $R_2$  and  $C_3$ , will never create a resonance that would cause instability. Smaller values of C3 will result in faster settling time at the expense of overshoot for certain load ranges. While the  $R_{\rm iso}$  dual-feedback circuit solves the dc accuracy issue with the  $R_{\rm iso}$  circuit, it has some disadvantages as well. The disadvantage of this method is that the circuit is not as tolerant to changes in the output capacitance and can quickly become unstable. Therefore, the  $R_{\rm iso}$  dual-feedback circuit is best for situations where the output capacitance is known and will not vary significantly. This method generally results in a slower settling time than the  $R_{\rm iso}$  circuit as well.

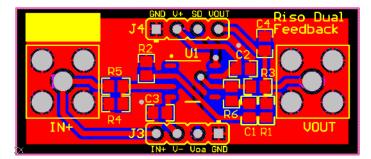

The PCB layout of the top layer of the  $R_{\rm iso}$  dual-feedback amplifier circuit configuration is displayed in Figure 38

Figure 38. R<sub>iso</sub> Dual-Feedback Top Layer

The PCB layout of the bottom layer of the  $R_{iso}$  dual-feedback amplifier circuit configuration is displayed in Figure 39.

Figure 39. R<sub>iso</sub> Dual-Feedback Bottom Layer

## 3.12 Dual-Supply, Non-Inverting Amplifier

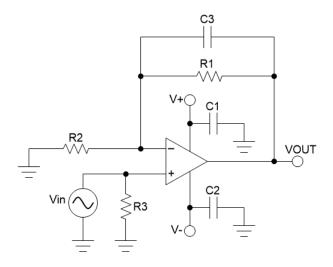

Figure 40 shows the schematic for the dual-supply, non-inverting amplifier circuit configuration.

Figure 40. Dual-Supply, Non-Inverting Amplifier Schematic

The non-inverting op-amp configuration takes an input signal that is applied directly to the high impedance non-inverting input terminal and outputs a signal that is the same polarity as the input signal. The load resistance for this topology is the sum of R1 and R2. The values of the resistors in the feedback network will determine the amount of gain to amplify the input signal.

Equation 26 displays the transfer function of the dual-supply, non-inverting amplifier circuit configuration shown in Figure 40.

$$V_{out} = \left(1 + \frac{R_1}{R_2}\right) V_{in} \tag{26}$$

Capacitor C3 provides the option to filter the output. The cutoff frequency of the filter can be calculated using Equation 27.

$$f_{\rm c} = \frac{1}{2\pi \times R_1 \times C_3} \tag{27}$$

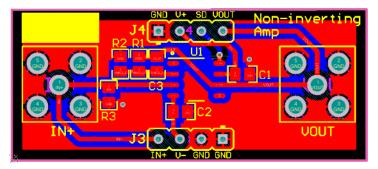

The PCB layout of the top layer of the dual-supply, non-inverting amplifier circuit configuration is displayed in Figure 41

Figure 41. Dual-Supply, Non-Inverting Amplifier Top Layer

The PCB layout of the bottom layer of the dual-supply, non-inverting amplifier circuit configuration is displayed in Figure 42.

Figure 42. Dual-Supply, Non-Inverting Amplifier Bottom Layer

## 3.13 Dual-Supply, Inverting Amplifier

Figure 43 shows the schematic for the dual-supply, inverting amplifier circuit configuration.

Figure 43. Dual-Supply, Inverting Amplifier Schematic

The inverting op-amp configuration takes an input signal that is applied directly to the inverting input terminal and outputs a signal that is the opposite polarity as the input signal. The benefit of this topology is that it avoids common mode limitations. The load resistance for this topology is equal to R2. The values of the resistors in the feedback network will determine the amount of gain to amplify the input signal.

Equation 28 displays the transfer function for the dual-supply, inverting amplifier circuit configuration shown in Figure 43.

$$V_{out} = -\frac{R_1}{R_2} V_{in}$$

(28)

Capacitor C3 provides the option to filter the output. The cutoff frequency of the filter can be calculated using Equation 29.

$$f_{\rm c} = \frac{1}{2\pi \times R_1 \times C_3} \tag{29}$$

The PCB layout of the top layer of the dual-supply, inverting amplifier circuit configuration is displayed in Figure 44.

Figure 44. Dual-Supply, Inverting Amplifier Top Layer

The PCB layout of the bottom layer of the dual-supply, inverting amplifier circuit configuration is displayed in Figure 45.

Figure 45. Dual-Supply, Inverting Amplifier Bottom Layer

www.ti.com Connections

### 4 Connections

This section provides a description for each connection available on the EVM.

## 4.1 Inputs and Outputs

The input/output connection slots were designed to fit the following connections: vertical SMA, horizontal SMA, wires, or through-hole test points. Examples of these four connectors are shown in this section.

The SMA recommended for this board is TE Connectivity part number 5-1814400-1.

Figure 46 shows SMA vertical connectors attached to both the input and output terminal.

Figure 46. SMA Vertical Connectors

Figure 47 shows SMA horizontal connectors attached to the input signal terminal.

Figure 47. SMA Horizontal Connectors

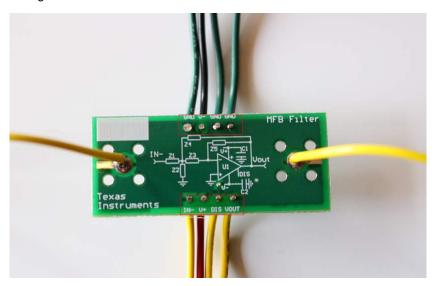

Figure 48 shows a wire attached to the input and output terminal.

Figure 48. Wire Connections

Connections www.ti.com

Figure 49 shows a through-hole test point connector attached to the output and Vref terminal.

Figure 49. Through-Hole Test Points

The input and output connections can also be accessed from the header strip. The input connections are labeled IN+ and IN- for the non-inverting and inverting inputs, respectively. The output connection is labeled VOUT. An example highlighting the input and output is shown in Figure 50.

Figure 50. Input and Output Pins in Terminal Area

www.ti.com Connections

### 4.2 Power

This EVM features both dual- and single-supply, op-amp configurations. Power can only be applied using the header pins located at the top and bottom of the PCB. The positive supply is labeled V+, the negative supply is labeled V-, and ground is labeled GND. As an alternative, wire can be used in place of the included terminals strips to power the board directly. Figure 51 shows an all-wire assembly for a multiple feedback filter configuration.

Figure 51. Wire Alternative for Terminal Area

### 4.3 Enable and Disable Feature

The DIYAMP-SC70-EVM provides a means to test the shutdown feature for op-amp devices equipped with a shutdown pin. The access to the shutdown pin, labeled SD, is located on the terminal area.

### 5 Bill of Materials and Reference

## 5.1 Bill of Materials

Table 7 lists the bill of materials.

### Table 7. Bill of Materials

| Designator | QTY | Value | Description                 | Package<br>Reference | Part Number | Manufacturer |

|------------|-----|-------|-----------------------------|----------------------|-------------|--------------|

| PCB        | 1   |       | Printed-Circuit Board       |                      | PA031       | Any          |

| TS1, TS2   | 2   |       | Header, 2.54mm,32x1,Gold,TH |                      | TS-132-G-AA | Samtec       |

### 5.2 Reference

- 1. Comparator with Hysteresis Reference Design (TIDU020)

- 2. TI Precision Labs Training https://training.ti.com/ti-precision-labs-op-amps

- 3. Analysis of the Sallen-Key Architecture (SLOA024)

- 4. AC Coupled, Single-Supply, Inverting and Non-inverting Amplifier Reference Design (TIDU871)

- 5. FilterPro Design Tool

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated