Datacom

#### Edition 2000-07

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 7/13/00. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

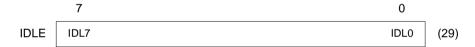

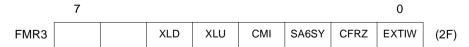

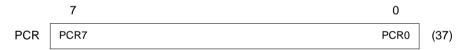

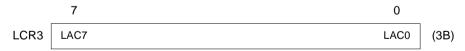

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

FALC<sup>®</sup>-LH E1/T1/J1 Framer and Line Interface Component for Long and Short Haul Applications PEB 2255 Version 1.3

Datacom

| D | ΕE | 2 | 2 | า | F | 5 |

|---|----|---|---|---|---|---|

| _ | _  | _ | _ | _ | J | J |

| Revision History: Previous Version: |                                                | 2000-07                    | DS 1 |

|-------------------------------------|------------------------------------------------|----------------------------|------|

|                                     |                                                | Preliminary Data Sheet DS1 |      |

| Page                                | e Subjects (major changes since last revision) |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

|                                     |                                                |                            |      |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

## **Preface**

The FALC®-LH framer and line interface component is designed to fulfill all required interfacing between an analog E1/T1/J1 line and the digital PCM system highway/H.100 bus.

The digital functions as well as the analog characteristics are configured via a flexible microprocessor interface.

## **Organization of this Document**

This Data Sheet is organized as follows:

## • Chapter 1, Introduction

Gives a general description of the product and its family, lists the key features, and presents some typical applications.

## • Chapter 2, Pin Descriptions

Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

## • Chapter 3 to Chapter 5, Functional Description E1/T1/J1

These chapters describe the functional blocks and principle operation modes, organized into separate sections for E1 and T1/J1 operation

## Chapter 6 and Chapter 7, Operational Description E1/T1/J1

Shows the operation modes and how they are to be initialized (separately for E1 and T1/J1).

## • Chapter 8, Signaling Controller Operating Modes

Describes signaling controller functions for both E1 and T1/J1 operation.

## Chapter 9 and Chapter 10, E1 Registers and T1/J1 Registers

Gives a detailed description of all implemented registers and how to use them in different applications/configurations.

#### Chapter 11. Electrical Characteristics

Specifies maximum ratings. DC and AC characteristics.

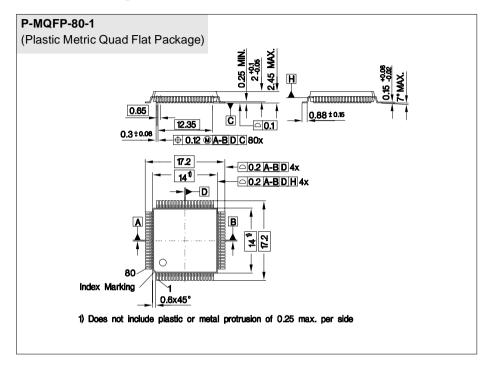

## Chapter 12, Package Outlines

Shows the mechanical values of the device package.

#### Chapter 13. Appendix

Gives an example for overvoltage protection and information about application notes and other support.

## · Chapter 14, Glossary

#### Index

#### **Related Documentation**

This document refers to the following international standards (in alphabetical/numerical order):

| ANSI/EIA-656                       | ITU-T G.705   |

|------------------------------------|---------------|

| ANSI T1.102                        | ITU-T G.706   |

| ANSI T1.403                        | ITU-T G.732   |

| AT&T PUB 43802                     | ITU-T G.735   |

| AT&T PUB 54016                     | ITU-T G.736   |

| AT&T PUB 62411                     | ITU-T G.737   |

| ESD Ass. Standard EOS/ESD-5.1-1993 | ITU-T G.738   |

| ETSI ETS 300 011                   | ITU-T G.739   |

| ETIS ETS 300 166                   | ITU-T G.823   |

| ETSI ETS 300 233                   | ITU-T G.824   |

| ETSI ETS 300 324                   | ITU-T G.962   |

| ETSI ETS 300 347                   | ITU-T G.963   |

| ETSI TBR12                         | ITU-T G.964   |

| ETSI TBR13                         | ITU-T I.431   |

| FCC Part68                         | ITU-Q.703     |

| GR-253-CORE                        | JT-G703       |

| GR-499-CORE                        | JT-G704       |

| GR-1089-CORE                       | JT-G706       |

| H.100                              | JT-I431       |

| H-MVIP                             | MIL-Std. 883D |

| IEEE 1149.1                        | TR-TSY-000009 |

| ITU-T G.703                        | UL 1459       |

| ITU-T G.704                        |               |

#### **Your Comments**

We welcome your comments on this document. We are continuously trying improving our documentation. Please send your remarks and suggestions by e-mail to sc.docu\_comments@infineon.com

Please provide in the subject of your e-mail:

device name (FALC®-LH), device number (PEB 2255), device version (Version 1.3),

and in the body of your e-mail:

document type (Data Sheet), issue date (2000-07) and document revision number (DS 1).

| l able of                                                                                 | Contents                                                                                                                                                                                                                                                                                                                          | Page                                   |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3                                                             | Introduction Features Logic Symbol Typical Applications                                                                                                                                                                                                                                                                           | 18                                     |

| <b>2</b><br>2.1<br>2.2                                                                    | Pin Descriptions         Pin Diagram         Pin Definitions and Functions                                                                                                                                                                                                                                                        | 24                                     |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.1.3<br>3.3.2                 | Functional Description E1/T1/J1  Functional Overview  Block Diagram  Functional Blocks  Microprocessor Interface  Mixed Byte/Word Access to the FIFOs  FIFO Structure  Interrupt Interface  Boundary Scan Interface                                                                                                               | 45<br>46<br>47<br>47<br>49<br>50       |

| 4<br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9 | Functional Description E1  Receive Path in E1 Mode Receive Equalization Network (E1) Receive Line Attenuation Indication (E1) Receive Clock and Data Recovery (E1) Receive Line Coding (E1) Loss of Signal Detection (E1) Receive Jitter Attenuator (E1) Jitter Tolerance (E1) Output Jitter (E1) Transmit Jitter Attenuator (E1) | 54<br>55<br>55<br>55<br>57<br>58<br>60 |

| 4.1.10<br>4.1.11<br>4.1.12<br>4.1.12.1<br>4.1.12.2<br>4.1.12.3<br>4.1.12.4                | Framer/Synchronizer  Receive Elastic Buffer (E1)  Receive Signaling Controller (E1)  HDLC or LAPD access  Sa bit Access (E1)  Channel Associated Signaling CAS (E1, serial mode)  Channel Associated Signaling CAS (E1, µP access mode)                                                                                           | 62<br>63<br>66<br>66<br>66             |

| 4.2<br>4.2.1<br>4.3<br>4.3.1<br>4.3.1.1<br>4.3.1.2<br>4.3.1.3                             | System Interface in E1 Mode Time Slot Assigner (E1) Transmit Path in E1 Mode Transmit Signaling Controller (E1) HDLC or LAPD access Sa bit Access (E1) Channel Associated Signaling CAS (E1, serial access mode)                                                                                                                  | 72<br>73<br>76<br>76                   |

| Table of | Contents                                              | age |

|----------|-------------------------------------------------------|-----|

| 4.3.1.4  | Channel Associated Signaling CAS (E1, µP access mode) | 77  |

| 4.3.2    | Transmit Elastic Buffer (E1)                          | 77  |

| 4.3.3    | Transmitter (E1)                                      | 78  |

| 4.3.4    | Transmit Line Interface (E1)                          |     |

| 4.3.5    | Programmable Pulse Shaper (E1)                        | 80  |

| 4.3.6    | Transmit Line Monitor (E1)                            |     |

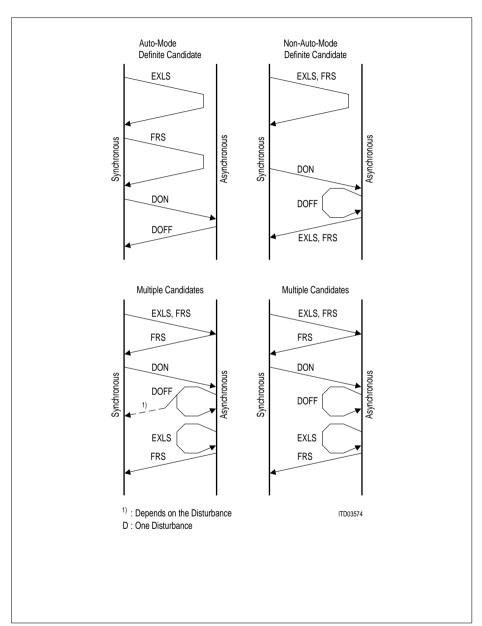

| 4.4      | Framer Operating Modes (E1)                           | 82  |

| 4.4.1    | General                                               | 82  |

| 4.4.2    | Doubleframe Format (E1)                               | 83  |

| 4.4.2.1  | Transmit Transparent Modes                            | 83  |

| 4.4.2.2  | Synchronization Procedure                             |     |

| 4.4.2.3  | A-Bit Access                                          | 85  |

| 4.4.2.4  | Sa - Bit Access                                       |     |

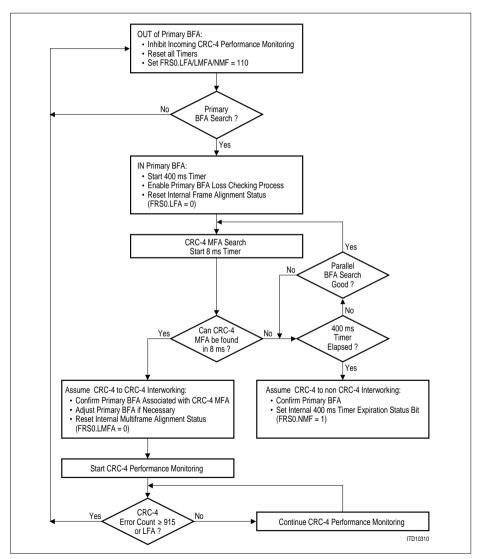

| 4.4.3    | CRC-Multiframe (E1)                                   |     |

| 4.4.3.1  | Synchronization Procedure                             |     |

| 4.4.3.2  | Automatic Force Resynchronization (E1)                |     |

| 4.4.3.3  | Floating Multiframe Alignment Window (E1)             |     |

| 4.4.3.4  | CRC4 Performance Monitoring (E1)                      |     |

| 4.4.3.5  | Modified CRC4 Multiframe Alignment Algorithm (E1)     |     |

| 4.4.3.6  | A-Bit Access (E1)                                     |     |

| 4.4.3.7  | Sa - Bit Access (E1)                                  |     |

| 4.4.3.8  | E-Bit Access (E1)                                     |     |

| 4.5      | Additional Functions (E1)                             |     |

| 4.5.1    | Error Performance Monitoring and Alarm Handling       |     |

| 4.5.2    | Auto Modes                                            |     |

| 4.5.3    | Error Counter                                         |     |

| 4.5.4    | Errored Second                                        |     |

| 4.5.5    | Second Timer                                          |     |

| 4.5.6    | In-Band Loop Generation and Detection                 |     |

| 4.5.7    | Time Slot 0 Transparent Mode                          |     |

| 4.6      | Test Functions (E1)                                   |     |

| 4.6.1    | Pseudo-Random Bit Sequence Generation and Monitor     |     |

| 4.6.2    | Remote Loop                                           |     |

| 4.6.3    | Payload Loop Back                                     |     |

| 4.6.4    | Local Loop                                            |     |

| 4.6.5    | Single Channel Loop Back                              | 100 |

| 4.6.6    |                                                       | 101 |

| 5        |                                                       | 102 |

| 5.1      |                                                       | 102 |

| 5.1.1    |                                                       | 103 |

| 5.1.2    | · · · · · · · · · · · · · · · · · · ·                 | 103 |

| 513      | Receive Clock and Data Recovery (T1/.I1)              | 103 |

| Table of | Contents                                             | Page  |

|----------|------------------------------------------------------|-------|

| 5.1.4    | Receive Line Coding (T1/J1)                          | . 103 |

| 5.1.5    | Loss of Signal Detection (T1/J1)                     | . 104 |

| 5.1.6    | Receive Jitter Attenuator (T1/J1)                    | . 105 |

| 5.1.7    | Jitter Tolerance (T1/J1)                             |       |

| 5.1.8    | Output Jitter (T1/J1)                                |       |

| 5.1.9    | Transmit Jitter Attenuator (T1/J1)                   | . 109 |

| 5.1.10   | Framer/Synchronizer (T1/J1)                          |       |

| 5.1.11   | Receive Elastic Buffer (T1/J1)                       | . 111 |

| 5.1.12   | Receive Signaling Controller (T1/J1)                 | . 115 |

| 5.1.12.1 | HDLC/SDLC or LAPD Access                             | . 115 |

| 5.1.12.2 | CAS Bit-robbing (T1/J1, serial access mode)          | . 115 |

| 5.1.12.3 | CAS Bit-robbing (T1/J1, µP access mode)              | . 116 |

| 5.1.12.4 | Bit Oriented Messages in ESF-DL Channel (T1/J1)      | . 116 |

| 5.1.12.5 | Data Link Access in F72 Format (T1/J1)               | . 116 |

| 5.2      | System Interface in T1/J1 Mode                       | . 116 |

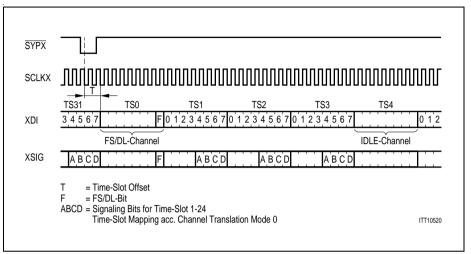

| 5.2.1    | Time Slot Assigner (T1/J1)                           | . 121 |

| 5.3      | Transmit Path in T1/J1 Mode                          | . 123 |

| 5.3.1    | Transmit Signaling Controller (T1/J1)                | . 129 |

| 5.3.1.1  | HDLC or LAPD access                                  | . 129 |

| 5.3.1.2  | CAS Bit-robbing (T1/J1)                              | . 129 |

| 5.3.1.3  | Data Link Access in ESF/F24 and F72 Format (T1/J1)   | . 130 |

| 5.3.2    | Transmit Elastic Buffer (T1/J1)                      | . 131 |

| 5.3.3    | Transmitter (T1/J1)                                  |       |

| 5.3.4    | Transmit Line Interface (T1/J1)                      | . 134 |

| 5.3.5    | Programmable Pulse Shaper and Line Build-Out (T1/J1) | . 135 |

| 5.3.6    | Transmit Line Monitor (T1/J1)                        |       |

| 5.4      | Framer Operating Modes (T1/J1)                       | . 137 |

| 5.4.1    | General                                              | . 137 |

| 5.4.2    | General Aspects of Synchronization                   | . 137 |

| 5.4.3    | 4-Frame Multiframe (F4 Format, T1/J1)                | . 140 |

| 5.4.3.1  | Synchronization Procedure                            | . 140 |

| 5.4.4    | 12-Frame Multiframe (D4 or SF Format, T1/J1)         |       |

| 5.4.4.1  | Synchronization Procedure                            |       |

| 5.4.5    | Extended Superframe (F24 or ESF Format, T1/J1)       | . 142 |

| 5.4.5.1  | Synchronization Procedures                           |       |

| 5.4.5.2  | Remote Alarm (yellow alarm) Generation/Detection     | . 144 |

| 5.4.5.3  | CRC6 Generation and Checking (T1/J1)                 |       |

| 5.4.6    | 72-Frame Multiframe (SLC96 Format, T1/J1)            | . 144 |

| 5.4.6.1  | Synchronization Procedure                            |       |

| 5.4.7    | Summary of Frame Conditions (T1/J1)                  | . 147 |

| 5.5      | Additional Functions (T1/J1)                         |       |

| 5.5.1    | Error Performance Monitoring and Alarm Handling      | . 148 |

| Table of                                                                                                                   | Contents                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 5.5.2<br>5.5.3<br>5.5.4<br>5.5.5<br>5.5.6<br>5.5.7<br>5.5.8<br>5.5.9<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.5<br>5.6.6 | Auto Modes Error Counter Errored Second Second Timer Clear Channel Capability In-Band Loop Generation and Detection Transparent Mode Pulse Density Detection Test Functions (T1/J1) Pseudo-Random Bit Sequence Generation and Monitor Remote Loop Payload Loop Back Local Loop Single Channel Loop Back (loopback of time slots) Alarm Simulation (T1/J1)                                                   | . 150<br>. 150<br>. 150<br>. 151<br>. 151<br>. 152<br>. 152<br>. 153<br>. 154<br>. 155<br>. 156<br>. 157 |

| 6<br>6.1<br>6.2<br>6.3                                                                                                     | Operational Description E1  Operational Overview E1  Device Reset E1  Device Initialization in E1 Mode                                                                                                                                                                                                                                                                                                      | . 158<br>. 158                                                                                           |

| <b>7</b> 7.1 7.2 7.3                                                                                                       | Operational Description T1/J1 Operational Overview T1/J1 Device Reset T1/J1 Device Initialization in T1/J1 Mode                                                                                                                                                                                                                                                                                             | . 163<br>. 163                                                                                           |

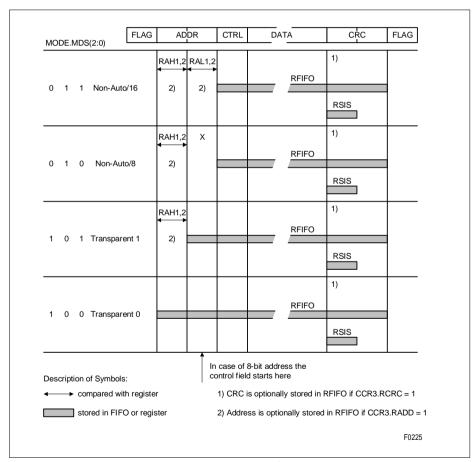

| 8<br>8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.2<br>8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5           | Signaling Controller Operating Modes  HDLC Mode  Non-Auto-Mode (MODE.MDS21 = 01)  Transparent Mode 1 (MODE.MDS20 = 101)  Transparent Mode 0 (MODE.MDS20 = 100)  Receive Data Flow  Transmit Data Flow  Extended Transparent Mode  Signaling Controller Functions  Shared Flags  Preamble Transmission  Transparent Transmission and Reception  Cyclic Transmission (fully transparent)  CRC ON/OFF Features | . 169<br>. 169<br>. 170<br>. 170<br>. 171<br>. 172<br>. 172<br>. 172<br>. 172                            |

| 8.3.6<br>8.3.7<br>8.3.8<br>8.3.9                                                                                           | Receive Address pushed to RFIFO  HDLC Data Transmission  HDLC Data Reception  Sa bit Access (E1)                                                                                                                                                                                                                                                                                                            | . 173<br>. 173<br>. 175                                                                                  |

| Table of                                                                                                                                                       | Contents                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 8.3.10<br>8.3.10.1                                                                                                                                             | Bit Oriented Message Mode (T1/J1)                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

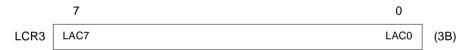

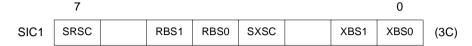

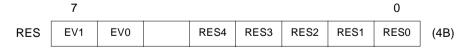

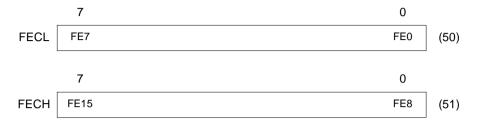

| 9<br>9.1<br>9.2<br>9.3<br>9.4                                                                                                                                  | E1 Registers  E1 Control Register Addresses  Detailed Description of E1 Control Registers  E1 Status Register Addresses  Detailed Description of E1 Status Registers                                                                                                                                                                                                                                                                   | . 180<br>. 183<br>. 228                                                                                  |

| 10<br>10.1<br>10.2<br>10.3<br>10.4                                                                                                                             | T1/J1 Registers  T1/J1 Control Register Addresses  Detailed Description of T1/J1 Control Registers  T1/J1 Status Register Addresses  Detailed Description of T1/J1 Status Registers                                                                                                                                                                                                                                                    | . 258<br>. 261<br>. 307                                                                                  |

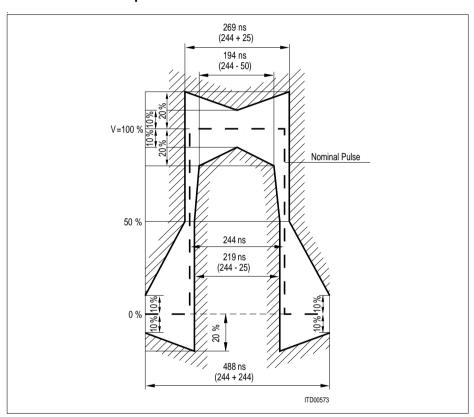

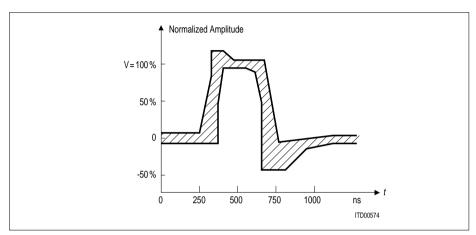

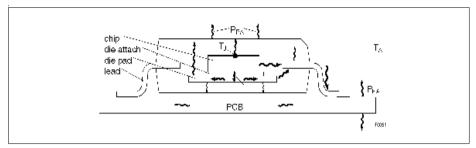

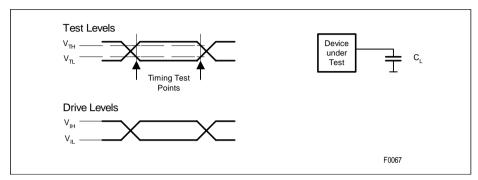

| 11<br>11.1<br>11.2<br>11.3<br>11.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.5<br>11.4.5.1<br>11.4.5.2<br>11.4.6<br>11.4.7<br>11.4.8.1<br>11.4.8.2<br>11.5<br>11.6 | Electrical Characteristics Absolute Maximum Ratings Operating Range DC Characteristics AC Characteristics Recommended Oscillator Circuits XTAL Clock Timing JTAG Boundary Scan Interface Reset Microprocessor Interface Intel Bus Interface Mode Motorola Bus Interface Mode Line Interface System Interface Pulse Templates - Transmitter Pulse Template E1 Pulse Template T1 Capacitances Package Characteristics Test Configuration | . 335<br>. 336<br>. 339<br>. 339<br>. 341<br>. 342<br>. 342<br>. 345<br>. 355<br>. 355<br>. 356<br>. 357 |

| 12                                                                                                                                                             | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                       | . 360                                                                                                    |

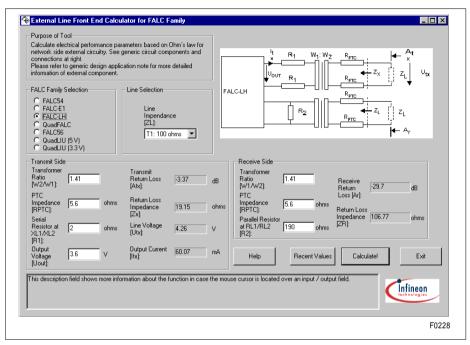

| 13.1<br>13.2<br>13.3<br>13.4                                                                                                                                   | Appendix Protection Circuitry Application Notes Software Support Differences to Version PEB 2255 V1.1                                                                                                                                                                                                                                                                                                                                  | . 361<br>. 362<br>. 364                                                                                  |

| 14                                                                                                                                                             | Glossary                                                                                                                                                                                                                                                                                                                                                                                                                               | . 365                                                                                                    |

| List of Figu | ures                                                          | Page  |

|--------------|---------------------------------------------------------------|-------|

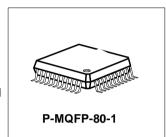

| Figure 1     | Logic Symbol                                                  | 21    |

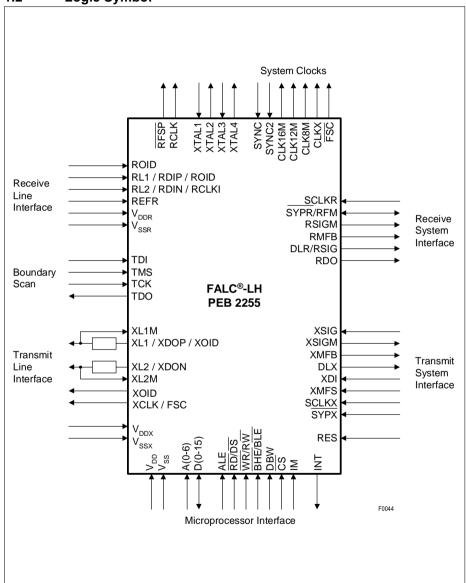

| Figure 2     | Multiple E1/T1/J1 Link over Frame Relay                       | 22    |

| Figure 3     | 8 Channel E1/T1/J1 Interface to the ATM Layer                 | 23    |

| Figure 4     | Multiple FALC Clocking Options                                |       |

| Figure 5     | Pin Configuration                                             | 24    |

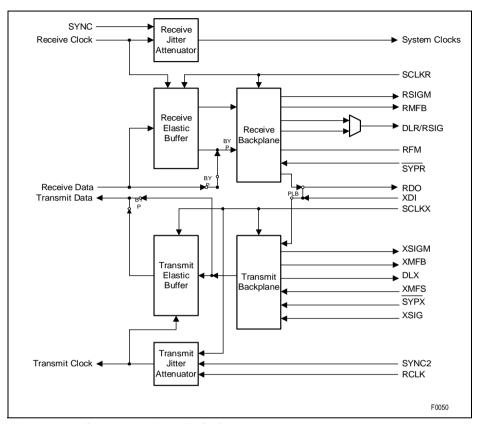

| Figure 6     | Block Diagram                                                 |       |

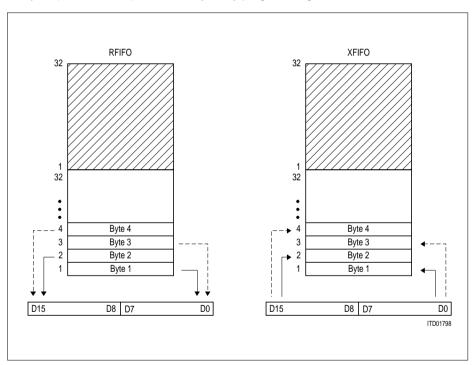

| Figure 7     | FIFO Word Access (Intel Mode)                                 |       |

| Figure 8     | FIFO Word Access (Motorola Mode)                              |       |

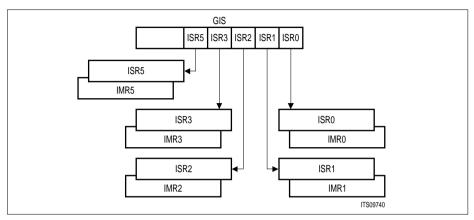

| Figure 9     | Interrupt Status Registers                                    | 51    |

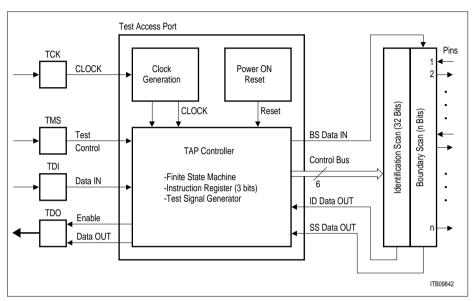

| Figure 10    | Block Diagram of Test Access Port and Boundary Scan           | 53    |

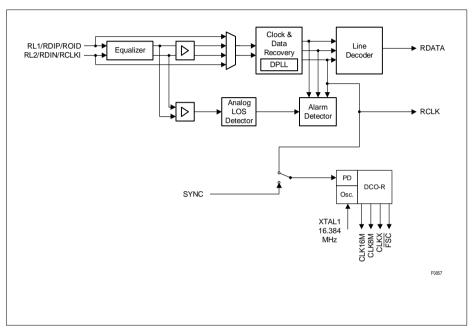

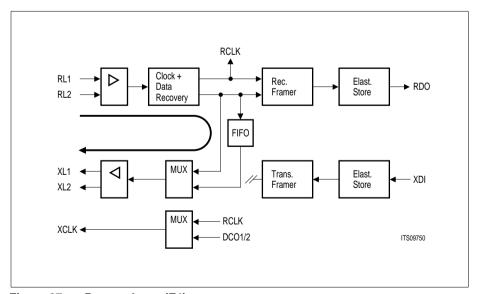

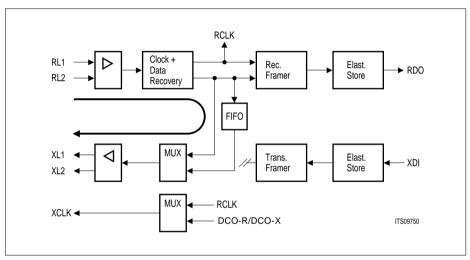

| Figure 11    | Receive Clock System (E1)                                     |       |

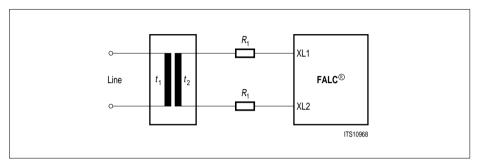

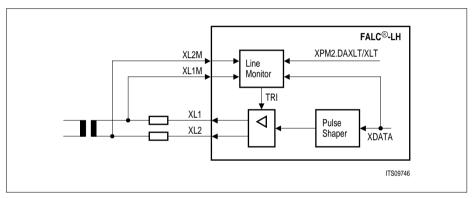

| Figure 12    | Receiver Configuration (E1)                                   |       |

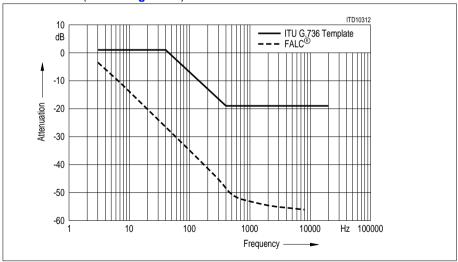

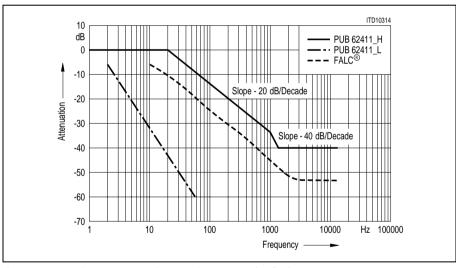

| Figure 13    | Jitter Attenuation Performance (E1)                           | 59    |

| Figure 14    | Jitter Tolerance (E1)                                         | 60    |

| Figure 15    | Transmit Clock System (E1)                                    | 62    |

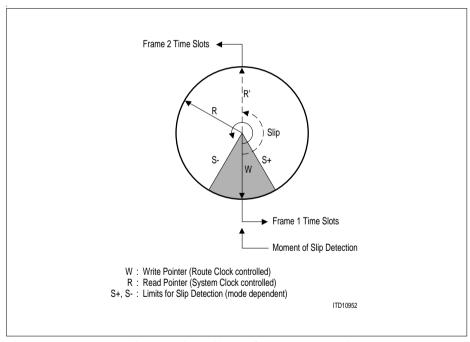

| Figure 16    | The Receive Elastic Buffer as Circularly Organized Memory     | 65    |

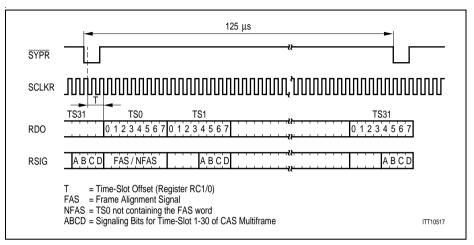

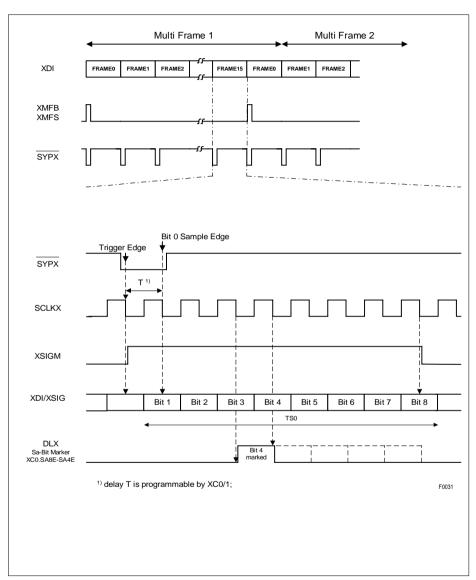

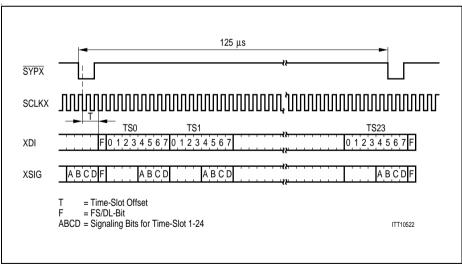

| Figure 17    | 2.048 MHz Receive Signaling Highway (E1)                      |       |

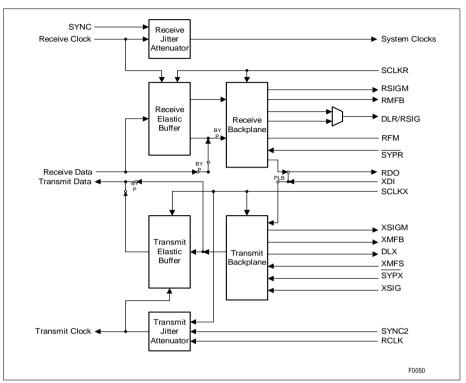

| Figure 18    | System Interface (E1)                                         | 70    |

| Figure 19    | Receive System Interface Clocking (E1)                        | 71    |

| Figure 20    | Transmit System Interface Clocking: 2.048 MHz (E1)            | 74    |

| Figure 21    | Transmit System Interface Clocking: 8.192 MHz/4.096 Mbit/s (E | 1) 75 |

| Figure 22    | 2.048 MHz Transmit Signaling Highway (E1)                     | 77    |

| Figure 23    | Transmitter Configuration (E1)                                | 79    |

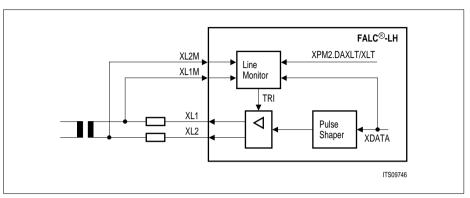

| Figure 24    | Transmit Line Monitor Configuration (E1)                      |       |

| Figure 25    | Data Flow in Transparent Mode                                 | 84    |

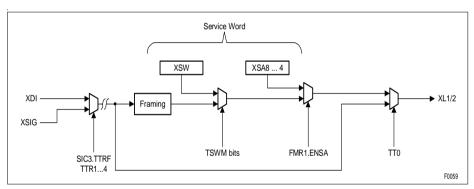

| Figure 26    | CRC4 Multiframe Alignment Recovery Algorithms                 | 92    |

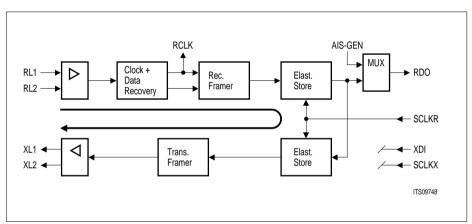

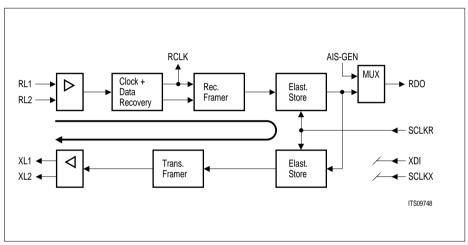

| Figure 27    | Remote Loop (E1)                                              | 97    |

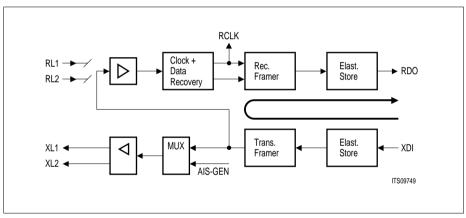

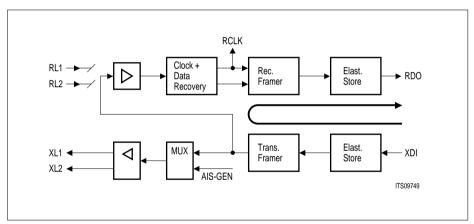

| Figure 28    | Payload Loop (E1)                                             |       |

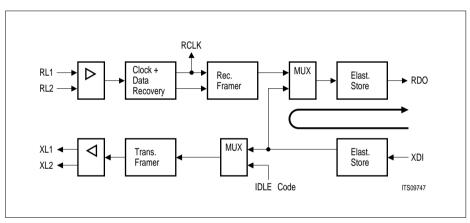

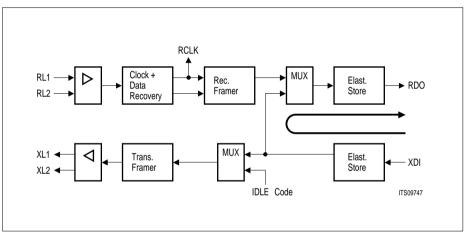

| Figure 29    | Local Loop (E1)                                               | 99    |

| Figure 30    | Single Channel Loopback (E1)                                  |       |

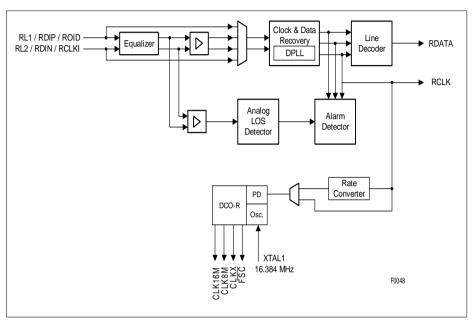

| Figure 31    | Receive Clock System (T1/J1)                                  | 102   |

| Figure 32    | Receiver Configuration (T1/J1)                                | 104   |

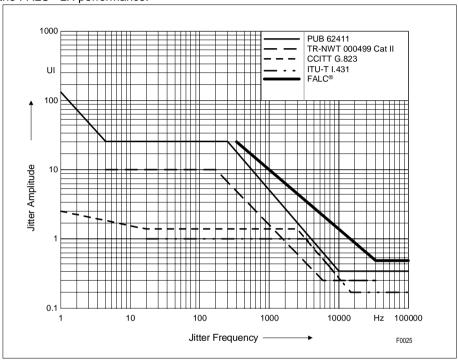

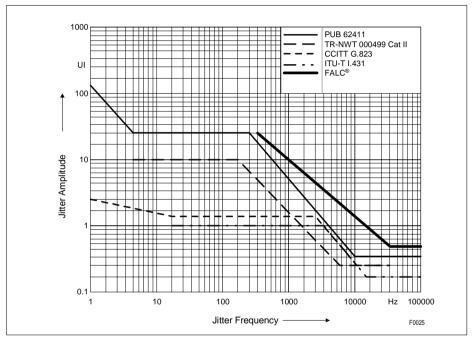

| Figure 33    | Jitter Attenuation Performance (T1/J1)                        | 107   |

| Figure 34    | Jitter Tolerance (T1/J1)                                      | 108   |

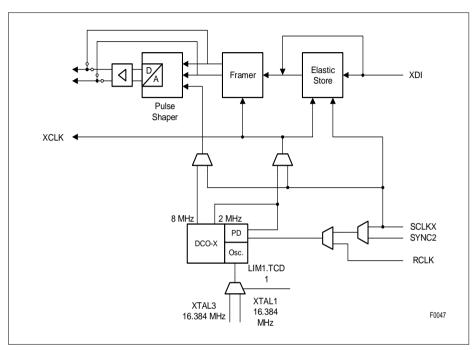

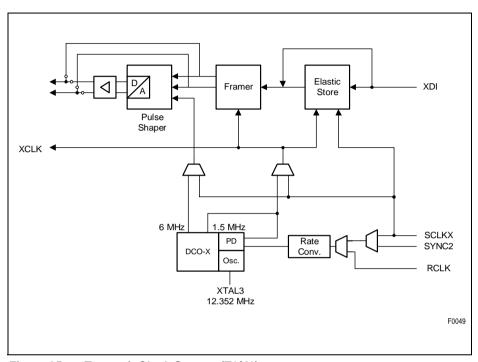

| Figure 35    | Transmit Clock System (T1/J1)                                 | 110   |

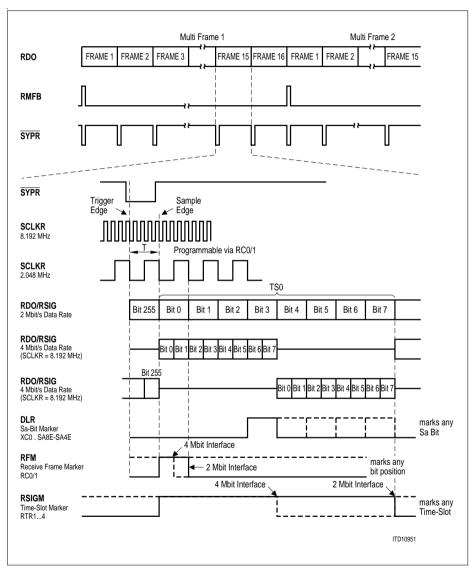

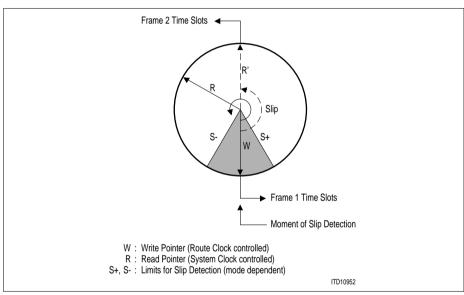

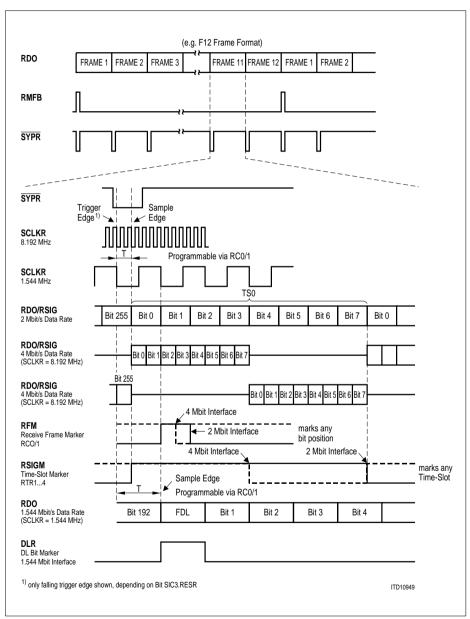

| Figure 36    | The Receive Elastic Buffer as Circularly Organized Memory     | 113   |

| Figure 37    | System Interface (T1/J1)                                      | 118   |

| Figure 38    | Receive System Interface Clocking (T1/J1)                     | 119   |

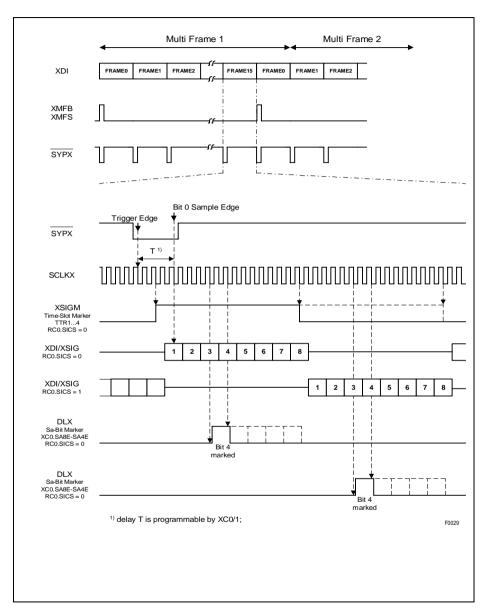

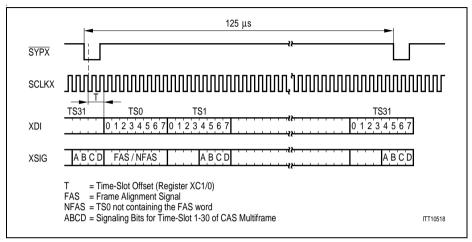

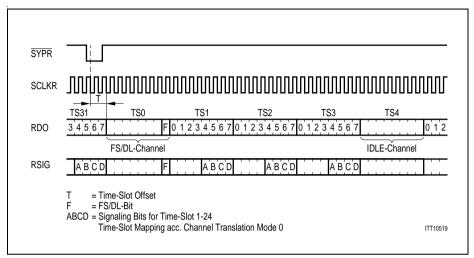

| Figure 39    | 2.048 Mbit/s Receive Signaling Highway (T1/J1)                | 120   |

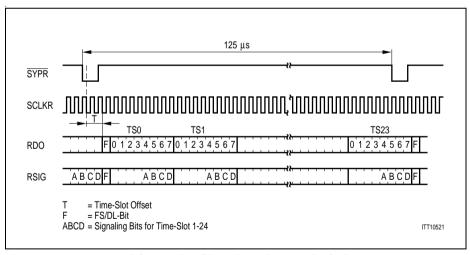

| Figure 40    | 1.544 Mbit/s Receive Signaling Highway (T1/J1)                |       |

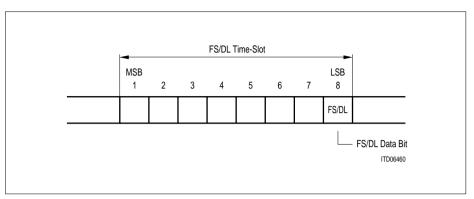

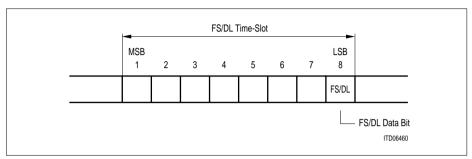

| Figure 41    | Receive FS/DL Bits in Time Slot 0 on RDO (T1/J1)              | 122   |

| Figure 42    | Transmit System Interface Clocking: 1.544 MHz (T1/J1)         |       |

| List of Figur | res                                                        | Page |

|---------------|------------------------------------------------------------|------|

| Figure 43     | Transmit System Interface Clocking: 8 MHz/4 Mbit/s (T1/J1) | 125  |

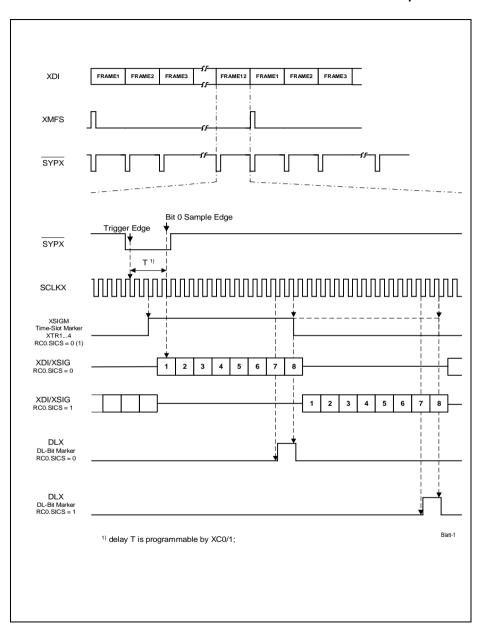

| Figure 44     | 2.048 Mbit/s Transmit Signaling Clocking (T1/J1)           | 126  |

| Figure 45     | 1.544 Mbit/s Transmit Signaling Highway (T1/J1)            |      |

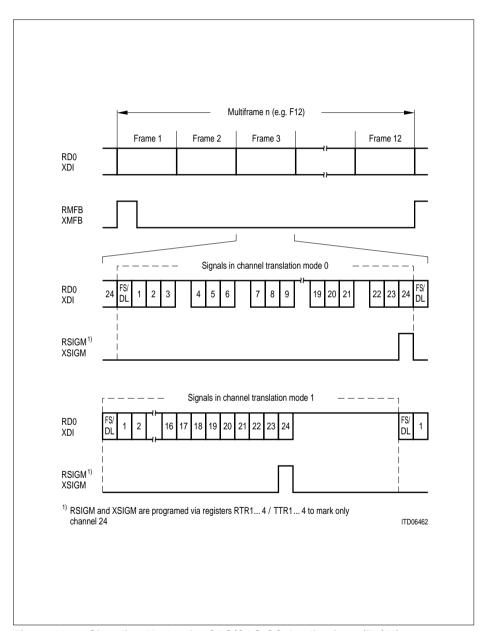

| Figure 46     | Signaling Marker for CAS/CAS-CC Applications (T1/J1)       |      |

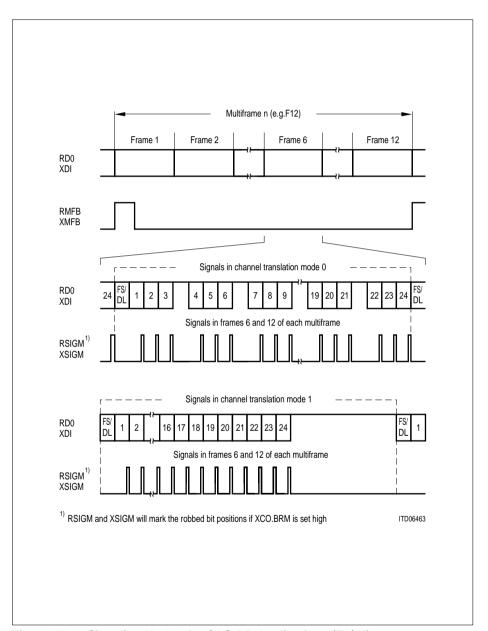

| Figure 47     | Signaling Marker for CAS-BR Applications (T1/J1)           |      |

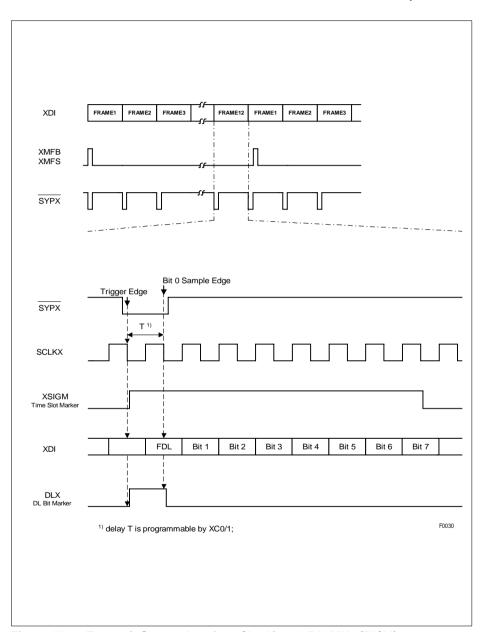

| Figure 48     | Transmit FS/DL Bits on XDI (T1/J1)                         | 129  |

| Figure 49     | Transmitter Configuration (T1/J1)                          |      |

| Figure 50     | Transmit Line Monitor Configuration (T1/J1)                |      |

| Figure 51     | Influences on Synchronization Status (T1/J1)               |      |

| Figure 52     | Remote Loop (T1/J1)                                        |      |

| Figure 53     | Payload Loop (T1/J1)                                       |      |

| Figure 54     | Local Loop (T1/J1)                                         |      |

| Figure 55     | Channel Loopback (T1/J1)                                   |      |

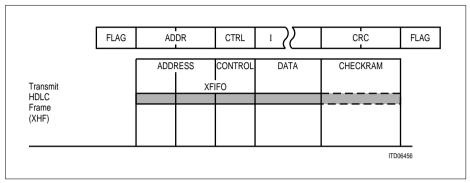

| Figure 56     | HDLC Receive Data Flow of FALC®-LH                         |      |

| Figure 57     | HDLC Transmit Data Flow of FALC®-LH                        |      |

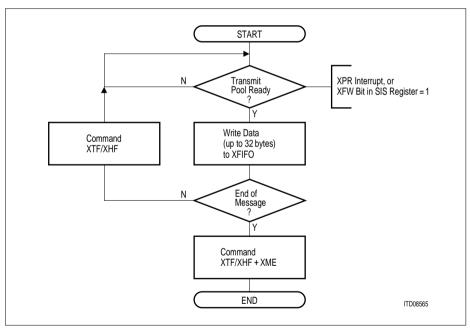

| Figure 58     | Interrupt Driven Data Transmission (flow diagram)          |      |

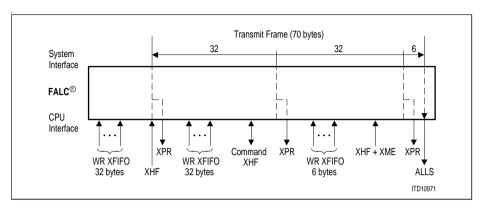

| Figure 59     | Interrupt Driven Transmission Example                      |      |

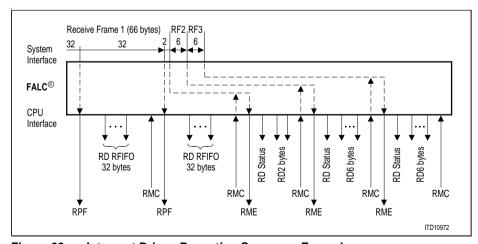

| Figure 60     | Interrupt Driven Reception Sequence Example                |      |

| Figure 61     | Crystal Oscillator Circuit (master/slave mode)             |      |

| Figure 62     | External Oscillator Circuit (master mode)                  |      |

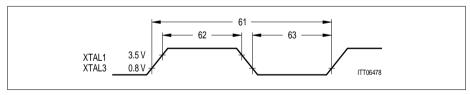

| Figure 63     | XTAL External Clock Timing                                 |      |

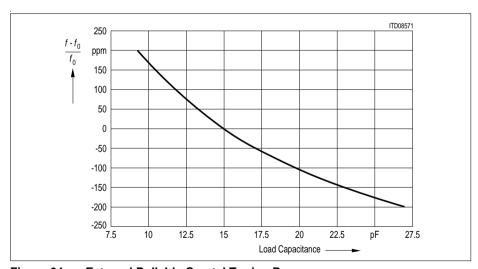

| Figure 64     | External Pullable Crystal Tuning Range                     |      |

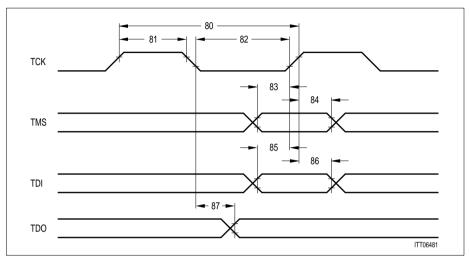

| Figure 65     | JTAG Boundary Scan Timing                                  |      |

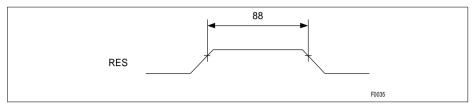

| Figure 66     | Reset Timing                                               |      |

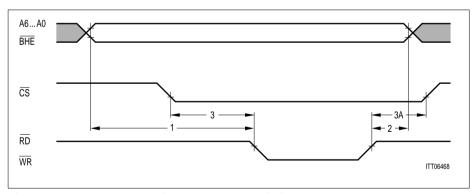

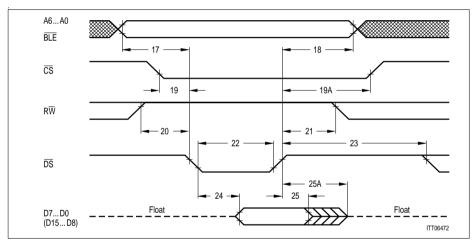

| Figure 67     | Intel Non-Multiplexed Address Timing                       |      |

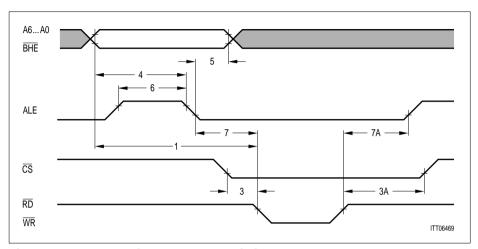

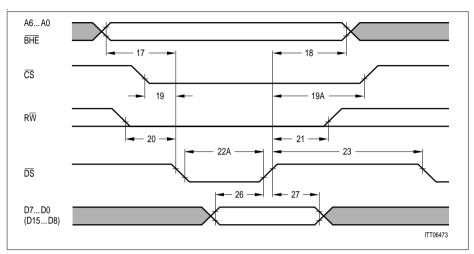

| Figure 68     | Intel Multiplexed Address Timing                           |      |

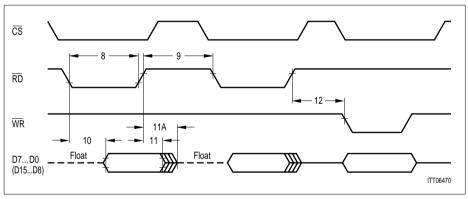

| Figure 69     | Intel Read Cycle Timing                                    |      |

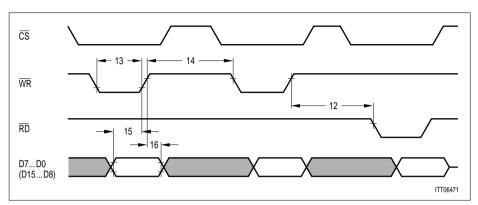

| Figure 70     | Intel Write Cycle Timing                                   |      |

| Figure 71     | Motorola Read Cycle Timing                                 |      |

| Figure 72     | Motorola Write Cycle Timing                                |      |

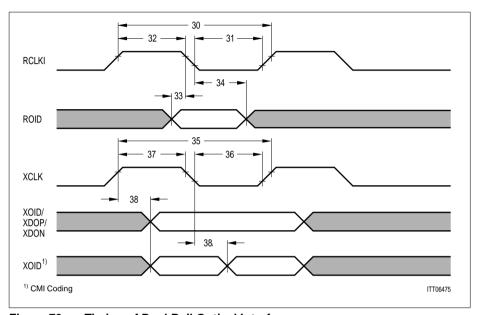

| Figure 73     | Timing of Dual Rail Optical Interface                      |      |

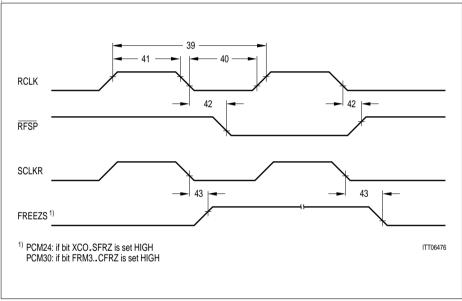

| Figure 74     | Receive Clock and RFSP/FREEZS Timing                       |      |

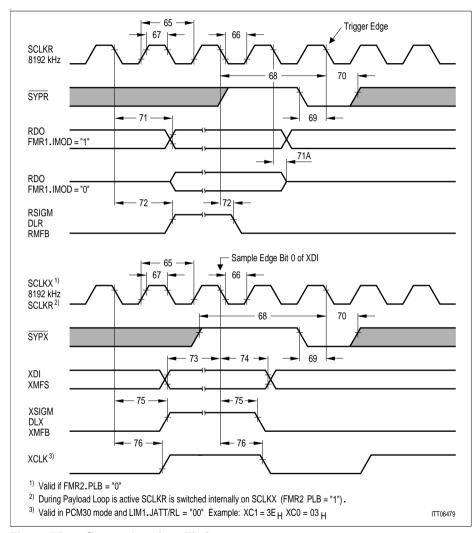

| Figure 75     | System Interface Timing                                    |      |

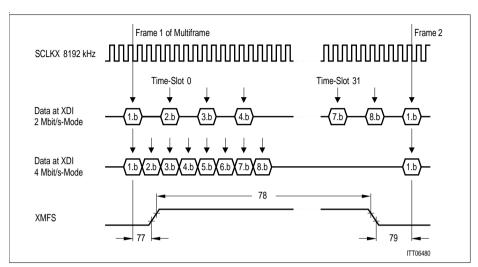

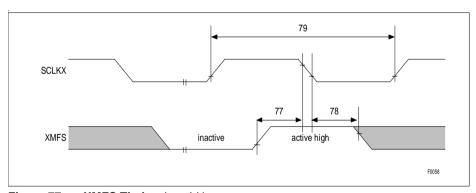

| Figure 76     | XMFS Timing                                                |      |

| Figure 77     | XMFS Timing (cont'd.)                                      |      |

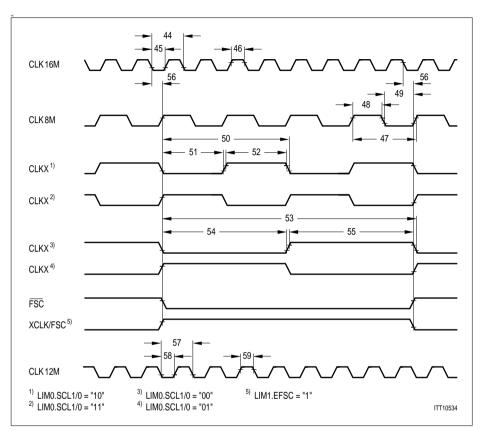

| Figure 78     | System Clock Timing                                        |      |

| Figure 79     | Pulse Shape at Transmitter Output for E1 Applications      |      |

| Figure 80     | T1 Pulse Shape                                             |      |

| Figure 81     | Thermal Behavior of Package                                |      |

| Figure 82     | Input/Output Waveforms for AC Testing                      |      |

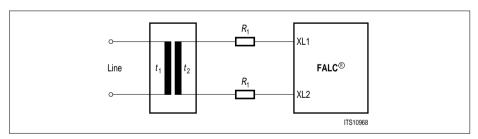

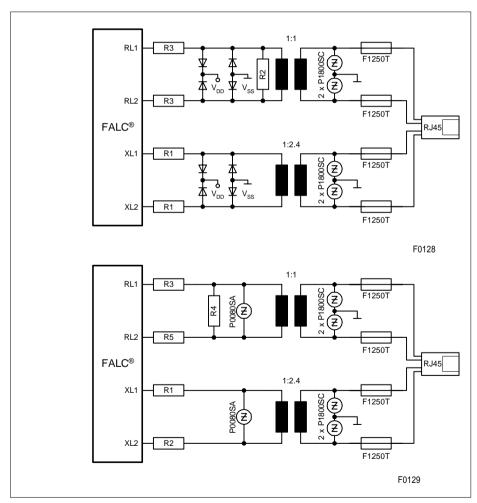

| Figure 83     | Protection Circuitry                                       |      |

| Figure 84     | External Line Frontend Calculator                          | 363  |

| List of Tab | les                                                       | Page |

|-------------|-----------------------------------------------------------|------|

| Table 1     | Pin Definitions - Microprocessor Interface                | 25   |

| Table 2     | Pin Definitions - Line Interface                          |      |

| Table 3     | Pin Definitions - Clock Generation                        | 32   |

| Table 4     | Pin Definitions - System Interface                        | 35   |

| Table 5     | Pin Definitions - Miscellaneous                           |      |

| Table 6     | Data Bus Access (16-Bit Intel Mode)                       |      |

| Table 7     | Data Bus Access (16-Bit Motorola Mode)                    | 48   |

| Table 8     | Selectable Bus and Microprocessor Interface Configuration |      |

| Table 9     | Recommended Receiver Configuration Values (E1)            |      |

| Table 10    | System Clocking (E1)                                      |      |

| Table 11    | Output Jitter (E1)                                        | 60   |

| Table 12    | Receive Buffer Operating Modes (E1)                       | 64   |

| Table 13    | System Clock and Data Rates (E1)                          |      |

| Table 14    | Time Slot Assigner (E1)                                   | 72   |

| Table 15    | Transmit Buffer Operating Modes (E1)                      | 78   |

| Table 16    | Example Transmitter Configuration Values (E1)             | 79   |

| Table 17    | Allocation of Bits 1 to 8 of Time Slot 0 (E1)             | 83   |

| Table 18    | Transmit Transparent Mode (Doubleframe E1)                | 84   |

| Table 19    | CRC-Multiframe Structure (E1)                             |      |

| Table 20    | Transmit Transparent Mode (CRC Multiframe E1)             |      |

| Table 21    | Summary of Alarm Detection and Release (E1)               |      |

| Table 22    | Recommended Receiver Configuration Values (T1/J1)         |      |

| Table 23    | System Clocking (T1/J1)                                   |      |

| Table 24    | Output Jitter (T1/J1)                                     |      |

| Table 25    | Receive Buffer Operating Modes (T1/J1)                    |      |

| Table 26    | Channel Translation Modes (T1/J1)                         |      |

| Table 27    | System Clock and Data Rates (T1/J1)                       |      |

| Table 28    | Time Slot Assigner (T1/J1)                                |      |

| Table 29    | Transmit Buffer Operating Modes (T1/J1)                   |      |

| Table 30    | Example Transmitter Configuration Values (T1/J1)          |      |

| Table 31    | Pulse Shaper Programming (T1/J1)                          |      |

| Table 32    | Resynchronization Timing (T1/J1)                          |      |

| Table 33    | 4-Frame Multiframe Structure (T1/J1)                      |      |

| Table 34    | 12-Frame Multiframe Structure (T1/J1)                     |      |

| Table 35    | Extended Superframe Structure (F24, ESF; T1/J1)           |      |

| Table 36    | 72-Frame Multiframe Structure (T1/J1)                     |      |

| Table 37    | Summary Frame Recover/Out of Frame Conditions (T1/J1)     |      |

| Table 38    | Summary of Alarm Detection and Release (T1/J1)            |      |

| Table 39    | Initial Values after Reset (E1)                           |      |

| Table 40    | Initialization Parameters (E1)                            |      |

| Table 41    | Line Interface Initialization (E1)                        |      |

| Table 42    | Framer Initialization (E1)                                | 161  |

| List of Tab | les                                                   | Page |

|-------------|-------------------------------------------------------|------|

| Table 43    | HDLC Controller Initialization (E1)                   | 162  |

| Table 44    | CAS-CC Initialization (E1)                            |      |

| Table 45    | Initial Values after reset and FMR1.PMOD = 1 (T1/J1)  | 164  |

| Table 46    | Initialization Parameters (T1/J1)                     | 165  |

| Table 47    | Line Interface Initialization (T1/J1)                 | 166  |

| Table 48    | Framer Initialization (T1/J1)                         | 166  |

| Table 49    | Initialization of the HDLC controller (T1/J1)         | 167  |

| Table 50    | Initialization of the CAS-BR Controller (T1/J1)       | 168  |

| Table 51    | E1 Control Register Address Arrangement               | 180  |

| Table 52    | E1 Status Register Address Arrangement                | 228  |

| Table 53    | T1/J1 Control Register Address Arrangement            |      |

| Table 54    | Pulse Shaper Programming (T1/J1)                      | 288  |

| Table 55    | T1/J1 Status Register Address Arrangement             | 307  |

| Table 56    | Maximum Ratings                                       | 335  |

| Table 57    | Power Supply Range                                    | 335  |

| Table 58    | DC Parameters                                         | 336  |

| Table 59    | XTAL Timing Parameter Values                          | 339  |

| Table 60    | JTAG Boundary Scan Timing Parameter Values            |      |

| Table 61    | Reset Timing Parameter Values                         |      |

| Table 62    | Intel Bus Interface Timing Parameter Values           |      |

| Table 63    | Motorola Bus Interface Timing Parameter Values        | 346  |

| Table 64    | Dual Rail Optical Interface Parameter Values          |      |

| Table 65    | Receive Clock and RFSP/FREEZS Timing Parameter Values | 348  |

| Table 66    | System Interface Timing Parameter Values              | 351  |

| Table 67    | System Clock Timing Parameter Values                  | 354  |

| Table 68    | T1 Pulse Template (ANSI T1.102)                       | 356  |

| Table 69    | Capacitances                                          |      |

| Table 70    | Package Characteristic Values                         |      |

| Table 71    | AC Test Conditions                                    | 359  |

## 1 Introduction

The FALC®-LH framer and line interface component is designed to fulfill all required interfacing between an analog E1/T1/J1 line and the digital PCM system highway, H.100 or H-MVIP bus for world market telecommunication systems.

Due to its multitude of implemented functions, it fits to a wide range of networking applications and fulfills the according international standards. The FALC®-LH offers a generic E1/T1/J1 analog line interface without the need to change external components. Optional crystal-less jitter attenuation reduces the amount of required external components.

Equipped with a flexible microprocessor interface, it connects to any control processor environment. A standard boundary scan interface is provided to support board level testing. Flat pack device packaging, small number of external components and low power consumption lead to reduced overall system costs.

Other members of the FALC® family are the FALC®54 for short haul applications, the FALC®56 for long haul and short haul applications as well as the QuadFALC<sup>TM</sup> supplying four long haul and short haul interfaces on one single chip.

# E1/T1/J1 Framer and Line Interface Component for Long and Short Haul Applications FALC®-LH

**PEB 2255**

#### Version 1.3

### 1.1 Features

#### Line Interface

- High density, generic interface for all E1/T1/J1 applications

- Analog receive and transmit circuitry for long haul and short haul applications

- Data and clock recovery using an integrated digital phase locked loop

- Maximum line attenuation up to -43 dB at 1024 kHz (E1)

- and up to -36 dB at 772 kHz (T1/J1)

- Programmable transmit pulse shapes for E1 and T1/J1 pulse masks

- Programmable line build-out for CSU signals according to ANSI T1.403 + FCC68 in steps of 0 dB, -7.5 dB, -15 dB and -22.5 dB (T1/J1)

- · Low transmitter output impedances for high transmit return loss

- Tristate function of the analog transmit line outputs

- · Transmit line monitor protecting the device from damage

- Jitter specifications of ITU-T I.431, G.703, G.736 (E1), G.823 (E1) and AT&T TR62411 (T1/J1) are met

- Optional crystal-less wander and jitter attenuation/compensation

- Dual rail or single rail digital inputs and outputs

- · Unipolar NRZ or CMI coding for interfacing fibre optical transmission routes

- Selectable line codes (E1: HDB3, AMI T1/J1: B8ZS, AMI with ZCS) for analog interface

- Loss of signal indication with programmable thresholds according to ITU-T G.775 and ETS300233 (E1)/ANSI T1.403, T1.231(T1/J1)

- Clock generator for jitter free system/transmit clocks

- · Local loop and remote loop for diagnostic purposes

- Only one type of transformer (ratio 1:  $\sqrt{2}$ ) for E1 75/120  $\Omega$  and T1/J1 100/110  $\Omega$

## Frame Aligner

- Frame alignment/synthesis for 2048 kbit/s according to ITU-T G.704 (E1) and for 1544 kbit/s according to ITU-T G.704 and JT G.704 (T1/J1)

- · Programmable frame formats:

- E1: Doubleframe, CRC Multiframe (E1)

- T1: 4-Frame Multiframe (F4,FT), 12-Frame Multiframe (F12, D3/4), Extended Superframe (F24, ESF), Remote Switch Mode (F72, SLC96)

- · Selectable conditions for recover/loss of frame alignment

- CRC4 to non-CRC4 interworking of ITU-T G. 706 Annex B (E1)

- Error checking via CRC4 procedures according to ITU-T G. 706 (E1)

- Error checking via CRC6 procedures according to ITU-T G. 706 and JT G.706 (T1/J1)

- Performs synchronization in ESF format according to NTT requirements (J1)

- Alarm and performance monitoring per second

16 bit counter for CRC-, framing errors, code violations, error monitoring via E bit and

SA6 bit (E1), errored blocks, PRBS bit errors

- Insertion and extraction of alarm indication signals (AIS, Remote/Yellow Alarm, AUXP)

- IDLE code insertion for selectable channels

- 8.192 MHz/2.048 MHz (E1) or 8.192 MHz/1.544 MHz (T1/J1) system clock frequency

- Selectable 2048/4096 kbit/s backplane interface with programmable receive/transmit timeslot offset

- Programmable tristate function of 4096 kbit/s output via RDO

- Elastic store for receive and transmit route clock wander and jitter compensation; controlled slip capability and slip indication

- Programmable elastic buffer size: 2 frames/1 frame/short buffer/bypass

- Supports fractional E1 or T1 access

- Flexible transparent modes

- Programmable In-Band Loop Code detection and generation (TR62411)

- Channel loop back, line loop back or payload loop back capabilities (TR54016)

- Pseudo random bit sequence (PRBS) generator and monitor

- Provides loop-timed mode

- Clear channel capabilities (T1/J1)

## **Signaling Controller**

- HDLC controller

- Bit stuffing, CRC check and generation, flag generation, flag and address recognition, handling of bit oriented functions, programmable preamble

- DL-channel protocol for ESF format according to ANSI T1.403 or according to AT&T TR54016 (T1/J1)

- DL-channel protocol for F72 (SLC96) format

- CAS controller with last look capability, enhanced CAS- register access and freeze signaling indication

- Robbed bit signaling capability (T1/J1)

- Provides access to serial signaling data streams

- CAS Multiframe synchronization and synthesis according to ITU-T G.732

- Alarm insertion and detection (AIS and LOS in Timeslot 16)

- Transparent mode

- FIFO buffers (64 bytes deep) for efficient transfer of data packets.

- Time-slot assignment

Any combination of time slots selectable for data transfer independent of signaling mode

## Microprocessor Interface

- 8/16 bit microprocessor bus interface (Intel or Motorola type)

- · All registers directly accessible (byte or word access)

- · Multiplexed and non-multiplexed address bus operations

- Extended interrupt capabilities

- · Hardware and software reset

- · One second timer

#### General

- Boundary scan standard IEEE 1149.1

- P-MQFP-80 package; body size 14x14; pitch 0.65

- 5V power supply

- Typical power consumption 450 mW

## **Applications**

- Wireless Basestations

- E1/T1/J1 ATM Gateways, Multiplexer

- E1/T1/J1 Channel & Data Service Units (CSU, DSU)

- E1/T1/J1 Internet Access Equipment

- I AN/WAN Router

- ISDN PRI, PABX

- Digital Access Cross Connect Systems (DACS)

- SONET/SDH Add/Drop Multiplexer

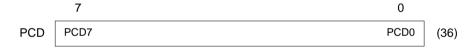

# 1.2 Logic Symbol

Figure 1 Logic Symbol

# 1.3 Typical Applications

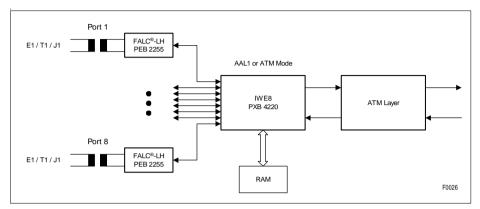

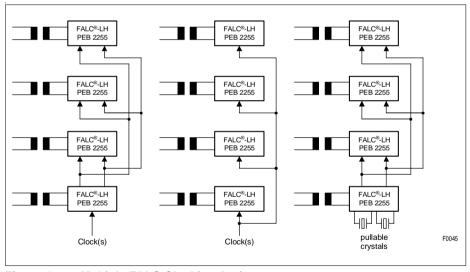

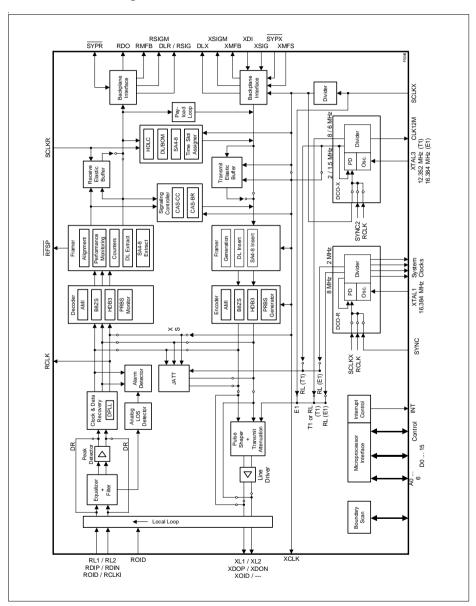

The figures show a multiple link circuit for Frame Relay applications using the FALC-LH together with the 128 channel HDLC controller M128X and the Memory Timeswitch MTLS as well as an 8 channel interface to the ATM layer combined with n IWE8 device.

Figure 2 Multiple E1/T1/J1 Link over Frame Relay

Figure 3 8 Channel E1/T1/J1 Interface to the ATM Layer

Figure 4 Multiple FALC Clocking Options

# 2 Pin Descriptions

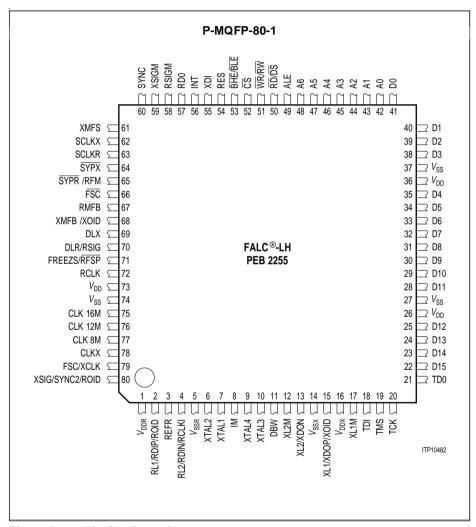

## 2.1 Pin Diagram

(top view)

Figure 5 Pin Configuration

# 2.2 Pin Definitions and Functions

:

## Table 1 Pin Definitions - Microprocessor Interface

| Pin No.              | Symbol                  | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|-------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4248                 | A0 A6                   | I                                     | Address Bus These inputs interface to seven bits of the system's address bus to select one of the internal registers for read or write.                                                                                                                                                                                                                                                                                                                                                                               |

| 4138<br>3528<br>2522 | D0D3<br>D4D11<br>D12D15 | I/O                                   | Bidirectional tristate data lines which interface to the system's data bus. Their configuration is controlled by the level of pin DBW: 8-bit mode (DBW = 0): D0 D7 are active. D8 D15 are in high impedance and have to be connected to $V_{\rm DD}$ or $V_{\rm SS}$ . 16-bit mode (DBW = 1): D0 D15 are active. In case of byte transfers, the active half of the bus is determined by A0 and $\overline{\rm BHE/BLE}$ and the selected bus interface mode (via pin IM). The unused half is in high impedance state. |

| 49                   | ALE                     |                                       | Address Latch Enable A high on this line indicates an address on the external address/data bus. The address information provided on lines A0 A6 is internally latched with the falling edge of ALE. This function allows the FALC $^8$ -LH to be connected to a multiplexed address/data bus directly. In this case, pins A0 A6 must be connected to the Data Bus pins externally. In case of demultiplexed mode this pin has to be connected to $V_{\rm DD}$ or $V_{\rm SS}$ directly.                               |

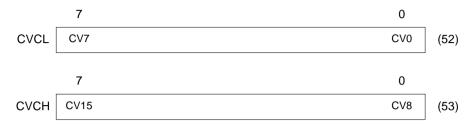

| 52                   | CS                      | I                                     | Chip Select A low signal selects the FALC®-LH for read and write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 1 Pin Definitions - Microprocessor Interface (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50      | RD/DS  | I                                     | Read Enable (Intel bus mode) This signal indicates a read operation. When the FALC®-LH is selected via CS, the RD signal enables the bus drivers to output data from an internal register addressed by A0 A6 on to the Data Bus.  Data Strobe (Motorola bus mode) This pin serves as input to control read/write operations. It is logically ored with pin CS. |

| 51      | WR/RW  | 1                                     | Write Enable (Intel bus mode) This signal indicates a write operation. When CS is active the FALC®-LH loads an internal register with data provided on the Data Bus. Read/Write Enable (Motorola bus mode) This signal distinguishes between read and write operation.                                                                                         |

| 11      | DBW    | 1                                     | Data Bus Width (Bus Interface Mode) A low signal on this input selects the 8-bit bus interface mode. A high signal on this input selects the 16-bit bus interface mode. In this case word transfer to/from the internal registers is enabled. Byte transfers are implemented by using A0 and BHE/BLE.                                                          |

| 8       | IM     | I                                     | Interface Mode The level at this pin defines the bus interface mode: A low signal on this input selects the Intel interface mode. A high signal on this input selects the Motorola interface mode.                                                                                                                                                             |

Table 1 Pin Definitions - Microprocessor Interface (cont'd)

| Pin No. | Symbol  | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|---------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53      | BHE/BLE | I + PU                                | Bus High Enable (Intel bus mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the upper byte of the data bus (D8 D15). In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD}$ . Bus Low Enable (Motorola bus mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the lower byte of the data bus (D0 D7). In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD}$ . |

| 56      | INT     | O/oD                                  | Interrupt Request INT serves as general interrupt request which may include all interrupt sources. These interrupt sources can be masked via registers IMR0 5. Interrupt status is reported via registers GIS (Global Interrupt Status) and ISR0 3,5.  Output characteristics (push-pull active low/high, open drain) are determined by programming the IPC register.  (oD = open drain output)                                                                                                                    |

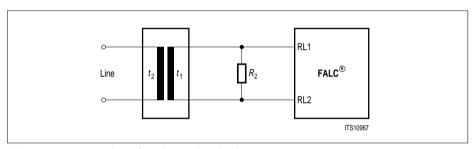

| Table 2 | Pin Def | initions - Line                       | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Symbol  | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |         | Line I                                | nterface Receive                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2       | RL1     | I (analog)                            | Line Receiver 1 Analog Input from the external transformer. Selected if LIM1.DRS = 0.                                                                                                                                                                                                                                                                                                                                                                 |

|         | RDIP    | I                                     | Receive Data Input Positive Digital input for received dual rail PCM(+) route signal which will be latched with the internal generated Receive Route Clock. An internal DPLL will extract the Receive Route Clock from the incoming data pulse. The Duty cycle of the received signal has to be close to 50%.  The Dual Rail mode is selected if LIM1.DRS = 1 and FMR0.RC1 = 1. Input polarity is selected by bit RC0.RDIS (after reset: active low). |

|         | ROID    | I                                     | Receive Optical Interface Data Unipolar data received from fiber optical interface with 2048 kbit/s (E1) or 1544 kbit/s (T1/J1). Latching of data is done with the falling edge of RCLKI. Input polarity is selected by bit RC0.RDIS. The Single Rail mode is selected if LIM1.DRS = 1 and FMR0.RC1 = 0.                                                                                                                                              |

| 80      | ROID    | I                                     | Receive Optical Interface Data LOOP.SPN = 1 Unipolar data received from fiber optical interface with 2048 kbit/s (E1) or 1544 kbit/s (T1/ J1). Latching of data is done with the falling edge of RCLKI. Input polarity is selected by bit RC0.RDIS. The Single Rail mode is selected if LIM1.DRS = 1 and FMR0.RC1 = 0.  Note: This pin contains multiple functions, see                                                                               |

|         |         |                                       | also SYNC2 and XSIG.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 2 Pin Definitions - Line Interface (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | RL2    | I (analog)                            | Line Receiver 2 Analog Input from the external transformer. Selected if LIM1.DRS = 0.                                                                                                                                                                                                                                                                                                                                                         |

|         | RDIN   | I                                     | Receive Data Input Negative Input for received dual rail PCM(-) route signal which will be latched with the internal generated Receive Route Clock. An internal DPLL will extract the Receive Route Clock from the incoming data pulse. The duty cycle of the received signal has to be close to 50%.  The dual rail mode is selected if LIM1.DRS = 1 and FMR0.RC1 = 1. Input polarity is selected by bit RC0.RDIS (after reset: active low). |

|         | RCLKI  |                                       | Receive Clock Input Receive clock input for the optical interface if LIM1.DRS = 1 and FMR0.RC1/0 = 00. Clock frequency: 2048 kHz (E1) or 1544 kHz (T1/J1).                                                                                                                                                                                                                                                                                    |

| Table 2 | Pin Definitions - | Line | Interface | (cont'd) |

|---------|-------------------|------|-----------|----------|

|---------|-------------------|------|-----------|----------|

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|--------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | Line II                               | nterface Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15      | XL1    | O (analog)                            | Transmit Line 1 Analog output to the external transformer. Selected if LIM1.DRS = 0. After reset this pin is in a high impedance state until bit FMR0.XC1 is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | XDOP   | 0                                     | Transmit Data Output Positive This digital output for transmitted dual rail PCM(+) route signals can provide - half bauded signals with 50% duty cycle (LIM0.XFB = 0) or - full bauded signals with 100% duty cycle (LIM0.XFB = 1) The data will be clocked off on the positive transitions of XCLK in both cases. Output polarity is selected by bit LIM0.XDOS (after reset: active low). The dual rail mode is selected if LIM1.DRS = 1 and FMR0.XC1 = 1. After reset this pin is in a high impedance state until register LIM1.DRS is set.                                                                                                                                                       |

|         | XOID   | O                                     | Transmit Optical Interface Data Unipolar data sent to fiber optical interface with 2048 kbit/s (E1) or 1544 kbit/s (T1/J1) which will be clocked off on the positive transitions of XCLK. Clocking off data in NRZ code is done with 100% duty cycle. Data in CMI code (E1 only) are shifted out with 50% or 100% duty cycle according to the CMI coding. Output polarity is selected by bit LIMO.XDOS (after reset: data is sent active high). The single rail mode is selected if LIM1.DRS = 1 and FMR0.XC1 = 0. After reset this pin is in a high impedance state until register LIM1.DRS is set. If LOOP.SPN = 1 this pin function is not defined and should be tristated by enabling XPM2.XLT. |

Table 2 Pin Definitions - Line Interface (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | XL1M   | I                                     | Transmit Line 1 Monitor Analog input from external transmit transformer (XL1). This pin must be connected, otherwise pin XL1 could be set into high impedance state automatically. If digital line interface mode is selected (LIM1.DRS = 1), this input has to be connected to V <sub>SSX</sub> .                                                                                                                                                                                                                                            |

| 13      | XL2    | O (analog)                            | Transmit Line 2 Analog output for the external transformer. Selected if LIM1.DRS = 0. After reset this pin is in a high impedance state until bit FMR0.XC1 is set.                                                                                                                                                                                                                                                                                                                                                                            |

|         | XDON   | 0                                     | Transmit Data Output Negative This digital output for transmitted dual rail PCM(-) route signals can provide - half bauded signals with 50% duty cycle (LIM0.XFB = 0) or - full bauded signals with 100% duty cycle (LIM0.XFB = 1) The data will be clocked off on the positive transitions of XCLK in both cases. Output polarity is selected by bit LIM0.XDOS (after reset: active low). The dual rail mode is selected if LIM1.DRS = 1 and FMR0.XC1 = 1. After reset this pin is in a high impedance state until register LIM1.DRS is set. |

| 12      | XL2M   | I                                     | Transmit Line 2 Monitor Analog input from external transmit transformer (XL2). This pin must be connected, otherwise pin XL2 could be set into high impedance state automatically. If digital line interface mode is selected (LIM1.DRS = 1), this input has to be connected to V <sub>SSX</sub> .                                                                                                                                                                                                                                            |

| Table 3 | Pin Def | initions - Cloc                       | k Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Symbol  | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

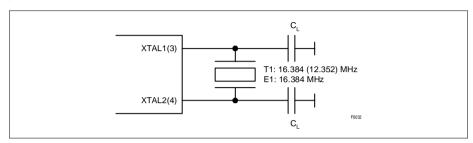

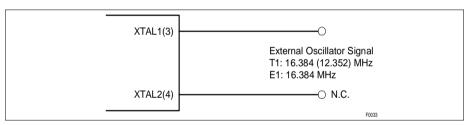

| 7       | XTAL1   | 1                                     | Crystal Connection 16.384 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6       | XTAL2   | 0                                     | A pullable crystal of 16.384 MHz has to be provided at these pins, if jitter attenuation of the system clocks is done internally. If not, or if crystal-less jitter attenuation is used, either a regular crystal of 16.384 MHz has to be connected to XTAL1/XTAL2 or a 16.384-MHz clock must be connected to XTAL1 while XTAL2 is left open.                                                                                                                                                                                                                                                                                                                                         |

| 10      | XTAL3   | I                                     | Crystal Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |