# **2 Amp PLC Line Driver**

# Description

The NCS5651 is a high efficiency, Class A/B, low distortion power line driver. It is optimized to accept a signal from a Power Line Carrier modem. The device consists of two Operational Amplifiers (opamps).

The output opamp is designed to drive up to 2 A peak into an isolation transformer or simple coil coupling to the mains. At an output current of 1.5 A, the output voltage is guaranteed to swing within 1 V or less of either rail giving the user improved SNR.

In addition to the output amplifier, a small–signal opamp is provided which can be configured as a unity gain follower buffer or can provide the first stage of a 4–pole low pass filter.

The NCS5651 offers a current limit, programmable with a single resistor,  $R_{LIM}$ , together with a current limit flag. The device provides two independent thermal flags with hysteresis: a thermal warning flag to let the user know the internal junction temperature has reached a user programmable thermal warning threshold and a thermal error flag that indicates the internal junction temperature has exceeded 150°C.

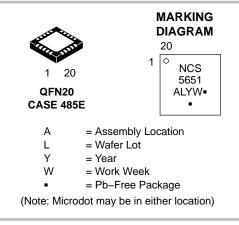

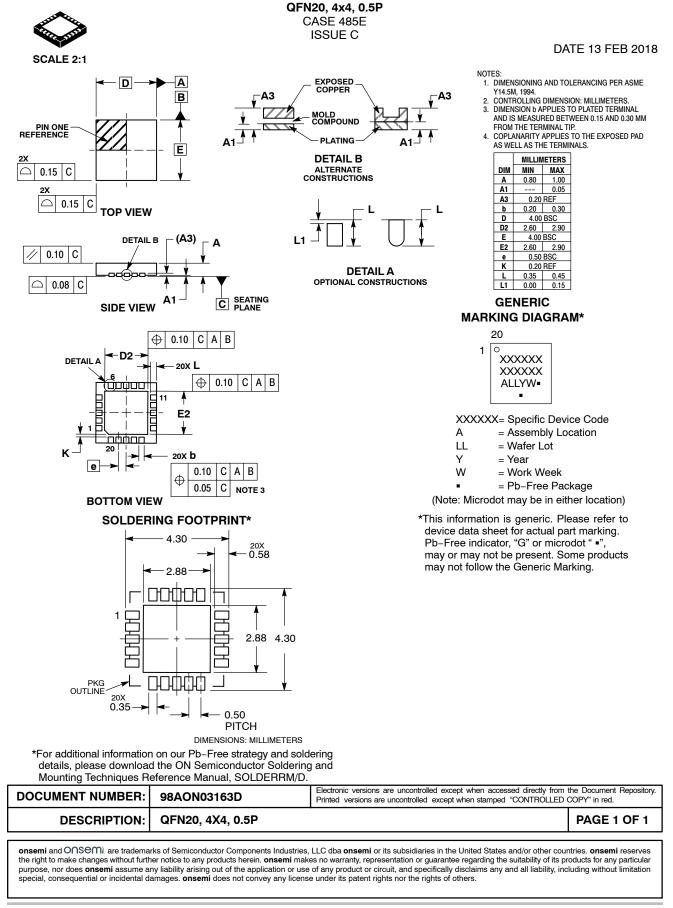

The NCS5651 has a power supply voltage range of 6–12 V. It can be shut down, leaving the outputs highly–impedant. The NCS5651 comes in a 20–lead QFN package ( $4 \times 4 \times 1 \text{ mm}^3$ ) with an exposed thermal pad for enhanced thermal reliability.

# Features

- Rail-to-Rail: Drop of Only  $\pm 1$  V with  $I_{OUT} = 1.5$  A

- V<sub>BB</sub> Supply Voltage: 6–12 V

- Flexible 4<sup>th</sup>–Order Filtering

- Current-Limit Set with One Resistor

- Diagnostic Flags Level Shifted to V<sub>CC</sub> to Simplify Interface with External MCU

- Thermal Warning Flag with Flexible Threshold Setting

- Thermal Error flag and Shutdown

- Overcurrent Flag

- Enable/Shutdown Control

- Extended Junction Temperature Range: -40°C to +125°C

- Small Package: 20–pin  $4 \times 4 \times 1 \text{ mm}^3$  NQFP with Exposed Thermal Pad

- Optimized for Operation in the CENELEC A to D Frequency Band

- This is a Pb–Free Device

#### **Typical Applications**

- Power Line Communication Driver in AMM and AMR Metering Systems

- Valve, Actuator, and Motor Driver

- Audio

# **ON Semiconductor®**

www.onsemi.com

# **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NCS5651MNTXG | QFN20<br>(Pb–Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part or orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

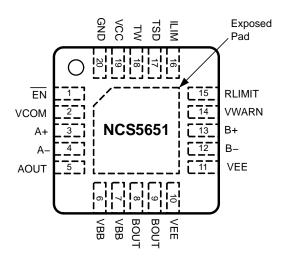

Table 1. NCS5651 PINOUT

| Signal Name | Туре   | Pin #  | Pin Description                                 |

|-------------|--------|--------|-------------------------------------------------|

| ENB         | Input  | 1      | Enable input (active low)                       |

| VCOM        | Power  | 2      | Virtual Common Voltage = (VCC – VEE)/2 (Note 1) |

| A+          | Input  | 3      | Non inverting input of opamp A                  |

| A–          | Input  | 4      | Inverting input of opamp A                      |

| AOUT        | Output | 5      | Output of opamp A                               |

| VBB         | Power  | 6, 7   | Positive Power Supply Amplifiers                |

| BOUT        | Output | 8, 9   | Output of opamp B                               |

| VEE         | Power  | 10, 11 | Negative Power Supply Amplifiers                |

| B-          | Input  | 12     | Inverting input of opamp B                      |

| B+          | Input  | 13     | Non inverting input of opamp B                  |

| VWARN       | Input  | 14     | Thermal Warning Temp Set                        |

| RLIMIT      | Input  | 15     | Output B Current Limit Set Resistor             |

| ILIM        | Output | 16     | Current Limit Flag                              |

| TSD         | Output | 17     | Thermal Shutdown Flag                           |

| TW          | Output | 18     | Thermal Warning Flag                            |

| VCC         | Power  | 19     | Logic supply                                    |

| GND         | Power  | 20     | Logic ground                                    |

| EXP         | Power  | -      | Exposed pad. To be connected to VEE potential   |

1. The principal purpose of pin 2 is to facilitate the implementation of the 4th-order low pass filter when operating on single-sided supply by providing a virtual common at mid-supply. When operating on dual balanced supplies, Pin 2 must be left floating and the external common of the dual supplies should be used for the filter implementation

Figure 2. NCS5651 Block Diagram

# Table 2. ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                            | Min                   | Max                   | Unit |

|------------------|------------------------------------------------------|-----------------------|-----------------------|------|

| TJ               | Junction temperature                                 | -40                   | +160                  | °C   |

| T <sub>STG</sub> | Storage temperature                                  | -65                   | +165                  | °C   |

| V <sub>S</sub>   | Supply voltage (V <sub>BB</sub> to V <sub>EE</sub> ) | -0.3                  | 13.2                  | V    |

| V <sub>ICR</sub> | Common Mode Voltage Range input                      | V <sub>EE</sub> – 0.3 | V <sub>BB</sub> + 0.3 | V    |

| V <sub>CCM</sub> | Logic Supply Voltage                                 |                       | 5.5                   | V    |

| VI               | Logic Input Voltage                                  | GND – 0.3             | V <sub>CC</sub> + 0.3 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

| Table 3. THERMAL CHARACTERISTICS R <sub>0</sub> | A obtained with 2S2P test boards according to JEDEC JESD51 standard. |

|-------------------------------------------------|----------------------------------------------------------------------|

|-------------------------------------------------|----------------------------------------------------------------------|

| Symbol         | Rating                                       | Typical Value | Unit |

|----------------|----------------------------------------------|---------------|------|

| $R_{\thetaJA}$ | Thermal Resistance, Junction-to-Air (Note 3) | 38            | °C/W |

# Table 4. RECOMMENDED OPERATING CONDITIONS (Note 2)

| Symbol          | Parameter                                            |     | Max  | Unit |

|-----------------|------------------------------------------------------|-----|------|------|

| T <sub>A</sub>  | Ambient Temperature                                  | -40 | +125 | °C   |

| V <sub>S</sub>  | Supply voltage (V <sub>BB</sub> to V <sub>EE</sub> ) | 6   | 12   | V    |

| V <sub>CC</sub> | Logic Supply voltage)                                | 3.0 | 5.0  | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

2. Refer to the electrical characteristics and the application information for Safe Operating Area.

# Table 5. ELECTRICAL CHARACTERISTICS $V_{BB}$ = 12 V; -40°C $\leq$ T\_J $\leq$ +125°C

| Symbol              | Parameter                         | Condition                                                                                                                                                                 | Min                   | Тур       | Max                 | Unit               |

|---------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|---------------------|--------------------|

| OPERATIO            | NAL AMPLIFIER A                   |                                                                                                                                                                           |                       |           |                     |                    |

| V <sub>OS,A</sub>   | Input offset voltage              |                                                                                                                                                                           |                       | ± 3       | ± 10                | mV                 |

| PSRRA               | Power supply rejection ratio      |                                                                                                                                                                           |                       | 25        | 150                 | $\mu V/V$          |

| I <sub>B,A</sub>    | Input bias current (Note 3)       |                                                                                                                                                                           |                       |           | 1                   | nA                 |

| e <sub>n,A</sub>    | Input voltage noise density       | f = 1 kHz; V <sub>IN</sub> = GND;<br>BW = 131 kHz                                                                                                                         |                       | 250       |                     | nV/v <sub>Hz</sub> |

| V <sub>CM,A</sub>   | Common Mode voltage range         |                                                                                                                                                                           | V <sub>EE</sub> – 0.1 |           | V <sub>BB</sub> – 3 | V                  |

| CMRRA               | Common Mode Rejection Ration      | $V_{EE} - 0.1 \le V_{CM} \le V_{CC} - 3$                                                                                                                                  | 70                    | 85        |                     | dB                 |

| Z <sub>IDM,A</sub>  | Differential Input Impedance      |                                                                                                                                                                           |                       | 0.2   1.5 |                     | GΩ   pF            |

| Z <sub>ICM,A</sub>  | Common Mode Input Impedance       |                                                                                                                                                                           |                       | 0.2   3   |                     | GΩ   pF            |

| A <sub>OL,A</sub>   | Open Loop Gain (Note 3)           | R <sub>L</sub> = 500 Ω                                                                                                                                                    | 80                    | 100       |                     | dB                 |

| GBW <sub>A</sub>    | Gain Bandwidth Product            |                                                                                                                                                                           |                       | 80        |                     | MHz                |

| $FPBW_A$            | Full Power Bandwidth (Note 3)     | CLG = +5; V <sub>OUT</sub> = 11 V <sub>PP</sub>                                                                                                                           |                       | 1.5       |                     | MHz                |

| SRA                 | Slew Rate                         |                                                                                                                                                                           |                       | 60        |                     | V/µs               |

| THD+N <sub>A</sub>  | Total Harmonic Distortion + Noise | CLG = +1; $R_L = 500 \Omega$ ; $V_O = 8 V_{PP}$ ; f = 1 kHz; $C_{in} = 220 \mu$ F;<br>$C_{out} = 330 \mu$ F                                                               |                       | 0.015     |                     | %                  |

|                     |                                   | $\begin{array}{c} {CLG = +1;} \ R_L = 50 \ \Omega; \ V_O = \\ 8 \ V_{PP}; \ f = 1 \ \text{kHz}; \ C_{in} = 220 \ \mu\text{F}; \\ C_{out} = 330 \ \mu\text{F} \end{array}$ |                       | 0.023     |                     | %                  |

| V <sub>OH,A</sub>   | Output swing from Positive Rail   |                                                                                                                                                                           |                       | 0.3       | 1                   | V                  |

| V <sub>OL,A</sub>   | Output swing from Negative Rail   | $R_L = 500 \Omega$ to mid–supply                                                                                                                                          |                       | 0.3       | 1                   | V                  |

| I <sub>SC,A</sub>   | Short-Circuit Current             |                                                                                                                                                                           |                       | 280       |                     | mA                 |

| Z <sub>O,A</sub>    | Output Impedance                  | CLG = 4; f = 100 kHz                                                                                                                                                      |                       | 0.25      |                     | Ω                  |

| C <sub>LOAD,A</sub> | Capacitive Load Drive             |                                                                                                                                                                           |                       | 100       |                     | pF                 |

| OPERATIO            | NAL AMPLIFIER B                   |                                                                                                                                                                           |                       |           |                     |                    |

| V <sub>OS,B</sub>   | Input offset voltage              |                                                                                                                                                                           |                       | ± 3       | ± 10                | mV                 |

| PSRR <sub>B</sub>   | Offset versus power supply        |                                                                                                                                                                           |                       | 25        | 150                 | μV/V               |

| I <sub>B,B</sub>    | Input bias current (Note 3)       |                                                                                                                                                                           |                       |           | 1                   | nA                 |

| e <sub>n.B</sub>    | Input voltage noise density       | f = 1 kHz; V <sub>IN</sub> = GND;                                                                                                                                         |                       | 125       |                     | nV/v <sub>Hz</sub> |

| e <sub>n,B</sub>    | Input voltage noise density  | f = 1 kHz; V <sub>IN</sub> = GND;<br>BW = 131 kHz |                       | 125      |                     | nV/v <sub>Hz</sub> |

|---------------------|------------------------------|---------------------------------------------------|-----------------------|----------|---------------------|--------------------|

| V <sub>CM,B</sub>   | Common Mode voltage range    |                                                   | V <sub>EE</sub> – 0.1 |          | V <sub>BB</sub> – 3 | V                  |

| CMRR <sub>B</sub>   | Common Mode Rejection Ratio  | $V_{EE}-0.1 \leq V_{CM} \leq V_{BB}-3$            | 70                    | 85       |                     | dB                 |

| Zi <sub>DIF,B</sub> | Differential Input Impedance |                                                   |                       | 0.2   11 |                     | GΩ   pF            |

| Zi <sub>CM,B</sub>  | Common Mode Input Impedance  |                                                   |                       | 0.2   22 |                     | GΩ   pF            |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Guaranteed by characterization or design

CLG = Closed Loop Gain

The V<sub>COM</sub> voltage is generated by an internal resistive divider. The pin should not be loaded.

6. Characterization data only. Not tested in production.

# Table 5. ELECTRICAL CHARACTERISTICS V<sub>BB</sub> = 12 V; -40°C $\leq$ T<sub>J</sub> $\leq$ +125°C

| Symbol              | Parameter                                        | Condition                                                                                                                                | Min       | Тур   | Max     | Unit |

|---------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|---------|------|

| OPERATIO            | NAL AMPLIFIER B                                  |                                                                                                                                          |           |       |         |      |

| A <sub>OL,B</sub>   | Open Loop Gain (Note 3)                          | $R_L = 5 \Omega$                                                                                                                         | 80        | 100   |         | dB   |

| GBW <sub>B</sub>    | Gain Bandwidth Product                           |                                                                                                                                          |           | 60    |         | MHz  |

| FPBW <sub>B</sub>   | Full Power Bandwidth (Note 3)                    | CLG = +5; V <sub>OUT</sub> = 11 V <sub>PP</sub>                                                                                          | 200       | 400   |         | kHz  |

| SR <sub>B</sub>     | Slew Rate                                        |                                                                                                                                          |           | 70    |         | V/μs |

|                     | Tatal Harmania Distantian 4 Maias                | $\begin{array}{l} CLG = \texttt{+1}; \ R_{L} = \texttt{50} \ \Omega; \\ V_{O} = \texttt{8} \ V_{PP}; \ f = \texttt{1} \ kHz \end{array}$ |           | 0.015 |         | %    |

| THD+N <sub>B</sub>  | Total Harmonic Distortion + Noise                | CLG = +1; R <sub>L</sub> = 50 Ω;<br>V <sub>O</sub> = 8 V <sub>PP</sub> ; f = 100 kHz                                                     |           | 0.023 |         | %    |

| V <sub>OH,B</sub>   | Output swing from Positive Rail                  | I <sub>OUT</sub> = −1.5 A @ T <sub>J</sub> = 25°C                                                                                        |           | 0.7   | 1       | V    |

|                     |                                                  | I <sub>OUT</sub> = –1.0 A @ T <sub>J</sub> = 125°C                                                                                       |           | 0.7   | 1       |      |

| V <sub>OL,B</sub>   | Output swing from Negative Rail                  | I <sub>OUT</sub> = +1.5 A @ T <sub>J</sub> = 25°C                                                                                        |           | 0.4   | 1       | V    |

|                     |                                                  | I <sub>OUT</sub> = +1.0 A @ T <sub>J</sub> = 125°C                                                                                       |           | 0.4   | 1       |      |

| I <sub>SC,B</sub>   | Short-Circuit Current                            |                                                                                                                                          |           | 280   |         | mA   |

| Z <sub>O,B</sub>    | Output Impedance                                 | CLG = 1; f = 100 kHz; ENB = 0                                                                                                            |           | 0.065 |         | Ω    |

| Z <sub>O,B</sub>    | Output Impedance                                 | ENB = 1                                                                                                                                  |           | 12    |         | MΩ   |

| C <sub>LOAD,B</sub> | Capacitive Load Drive                            |                                                                                                                                          |           | 500   |         | nF   |

| ВОТН АМР            | LIFIERS COMBINED                                 |                                                                                                                                          |           |       |         |      |

| T <sub>J,SD</sub>   | Junction temperature shutdown threshold          | (Note 6)                                                                                                                                 | +150      | +160  |         | °C   |

| $T_{J,SD,R}$        | Junction temperature shutdown recovery threshold | (Note 6)                                                                                                                                 |           | +135  |         | °C   |

| Τ <sub>W</sub>      | Thermal warning tolerance (Note 4)               | T <sub>W</sub> is determined by the ratio of 2 resistors                                                                                 |           | ± 10  |         | °C   |

| I <sub>LIM</sub>    | Current Limit Tolerance                          | I <sub>LIM</sub> is determined by<br>a single resistor                                                                                   |           | ± 50  |         | mA   |

| I <sub>QE</sub>     | Quiescent Current, enabled                       | ENB = 0                                                                                                                                  |           | 20    | 40      | mA   |

| I <sub>QD</sub>     | Quiescent Current, disabled                      | ENB = 1                                                                                                                                  |           | 120   | 150     | μA   |

| V <sub>COM</sub>    | Common mode reference output voltage             | (Note 5)                                                                                                                                 | 5.8       | 6.0   | 6.2     | V    |

|                     | Common mode reference output<br>impedance        | (Notes 5 and 6)                                                                                                                          |           | 110   |         | kΩ   |

| LOGIC               |                                                  |                                                                                                                                          |           |       |         |      |

| VIH                 | ENB input level high                             |                                                                                                                                          | GND + 2   |       |         | V    |

| V <sub>IL</sub>     | ENB input level low                              |                                                                                                                                          |           | -     | 0.8     | V    |

| I <sub>IH</sub>     | ENB input current                                | V <sub>ENB</sub> = 3.3 V                                                                                                                 |           | 10    |         | μΑ   |

| ۱ <sub>IL</sub>     | 1                                                | V <sub>ENB</sub> = 0 V                                                                                                                   |           | 0.1   |         | μΑ   |

| V <sub>OH</sub>     | Flag Output High level                           |                                                                                                                                          |           |       | GND + 2 | V    |

| V <sub>OL</sub>     | Flag Output Low level                            |                                                                                                                                          | GND + 0.8 |       |         | V    |

| t <sub>sd</sub>     | Output Shutdown time                             | ENB $0 \rightarrow 1$                                                                                                                    |           | 60    |         | ns   |

| t <sub>en</sub>     | Output Enable time                               | ENB $1 \rightarrow 0$                                                                                                                    |           | 5     | 10      | μs   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Guaranteed by characterization or design

4. CLG = Closed Loop Gain

5. The V<sub>COM</sub> voltage is generated by an internal resistive divider. The pin should not be loaded.

6. Characterization data only. Not tested in production.

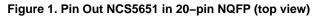

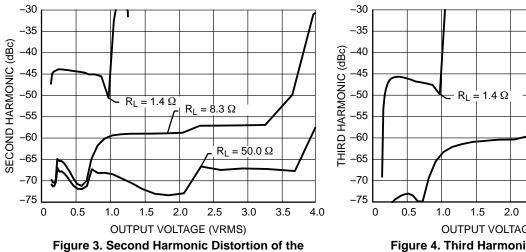

# **TYPICAL PERFORMANCE CHARACTERISTICS**

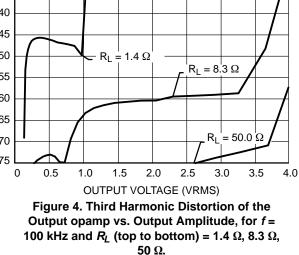

Figure 3. Second Harmonic Distortion of the Output opamp vs. Output Amplitude, for f = 100 kHz and  $R_L$  (top to bottom) = 1.4  $\Omega$ , 8.3  $\Omega$ , 50  $\Omega$ .

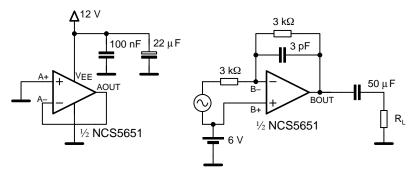

Figure 5. Test Circuit for Figures 3 and 4

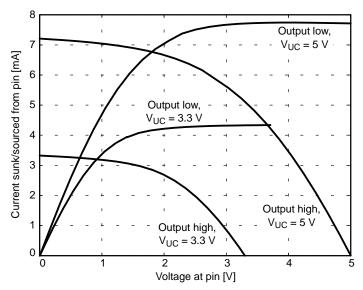

Figure 6. Digital Output Pin (ILIM, TSD, TW) Current Sourcing and Sinking Capability

# **TYPICAL APPLICATION**

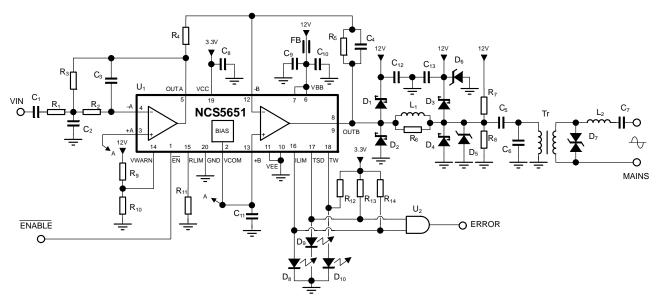

A typical power line communication (PLC) application for the NCS5651 is shown in Figure 7. The input amplifier is used in an MFB topology with the power amplifier configured as an inverting amplifier (C4 is required for stability). The circuit formed by D1–D5, L1 and R6 protects the amplifier from high–energy transients from the mains. For more information on power line communication, refer to [3]. For more information on circuit design with the NCS5651, refer to the NCN49597/9 user manual [1].

Figure 7. Typical Application Schematic for PLC modem

| Reference<br>Designator                           | Value<br>(typical) | Note                                                            | Manufacturer     | Part Number  |

|---------------------------------------------------|--------------------|-----------------------------------------------------------------|------------------|--------------|

| U <sub>1</sub>                                    |                    | Power operational amplifier                                     | ON Semiconductor | NCS5651      |

| U <sub>2</sub>                                    |                    | AND gate                                                        | ON Semiconductor | MC74VHC1G32  |

| D <sub>1</sub> , D <sub>2</sub>                   |                    | Schottky diode                                                  | ON Semiconductor | MBRA140      |

| D <sub>3</sub> , D <sub>4</sub>                   |                    | Schottky diode                                                  | ON Semiconductor | MBRA340      |

| $D_5$                                             |                    | Zener Transient Voltage suppressor                              | ON Semiconductor | 1SMA11ATG3   |

| D <sub>6</sub>                                    |                    | Zener Transient Voltage suppressor                              | ON Semiconductor | 1SMA12ATG3   |

| D <sub>7</sub>                                    |                    | Zener Transient Voltage suppressor                              | ON Semiconductor | P6SMB11CAT3G |

| D <sub>8</sub> , D <sub>9</sub> , D <sub>10</sub> |                    | Low power indication LED                                        |                  |              |

| R <sub>x</sub>                                    | TBD                |                                                                 |                  |              |

| C <sub>x</sub>                                    | TBD                |                                                                 |                  |              |

| L <sub>1</sub>                                    | 3,3 μH             | Saturation current $\ge$ 2 A                                    |                  |              |

| L <sub>2</sub>                                    | 10–27<br>μH        | Depending on transformer and communication carrier<br>frequency |                  |              |

| FB                                                | 600 Ω @<br>10 MHz  | Ferrite bead, $\geq$ 1.5 A current rating                       |                  |              |

| Tr                                                |                    | Coupling transformer                                            |                  |              |

| Table | 6. BILL | OF MA | <b>FERIALS</b> |

|-------|---------|-------|----------------|

|       |         |       |                |

# APPLICATION INFORMATION

#### **Exposed Thermal Pad**

The NCS5651 is capable of delivering 1.5 A into a complex load. Output signal swing should be kept as high as possible. This will minimize internal heat generation, reducing the internal junction temperature. The NCS5651 can swing to within 1 V of either rail without adding distortion.

An exposed thermal pad is provided on the bottom of the device to facilitate heat dissipation. The printed circuit board and soldering process must be carefully designed to minimize the thermal resistance between the exposed pad and the ambient. Refer to [1,2] for more information.

#### Multi-Feedback Filter (MFB)

CENELEC EN 50065-1 is a European standard for signaling on low-voltage electrical installations in the frequency range 3 kHz to 148. 5 kHz. More specifically Part 1 of that specification deals with frequency bands and electromagnetic disturbances introduced into the electrical mains. A practical solution to meet this requirement is to place a 4th-order filter between the output of the modem and the isolation transformer connected to the mains. In this datasheet a MFB filter topology is proposed to help meet the requirements of the CENELEC standard. Four pole filters require two op amps for implementation. The NCS5651 has an input pre-amplifier and an output power amplifier. Therefore only passive components (R's and C's) need to be added. In addition the NCS5651 has a mid-supply virtual common at pin 2 (Vcom) to facilitate implementation of the filter topology.

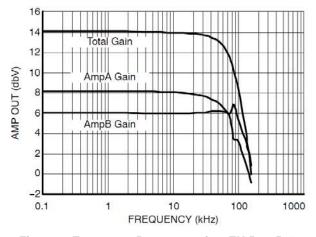

Figure 8 shows the frequency response for each stage and the overall filter.

Figure 8. Frequency Response of an EN 50065–1 Compliant Filter

#### Decoupling

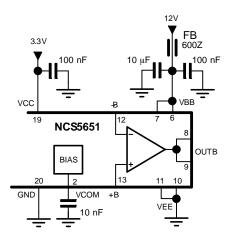

Optimal stability and noise rejection will be implemented with power supply bypassing placed as physically close to the device as possible. A parallel combination of 10  $\mu$ F and 10 nF is recommended for each sensitive point. For either single–supply operation or split supply operation, bypass should be placed directly across  $V_{BB}$  to  $V_{EE}$ . In addition add bypass from  $V_{CC}$  to GND (Figure 9).

Figure 9. Decoupling Capacitors

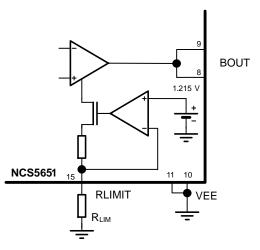

#### Current Limit (R-Limit)

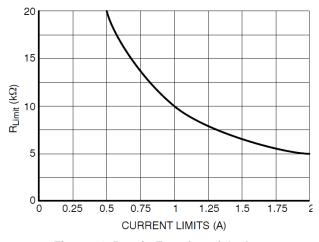

The maximal output current of the NCS5651 can be programmed by the simple addition of a resistor ( $R_{LIM}$ ) from pin 15 to  $V_{EE}$  (Figure 7). Figure 8 shows the limiting value for given resistance, with a tolerance of ±50 mA. Unlike traditional power amplifiers, the NCS5651 current limit functions both when sourcing and sinking current. To calculate the resistance required to program a desired current limit the following equation can be used:

$$_{\text{LIM}} = \frac{1.215}{\text{R}_{\text{LIM}}} \times 8197$$

If the load current reaches the set current limit, the ILIM flag will go logic high. As an example, the user may act on this by reducing the signal amplitude. When the current output recovers, the ILIM flag returns low.

Figure 10. Programming the Current Limit

Figure 11 illustrates the required resistance to program the current limit.

Figure 11.  $R_{LIM}$  in Function of the  $I_{LIM}$

#### **Thermal Shutdown and Thermal Warning Flag**

Excessive dissipation inside the amplifier, for instance during overload conditions, can result in damaging junction temperatures. A thermal shutdown protection monitors the junction temperature to protect against this.

When the internal junction temperature reaches approximately 160°C, the amplifier is disabled and placed in a high–impedance state. The amplifier will be re–enabled – assuming the Enable input is still active – when the junction temperature cools back down to approximately 135°C.

During thermal shutdown the TSD flag (thermal shut down, pin 17) will go logic high.

The user has the option to avoid entering into the TSD mode by monitoring the junction temperature via the Thermal Warning feature.

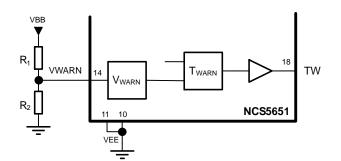

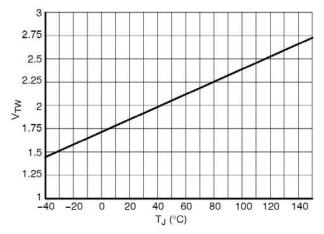

Any junction temperature ( $T_{WARN}$ ) from 105°C to 145°C can be programmed by applying the appropriate voltage to pin 14. Figure 11 shows how this may be realized with a voltage divider between VBB (pins 6,7) and VEE (the negative supply, pin 10 or 11). The voltage ratio required to program the thermal warning of the NCS5651 can be calculated using:

$$V_{TW} = 6.665 \times 10^{-3} (T_J) + 1.72$$

(eq. 1)

#### Figure 12. Setting the Thermal Warning Limit by Applying the Corresponding Threshold Voltage to Pin 14 (VWARN)

Figure 13 illustrates the linearity of the internal junction temperature to the required voltage on pin 14 (Twarn).

Figure 13. Thermal Warning Threshold in Function of Junction Temperature

# Virtual Common (V<sub>COM</sub>)

The principal purpose of  $V_{COM}$  is to provide a convenient virtual common for implementing the 4<sup>th</sup>-order CENELEC filter when operating on single-sided power supply. When operating on balanced split supplies it is recommended to use the power supply common for the filter implementation and to leave  $V_{COM}$  floating.

The output impedance of  $V_{COM}$  is high, about 110 k $\Omega$ ; thus, it is strongly recommended to use  $V_{COM}$  only for biasing the non-inverting inputs. In addition, it must be buffered with a ceramic capacitor for optimal supply noise rejection.

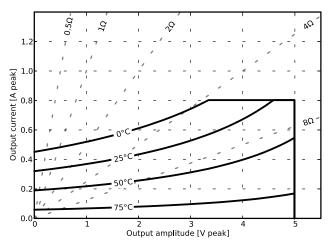

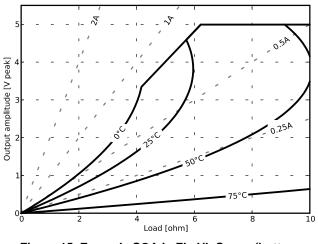

# Safe Operating Area

The safe operating area (SOA) of an amplifier is the collection of output currents  $I_L$  and the output voltages  $V_L$  that will result in normal operation with risk of destruction due to overcurrent or overheating.

In a normal application only the output amplifier of the line driver must be considered; the load on the small–signal amplifier is usually negligible.

The output amplifier SOA depends on the thermal resistance from junction to ambient  $R_{\theta JA}$ , which in turn strongly depends on board design.  $R_{\theta JA} = 50$  K/W in free air is a typical value, which may be used even if the host printed circuit board (PCB) is mounted in a small closed box, provided the transmission of frames are infrequent and widely spread in time.

This typical value is also used in the generation of the curves plotted in Figures 14 and 15.

Figure 14 shows the SOA in function of output current  $I_L$  and output voltage  $V_L$  with the ambient temperature as independent parameter. The maximum allowed current is 800 mA RMS. For that reason it is recommended to limit the output current by using  $R_{LIM} = 5 \text{ k}\Omega$ . This current limitation is plotted as a horizontal line. The maximal output voltage is limited by  $V_{CC,max}$ ,  $V_{OH}$  and  $V_{OL}$ . This results in the straight line on the right hand side of the  $V_L$ – $I_L$  plot. The area below and left from these limitations is considered as safe. The relation between output voltage and current is the impedance as seen at the output of the power operational amplifier. Constant impedance lines are represented by canted lines.

Although voltage–versus–current is the normal representation of safe operating area, a PLC line driver can only control one of these variables: voltage and current are linked through the mains impedance. Figure 15 displays exactly the same information as Figure 14 but might be easier to work with. Constant current values are now represented as canted lines.

Figure 15. Example SOA in ZL–VL Space (bottom right corner is safe)

Again, the safe operating area depends on PCB layout. Thus, the designer must verify the performance of her particular design [1].

#### **Digital Power Supply GND-Reference and Translators**

In many mixed signal applications analog GND and digital GND are not at the same potential. To minimize GND loop issues, the NCS5651 has a separate GND pin (pin 20) which should be used to reference the digital supply and the warning flags (pins 16, 17, and 18). In most applications this would be the same GND reference used for the PLC modem. Please note that at some point in the application digital GND and analog GND must be tied together.

#### REFERENCES

In this document references are made to:

- 1. ON Semiconductor, Design Manual NCN49597/9, December 2014. The latest version is available from your sales representative.

- 2. ON Semiconductor. AND8402/D Thermal Considerations for the NCS5651 (application note). 2014–08–01. Online at <u>http://www.onsemi.com/pub/Collateral/AND8402</u> <u>-D.PDF</u>

- 3. ON Semiconductor. AND9165/D. Getting started with power line communication (application note). 2014–11–01. Online at

http://www.onsemi.com/pub\_link/Collateral/AND 9165-D.PDF

# ONSEMI

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales