# NX1A4WP

# A4WP compliant high frequency wireless charging receiver front end

Rev. 2 — 4 August 2015

Product short data sheet

## 1. General description

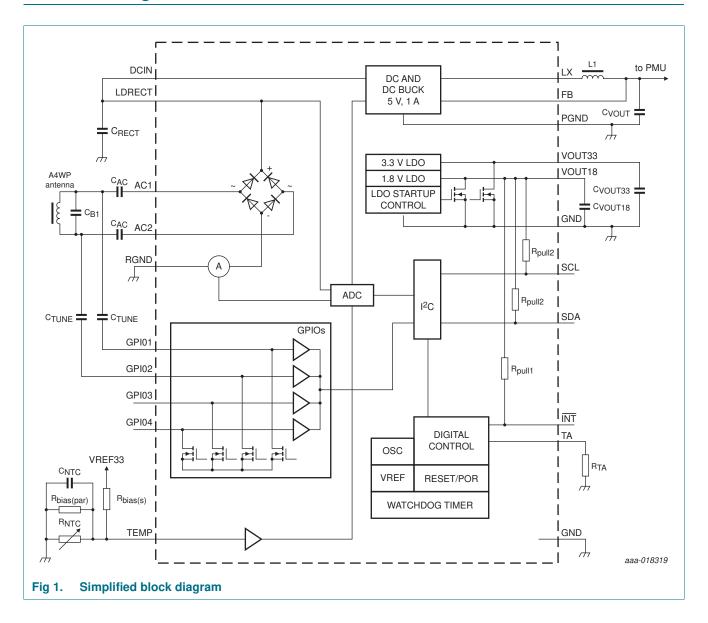

The NX1A4WP is an A4WP (Alliance for Wireless Power) compliant wireless power receiver front end. It contains a high-voltage, highly efficient rectifier, integrated LDOs, a D2C-to-DC converter, a multi-channel 12-bit ADC, four GPIOs and a Fast-Mode I²C-bus interface. The integrated rectifier supports voltages of up to 20 V and is protected by an integrated automatic clamping function and an automatic over-power protection function. The DC-to-DC regulator delivers a nominal voltage of 5 V. The host microcontroller configures the on-chip controller for automatic interrupt-driven system control. The controller reads the rectifier output voltage, current level information, junction temperature and external temperature sensor information from the ADC. It controls the DC-to-DC converter as well as the GPIOs.

## 2. Features and benefits

- 25 V tolerant antenna input pins

- Automatic over-voltage protection of the antenna inputs

- 6.78 MHz compatible integrated rectifier

- High efficiency with an active rectifier and a DC-to-DC converter

- Integrated LDOs (1.8 V and 3.3 V up to 100 mA) with auto enable and discharge path

- Integrated DC-to-DC buck regulator with 5 V, 1.2 A output

- Multi-channel 12-bit ADC subsystem

- Temperature sensor (NTC) analog interface

- USB bus power supply detection

- 400 kHz I<sup>2</sup>C-bus slave interface

- Software and power-on reset of the on-chip digital controller

- Programmable rectifier modes: active, half-active and passive

- 2 digital General Purpose Input and Output ports (GPIOs) with open-drain outputs and up to 60 V tolerance for control and communication applications

- 2 digital General Purpose Input and Output ports (GPIOs) with open-drain outputs and

25 V tolerance for control and communication applications

- Protection circuitry

- Automatic over-power protection

- Automatic AC short to ground for OVP option

- ◆ Automatic DC-to-DC over-voltage protection lock out option

- Over-temperature protection

- Over-voltage protection

- Under-voltage protection

# High frequency wireless charging receiver front end

- Under-voltage lockout (for LDOs and DC-to-DC controller)

- Specified from -40 °C to +85 °C ambient temperature

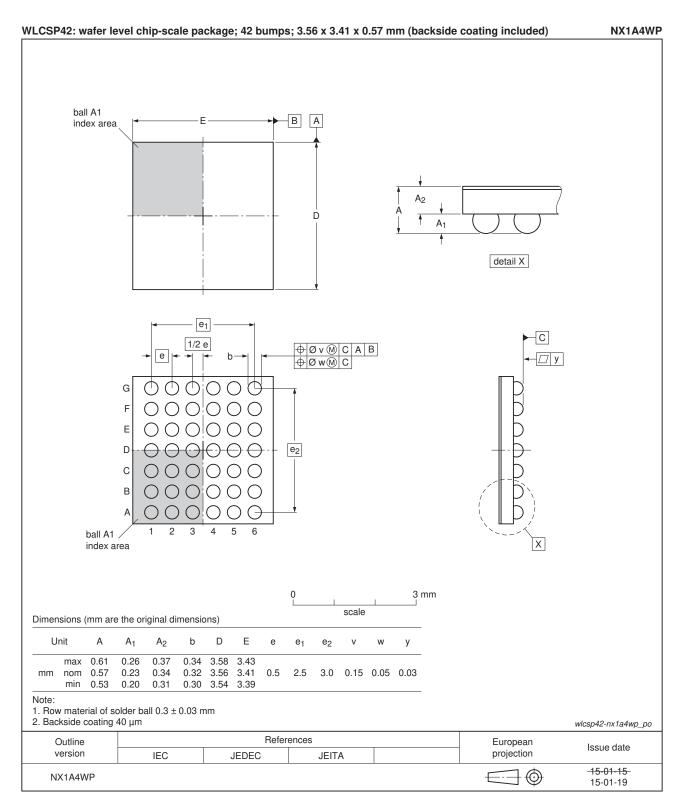

- $\blacksquare$  3.56  $\times$  3.41 mm WLCSP with 0.5 mm pitch

# 3. Applications

Portable electronic devices with integrated wireless charging / wireless power RX capabilities according to the A4WP standard

## 4. Ordering information

## Table 1. Ordering information

| Type number | Topside | Package |                                                                                                      |         |

|-------------|---------|---------|------------------------------------------------------------------------------------------------------|---------|

|             | marking | Name    | Description                                                                                          | Version |

| NX1A4WP     | NX1A4WP | WLCSP42 | Wafer level chip-scale package; 42 bumps; $3.56\times3.41\times0.57$ mm (back side coating included) | NX1A4WP |

## 4.1 Ordering options

#### Table 2. Ordering options

| Type number | Orderable part number | Package | <u> </u>                              | Minimum order quantity | Temperature range |

|-------------|-----------------------|---------|---------------------------------------|------------------------|-------------------|

| NX1A4WP     | NX1A4WPZ              | WLCSP42 | Reel 7" Q1/T1 *Standard mark chips DP | 2000                   | −40 °C to +85 °C  |

## High frequency wireless charging receiver front end

# 5. Block diagram

## High frequency wireless charging receiver front end

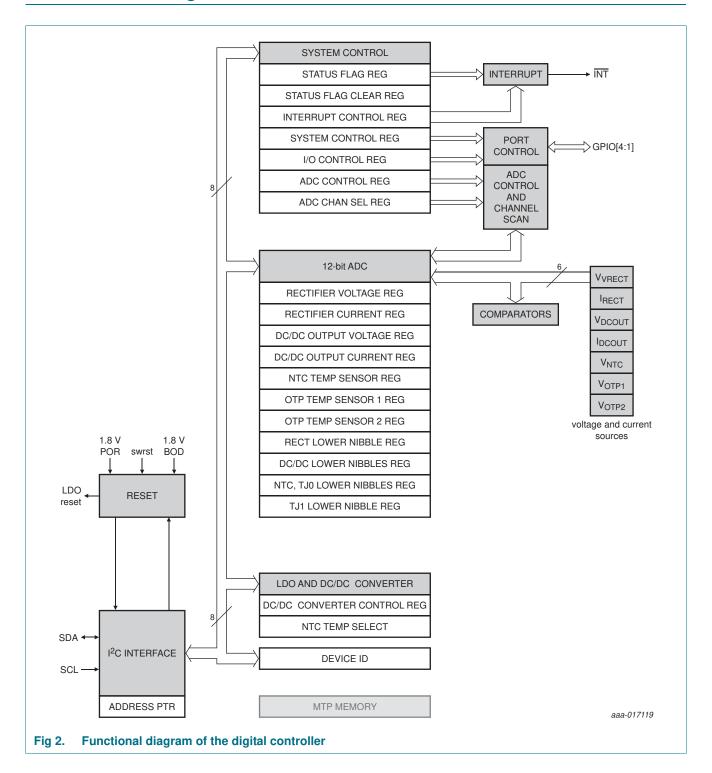

## 6. Functional diagram

## High frequency wireless charging receiver front end

#### High frequency wireless charging receiver front end

## 7. Functional description

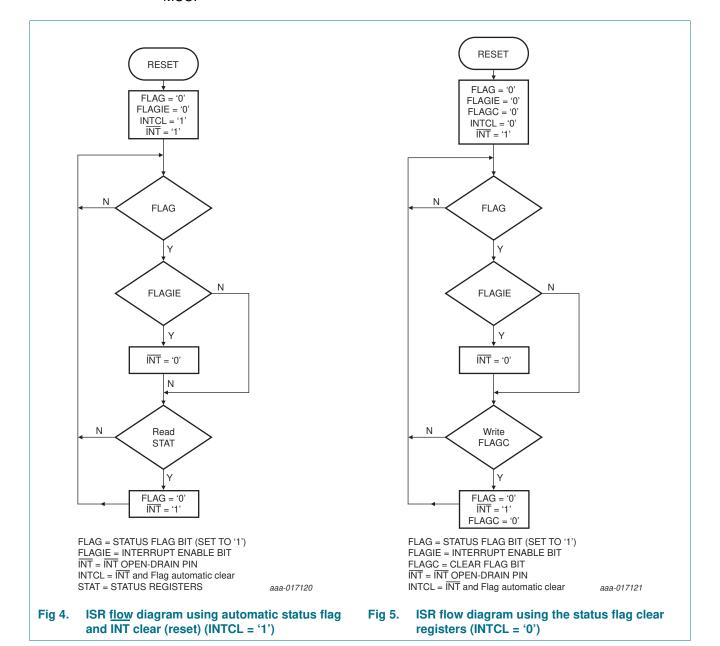

### 7.1 Interrupt handling

<u>Figure 4</u> and <u>Figure 5</u> provide flow diagrams of the interrupt service request for the host MCU.

NX1A4WP\_SDS

#### High frequency wireless charging receiver front end

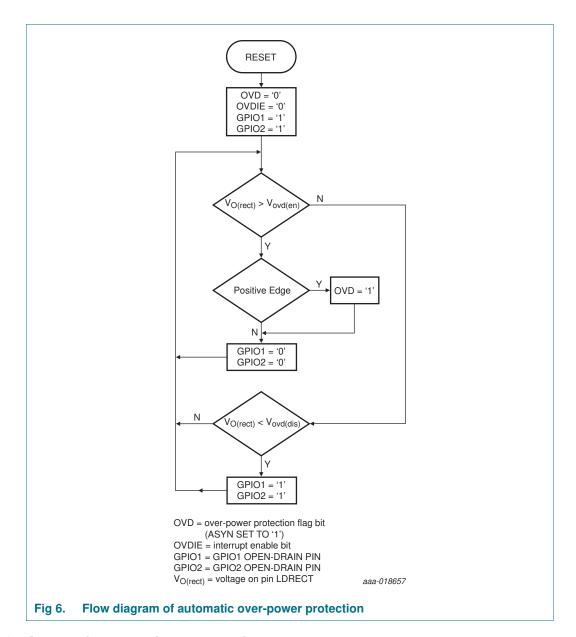

#### 7.1.1 Automatic over-power protection (OVP)

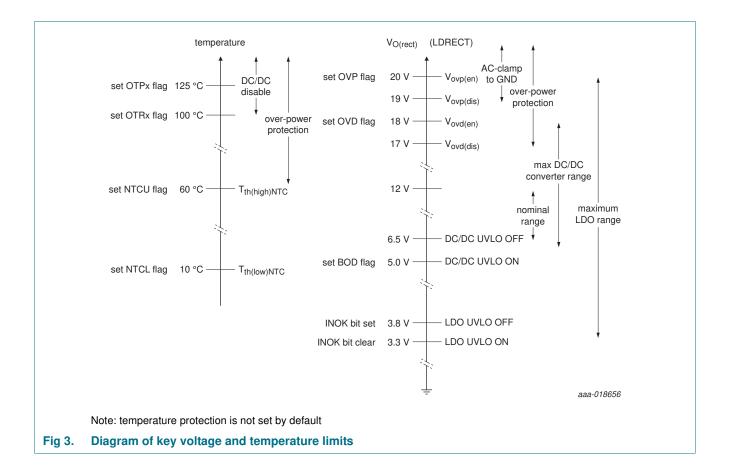

The over-power function automatically enables when the rectifier output voltage  $(V_{O(rect)})$  exceeds 18 V. It turns on GPIO1 and GPIO2 in an effort to reduce energy transfer.

The OVD function is permanently enabled. A voltage comparator is used to detect when  $V_{O(rect)}$  rises above the upper voltage limit,  $V_{ovd(en)}$ . The rising edge of the comparator output sets the OVD flag bit to logic 1. The OVD flag is a bit corresponding to the status register STATU. The OVD flag records the occurrence of the event. The GPIO1 and GPIO2 open-drain pins connect the  $C_{TUNE}$  capacitors to ground as long as  $V_{RECT}$  is above  $V_{ovd(dis)}$ . Also, if the OVDIE bit is set to logic 1, the open-drain  $\overline{INT}$  pin is set to logic 0. It initiates an interrupt service request from the host microcontroller. To clear the interrupt triggered condition, the  $V_{RECT}$  voltage must drop below the over-voltage limit ( $V_{ovd(dis)}$ ). The OVD flag bit is cleared by using the automatic clear of status bits (INTCL = logic 1 in the SYSCONL register) and reading the STATU register. Alternatively, it can be cleared by writing a logic 1 to the OVDC bit in the status flag clear register. Resetting the  $\overline{INT}$  pin back to logic 1 clears the interrupt request. Once the OVD flag is cleared, it is not set again until the  $V_{O(rect)}$  voltage crosses below  $V_{ovd(dis)}$  and then exceeds  $V_{ovd(en)}$  again. See  $\overline{Figure 4}$  and  $\overline{Figure 5}$  for diagrams of interrupt request handling by the host microcontroller and the NX1A4WP device.

7 of 43

#### High frequency wireless charging receiver front end

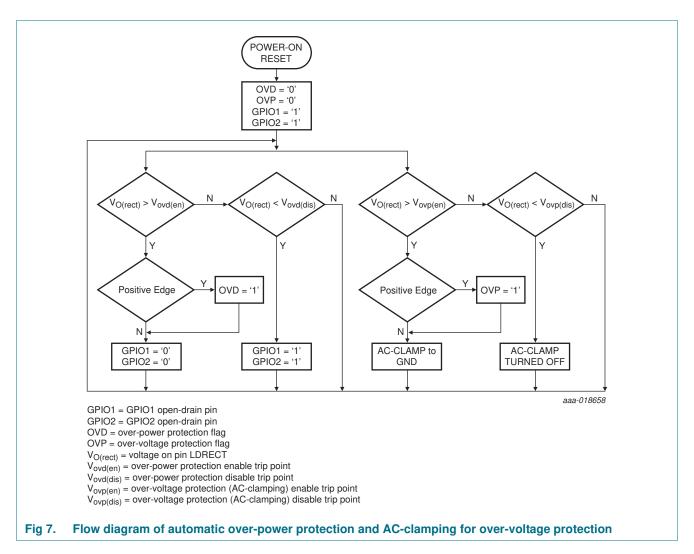

#### 7.1.2 Automatic over-voltage protection

Sudden jumps in the voltage or energy transmitted to a receiver can occur when other receivers are switched in and out of the common radiation field of a single transmitter. There are two alternative mechanisms available for over-voltage protection of the AC-input pins (AC1 and AC2). The automatic frequency over-power protection method is described above in <a href="Section 7.1.1">Section 7.1.1</a>, and the other option, the AC-clamp, is described in this section. For details see <a href="Figure 3">Figure 6</a> and <a href="Figure 7">Figure 7</a>.

The automatic over-voltage protection shorts both AC-input pins directly to ground when the rectifier output voltage ( $V_{O(rect)}$ ) exceeds the over-voltage protection limit ( $V_{ovp(en)}$ ). When the over-voltage takes place, the energy stays in the resonator circuit. In this way, the rectifier voltage stops from rising any further. When the rectifier voltage drops below the over-voltage protection limit ( $V_{ovp(dis)}$ ) the shorts are removed and the rectifier returns to normal operation.

#### High frequency wireless charging receiver front end

The AC-clamp function is permanently enabled. When  $V_{O(rect)}$  is higher than  $V_{ovp(en)}$ , the OVP flag bit in the status register is set to logic 1. Both AC-input pins are shorted to ground as long as  $V_{O(rect)}$  is above  $V_{ovp(dis)}$ . Also, if the OVPIE bit is set to logic 1, the open-drain INT pin is set to logic 0. It initiates an interrupt service request (ISR) from the host microcontroller. To clear the interrupt condition, the  $V_{O(rect)}$  voltage must drop below the over-voltage Protection Off limit ( $V_{ovp(dis)}$ ). The microcontroller clears the OVP status flag by setting the OVPC bit to logic 1 in the status flag clear register. It is also cleared if the INTCL bit in the SYSCONL register is enabled, and the STATU register is read. The INT pin is reset back to logic 1. For details, see Figure 7.

During an over-voltage event, all LDO regulators remain enabled.

In contrast, the response of the DC-to-DC converter to an over-voltage event is software selectable by the host microcontroller. The default setting of the DCOVE bit is logic 0 in the system control register. The DC-to-DC converter is permanently enabled and an OVP event does not control it.

**WARNING:** When both the DCOVE bit and the OVPIE bit are set to logic 1, the DC-to-DC converter is disabled automatically. It is done by setting the DCEN bit to logic 0 in the system control register when the OVP flag bit is set to logic 1 in the status register.

The OVP flag triggers an interrupt request and is cleared by clearing the flag bit. After the over-voltage event is removed and the rectifier returns to normal operation, the DC-to-DC converter must be re-enabled. It is re-enabled by setting the DCEN bit to logic 1 and clearing the OVP flag using the host microcontroller.

9 of 43

#### High frequency wireless charging receiver front end

## 7.2 ADC

The ADC enables direct measurements of internal voltages, currents, on-chip temperatures, and off-chip temperatures ( $V_{O(rect)}$ ,  $I_{O(rect)}$ ,  $V_{O}$ ,  $I_{O}$ , chip temperature and NTC voltage). It is a 12-bit successive approximation (SAR) Analog-to-Digital converter (ADC) with a 7-channel input multiplexer. The host microcontroller configures and controls the ADC. The ADC does a single scan cycle of the selected input channels and stores their code values in corresponding data registers for readout by the microcontroller. The analog input channels are selected or de-selected by setting the ADx bits to logic 1 or logic 0 in the ADC channel enable register. The ADC controller subsystem sequentially converts the input voltage of each of the selected input channels. It stores the corresponding 12-bit results in the respective data registers in the form of the MSB byte register and the LSB nibble register. After completion of the last selected channel, the ADC is disabled.

The ADC samples the selected input channels before the 400 kHz I<sup>2</sup>C bus allows the host MCU to read the first data byte from the first enabled channel. So, the host microcontroller does not require further control of the ADC or completion confirmation.

#### High frequency wireless charging receiver front end

### 7.3 On-chip over-temperature protection

On-chip temperature sensors are used to monitor the DC-to-DC converter and the active rectifier for excessive heating. They are intrinsic p-n-junction diode references each connected to a voltage comparator with their own voltage reference. The OTP1 or OTP2 flags in the status register are set to logic 1 whenever the diode voltage transitions above the comparator reference voltage (125 °C, typically). If this condition occurs, the DC-to-DC converter can be disabled. The automatic disable mode is enabled when both the DCTOE bit in the system control register and the corresponding OTPxIE bit in the ICON register are set to logic 1.

When the temperature drops below 100 °C (typically), another interrupt is triggered and the OTRx flag is set to logic 1. It indicates that the device has recovered from the over-temperature condition and is ready to operate in a safe range again. The OTPx and/or OTRx flags remain set to logic 1. The microcontroller can clear the flags. Alternatively, the flags can be cleared by using the automatic clear function (INTCL = logic 1) and reading the STATL register via the  $I^2C$  bus.

The OTPx or OTRx flags trigger an interrupt service request (ISR) from the microcontroller by setting the INT pin to logic 0. The microcontroller can measure the voltages directly with the ADC. It makes the necessary adjustments either by disabling the DC-to-DC converter or reducing the power of the transmitter. It can monitor the temperature until it returns to a lower value before it re-enables the DC-to-DC converter.

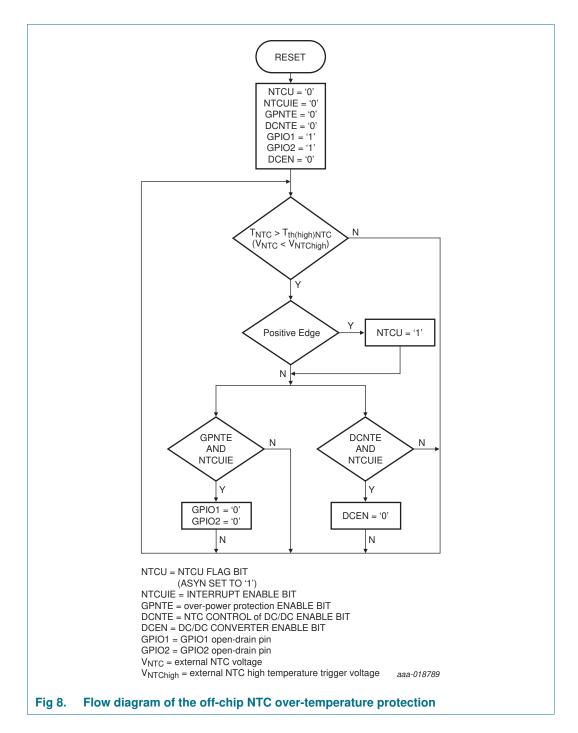

## 7.4 Off-chip NTC over- and under-temperature protection

The NX1A4WP supports one external NTC temperature sensor. A constant and accurate 3.3 V voltage source is supplied from the VREF33 pin. The NTC voltage is input through the TEMP pin and connected to two voltage comparators. The voltage comparators have their voltage references  $T_{th(high)NTC}$  typically 60 °C, and  $T_{th(low)NTC}$  typically 10 °C. Whenever the temperature is outside this range, either the NTCU flag or the NTCL flag is set to logic 1 in the status register. If the corresponding interrupt enable bits are set to logic 1 in the interrupt control register, the NTCU or NTCL flags trigger an interrupt service request (ISR) from the microcontroller by setting the  $\overline{INT}$  pin to logic 0. The microcontroller can trigger an ADC scan cycle and directly measure the output voltage of the NTC temperature sensor. For details refer to Figure 3, Figure 5 and Figure 8. (See also Table 4 and Section 7.10.4). By setting the DCNTE bit in the SYSCONL register to logic 1, the DC-to-DC converter is disabled when the upper NTC temperature limit ( $T_{th(high)NTC}$ ) is exceeded.

Refer to Section 7.10.4.4 for further details.

## High frequency wireless charging receiver front end

## 7.5 DCIN and LDRECT inputs

To minimize supply voltage noise and ripple, bypass capacitor of value between 35  $\mu$ F to 100  $\mu$ F is connected between these pins and ground.

## High frequency wireless charging receiver front end

#### 7.6 LDODCPL

The pin LDODCPL allows for noise filtering of the internal LDO18 and LDO33 supply rail. It reduces supply noise and allows the switching of the LDO supply input between  $V_{O(rect)}$  and the DC-to-DC converter output voltage in order to optimize efficiency. As soon as the DC-to-DC converter output voltage is sufficiently high, the LDO supply input is switched from the LDRECT pin to the LDDC pin. The LDDC pin is connected to the output of the DC-to-DC converter. A decoupling capacitor of 10  $\mu F$  is connected between this node and ground.

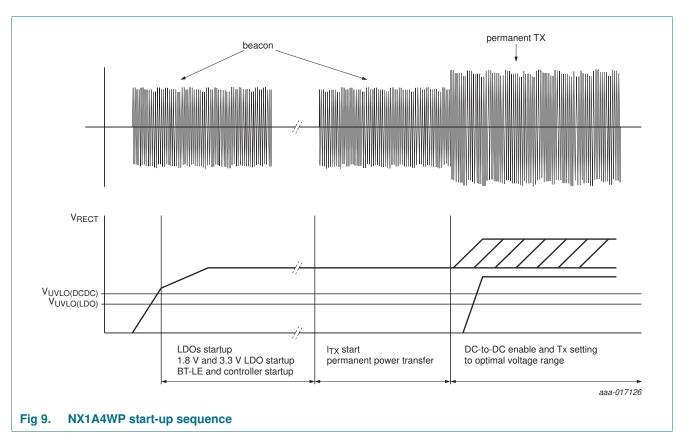

## 7.7 LDO start-up control

The LDO start-up control monitors the DC input voltage. Once this voltage exceeds  $V_{UVLO}$  the two LDOs are enabled simultaneously after a delay of ~1.5 ms. The LDOs are disabled in case their DC supply voltage drops below  $V_{BODtrip}$

$(V_{\text{UVLO(LDO)}} = V_{\text{BOD(LDO)}} + V_{\text{BODhys}})$ , see Figure 9.

If there is a shutdown, the LDOs contain discharge paths to ramp down the supply voltage.

## High frequency wireless charging receiver front end

## 7.8 General Purpose digital Input Output ports (GPIOs)

The GPIOs can be used for control and communication applications. They are software configured and controlled through the I<sup>2</sup>C and can be configured as digital inputs and/or open-drain outputs.

Each GPIO's operation mode can be controlled individually using the GPIEx bits in the IOCONL register. When configured as inputs, the logic level of each GPIO pin can be read through the associated GPI bit in the IOCONU register. If a GPIO is used as an open-drain output, the open-drain pull-down transistor is enabled. The pin is pulled low by writing a logic 0 to the related GPO bit in the IOCONL register. Otherwise, the pin is tri-stated (high impedance). When the pin is not pulled to a logic level, the input buffer should be disabled to prevent feed-through currents in the buffer.

## 7.9 External supply detect pin (TA)

The TA pin can be used to sense an external supply connection or state change. If the logic value changes from high to low or low to high for more than 11 ms, the interrupt pin is asserted. The pin cannot be disabled through  $I^2C$ , and it should not be left floating. When the TA pin is not used, it is recommended to pull it down to ground through resistor  $R_{TA}$  (see Table 4).

#### 7.10 Software interface<sup>1</sup>

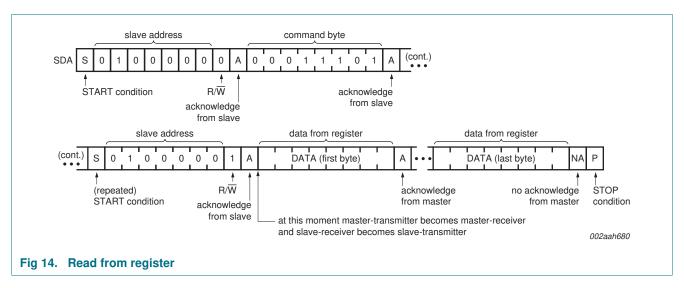

#### 7.10.1 I<sup>2</sup>C device address

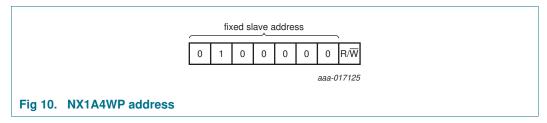

The slave address of the NX1A4WP is shown in Figure 10.

The LSB of the slave address defines the operation (read or write) to be performed. A HIGH (logic 1) selects a read operation, while a LOW (logic 0) selects a write operation.

#### 7.10.2 I<sup>2</sup>C-bus interface definition

Table 3. Interface definition

| Byte                               |         |    |    | В  | it |    |    |         |

|------------------------------------|---------|----|----|----|----|----|----|---------|

|                                    | 7 (MSB) | 6  | 5  | 4  | 3  | 2  | 1  | 0 (LSB) |

| I <sup>2</sup> C-bus slave address | 0       | 1  | 0  | 0  | 0  | 0  | 0  | R/W     |

| I/O data bus                       | B7      | B6 | B5 | B4 | В3 | B2 | B1 | B0      |

#### 7.10.3 Pointer register and command byte

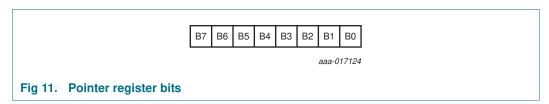

Following the successful acknowledgement of the address byte, the bus master sends a register address byte, which is stored in the Pointer register of the NX1A4WP. This register is write only.

NX1A4WP\_SDS

<sup>1.</sup> Reference: 'l<sup>2</sup>C-bus specification and user manual', UM10204, Rev. 06, 4 April 2014

#### High frequency wireless charging receiver front end

If auto increment is enabled (default: the AUTO bit in the SYSCONU register set to logic 1), the register address will be incremented after every data read or data write transaction.

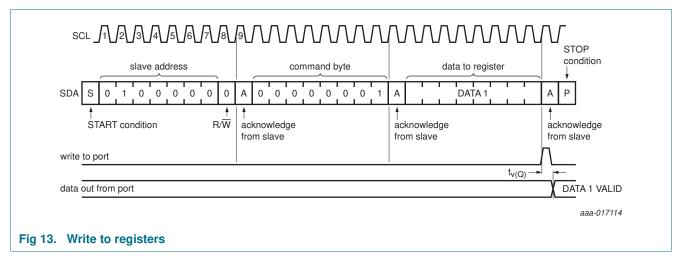

As an example, the communication flow to read the ADC channels from the ADC0DU to the ADC6DL register is shown here:

- 1. AUTO in SYSCONU = logic 1

- 2. MCU writes FDh to register address ADCEL to trigger ADC conversions on 6 of the 7 ADC input channels:

- send slave/device address 0100 0000 (with LSB = logic 0 for write operation)

- send ADCEL address 0000 1001 (09h) to the pointer register

- send data 1111 1101 to ADCEL so that the 6 ADC channels are selected and the conversions are started

- 3. MCU reads channels ADC0DU to ADC6DL:

- send the slave/device address 0100 0000 (with LSB = logic 0 for write operation)

- send the ADC0DU address 0000 1011 (0Bh) to the pointer register

- send the slave/device address 0100 0001 (with LSB = logic 1 for READ operation)

- read the register address 0Bh; the pointer register is incremented after it is read automatically from ADC0DU (0Bh) 0000 1011 to ADC1DU (0Ch) 00001100

- read the register address 0Ch; the pointer register is incremented after it is read automatically from ADC1DU (0Ch) 0000 1100 to ADC2DU (0Dh) 00001101;

- continue until e.g. ADC6DL is read and MCU terminates read sequence by not acknowledging and sending a stop condition

**NXP Semiconductors**

Table 4. NX1A4WP Register address map and bit definitions

|                            |                                                 |                                                          |        | Address | s / data co | ntent [1][2] | ]     |        |        |        |        |                |

|----------------------------|-------------------------------------------------|----------------------------------------------------------|--------|---------|-------------|--------------|-------|--------|--------|--------|--------|----------------|

| Hexade<br>cimal<br>Address | Name                                            | Description                                              | Access | B7      | В6          | B5           | B4    | В3     | B2     | B1     | В0     | Reset<br>value |

| System C                   | Control and S                                   | tatus Registers                                          |        |         |             |              |       |        |        |        |        |                |

| 00                         | STATL                                           | Status Register Lower Byte                               | RO     | IDC     | NTCL        | NTCU         | OTR2  | OTR1   | OTP2   | OTP1   | INOK   | xxxx xxxx      |

| 01                         | STATU Status Register Upper Byte                |                                                          | RO     | _       | _           | _            | OVP   | OVD    | _      | BOD    | TAH    | 0000 0000      |

| 02                         | SFCLRL Status Flag Clear Register Lower Byte    |                                                          | WO     | IDCC    | NTCLC       | NTCUC        | OTR2C | OTR1C  | OTP2C  | OTP1C  | _      | 0000 0000      |

| 03                         | SFCLRU Status Flag Clear Register Upper<br>Byte |                                                          | WO     | _       | _           | _            | OVPC  | OVDC   | _      | BODC   | TAHC   | 0000 0000      |

| 04                         | ICON                                            | Interrupt Control Register                               | R/W    | TAIE    | OVPIE       | OVDIE        | IDCIE | NTCLIE | NTCUIE | OTP2IE | OTP1IE | 0000 0000      |

| 05                         | SYSCONL                                         | System Control Register Lower<br>Byte                    | R/W    | INTCL   | DCOVE       | HRECT        | PRECT | DCNTE  | GPNTE  | _      | DCTOE  | 1000 0010      |

| 06                         | SYSCONU                                         | System Control Register Upper<br>Byte                    | R/W    | _       | _           | _            | _     | _      | AUTO   | SWRT   | DCEN   | 1111 0100      |

| 07                         | IOCONL                                          | I/O Control Register Lower Byte                          | R/W    | GPIE4   | GPIE3       | GPIE2        | GPIE1 | GPO4   | GPO3   | GPO2   | GPO1   | 0000 1111      |

| 08                         | IOCONU                                          | I/O Control Register Upper Byte                          | RO     | _       | _           | _            | _     | GPI4   | GPI3   | GPI2   | GPI1   | 0000 0000      |

| <b>ADC Reg</b>             | Registers                                       |                                                          |        |         |             |              |       |        |        |        |        |                |

| 09                         | ADCEL                                           | ADC Channel Enable Register<br>Lower Byte                | R/W    | ADEN    | AD6         | AD5          | AD4   | AD3    | AD2    | AD1    | AD0    | 0111 1111      |

| 0A                         | ADCEU                                           | ADC Channel Enable Register<br>Upper Byte                | R/W    | _       | _           | _            | _     | _      | _      | _      | _      | 0000 0000      |

| 0B                         | ADC0DU                                          | ADC Channel 0 V <sub>RECT</sub> Data Reg. Upper Byte     | RO     | ADC0DI  | J           |              |       |        |        |        |        | [2]            |

| 0C                         | ADC1DU                                          | ADC Channel 1 I <sub>RECT</sub> Data Reg. Upper Byte     | RO     | ADC1DI  | J           |              |       |        |        |        |        | [2]            |

| 0D                         | ADC2DU                                          | ADC Channel 2 V <sub>DCOUT</sub> Data<br>Reg. Upper Byte | RO     | ADC2DI  | J           |              |       |        |        |        |        | [2]            |

| 0E                         | ADC3DU                                          | ADC Channel 3 I <sub>DCOUT</sub> Data<br>Reg. Upper Byte | RO     | ADC3DI  | J           |              |       |        |        |        |        | [2]            |

| 0F                         |                                                 |                                                          | RO     | ADC4DI  | J           |              |       |        |        |        |        | [2]            |

| 10                         | ADC5DU                                          | ADC Channel 5 V <sub>OTP1</sub> Data Reg. Upper Byte     | RO     | ADC5DI  | J           |              |       |        |        |        |        | [2]            |

NXP

Semiconductors

Table 4. NX1A4WP Register address map and bit definitions

| AWA           |                                                           |                                                           |                                                                |        | Address | / data co  | ntent [1][2] |        |        |        |        |           |                |

|---------------|-----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------|--------|---------|------------|--------------|--------|--------|--------|--------|-----------|----------------|

|               | Hexade<br>cimal<br>Address                                | Name                                                      | Description                                                    | Access | B7      | B6         | B5           | B4     | В3     | B2     | B1     | В0        | Reset<br>value |

|               | 11                                                        | ADC6DU                                                    | ADC Channel 6 V <sub>OTP2</sub> Data Reg. Upper Byte           | RO     | ADC6DU  |            |              |        |        |        |        |           | [2]            |

|               | 12                                                        | ADC10DL ADC Channel 1 and 0 Data<br>Register Lower Nibble |                                                                |        | ADC10D  | L          |              |        |        |        |        |           | [2]            |

|               | ADC32DL ADC Channel 3 and 2 Data Register Lower Nibble RC |                                                           |                                                                | RO     | ADC32D  | L          |              |        |        |        |        |           | [2]            |

|               | 14                                                        | ADC54DL ADC Channel 5 and 4 Data<br>Register Lower Nibble |                                                                |        | ADC54D  | L          |              |        |        |        |        |           | [2]            |

| All informa   | 15                                                        | ADC6DL                                                    | ADC Channel 6 Data Register<br>Lower Nibble                    | RO     | ADC6DL  |            |              |        |        |        |        |           | [2]            |

|               | DC-to-DC                                                  | Control Reg                                               | isters                                                         |        |         |            |              |        |        |        |        |           |                |

| ouidod in thi | 19                                                        | DCSEL                                                     | DC-to-DC V <sub>OUT</sub> and I <sub>OUT</sub> Level<br>Select | R/W    | V3      | V2         | V1           | V0     | C3     | C2     | C1     | C0        | 0100 1011      |

|               | NTC inter                                                 | rupt tempera                                              | ture limit control register                                    |        |         |            |              |        |        |        |        |           |                |

| -             | 1A NTCSEL NTC High and Low INT Level R/W Select           |                                                           | R/W                                                            | _      | _       | NTCUL<br>1 | NTCUL<br>0   | _      | _      | NTCLL1 | NTCLL0 | 0001 0001 |                |

| ,             | Device Identification code                                |                                                           |                                                                |        |         |            | •            |        | •      | •      |        | •         |                |

| one disolais  | 1F                                                        | DEVID Device Identification Code Register                 |                                                                | RO     | DEVID7  | DEVID6     | DEVID5       | DEVID4 | DEVID3 | DEVID2 | DEVID1 | DEVID0    | 0100 1000      |

<sup>[1]</sup> Bits described with '-' in this table are reserved for future use. Always write logic 0 to undefined bits.

<sup>[2]</sup> Bits with no value given have no default (e.g. the ADC data bits). Generation of valid content for those bits has to be triggered by conducting an ADC conversion cycle.

## 7.10.4 Register descriptions

#### 7.10.4.1 Status registers (STATL, address 00h; STATU, address 01h)

The status register contains basic device status flags. It contains temperature limit status, over-current, over-voltage, recorded reset events (BOD), and detection of the presence of a USB power supply. The status registers are read-only and writes to these registers have no effect. With autoincrement and autoclear active (AUTO = logic 1 and INTCL = logic 1), both registers must be read simultaneously in one I<sup>2</sup>C read segment. It is to prevent the STATU register being cleared with the next ACK, due to data caching in this mode and information might get lost. These registers should be read after power-up of the controller to clear them initially as it is not done by the POR. A read operation is performed as described in Section 7.10.5.2.

High frequency wireless charging receiver front end

Table 5. Status register lower byte (STATL, address 00h)

| Bit     | 7   | 6    | 5    | 4    | 3    | 2        | 1        | 0    |

|---------|-----|------|------|------|------|----------|----------|------|

| Symbol  | IDC | NTCL | NTCU | OTR2 | OTR1 | OTP2 [3] | OTP1 [3] | INOK |

| Default | Χ   | Х    | Х    | Х    | Х    | Х        | Χ        | Χ    |

Table 6. Status register lower byte bit mapping (STATL, address 00h)

| Bit | Symbol   | Function [1][2]                                                                                                                                                                                     |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | INOK [2] | INOK reflects the current voltage level of the power supply for the LDO regulators (LDODCPL pin) INOK = logic 0; $V_{LDODCPL} < 3.3 \text{ V}$ INOK = logic 1; $V_{LDODCPL} > 3.8 \text{ V}$        |

| 1   | OTP1 3   | If the OTP1 (rectifier) temperature sensor rises above the $T_j$ = 125 °C limit, OTP1 toggles from logic 0 to logic 1 OTP1 = logic 0 if $T_{j(OTP1)}$ < 125 °C or after resetting OTP1              |

| 2   | OTP2 3   | If the OTP2 (DC-to-DC) temperature sensor rises above the $T_j = 125~^{\circ}C$ limit, OTP2 toggles from logic 0 to logic 1 OTP2 = logic 0 if $T_{j(OTP2)} < 125~^{\circ}C$ or after resetting OPT2 |

| 3   | OTR1     | If the OTP1 (rectifier) temperature sensor falls below the $T_j$ = 100 °C limit, OTR1 toggles from logic 0 to logic 1 OTR1 = logic 0 at any other temperature and after resetting OTR1              |

| 4   | OTR2     | If the OTP2 (DC-to-DC) temperature sensor falls below the $T_j = 100$ °C limit, OTR2 toggles logic 0 to logic 1 OTR2 = logic 0 at any other temperature and after resetting OTR2                    |

| 5   | NTCU[4]  | If the NTC sensor temperature rises above the $T_{th(high)NTC}$ limit, NTCU toggles from logic 0 to logic 1<br>NTCU = logic 0 if NTC < $T_{th(high)NTC}$ or after resetting NTCU                    |

| 6   | NTCL[4]  | If the NTC sensor temperature falls below the $T_{th(low)NTC}$ limit, NTCL toggles from logic 0 to logic 1<br>NTCL = logic 0 if NTC > $T_{th(low)NTC}$ or after resetting NTCL                      |

| 7   | IDC      | IDC = logic 1; DC-to-DC converter output current rises above the current limit (DCSEL, bits C3-C0) IDC = logic 0; DC-to-DC converter output current is below limit (DCSEL, bits C3-C0)              |

<sup>[1]</sup> The status bits, except INOK, are edge triggered on the related event occurring (edge triggered: flag stores an event at its beginning with no relation to the duration or its end. For example, the event can be a rising or a falling edge of a signal). The bits are not automatically reset once triggered. They store the event related to their function until cleared via the respective status flag clear bit or by reading the STATL register while INTCL is logic 1.

#### High frequency wireless charging receiver front end

- [2] INOK is a non-latched bit representing the level of the LDO supply voltage V<sub>LDODCPL</sub> sensed by a BOD circuit.

- [3] The OTP1 sensor is located near the rectifier area while the OPT2 sensor is near the DC-to-DC converter.

- [4] The NTC comparator has hysteresis of 10 °C.

Table 7. Status register upper byte (STATU, address 01h)

| Bit     | 7 | 6 | 5 | 4   | 3   | 2 | 1   | 0   |

|---------|---|---|---|-----|-----|---|-----|-----|

| Symbol  | - | _ | _ | OVP | OVD | - | BOD | TAH |

| Default | 0 | 0 | 0 | 0   | 0   | 0 | 0   | 0   |

Table 8. Status register upper byte bit mapping (STATU, address 01h)

| Bit | Symbol             | Function [1] [2]                                                                                                                                                                                                                                                    |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TAH <sup>[2]</sup> | TAH is a non-latched bit always reflecting the TA input pin voltage level. It cannot be cleared via TAHC.                                                                                                                                                           |

|     |                    | TAH = logic 1; a high voltage is detected on the TA pin TAH = logic 0; a low voltage is detected on the TA pin                                                                                                                                                      |

| 1   | BOD                | BOD = logic 1; DCIN ( $V_{O(rect)}$ ) voltage falls below $V_{BOD(DCDC)}$ , brownout detector monitoring the voltage on the DCIN pin was triggered BOD = logic 0; DCIN voltage did not experience a brownout event The BOD flag is cleared on the initial power-up. |

| 2   | _                  | Reserved                                                                                                                                                                                                                                                            |

| 3   | OVD                | $\begin{aligned} & \text{OVD = logic 0; V}_{O(\text{rect})} < V_{\text{ovd(en)}} \\ & \text{OVD = logic 1; over-voltage protection limit reached} \\ & \text{(DCIN voltage} > V_{\text{ovd(en)}}) \end{aligned}$                                                    |

| 4   | OVP                | $\begin{aligned} & \text{OVP} = \text{logic 0; } V_{\text{O(rect)}} < V_{\text{ovd(en)}} \\ & \text{OVP} = \text{logic 1; AC-clamping over-voltage protection limit reached} \\ & \text{(DCIN voltage} > V_{\text{ovd(en)}}) \end{aligned}$                         |

| 5   | _                  | Reserved                                                                                                                                                                                                                                                            |

| 6   | _                  | Reserved                                                                                                                                                                                                                                                            |

| 7   | _                  | Reserved                                                                                                                                                                                                                                                            |

- [1] The status bits, except TAH, are edge triggered on the related event occurring (edge triggered: flag bit stores an event at its beginning with no relation to the duration or its end. For example, an event can be a rising and/or a falling edge of a signal). The bits are not automatically reset once triggered and only store the event related to their function until cleared via the respective status flag clear bit or by reading the STATU register while INTCL is logic 1.

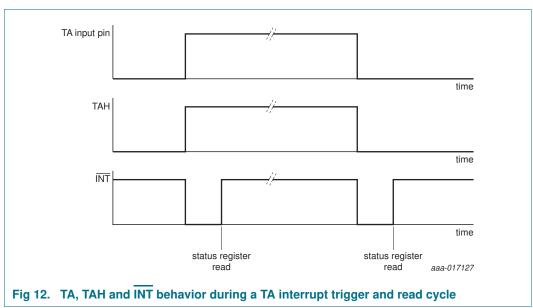

- [2] TAH is a non-latched bit representing the voltage level of the TA input pin. The INT signal records the event in a hidden register and is edge triggered on both edges of TAH. (INT is triggered in case TAH toggles from logic 0 to logic 1 or reverse). The INT hidden register is cleared by writing a logic 1 to the TAHC bit in the SFCLRU register or by reading the STATU register with the INTCL bit set to logic 1 in the SYSCONL register.

The basic behavior of TAH in combination with  $\overline{\text{INT}}$  while reading the status registers (INTCL = logic 1) is depicted in Figure 12 below. The TA input pin filters out glitches less than 11 ms wide using a digital debounce circuit.

#### High frequency wireless charging receiver front end

# 7.10.4.2 Status flag clear registers (SFCLRL, address 02h; SFCLRU, address 03h)

Status flag bits record certain events and reside in the status registers, STATL or STATU. They can be cleared individually by writing a logic 1 to the matching bit in the status flag clear registers. The bit positions in SFCLRL matching positions in STATL are cleared by writing a logic 1. Similarly, the bit positions in SFCLRU matching those positions in STATU, are cleared by writing a logic 1. Refer to <a href="Table 5">Table 5</a> and <a href="Table 7">Table 7</a> for details. For TAH, the corresponding status flag clear bit TAHC is to reset the hidden <a href="INT">INT</a> pin control latch. However, it does not clear the non-latched TAH flag bit to logic 0. The INOK bit is a non-latched bit and does not trigger an interrupt. Therefore, there is no corresponding clear bit. These 2 bits represent true logic level of the related signals and do not record events. Alternatively, all the status flags can be cleared automatically by reading each status register when the INTCL bit in the SYSCONL register is set to logic 1

Table 9. Status flag clear register lower byte (SFCLRL, address 02h)

|         |      | •     |       | •     |       | •     |       |            |

|---------|------|-------|-------|-------|-------|-------|-------|------------|

| Bit     | 7    | 6     | 5     | 4     | 3     | 2     | 1     | 0          |

| Symbol  | IDCC | NTCLC | NTCUC | OTR2C | OTR1C | OTP2C | OTP1C | <u>[1]</u> |

| Default | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0          |

Table 10. Status flag clear register upper byte (SFCLRU, address 03h)

| Bit     | 7          | 6          | 5          | 4    | 3    | 2          | 1    | 0        |

|---------|------------|------------|------------|------|------|------------|------|----------|

| Symbol  | <u>[1]</u> | <u>[1]</u> | <u>[1]</u> | OVPC | OVDC | <u>[1]</u> | BODC | TAHC [2] |

| Default | 0          | 0          | 0          | 0    | 0    | 0          | 0    | 0        |

<sup>[1]</sup> Reserved, always write logic 0 to undefined bits.

(reset default value).

<sup>[2]</sup> INOK and TAH cannot be reset. By writing a logic 1 to the TAHC bit, only the INT pin control latch for the TAH bit is cleared.

## High frequency wireless charging receiver front end

## 7.10.4.3 Interrupt control register (ICON, address 04h)

The interrupt control register enables the masking of the different available interrupt signals. When enabled, interrupt events trigger the  $\overline{\text{INT}}$  pin to be pulled low when the matching flag bit in the status registers (STATL and STATU) is set. The status registers are cleared by reading the register with INTCL = logic 1 (automatic clear) or via the status flag clear register. The status bits in each status register remain set until cleared. The  $\overline{\text{INT}}$  pin is connected to the VOUT18 supply via an integrated 20 k $\Omega$  resistor.

Table 11. Interrupt control register (ICON, address 04h)

| Bit     | 7    | 6     | 5     | 4     | 3      | 2      | 1      | 0      |

|---------|------|-------|-------|-------|--------|--------|--------|--------|

| Symbol  | TAIE | OVPIE | OVDIE | IDCIE | NTCLIE | NTCUIE | OTP2IE | OTP1IE |

| Default | 0    | 0     | 0     | 0     | 0      | 0      | 0      | 0      |

Table 12. Interrupt control register bit mapping (ICON, address 04h)

| Bit | Symbol | Function                                                                                                                                                                                       |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | OTP1IE | Over-temperature protection 1 interrupt enable OTP1IE = logic 1; OTP1 or OTR1 can trigger INT OTP1IE = logic 0;OTP1 or OTR1 trigger of INT disabled                                            |

| 1   | OTP2IE | Over-temperature protection 2 interrupt enable OTP2IE = logic 1; OTP2 or OTR2 can trigger INT OTP2IE = logic 0; OTP2 or OTR2 trigger of INT disabled                                           |

| 2   | NTCUIE | NTC high temperature limit exceeded $\underline{(T_{th(high)NTC})}$ $\overline{INT}$ enable NTCUIE = logic 1; NTCU can trigger INT NTCUIE = logic 0; NTCU trigger of $\overline{INT}$ disabled |

| 3   | NTCLIE | NTC lower temperature limit exceeded (T <sub>th(low)NTC</sub> ) INT enable NTCLIE = logic 1; NTCL can trigger INT NTCLIE = logic 0; NTCL trigger of INT disabled                               |

| 4   | IDCIE  | DC-to-DC converter output current limit exceeded INT enable IDCIE = logic 1; IDC can trigger INT IDCIE = logic 0; IDC trigger of INT disabled                                                  |

| 5   | OVDIE  | over-power protection reached INT enable  OVDIE = logic 1; OVD can trigger INT  OVDIE = logic 0; OVD trigger of INT disabled                                                                   |

| 6   | OVPIE  | V <sub>OVPon</sub> over-voltage protection limit reached INT enable OVPIE = logic 1; OVP can trigger INT OVPIE = logic 0; OVP trigger of INT disabled                                          |

| 7   | TAIE   | TA input interrupt trigger INT enable TAIE = logic 1; TA rising or falling input change can trigger INT TAIE = logic 0; TA input trigger of INT disabled                                       |

## 7.10.4.4 System control registers (SYSCONL, address 05h; SYSCONU, address 06h)

The lower byte of the system control register enables or disables possible automatic actions triggered by the status flags. Enabled interrupts trigger the  $\overline{\text{INT}}$  pin LOW. If the INTCL bit is set, the set status bits in a status register are cleared after the register is read, except for the INOK and the TAH flags. The INOK and TAH flags cannot be cleared as they are level triggered. If the INTCL bit is logic 0, the set status bits in the status registers remain set until cleared via the status flag clear register.

## High frequency wireless charging receiver front end

Table 13. System control register lower byte (SYSCONL, address 05h)

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1   | 0     |

|---------|-------|-------|-------|-------|-------|-------|-----|-------|

| Symbol  | INTCL | DCOVE | HRECT | PRECT | DCNTE | GPNTE | [1] | DCTOE |

| Default | 1     | 0     | 0     | 0     | 0     | 0     | 0   | 0     |

<sup>[1]</sup> Reserved, always write logic 0 to undefined bits

Table 14. System control register lower byte bit mapping (SYSCONL, address 05h)

| Bit | Symbol               | Function                                                                                                                                                                                                                                                                                                                            |

|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DCTOE                | Enable OTP1 or OTP2 control of DC-to-DC converter  DCTOE = logic 1; if (OTP1 and OTP1IE) are set to logic 1 or (OTP2 and  OTP2IE) are set to logic 1, DCEN is reset to logic 0  (junction over-temperature trip point reached, DC-to-DC turned off)  DCTOE = logic 0; no automatic DC-to-DC disable at over-temperature trip  point |

| 1   | _                    | Reserved                                                                                                                                                                                                                                                                                                                            |

| 2   | GPNTE                | Enable NTCU control of GPO1 and GPO2 for over-power protection GPNTE = logic 1; over-power protection enabled (GPO1, GPO2 low ohmic) as long as T <sub>th(high)NTC</sub> limit is exceeded GPNTE = logic 0: automatic over-power protection disabled                                                                                |

| 3   | DCNTE                | Enable NTCU control of DC-to-DC converter  DCNTE = logic 1; if NTCU and NTCUIE are set to logic 1, and the NTC over-voltage limit is reached, DCEN is reset to logic 0; no automatic DC-to-DC disable when the NTC upper temperature limit is reached                                                                               |

| 4   | PRECT                | PRECT = logic 1 and HRECT logic 0; enable passive rectification mode PRECT = logic 0 and HRECT = logic 0; active rectification mode enabled Bits PRECT and HRECT are mutually exclusive. If both bits are set at once, then they both default to 00b (active rectification mode)                                                    |

| 5   | HRECT                | HRECT = logic 1 and PRECT = logic 0: enable half-active rectification mode HRECT = logic 0 and PRECT = logic 0: active rectification mode enabled Bits PRECT and HRECT are mutually exclusive. If both bits are set at once, then they both default to 00b (active rectification mode)                                              |

| 6   | DCOVE                | Enable OVP control of DC-to-DC DCOVE = logic 1 If OVP and OVPIE are set to logic 1 and the AC-clamp enable trip point is reached, DCEN is reset to logic 0 DCOVE = logic 0; no automatic DC-to-DC disable at AC-clamp trip point                                                                                                    |

| 7   | INTCL <sup>[1]</sup> | Enable automatic clear (reset) of set status bits in the status registers and INT pin after a register read INTCL = logic 1; automatic clear of flag bits after read enabled INTCL = logic 0; no automatic clear. Status flags are cleared by writing a logic 1 to the related status flag clear register bits                      |

<sup>[1]</sup> When enabled, both status registers (STATL, STATU) must be read in a single I<sup>2</sup>C transaction sequence to avoid losing information.

The upper byte of the system control register controls the DC-to-DC controller. It allows for the software reset of the on-chip digital control logic back to its initialized logic state.

Table 15.

High frequency wireless charging receiver front end

|         |     | •   | • • • |     | ,   |      | ,    |      |

|---------|-----|-----|-------|-----|-----|------|------|------|

| Bit     | 7   | 6   | 5     | 4   | 3   | 2    | 1    | 0    |

| Symbol  | [1] | [1] | [1]   | [1] | [1] | AUTO | SWRT | DCEN |

| Default | 1   | 1   | 1     | 1   | 0   | 1    | 0    | 0    |

<sup>[1]</sup> Though the four MSBs [7:4] are set to logic 1 after reset and bit 3 is set to logic 0, always write logic 0 to these 5 bits.

Table 16. System control register upper byte bit mapping (SYSCONU, address 06h)

System control register upper byte (SYSCONU, address 06h)

| Bit | Symbol | Function                                                                                                                                                                                                                                                    |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DCEN   | Enable DC-to-DC converter  DCEN = logic 1; DC-to-DC converter enabled  DCEN = logic 0; DC-to-DC converter disabled                                                                                                                                          |

| 1   | SWRT   | Software reset resets all registers to their power-up default values only after the I <sup>2</sup> C-bus stop condition is detected SWRT = logic 1 reset all registers; bit SWRT is reset to logic 0                                                        |

| 2   | AUTO   | Enable pointer register auto increment. Pointer register address is incremented after every data byte transfer (read or write)  AUTO = logic 1; pointer register auto increment enabled (default)  AUTO = logic 0; pointer register auto increment disabled |

| 3   | -      | Reserved                                                                                                                                                                                                                                                    |

| 4   | -      | Reserved                                                                                                                                                                                                                                                    |

| 5   | -      | Reserved                                                                                                                                                                                                                                                    |

| 6   | -      | Reserved                                                                                                                                                                                                                                                    |

| 7   | -      | Reserved                                                                                                                                                                                                                                                    |

#### 7.10.4.5 I/O control register (IOCONL, address 07h; IOCONH, address 08h)

The I/O control register controls the General Purpose Input Output (GPIO) pins. The over-power protection circuit also controls the 60 V tolerant GPIO1 and GPIO2 pins. The GPIO3 and GPIO4 pins are 25 V tolerant and can be used for control and communication applications. A logic 1 written to the GPOx bits, tri-states the open-drain output. A logic 0 enables the open-drain output and the pin is shorted to ground. The logic level of GPIO pins is read by enabling the read buffers. The read buffers are enabled by writing a logic 1 to the corresponding GPIEx bit. The logic level of the GPIO pin is found in the matching GPIx bit.

Table 17. I/O control register byte (IOCONL, address 07h)

| Bit     | 7     | 6     | 5     | 4     | 3    | 2    | 1    | 0    |

|---------|-------|-------|-------|-------|------|------|------|------|

| Symbol  | GPIE4 | GPIE3 | GPIE2 | GPIE1 | GPO4 | GPO3 | GPO2 | GPO1 |

| Default | 0     | 0     | 0     | 0     | 1    | 1    | 1    | 1    |

Table 18. I/O control register byte bit mapping (IOCONL, address 07h)

| Bit | Symbol | Function                                                                            |

|-----|--------|-------------------------------------------------------------------------------------|

| 0   | GPO1   | GPIO1 control, logic 1 = Z; logic 0 = low ohmic; OR linked to over-power protection |

| 1   | GPO2   | GPIO2 control, logic 1 = Z; logic 0 = low ohmic; OR linked to over-power protection |

| 2   | GPO3   | GPIO3 control, logic 1 = Z; logic 0 = low ohmic                                     |

| 3   | GPO4   | GPIO4 control, logic 1 = Z; logic 0 = low ohmic                                     |

NX1A4WP\_SDS

#### High frequency wireless charging receiver front end

Table 18. I/O control register byte bit mapping (IOCONL, address 07h) ...continued

| Bit | Symbol | Function                                                |

|-----|--------|---------------------------------------------------------|

| 4   | GPIE1  | GPIO1 input buffer control, logic 0 = off; logic 1 = on |

| 5   | GPIE2  | GPIO2 input buffer control, logic 0 = off; logic 1 = on |

| 6   | GPIE3  | GPIO1 input buffer control, logic 0 = off; logic 1 = on |

| 7   | GPIE4  | GPIO2 input buffer control, logic 0 = off; logic 1 = on |

Table 19. I/O control register byte (IOCONU, address 08h)

| Bit     | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|---------|-----|-----|-----|-----|------|------|------|------|

| Symbol  | [1] | [1] | [1] | [1] | GPI4 | GPI3 | GPI2 | GPI1 |

| Default | 0   | 0   | 0   | 0   | 0    | 0    | 0    | 0    |

<sup>[1]</sup> Always write logic 0 to undefined bits

Table 20. I/O control register byte bit mapping (IOCONU, address 08h)

| Bit | Symbol | Function                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------|

| 0   | GPI1   | Input data latch for GPIO1. The input buffer must be enabled by setting the GPIE1 bit to logic 1 |

| 1   | GPI2   | Input data latch for GPIO2. The input buffer must be enabled by setting the GPIE2 bit to logic 1 |

| 2   | GPI3   | Input data latch for GPIO3. The input buffer must be enabled by setting the GPIE3 bit to logic 1 |

| 3   | GPI4   | Input data latch for GPIO4. The input buffer must be enabled by setting the GPIE4 bit to logic 1 |

| 4   | _      | Reserved [1]                                                                                     |

| 5   | _      | Reserved [1]                                                                                     |

| 6   | _      | Reserved [1]                                                                                     |

| 7   | _      | Reserved [1]                                                                                     |

<sup>[1]</sup> Always write logic 0 to undefined bits

# 7.10.4.6 ADC controller subsystem channel enable registers (ADCEL, address 09h; ADCEU, address 0Ah)

The ADC channel enable registers control the individual channels to be converted during a one-time scan cycle. Channels 0 to 6 can be individually selected. The conversion cycle is triggered by writing a logic 1 to the ADEN bit in the ADCEL register. The ADC controller subsystem samples and converts all selected channels in one sweep starting at the lowest selected number and stores the results. The data is transferred to the host controller via I<sup>2</sup>C reads. After the ADC cycle is triggered, the host microcontroller can start immediately to read the conversion results.

Table 21. ADC enable register lower byte (ADCEL, address 09h)

| Bit     | 7        | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|----------|-----|-----|-----|-----|-----|-----|-----|

| Symbol  | ADEN [1] | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 |

| Default | 0        | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

## High frequency wireless charging receiver front end

ADC sweep enable for channels 0 to 6 (reset after channels are read)

| Bit | Symbol | Function                        |

|-----|--------|---------------------------------|

| 0   | AD0    | V <sub>RECT</sub> measurements  |

| 1   | AD1    | I <sub>RECT</sub> measurements  |

| 2   | AD2    | V <sub>DCOUT</sub> measurements |

| 3   | AD3    | I <sub>DCOUT</sub> measurements |

| 4   | AD4    | V <sub>NTC</sub> measurements   |

| 5   | AD5    | V <sub>OTP1</sub> measurements  |

Table 22. ADC enable register lower byte bit mapping (ADCEL, address 09h)

V<sub>OTP2</sub> measurements

The ADEN bit in the ADCEL register serves 2 purposes. It initiates ADC conversion of the selected channels and acts as a conversion busy flag. It remains logic 1 until the ADC conversion of the last selected channel is completed, and then, it is cleared. The ADEN bit cannot be written to until it is cleared to logic 0 by the ADC controller. There is no interrupt associated with the ADC.

Table 23. ADC enable register upper byte (ADCEU, address 0Ah)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol  | [1] | [1] | [1] | [1] | [1] | [1] | [1] | [1] |

| Default | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

<sup>[1]</sup> Reserved, always write logic 0 to undefined bits.

AD6

ADEN 🗓

#### 7.10.4.7 ADC channel data registers (ADCxDU, ADCxDL, addresses 0Bh - 14h)

The ADC data registers are separated into upper byte and lower nibble of the respective 12-bit data word generated by the ADC for each channel conversion. In cases where an 8-bit value is sufficient, only the upper byte of each value can be read to reduce the read cycle time. Each 12-bit data word consists of ADCxDU(8 MSBs) and ADCxDL(4 LSBs).

Table 24. ADC channels, range and nominal resolution (ADCxDU, ADCxDL, addresses 0Ah - 17h)

| ADC     | Data                                 |                                   |                                                                      |    |                               |                             |    |    | ADC channel                                      |

|---------|--------------------------------------|-----------------------------------|----------------------------------------------------------------------|----|-------------------------------|-----------------------------|----|----|--------------------------------------------------|

| address | B7                                   | B6                                | B5                                                                   | B4 | В3                            | B2                          | B1 | B0 |                                                  |

| 0Bh     | ADC                                  | 0DU                               |                                                                      |    |                               |                             |    |    | V <sub>RECT</sub> upper byte                     |

| 0Ch     | ADC                                  | 1DU                               |                                                                      |    |                               |                             |    |    | I <sub>RECT</sub> upper byte                     |

| 0Dh     | ADC                                  | 2DU                               |                                                                      |    |                               |                             |    |    | V <sub>DCOUT</sub> upper byte                    |

| 0Eh     | ADC3DU I <sub>DCOUT</sub> upper byte |                                   |                                                                      |    | I <sub>DCOUT</sub> upper byte |                             |    |    |                                                  |

| 0Fh     | ADC                                  | DC4DU V <sub>NTC</sub> upper byte |                                                                      |    |                               | V <sub>NTC</sub> upper byte |    |    |                                                  |

| 10h     | ADC                                  | 5DU                               |                                                                      |    |                               |                             |    |    | V <sub>OTP1</sub> upper byte                     |

| 11h     | ADC                                  | 6DU                               |                                                                      |    |                               |                             |    |    | V <sub>OTP2</sub> upper byte                     |

| 12h     | ADC                                  | 1DL                               |                                                                      |    | ADC                           | 0DL                         |    |    | $I_{RECT}$ lower nibble, $V_{RECT}$ lower nibble |

| 13h     | ADC                                  | 3DL                               |                                                                      |    | ADC                           | 2DL                         |    |    | Reserved nibble, V <sub>DCOUT</sub> lower nibble |

| 14h     | ADC5DL ADC4DL                        |                                   | ADC4DL V <sub>OTP1</sub> lower nibble, V <sub>NTC</sub> lower nibble |    |                               |                             |    |    |                                                  |

| 15h     |                                      |                                   |                                                                      |    | ADC                           | 6DL                         |    |    | V <sub>OTP2</sub> lower nibble                   |

<sup>[1]</sup> Writing to the ADEN bit triggers the ADC controller subsystem to convert all the selected channels in one conversion cycle. The ADC controller is fast enough so that the first data can be read immediately through the 400 kHz I<sup>2</sup>C bus. Although not recommended for actual implementation, the following is just for completeness of information.

## High frequency wireless charging receiver front end

The ADC channel binary codes related to electrical signals are listed in <u>Table 26</u> to <u>Table 27</u>. The individual scaling per channel may differ, as the channels are scaled to the respective range.

Table 25. Rectifier output voltage coding, channel ADC0Dx, V<sub>RECT</sub>

| Channel electrical value | ADC readout, | ADC0DU<br>0Bh[7:0]b     | ADC0DL<br>12h[3:0]b       |

|--------------------------|--------------|-------------------------|---------------------------|

| V <sub>RECT</sub> [V]    | decimal code | upper byte, binary code | lower nibble, binary code |

| 4                        | 500          | 00011111                | 0100                      |

| 5                        | 624          | 00100111                | 0000                      |

| 6                        | 750          | 00101110                | 1110                      |

| 7                        | 875          | 00110110                | 1011                      |

| 8                        | 999          | 00111110                | 0111                      |

| 9                        | 1124         | 01000110                | 0100                      |

| 10                       | 1249         | 01001110                | 0001                      |

| 11                       | 1374         | 01010101                | 1110                      |

| 12                       | 1499         | 01011101                | 1011                      |

| 13                       | 1624         | 01100101                | 1000                      |

| 14                       | 1749         | 01101101                | 0101                      |

| 15                       | 1875         | 01110101                | 0011                      |

| 16                       | 1999         | 01111100                | 1111                      |

| 17                       | 2125         | 10000100                | 1101                      |

| 18                       | 2250         | 10001100                | 1010                      |

| 19                       | 2374         | 10010100                | 0110                      |

| 20                       | 2498         | 10011100                | 0010                      |

Table 26. Rectifier output current coding, channel ADC1Dx,

| Channel electrical value  | ADC readout, | ADC1DU<br>0Ch[7:0]b     | ADC1DL<br>12h[7:4]b       |

|---------------------------|--------------|-------------------------|---------------------------|

| I <sub>RECT</sub> [1] [A] | decimal code | upper byte, binary code | lower nibble, binary code |

| 0.1                       | 160          | 00001010                | 0000                      |

| 0.2                       | 336          | 00010101                | 0000                      |

| 0.3                       | 504          | 00011111                | 1000                      |

| 0.4                       | 688          | 00101011                | 0000                      |

| 0.5                       | 856          | 00110101                | 1000                      |

| 0.6                       | 1024         | 01000000                | 0000                      |

| 0.7                       | 1199         | 01001010                | 1111                      |

| 0.8                       | 1370         | 01010101                | 1010                      |

| 0.9                       | 1535         | 01011111                | 1111                      |

| 1.0                       | 1697         | 01101010                | 0001                      |

| 1.1                       | 1853         | 01110011                | 1101                      |

<sup>[1]</sup> I<sub>RECT</sub> can be estimated using approximation formulas:

$I_{RECT} \approx ADC(12bit) \; / \; 1715$

$I_{RECT} \approx ADC(8bit) / 107$

## High frequency wireless charging receiver front end

Table 27. DC-to-DC converter output voltage coding, channel ADC2Dx, V<sub>DCOUT</sub>

| Channel electrical value | ADC readout, | ADC2DU<br>0Dh[7:0]b     | ADC2DL<br>13h[3:0]b       |

|--------------------------|--------------|-------------------------|---------------------------|

| V <sub>DCOUT</sub> [V]   | decimal code | upper byte, binary code | lower nibble, binary code |

| 4.2                      | 1566         | 01100001                | 1110                      |

| 4.4                      | 1642         | 01100110                | 1010                      |

| 4.6                      | 1716         | 01101011                | 0100                      |

| 4.8                      | 1792         | 01110000                | 0000                      |

| 5.0                      | 1866         | 01110100                | 1010                      |

| 5.2                      | 1941         | 01111001                | 0101                      |

| 5.4                      | 2016         | 01111110                | 0000                      |

| 5.6                      | 2091         | 10000010                | 1011                      |

| 5.8                      | 2166         | 10000111                | 0110                      |

| 6.0                      | 2240         | 10001100                | 0000                      |

| 6.2                      | 2315         | 10010000                | 1011                      |

The DC-to-DC converter current readout offers only 7 effective bits.

Table 28. DC-to-DC converter output current coding, channel ADC3Dx, I<sub>DCOUT</sub>

| Channel electrical value            | ADC3DU<br>0Eh[7:0]d      | ADC3DU<br>0Eh[7:0]b     |

|-------------------------------------|--------------------------|-------------------------|

| I <sub>DCOUT</sub> [A] (average)[1] | upper byte, decimal code | upper byte, binary code |

| 0.06                                | 35                       | 00100011                |

| 0.14                                | 39                       | 00100111                |

| 0.23                                | 43                       | 00101011                |

| 0.32                                | 47                       | 00101111                |

| 0.42                                | 51                       | 00110011                |

| 0.51                                | 55                       | 00110111                |

| 0.61                                | 59                       | 00111011                |

| 0.70                                | 63                       | 00111111                |

| 0.79                                | 67                       | 01000011                |

| 0.89                                | 71                       | 01000111                |

| 1.0                                 | 75                       | 01001011                |

| 1.1                                 | 79                       | 01001111                |

| 1.2                                 | 83                       | 01010011                |

| 1.3                                 | 87                       | 01010111                |

| 1.4                                 | 91                       | 01011011                |

<sup>[1]</sup> I<sub>DCOUT</sub> is the nominal value for the maximum average output current when the DC-to-DC converter is used with a 2.2 µH inductor for L1 in <u>Figure 1</u>. Accuracy of the limit is largely dependent upon the inductor value tolerance

## High frequency wireless charging receiver front end

Table 29.  $V_{NTC}$  voltage coding and temperature coding, channel ADC4Dx,  $V_{NTC}$

| Channel electrical value |                                            | ADC readout, | ADC4DU<br>0Fh[7:0]b        | ADC4DL<br>14h[3:0]b          |

|--------------------------|--------------------------------------------|--------------|----------------------------|------------------------------|

| V <sub>NTC</sub> [1] [V] | $T_{amb}$ [°C] (10 k $\Omega$ B[1] = 3380) | decimal code | upper byte,<br>binary code | lower nibble,<br>binary code |

| 3.05                     | -40                                        | 3783         | 11101100                   | 0111                         |

| 3.02                     | -35                                        | 3756         | 11101010                   | 1100                         |

| 3.00                     | -30                                        | 3723         | 11101000                   | 1011                         |

| 2.96                     | -25                                        | 3682         | 11100110                   | 0010                         |

| 2.92                     | -20                                        | 3630         | 11100010                   | 1110                         |

| 2.87                     | -15                                        | 3568         | 11011111                   | 0000                         |

| 2.81                     | -10                                        | 3494         | 11011010                   | 0110                         |

| 2.74                     | -5                                         | 3407         | 11010100                   | 1111                         |

| 2.66                     | 0                                          | 3306         | 11001110                   | 1010                         |

| 2.57                     | 5                                          | 3192         | 11000111                   | 1000                         |

| 2.47                     | 10                                         | 3065         | 10111111                   | 1001                         |

| 2.36                     | 15                                         | 2927         | 10110110                   | 1111                         |

| 2.24                     | 20                                         | 2779         | 10101101                   | 1011                         |

| 2.11                     | 25                                         | 2620         | 10100011                   | 1100                         |

| 1.98                     | 30                                         | 2461         | 10011001                   | 1101                         |

| 1.85                     | 35                                         | 2297         | 10001111                   | 1001                         |

| 1.72                     | 40                                         | 2131         | 10000101                   | 0011                         |

| 1.59                     | 45                                         | 1967         | 01111010                   | 1111                         |

| 1.46                     | 50                                         | 1809         | 01110001                   | 0001                         |

| 1.34                     | 55                                         | 1657         | 01100111                   | 1001                         |

| 1.22                     | 60                                         | 1513         | 01011110                   | 1001                         |

| 1.11                     | 65                                         | 1377         | 01010110                   | 0001                         |

| 1.01                     | 70                                         | 1251         | 01001110                   | 0011                         |

| 0.91                     | 75                                         | 1136         | 01000111                   | 0000                         |

| 0.83                     | 80                                         | 1029         | 01000000                   | 0101                         |

| 0.75                     | 85                                         | 931          | 00111010                   | 0011                         |

| 0.68                     | 90                                         | 842          | 00110100                   | 1010                         |

| 0.61                     | 95                                         | 762          | 00101111                   | 1010                         |

| 0.55                     | 100                                        | 690          | 00101011                   | 0010                         |

| 0.50                     | 105                                        | 624          | 00100111                   | 0000                         |

| 0.46                     | 110                                        | 566          | 00100011                   | 0110                         |

| 0.41                     | 115                                        | 513          | 00100000                   | 0001                         |

| 0.37                     | 120                                        | 466          | 00011101                   | 0010                         |

| 0.34                     | 125                                        | 423          | 00011010                   | 0111                         |

<sup>[1]</sup> Refer to the NTC parameters in <u>Table 40</u>, Block Diagram in <u>Figure 1</u> and trimester circuit component values in <u>Table 4</u>.

#### High frequency wireless charging receiver front end

The NTC temperature values can be approximated for the full 12-bit value by the formula:

$$ADC(12bit) = trunc(0.00191 \times {T_{amb}}^3 - 0.225 \times {T_{amb}}^2 - 22.76 \times {T_{amb}} + 3295)$$

The maximum error within the temperature range of -40 °C to +85 °C is < 3 %.

For the 8-bit MSB value, the approximation formula is:

$$ADC(8bit) = trunc(0.0001 \times T_{amb}^{3} - 0.0121 \times T_{amb}^{2} - 1.43 \times T_{amb} + 204)$$

The maximum error within the temperature range of -40 °C to +80 °C is < 3 %.

Table 30. V<sub>OTPx</sub>, on-chip temperature sensor coding, channel ADC5Dx and ADC6Dx, V<sub>OTPx</sub>