# 3.3V/5V PECL/ECL 3GHz DUAL DIFFERENTIAL 2:1 MULTIPLEXER

### ECL Pro™ SY100EP56V FINAL

- Dual, fully differential 2:1 PECL/ECL multiplexer

- Guaranteed AC parameters over temperature/ voltage:

- > 3GHz f<sub>MAX</sub> (toggle)

- < 100ps within device skew</li>

- < 230ps rise/fall times</li>

- < 500ps propagation delay</li>

- Flexible power supply: 3.0V to 5.5V

- Wide operating temperature range: -40°C to +85°C

- V<sub>BB</sub> reference for AC-coupled and single-ended applications

- Both channels have independent input select or common select control

- 100k PECL/ECL compatible logic

- Available in 20-pin TSSOP package

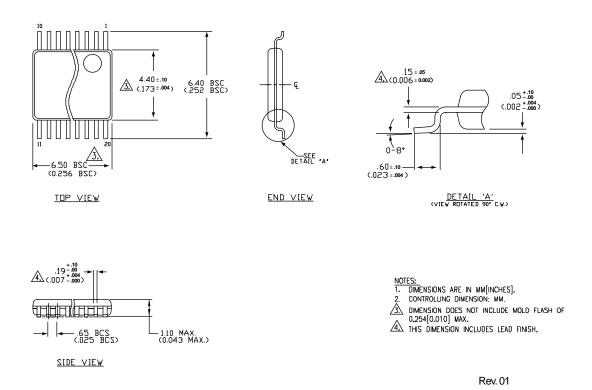

20-pin TSSOP Package

ECL Pro™

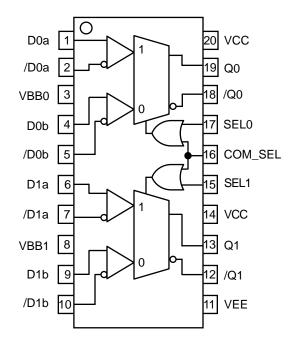

The SY100EP56V is a high-speed, low-skew, fully differential Dual PECL/ECL 2:1 multiplexer. This device is a pin-for-pin, plug-in replacement to the MC10/100EP56DT. Two separate 2:1 multiplexers (Channel 0 and Channel 1) with dedicated select control pins (SEL0 and SEL1) are implemented in a 20-pin TSSOP package. The signal-path inputs (D0a, D0b and D1a, D1b) accept differential signals as low as 150mV pk-pk. For applications that require common select control for both channels A & B, a common select pin (COM\_SEL) is available. All I/O pins are 100k PECL/ECL logic compatible.

AC-performance is guaranteed over the industrial -40°C to +85°C temperature range and 3.0V to 5.5V supply voltage range. This device will operate in PECL/LVPECL or ECL/LVECL mode. The 500ps max (400 typ) propagation delay is matched for all signal and logic select paths: D-to-Q<sub>OUT</sub>, SEL-to-Q<sub>OUT</sub>, and COM\_SEL-to-Q<sub>OUT</sub>. Two V<sub>BB</sub> output reference pins (approx equal to V<sub>CC</sub> -1.4V) are available for AC-coupled or single-ended applications.

The SY100EP56V is part of Micrel's high-speed, Precision Edge timing and distribution family. For applications that require a different I/O combination, consult the Micrel website at *www.micrel.com*, and choose from a comprehensive product line of high-speed, low skew fanout buffers, translators, and clock dividers.

| Micrel Semiconductor | ON Semiconductor |

|----------------------|------------------|

| SY100EP56VK4I        | MC100EP56DT      |

| SY100EP56VK4ITR      | MC100EP56DTR2    |

| Pin                    | Pin Number    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0a, /D0a<br>D0b, /D0b | 1, 2,<br>4, 5 | Channel 0 PECL/ECL differential signal inputs. Multiplexing of these two differential inputs is controlled by SEL0, or COM_SEL. The signal inputs include internal $75k\Omega$ pull-down resistors. Default condition is LOW when left floating. The input signal should be terminated externally. See " <i>Termination</i> " section                                                                                                                                                                                                                                                                                                                                                                                     |

| D1a, /D1a<br>D1b, /D1b | 6, 7<br>9, 10 | Channel 1 PECL/ECL differential signal inputs. Multiplexing of these two differential inputs is controlled by SEL1, or COM_SEL. The signal inputs include internal $75k\Omega$ pull-down resistors. Default condition is a logic LOW when left floating. The input signal should be terminated externally. See " <i>Termination</i> " section                                                                                                                                                                                                                                                                                                                                                                             |

| VBB0, VBB1             | 3, 8          | Channel 0 and Channel 1 reference output voltage. This reference is typically used to bias the unused inverting input for single-ended input applications, or as the termination point for AC– coupled differential input applications. V <sub>BB</sub> reference value is approximately V <sub>CC</sub> –1.4V, and tracks V <sub>CC</sub> 1:1. Maximum sink/source capability is 0.50mA. For single ended PECL inputs, connect to the unused input through a 50 $\Omega$ resistor. Decouple the V <sub>BB</sub> pin with a 0.01 $\mu$ F capacitor. For PECL/LVPECL inputs, the decoupling capacitor is connected to V <sub>CC</sub> , since PECL signals are referenced to V <sub>CC</sub> . Leave floating if not used. |

| VEE                    | 11            | Negative Power Supply: For PECL/LVPECL applications, connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| /Q1, Q1                | 12, 13        | Channel 1 100KEP PECL/ECL compatible differential output. PECL/ECL termination is with a 50 $\Omega$ resistor to V <sub>CC</sub> -2V. Unused output pairs may be left floating. Unused single-ended outputs must have a balanced load. For AC-coupled applications, the output stage emitter follower must have a DC current path to ground. See " <i>Termination</i> " section.                                                                                                                                                                                                                                                                                                                                          |

| SEL1, SEL0             | 15, 17        | 100KEP PECL/ECL compatible Channel 1 and Channel 0 MUX select control. See " <i>MUX Select Truth Table</i> ." Each pin includes an internal 75k $\Omega$ pull-down resistor. Default condition when left floating is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| COM_SEL                | 16            | 100KEP PECL/ECL compatible Channel 1 and Channel 0 Common MUX select control. This is the common select control pin for both Channels 0 and 1. Includes an internal 75k $\Omega$ pull-down resistor. Default condition when left floating is LOW. Leave floating when not used.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| /Q0, Q0                | 18, 19        | Channel 0 100K EP PECL/ECL compatible differential output. PECL/ECL termination is with a 50 $\Omega$ resistor to V <sub>CC</sub> -2V. Unused output pairs may be left floating. Unused single-ended outputs must have a balanced load. For AC-coupled applications, the output stage emitter follower must have a DC current path to ground. See " <i>Terminatior</i> " section.                                                                                                                                                                                                                                                                                                                                         |

| VCC                    | 14, 20        | Positive Power Supply: Both V <sub>CC</sub> pins must be connected to the same power supply externally. Bypass with $0.1\mu F/0.01\mu F$ low ESR capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SEL0 | SEL1 | COM_SEL | Q0, /Q0 | Q1, /Q1 |

|------|------|---------|---------|---------|

| Х    | Х    | н       | а       | а       |

| L    | L    | L       | b       | b       |

| L    | н    | L       | b       | а       |

| Н    | Н    | L       | а       | а       |

| Н    | L    | L       | а       | b       |

Т

| Symbol               | Ratin                                                                                              | g                                                                                           | Value                  | Unit   |  |  |

|----------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|--------|--|--|

| $V_{CC} - V_{EE}$    | Power Supply Voltage                                                                               | Power Supply Voltage                                                                        |                        |        |  |  |

| V <sub>IN</sub>      | Input Voltage ( $V_{CC} = 0V$ , $V_{IN}$ not mo<br>Input Voltage ( $V_{EE} = 0V$ , $V_{IN}$ not mo | pre negative than V <sub>EE</sub> )<br>pre positive than V <sub>CC</sub> )                  | -6.0 to 0<br>+6.0 to 0 | V<br>V |  |  |

| I <sub>OUT</sub>     | Output Current                                                                                     | –Continuous<br>–Surge                                                                       | 50<br>100              | mA     |  |  |

| I <sub>BB</sub>      | V <sub>BB</sub> Sink/Source Current <sup>(2)</sup>                                                 |                                                                                             | ±0.5                   | mA     |  |  |

| T <sub>A</sub>       | Operating Temperature Range                                                                        |                                                                                             | -40 to +85             | °C     |  |  |

| T <sub>store</sub>   | Storage Temperature Range                                                                          |                                                                                             | –65 to +150            | °C     |  |  |

| $\theta_{JA}$        | Package Thermal Resistance<br>(Junction-to-Ambient)                                                | –Still-Air (single-layer PCB)<br>–Still-Air (multi-layer PCB)<br>–500lfpm (multi-layer PCB) | 115<br>75<br>65        | °C/W   |  |  |

| $\theta^{\text{JC}}$ | Package Thermal Resistance<br>(Junction-to-Case)                                                   |                                                                                             | 21                     | °C/W   |  |  |

Note 1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

Note 2. Due to the limited drive capability, the V<sub>BB</sub> reference should only be used for inputs from the same package device (i.e., do not use for other devices).

|                 |                           | ٦    | Γ <sub>A</sub> = -40 | °C   | Т    | <sub>A</sub> = +25° | C    | Т    | T <sub>A</sub> = +85°C |      |      |                   |

|-----------------|---------------------------|------|----------------------|------|------|---------------------|------|------|------------------------|------|------|-------------------|

| Symbol          | Parameter                 | Min. | Тур.                 | Max. | Min. | Тур.                | Max. | Min. | Тур.                   | Max. | Unit | Condition         |

| V <sub>CC</sub> | Power Supply Voltage      |      |                      |      |      |                     |      |      |                        |      | V    |                   |

|                 | (PECL)                    | 4.5  | 5.0                  | 5.5  | 4.5  | 5.0                 | 5.5  | 4.5  | 5.0                    | 5.5  |      |                   |

|                 | (LVPECL)                  | 3.0  | 3.3                  | 3.8  | 3.0  | 3.3                 | 3.8  | 3.0  | 3.3                    | 3.8  |      |                   |

|                 | (ECL)                     | -5.5 | -5.0                 | -4.5 | -5.5 | -5.0                | -4.5 | -5.5 | -5.0                   | -4.5 |      |                   |

|                 | (LVECL)                   | -3.8 | -3.3                 | -3.0 | -3.8 | -3.3                | -3.0 | -3.8 | -3.3                   | -3.0 |      |                   |

| $I_{EE}$        | Supply Current            |      | 50                   | 65   |      | 50                  | 65   |      | 50                     | 65   | mA   | No Load           |

| I <sub>IH</sub> | Input HIGH Current        | _    | _                    | 150  |      | _                   | 150  | -    | _                      | 150  | μA   | $V_{IN} = V_{IH}$ |

| IIL             | Input LOW Current         |      |                      |      |      |                     |      |      |                        |      |      |                   |

| IL.             | All Inputs                | 0.5  | —                    | —    | 0.5  | —                   | —    | 0.5  | —                      | _    | μA   | $V_{IN} = V_{IL}$ |

| C <sub>IN</sub> | Input Capacitance (TSSOP) | _    | _                    | _    | _    | 1.0                 | _    | _    | _                      | _    | pF   |                   |

Note 1. 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained.

| V <sub>CC</sub> = 3.3 | V ±10%, V <sub>EE</sub> = 0V                           | _    |                     |                 |      |                     |                 |      |                     |                 |      |                                    |

|-----------------------|--------------------------------------------------------|------|---------------------|-----------------|------|---------------------|-----------------|------|---------------------|-----------------|------|------------------------------------|

|                       |                                                        | Т    | <sub>A</sub> = −40° | С               | Т    | <sub>A</sub> = +25° | С               | Т    | <sub>A</sub> = +85° | C               |      |                                    |

| Symbol                | Parameter                                              | Min. | Тур.                | Max.            | Min. | Тур.                | Max.            | Min. | Тур.                | Max.            | Unit | Condition                          |

| V <sub>IL</sub>       | Input LOW Voltage<br>(Single-Ended)                    | 1355 | —                   | 1675            | 1355 | —                   | 1675            | 1355 | _                   | 1675            | mV   |                                    |

| V <sub>IH</sub>       | Input HIGH Voltage<br>(Single-Ended)                   | 2075 | —                   | 2420            | 2075 | —                   | 2420            | 2075 | —                   | 2420            | mV   |                                    |

| V <sub>OL</sub>       | Outuput LOW Voltage                                    | 1355 | 1480                | 1605            | 1355 | 1480                | 1605            | 1355 | 1480                | 1605            | mV   | 50 $\Omega$ to V <sub>CC</sub> –2\ |

| V <sub>OH</sub>       | Output HIGH Voltage                                    | 2155 | 2280                | 2405            | 2155 | 2280                | 2405            | 2155 | 2280                | 2405            | mV   | 50 $\Omega$ to V <sub>CC</sub> –2\ |

| V <sub>BB</sub>       | Output Reference Voltage                               | 1775 | 1875                | 1975            | 1775 | 1875                | 1975            | 1775 | 1875                | 1975            | mV   |                                    |

| V <sub>IHCMR</sub>    | Input HIGH Voltage <sup>(2)</sup><br>Common Mode Range | 2.0  | _                   | V <sub>CC</sub> | 2.0  | _                   | V <sub>CC</sub> | 2.0  | _                   | V <sub>CC</sub> | V    |                                    |

Note 1. 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained. Input and output parameters are at  $V_{CC} = 3.3V$ . They vary 1:1 with  $V_{CC}$ .

Note 2. The  $V_{\text{IHCMR}}$  range is referenced to the most positive side of the differential input signal.

#### $V_{CC} = 5.0V \pm 10\%, V_{EE} = 0V$

|                    |                                                        | T <sub>A</sub> = −40°C |      |                 | ٦    | Γ <sub>A</sub> = +25 | °C              | T    | <sub>A</sub> = +85° | C               |      |                                    |

|--------------------|--------------------------------------------------------|------------------------|------|-----------------|------|----------------------|-----------------|------|---------------------|-----------------|------|------------------------------------|

| Symbol             | Parameter                                              | Min.                   | Тур. | Max.            | Min. | Тур.                 | Max.            | Min. | Тур.                | Max.            | Unit | Condition                          |

| V <sub>IL</sub>    | Input LOW Voltage<br>(Single-Ended)                    | 3055                   | -    | 3375            | 3055 | —                    | 3375            | 3055 | —                   | 3375            | mV   |                                    |

| V <sub>IH</sub>    | Input HIGH Voltage<br>(Single-Ended)                   | 3775                   |      | 4120            | 3775 | —                    | 4120            | 3775 | _                   | 4120            | mV   |                                    |

| V <sub>OL</sub>    | Outuput LOW Voltage                                    | 3055                   | 3180 | 3305            | 3055 | 3180                 | 3305            | 3055 | 3180                | 3305            | mV   | 50 $\Omega$ to V <sub>CC</sub> –2V |

| V <sub>OH</sub>    | Output HIGH Voltage                                    | 3855                   | 3980 | 4105            | 3855 | 3980                 | 4105            | 3855 | 3980                | 4105            | mV   | 50 $\Omega$ to V_CC-2V             |

| V <sub>BB</sub>    | Output Reference Voltage                               | 3475                   | 3575 | 3675            | 3475 | 3575                 | 3675            | 3475 | 3575                | 3675            | mV   |                                    |

| V <sub>IHCMR</sub> | Input HIGH Voltage <sup>(2)</sup><br>Common Mode Range | 2.0                    |      | V <sub>CC</sub> | 2.0  | _                    | V <sub>CC</sub> | 2.0  | _                   | V <sub>cc</sub> | V    |                                    |

Note 1. 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained. Input and output parameters are at  $V_{CC} = 5.0V$ . They vary 1:1 with  $V_{CC}$ .

Note 2. The  $V_{IHCMR}$  range is referenced to the most positive side of the differential input signal.

|                    | V _ | 5 5\/  | to   | 2 01/ |  |

|--------------------|-----|--------|------|-------|--|

| $V_{\rm CC} = 0V,$ |     | :-0.0V | 10 - | -3.UV |  |

|                    |                                                        | $T_A = -40^{\circ}C$ $T_A =$ |       | r <sub>A</sub> = +25 | <sub>A</sub> = +25°C |       | <sub>A</sub> = +85° | С               |       |       |      |                        |

|--------------------|--------------------------------------------------------|------------------------------|-------|----------------------|----------------------|-------|---------------------|-----------------|-------|-------|------|------------------------|

| Symbol             | Parameter                                              | Min.                         | Тур.  | Max.                 | Min.                 | Тур.  | Max.                | Min.            | Тур.  | Max.  | Unit | Condition              |

| V <sub>IL</sub>    | Input LOW Voltage                                      | -1945                        | _     | -1625                | -1945                | -     | -1625               | -1945           |       | -1625 | mV   |                        |

| V <sub>IH</sub>    | Input HIGH Voltage                                     | -1225                        | _     | -880                 | -1225                |       | -880                | -1225           |       | -880  | mV   |                        |

| V <sub>OL</sub>    | Outuput LOW Voltage                                    | -1945                        | -1820 | -1695                | -1945                | -1820 | -1695               | -1945           | -1820 | -1695 | mV   | 50 $\Omega$ to V_CC-2V |

| V <sub>OH</sub>    | Output HIGH Voltage                                    | -1145                        | -1020 | -895                 | -1145                | -1020 | -895                | -1145           | -1020 | -895  | mV   | 50 $\Omega$ to V_CC-2V |

| V <sub>BB</sub>    | Output Reference Voltage                               | -1525                        | -1425 | -1325                | -1525                | -1425 | -1325               | -1525           | -1425 | -1325 | mV   |                        |

| V <sub>IHCMR</sub> | Input HIGH Voltage <sup>(2)</sup><br>Common Mode Range | V <sub>EE</sub>              | +2.0  | 0.0                  | V <sub>EE</sub>      | +2.0  | 0.0                 | V <sub>EE</sub> | +2.0  | 0.0   | V    |                        |

Note 1. 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained.

Note 2. The V<sub>IHCMR</sub> range is referenced to the most positive side of the differential input signal.

## $\overline{V_{CC} = 0V; V_{EE} = -3.0V}$ to -5.5V or $V_{CC} = 3.0V$ to 5.5V, $V_{EE} = 0V$

|                                      |                                                                                    | T                 | <sub>A</sub> = −40° | С                 | Т                 | <sub>A</sub> = +25° | C                 | Т                 | <sub>A</sub> = +85° | C                 |                     |           |

|--------------------------------------|------------------------------------------------------------------------------------|-------------------|---------------------|-------------------|-------------------|---------------------|-------------------|-------------------|---------------------|-------------------|---------------------|-----------|

| Symbol                               | Parameter                                                                          | Min.              | Тур.                | Max.              | Min.              | Тур.                | Max.              | Min.              | Тур.                | Max.              | Unit                | Condition |

| f <sub>MAX</sub>                     | Max. Toggle Frequency <sup>(1)</sup>                                               | 3                 |                     |                   | 3                 |                     | —                 | 3                 |                     | —                 | GHz                 |           |

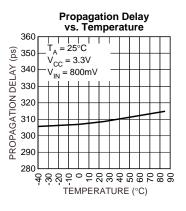

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay (Differential)<br>D to Q, /Q<br>SEL to Q, /Q<br>COM_SEL to Q, /Q | 230<br>250<br>250 | 290<br>300<br>350   | 450<br>450<br>450 | 230<br>250<br>250 | 290<br>320<br>360   | 470<br>470<br>470 | 230<br>250<br>250 | 300<br>330<br>400   | 500<br>500<br>500 | ps<br>ps<br>ps      |           |

| t <sub>SKEW</sub>                    | Within-Device Skew <sup>(2)</sup> Q, /Q                                            | _                 | 50                  | 100               | _                 | 50                  | 100               | _                 | 50                  | 100               | ps                  |           |

|                                      | Part-to-Part Skew <sup>(2)</sup>                                                   | _                 | _                   | 200               | _                 |                     | 200               |                   |                     | 200               | ps                  |           |

| t <sub>JITTER</sub>                  | Cycle-to-Cycle Jitter (rms)                                                        |                   | 0.2                 | < 1               |                   | 0.2                 | < 1               |                   | 0.2                 | < 1               | ps <sub>rms</sub>   |           |

|                                      | Random Jitter                                                                      |                   |                     | _                 |                   | <1                  | _                 | -                 | -                   | _                 | ps <sub>rms</sub>   | Note 3    |

|                                      | Deterministic Jitter<br>@1.25Gbps<br>@2.5Gbps                                      |                   | _                   |                   | _                 | <25<br><50          |                   |                   |                     |                   | ps <sub>pk-pk</sub> | Note 4    |

| V <sub>DIFF</sub>                    | Input Voltage (Differential)                                                       | 150               | 800                 | 1200              | 150               | 800                 | 1200              | 150               | 800                 | 1200              | mV                  |           |

| t <sub>r,</sub> t <sub>f</sub>       | Output Rise/Fall Time Q, /Q<br>(20% to 80%)                                        | _                 | 120                 | 170               | _                 | 130                 | 180               | —                 | 150                 | 230               | ps                  |           |

**Note 1.** Measured with 750mV input signal, 50% duty cycle. Output swing  $\geq$ 400mV. All loading with a 50 $\Omega$  to V<sub>CC</sub> –2.0V.

Note 2. Skew is measured between outputs under identical transitions. Duty cycle skew is defined only for differential operation when the delays are measured from the cross point of the inputs to the cross point of the outputs.

Note 3. RJ is measured with a K28.7 comma detect character pattern, measured at 1.25Gbps and 2.5Gbps.

Note 4. DJ is measured at 1.25Gbps and 2.5Gbps, with both K28.5 and 2<sup>23</sup>–1 PRBS pattern.

| Ordering<br>Code               | Package<br>Type | Operating<br>Range | Package<br>Marking | Ordering<br>Code                  | Pa |

|--------------------------------|-----------------|--------------------|--------------------|-----------------------------------|----|

| SY100EP56VK4C                  | K4-20-1         | Commercial         | XEP56V             | SY100EP56VK4I <sup>(2)</sup>      | K  |

| SY100EP56VK4CTR <sup>(1)</sup> | K4-20-1         | Commercial         | XEP56V             | SY100EP56VK4ITR <sup>(1, 2)</sup> | K  |

| Ordering<br>Code                  | Package<br>Type | Operating<br>Range | Package<br>Marking |

|-----------------------------------|-----------------|--------------------|--------------------|

| SY100EP56VK4I <sup>(2)</sup>      | K4-20-1         | Industrial         | XEP56V             |

| SY100EP56VK4ITR <sup>(1, 2)</sup> | K4-20-1         | Industrial         | XEP56V             |

Note 1. Tape and Reel.

Note 2. Recommended for new designs.

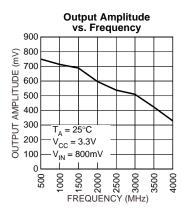

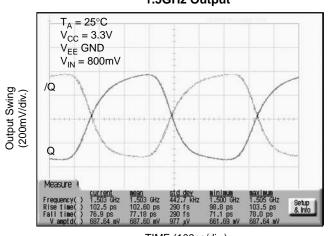

# $V_{CC} = 3.3V$ , $V_{EE} = GND$ , $T_A = 25^{\circ}C$ , unless otherwise stated.

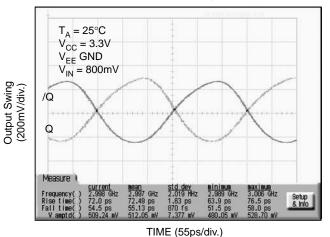

Frequency() 500.3 HHz 500

TIME (300ps/div.)

1.5GHz Output

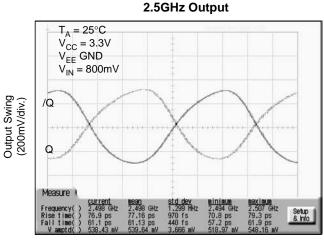

TIME (100ps/div.)

3.0GHz Output

TIME (60ps/div.)

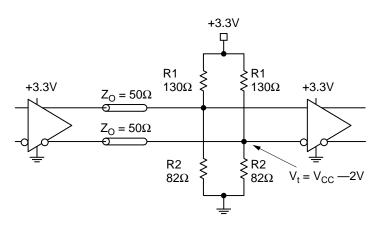

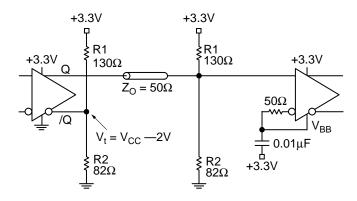

Figure 1. Parallel Termination–Thevenin Equivalent

**Note 1.** For +5.0V systems:  $R1 = 82\Omega$ ,  $R2 = 130\Omega$ .

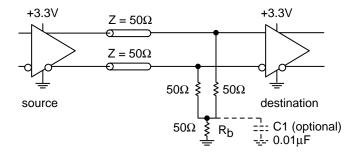

Figure 2. Three-Resistor "Y-Termination"

- **Note 1.** Power-saving alternative to Thevenin termination.

- **Note 2.** Place termination resistors as close to destination inputs as possible.

- Note 3.  $R_b$  resistor sets the DC bias voltage, equal to  $V_t$ . For +3.3V systems  $R_b = 46\Omega$  to  $50\Omega$ . For +5V systems,  $R_b = 110\Omega$ .

Figure 3. Terminating Unused I/O

- Note 1. Unused output (/Q) must be terminated to balance the output.

- Note 2. Micrel's differential I/O logic devices include a  $\rm V_{BB}$  reference pin .

- Note 3. Connect unused input through  $50\Omega$  to V<sub>BB</sub>. Bypass with a  $0.01\mu$ F capacitor to V<sub>CC</sub>, not GND, as PECL is referenced to V<sub>CC</sub>.

- Note 4. For +2.5V systems:  $R1 = 250\Omega$ ,  $R2 = 62.5\Omega$ .

#### MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.