| PMU 8000 Series PoL Regulators          |  |

|-----------------------------------------|--|

| Input 4.5-17 V, Output up to 8 A / 44 W |  |

1/28701 - BMR668 Rev. D September 2020 © Flex

### **Key Features**

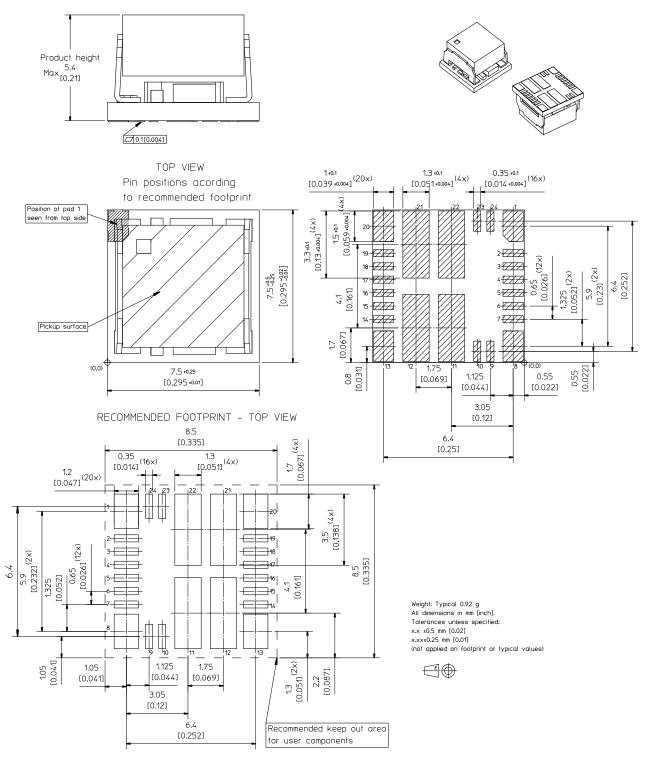

- Small size

- 7.5 x 7.5 x 5.4 mm (0.3 x 0.3 x 0.21 in)

- 0.6 V 5.5V output voltage range

- 8A maximum output current

- High efficiency, typ. 92.7% at 12 Vin, 3.3 Vout, 6A load

- Adjustable fixed switching frequency (200 kHz to 1.6 MHz)

- Control loop with fast load transient response

- Allows synchronization to an external clock

- Meets safety requirements according to IEC/EN/UL 62368-1

- MTBF 171.82 Mh

### **General Characteristics**

- Output short-circuit protection

- Over temperature protection

- Remote control

- Output voltage adjust function

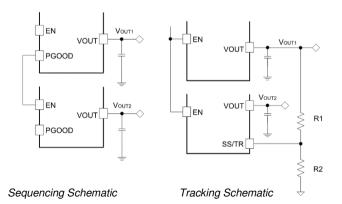

- Soft start (SS) or Tracking is configurable

- Power Good

- Highly automated manufacturing ensures quality

- ISO 9001/14001 certified supplier

### Design for Environment

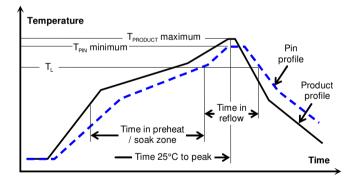

Meets requirements in hightemperature lead-free soldering processes.

### Contents

Ordering Information General Information Safety Specification Pin-out Descriptions Absolute Maximum Ratings

**Electrical Specification** 4 A / 0.6-5.5 V PMU8218......6 6 A / 0.6-5.5 V PMU8318.....11 8 A / 0.6-5.5 V PMU8418......16 **Operating Information** Thermal Consideration Mechanical Information Soldering Information **Delivery Package Information** Product Qualification Specification

| PMU 8000 Series PoL Regulators          |

|-----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W |

### **Ordering Information**

| Product number | Output           |

|----------------|------------------|

| PMU8218        | 0.6-5.5V, 4A/22W |

| PMU8318        | 0.6-5.5V, 6A/33W |

| PMU8418        | 0.6-5.5V, 8A/44W |

Product number and Packaging

| PMU8X18 n1               |        |          |            |                                |

|--------------------------|--------|----------|------------|--------------------------------|

| Options                  |        |          | <b>n</b> 1 |                                |

| Delivery package informa | tion   |          | 0          |                                |

| Options                  | Des    | cription |            |                                |

| n <sub>1</sub>           | C<br>D |          |            | 00 pcs /reel)<br>50 pcs /reel) |

Example: PMU8318 C means a surface mounted, positive logic product with tape and reel packaging, the reel capacity is 600 pcs products per reel.

# General Information Reliability

The failure rate ( $\lambda$ ) and mean time between failures (MTBF= 1/ $\lambda$ ) is calculated at max output power and an operating ambient temperature (T<sub>A</sub>) of +40°C. Flex Power uses Telcordia SR-332 Issue 4 to calculate the mean steady-state failure rate and standard deviation ( $\sigma$ ).

Telcordia SR-332 Issue 4 also provides techniques to estimate the upper confidence levels of failure rates based on the mean and standard deviation.

| Mean steady-state failure rate, $\lambda$ | Std. deviation, $\sigma$ |

|-------------------------------------------|--------------------------|

| 6 nFailures/h                             | 3.4 nFailures/h          |

MTBF (mean value) for the PMU series = 171.82 Mh. MTBF at 90% confidence level = 97.88 Mh

### Compatibility with RoHS requirements

The products are compatible with the relevant clauses and requirements of the RoHS directive 2011/65/EU and 2015/863 and have a maximum concentration value of 0.1% by weight in homogeneous materials for lead, mercury, hexavalent chromium, PBB, PBDE, DEHP, BBP, DBP, DIBP and of 0.01% by weight in homogeneous materials for cadmium.

Exemptions in the RoHS directive utilized in Flex Power products are found in the Statement of Compliance document.

Flex Power fulfills and will continuously fulfill all its obligations under regulation (EC) No 1907/2006 concerning the registration, evaluation, authorization and restriction of

| 1/28701 - BMR668 Rev. D September 2020 |   |

|----------------------------------------|---|

| © Flex                                 | 1 |

chemicals (REACH) as they enter into force and is through product materials declarations preparing for the obligations to communicate information on substances in the products.

### **Quality Statement**

The products are designed and manufactured in an industrial environment where quality systems and methods like ISO 9000, Six Sigma, and SPC are intensively in use to boost the continuous improvements strategy. Infant mortality or early failures in the products are screened out and they are subjected to an ATE-based final test. Conservative design rules, design reviews and product qualifications, plus the high competence of an engaged work force, contribute to the high quality of the products.

### Warranty

Warranty period and conditions are defined in Flex General Terms and Conditions of Sale.

### Limitation of Liability

Flex does not make any other warranties, expressed or implied including any warranty of merchantability or fitness for a particular purpose (including, but not limited to, use in life support applications, where malfunctions of product can cause injury to a person's health or life).

### © Flex 2020

The information and specifications in this technical specification is believed to be correct at the time of publication. However, no liability is accepted for inaccuracies, printing errors or for any consequences thereof. Flex reserves the right to change the contents of this technical specification at any time without prior notice.

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |  |  |  |

|-----------------------------------------|----------------------------------------|--|--|--|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |  |  |  |

### Safety Specification

### **General information**

Flex DC/DC converters and DC/DC regulators are designed in accordance with the safety standards IEC 62368-1, EN 62368-1 and UL 62368-1 *Audio/video, information and communication technology equipment -Part 1: Safety requirements*

IEC/EN/UL 62368-1 contains requirements to prevent injury or damage due to the following hazards:

- Electrical shock

- · Electrically-caused fire

- · Injury caused by hazardous substances

- Mechanically-caused injury

- Skin burn

- Radiation-caused injury

On-board DC/DC converters, Power interface modules and DC/DC regulators are defined as component power supplies. As components they cannot fully comply with the provisions of any safety requirements without "conditions of acceptability". Clearance between conductors and between conductors on the board in the final product must meet the applicable safety requirements. Certain conditions of acceptability apply for component power supplies with limited stand-off (see Mechanical Information for further information). It is the responsibility of the installer to ensure that the final product housing these components complies with the requirements of all applicable safety standards and regulations for the final product.

Component power supplies for general use shall comply with the requirements in IEC/EN/UL 62368-1. Product related standards, e.g. IEEE 802.3af *Power over Ethernet*, and ETS-300132-2 *Power interface at the input to telecom equipment, operated by direct current (dc)* are based on IEC/EN/UL 60950-1 with regards to safety.

Flex DC/DC converters, Power interface modules and DC/DC regulators are UL 62368-1 recognized and certified in accordance with EN 62368-1. The flammability rating for all construction parts of the products meet requirements for V-0 class material according to IEC 60695-11-10, *Fire hazard testing, test flames* – 50 W horizontal and vertical flame test methods.

### Non - isolated DC/DC regulators

The DC/DC regulator output is ES1 energy source if the input source meets the requirements for ES1 according to IEC/EN/UL 62368-1.

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |  |

|-----------------------------------------|----------------------------------------|--|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |  |

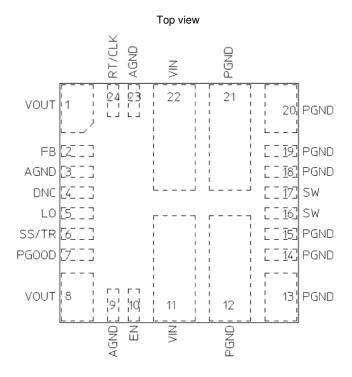

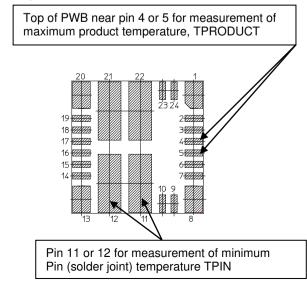

### Pin configuration and functions

# **Pin Functions**

| Pin                                                                                                                         | Designation                                                                                                                                                                                                                                          | Туре                                                                                                                | Function                                                                                                                                                                                                                                                                                          |  |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3, 9, 23                                                                                                                    | AGND                                                                                                                                                                                                                                                 | G                                                                                                                   | Analog ground, reference for logic signals. Connect these pins together using a plane but do not connect these pins to PGND. These pins are connected internally.                                                                                                                                 |  |

| 4                                                                                                                           | DNC                                                                                                                                                                                                                                                  |                                                                                                                     | Do Not Connect.                                                                                                                                                                                                                                                                                   |  |

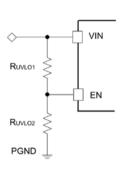

| 10                                                                                                                          | EN                                                                                                                                                                                                                                                   | Ι                                                                                                                   | Enable. Leave open or pull high to enable the device. Connect a voltage divider to implement adjustable undervoltage lockout and hysteresis. See section Undervoltage Lockout (UVLO).                                                                                                             |  |

| 2                                                                                                                           | Pagulatar foodbook input. Connect the output voltage foodbook register                                                                                                                                                                               |                                                                                                                     |                                                                                                                                                                                                                                                                                                   |  |

| 12, 13, 14, 15, 18,<br>19, 20, 21                                                                                           | PGND                                                                                                                                                                                                                                                 | G                                                                                                                   | Power ground. This is the common ground connection for VIN and VOUT power connections.                                                                                                                                                                                                            |  |

| 7                                                                                                                           | PGOOD                                                                                                                                                                                                                                                | Use a 10-k $\Omega$ to 100-k $\Omega$ pullup resistor to logic rail or other DC voltage no higher than 6.5 V.       |                                                                                                                                                                                                                                                                                                   |  |

| 24                                                                                                                          | RT/CLK         I         Switching frequency setting pin. In RT mode, an external timing resisto<br>adjusts the switching frequency. In CLK mode, the device synchronizes<br>external clock input to this pin. See sections Switching Frequency (RT) |                                                                                                                     | Switching frequency setting pin. In RT mode, an external timing resistor<br>adjusts the switching frequency. In CLK mode, the device synchronizes to an<br>external clock input to this pin. See sections Switching Frequency (RT) and<br>Synchronization (CLK).                                  |  |

| 6                                                                                                                           | SS/TR                                                                                                                                                                                                                                                | I                                                                                                                   | Soft-start and tracking pin. Connecting an external capacitor to this pin adjusts the output voltage soft start ramp slower than its 1.25-ms default setting. This pin can also be used for tracking and sequencing. See section Soft Start (SS) and Output Voltage Sequencing and Tracking (TR). |  |

| 16, 17                                                                                                                      | SW                                                                                                                                                                                                                                                   | 0                                                                                                                   | Switch node. Leave these pins open.                                                                                                                                                                                                                                                               |  |

| 5                                                                                                                           | LO                                                                                                                                                                                                                                                   | I                                                                                                                   | Loop Optimization pin. Internal loop compensation network. Connect the required Loop Optimization resistor between this pin and AGND. Do not leave this pin floating. See section Loop Optimization (LO).                                                                                         |  |

| 11, 22                                                                                                                      | VIN                                                                                                                                                                                                                                                  | I                                                                                                                   | Input voltage. Connect both pins to the input power source with a low impedance connection.                                                                                                                                                                                                       |  |

| 1, 8 VOUT O Output voltage. These pins are connected to the internal output induc<br>Connect these pins to the output load. |                                                                                                                                                                                                                                                      | Output voltage. These pins are connected to the internal output inductor.<br>Connect these pins to the output load. |                                                                                                                                                                                                                                                                                                   |  |

Technical Specification 5

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

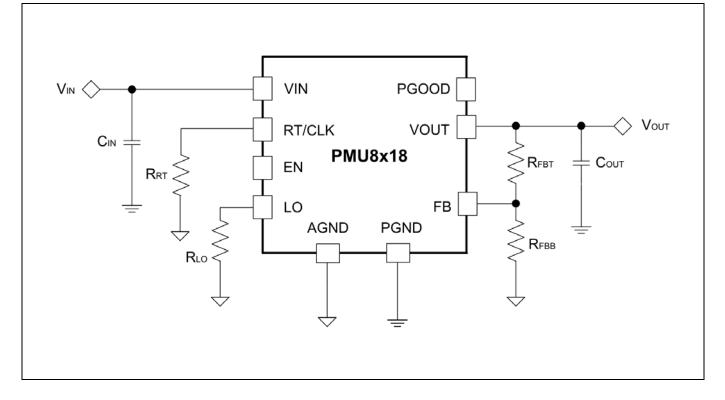

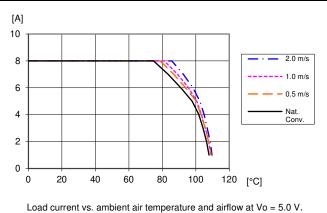

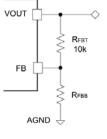

### **Typical Application Circuit**

### **Absolute Maximum Ratings**

| Characteristic   | S                             | min  | max                | Unit |

|------------------|-------------------------------|------|--------------------|------|

| T <sub>ref</sub> | Operating Temperature         | -40  | 125                | °C   |

| Ts               | Storage temperature           | -40  | 150                | °C   |

|                  | V <sub>IN</sub>               | -0.3 | 19                 | V    |

| Input Voltage    | EN, PGOOD, SS/TRK, RT/CLK, FB | -0.3 | 6.5                | V    |

|                  | AGND to PGND                  | -0.3 | 0.3                | V    |

|                  | SW                            | -1   | V <sub>IN</sub> +1 | V    |

| Output voltage   | SW (<10ns transients)         | -3   | V <sub>IN</sub> +3 | V    |

|                  | V <sub>OUT</sub>              | -0.3 | V <sub>IN</sub>    | V    |

Stress in excess of Absolute Maximum Ratings may cause permanent damage. Absolute Maximum Ratings, sometimes referred to as no destruction limits, are normally tested with one parameter at a time exceeding the limits in the Electrical Specification. If exposed to stress above these limits, function and performance may degrade in an unspecified manner.

### **Recommended Operating Conditions**

| Characteristics                        |                   | min   | typ  | max  | Unit |  |

|----------------------------------------|-------------------|-------|------|------|------|--|

| Input voltage, Note 1                  |                   | 4.5   | 12   | 17   | V    |  |

| Output voltage                         |                   | 0.6   |      | 5.5  | V    |  |

| EN voltage                             | Rising threshold  |       | 1.2  | 1.26 | V    |  |

| EN VOILAGE                             | Falling threshold | 1.1   | 1.15 |      | v    |  |

| PGOOD pullup voltage                   | ·                 | 5.5 V |      | V    |      |  |

| PGOOD sink current                     |                   |       |      | 1    | mA   |  |

| RT/CLK voltage range                   | e range 0 5.5     |       | 5.5  | V    |      |  |

|                                        | PMU8218           | 0     |      | 4    |      |  |

| Output current                         | PMU8318           | 0     |      | 6    | А    |  |

|                                        | PMU8418           | 0     |      | 8    |      |  |

| Operating temperature, T <sub>P1</sub> |                   | -40   |      | 105  | °C   |  |

Note 1. For output voltages from 0.6V to 5 V, the recommended minimum  $V_{IN}$  is 4.5 V or ( $V_{OUT}$  + 1 V), whichever is greater. For output voltages 5.0 V to 5.5 V, the recommended minimum  $V_{IN}$  is ( $V_{OUT}$  + 2 V).

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

### 1.0V, 4A / 4W Electrical Specification

$T_{P1} = -40$  to +105 °C,  $V_1 = 4.5$  to 17 V, unless otherwise specified under Conditions. Typical values given at:  $T_{P1} = +25$  °C,  $V_1 = 12$  V, max  $I_0$  unless otherwise specified under Conditions. Additional  $C_{W2} = 100$  UE Electrolytic + 2x10 UE Ceramic capacitors and  $C_{W2} = 4x47$  UE Ceramic capacit

| Charac                           | teristics                                                          | + 2x10 μF Ceramic capacitors and C <sub>OUT</sub> = 4x4<br>Conditions                 | min  | typ  | max  | Unit  |  |

|----------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|-------|--|

| Vi                               | Input voltage range                                                |                                                                                       | 4.5  | 12   | 17   | V     |  |

| Vloff                            | Turn-off input voltage                                             | Decreasing input voltage                                                              | 3.7  | 3.9  |      | V     |  |

| Vlon                             | Turn-on input voltage                                              | Increasing input voltage                                                              |      | 4.1  | 4.3  | V     |  |

| Cı                               | Internal input capacitance                                         |                                                                                       |      | 2    |      | μF    |  |

| Po                               | Output power                                                       |                                                                                       | 0    |      | 4.0  | W     |  |

| n                                | Efficiency                                                         | $V_1 = 12 V, 50 \%$ of max $I_0$                                                      |      | 87.6 |      | 0/    |  |

| η                                | Linciency                                                          | $V_1 = 12 V$ , max $I_0$                                                              |      | 88.5 |      | %     |  |

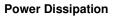

| Pd                               | Power Dissipation                                                  | $V_{\rm I}$ = 12 V, 50 % of max $I_{\rm O}$                                           |      | 0.28 |      | W     |  |

| I d                              |                                                                    | $V_1 = 12 V$ , max $I_0$                                                              |      | 0.52 |      | W     |  |

| Pli                              | Input idling power                                                 | V <sub>1</sub> = 12 V                                                                 |      | 0.17 |      | W     |  |

| P <sub>RC</sub>                  | Input standby power                                                | V <sub>1</sub> = 12 V                                                                 |      | 20   |      | mW    |  |

| f <sub>s</sub>                   | Switching frequency                                                | 10-100 % of max I <sub>0</sub>                                                        |      | 350  |      | kHz   |  |

| V <sub>Oi</sub>                  | Output voltage initial setti accuracy                              | ng and $V_1 = 12 V$ , max $I_0$                                                       |      | 1.0  |      | V     |  |

| Vo                               | Output voltage tolerance                                           | band 10-100 % of max Io                                                               |      | ±1.5 |      | %     |  |

|                                  | Idling voltage                                                     | $V_1 = 12 V$ , $I_0 = min I_0$                                                        | 1.0  |      |      | V     |  |

|                                  | Line regulation                                                    | I <sub>O</sub> = max lo                                                               |      | ±0.1 |      | mV    |  |

|                                  | Load regulation                                                    | V <sub>I</sub> = 12 V, 0-100 % of max I <sub>O</sub>                                  | ±0.9 |      |      | mV    |  |

| V <sub>tr</sub>                  | Load transient voltage deviation                                   | V <sub>I</sub> = 12 V, Load step 25-75-25 % of<br>max I <sub>0</sub> , di/dt = 2 A/µs | ±29  |      |      | mV    |  |

| t <sub>tr</sub>                  | Load transient recovery ti                                         | Mith Loop Optimization<br>C <sub>OUT</sub> = 518 μF; $R_{LO}$ = 3 kΩ                  |      | 37   |      | μS    |  |

| tr                               | Ramp-up time<br>(from 10-90 % of V <sub>o</sub> )                  | V <sub>I</sub> = 12 V, 100 % of max I <sub>O</sub>                                    |      | 1.1  |      | ms    |  |

| ts                               | Start-up time<br>(from V <sub>I</sub> connection to 90 % c         |                                                                                       |      | 1.6  |      | ms    |  |

|                                  | V <sub>I</sub> shut-down<br>fall time.                             | l <sub>o</sub> = max lo                                                               |      | 12.8 |      | ms    |  |

| t <sub>f</sub>                   | (from V <sub>1</sub> off to 10<br>% of V <sub>0</sub> ) $V_1 = 12$ | I <sub>o</sub> = min Io                                                               |      | 1.0  |      | S     |  |

|                                  | RC start-up time                                                   | $V_I = 12 V$ , max $I_O$                                                              |      | 1.5  |      | ms    |  |

| t <sub>RC</sub> t <sub>Inh</sub> | RC shut-down<br>fall time $V_1 = 12$                               | l <sub>o</sub> = max lo                                                               |      | 120  |      | μs    |  |

|                                  | (from RC off to 10 % of $V_0$ )                                    | I <sub>O</sub> = min Io                                                               |      | 1.2  |      | s     |  |

| lo                               | Output current                                                     |                                                                                       | 0    |      | 4    | А     |  |

| l <sub>lim</sub>                 | Current limit threshold                                            |                                                                                       |      | 11.7 |      | А     |  |

| l <sub>sc</sub>                  | Short circuit current                                              | RMS, 12 mΩ short                                                                      | 2.3  |      | А    |       |  |

| Cin                              | External input capacitance                                         | Ceramic type                                                                          | 20   |      |      | μF    |  |

| <b>C</b> in                      |                                                                    | Non-ceramic type, Note 2                                                              |      | 100  |      |       |  |

| C <sub>out</sub>                 | External output capacitan                                          | ce Note 3                                                                             | 188  |      | 1500 | μF    |  |

| V <sub>Oac</sub>                 | Output ripple & noise V <sub>I</sub> =                             | 12 V I <sub>o</sub> = max Io                                                          |      | 8.5  |      | mVp-p |  |

Note 2. For Non-ceramic type of external input capacitor, a 100 µF bulk capacitor is recommended for application with transient load requirement. An OS-CON capacitor is recommended when adding the bulk capacitor in low temperature. Note 3. A minimum external output ceramic capacitance is required. In low output voltage, more capacitance might to be added considering capacitance derating. The

maximum external output capacitor could only be ceramic type or combination of ceramic and a single non-ceramic type.

6

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

0.2

0.0

0

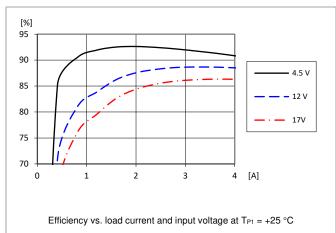

### 1.0V, 4A / 4W Typical Characteristics

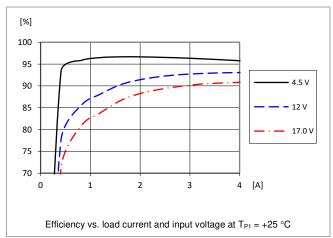

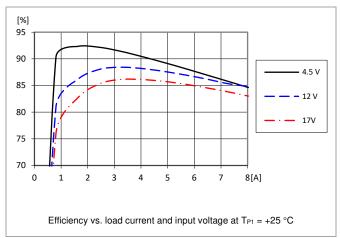

### Efficiency

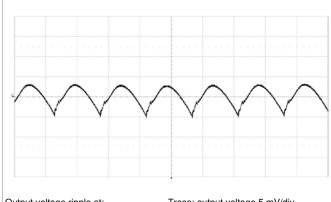

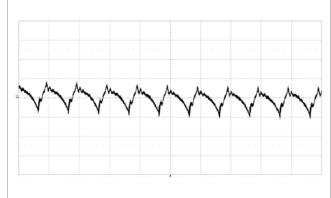

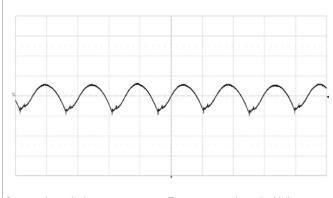

### **Output Ripple & Noise**

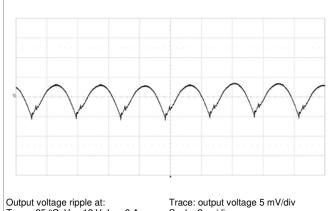

Output voltage ripple at:  $T_{P1} = +25 \text{ °C}, V_I = 12 \text{ V}, I_O = 4 \text{ A}$  $C_{OUT} = 4X47 \ \mu\text{F}$  Ceramic

Trace: output voltage 5 mV/div Scale: 2  $\mu s/div$  20 MHz bandwidth

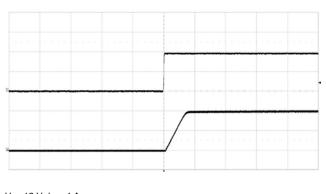

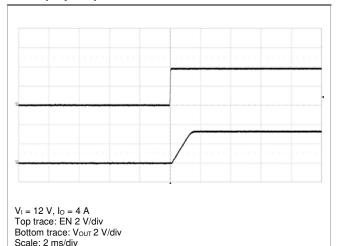

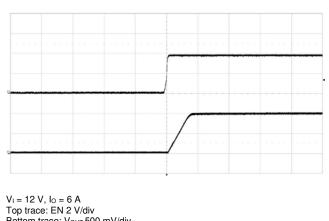

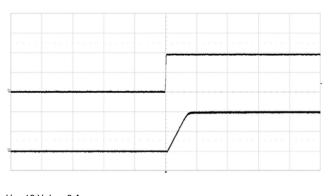

### Start up by EN pin

$\begin{array}{l} V_{i}=12 \; V, \; I_{O}=4 \; A \\ Top \; trace: \; EN \; 2 \; V/div \\ Bottom \; trace: \; V_{OUT} \; 500 \; mV/div \\ Scale: \; 2 \; ms/div \end{array}$

1

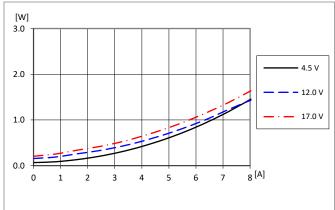

Dissipated power vs. load current and input voltage at  $T_{\text{P1}}$  = +25  $^{\circ}\text{C}$

3

4 [A]

2

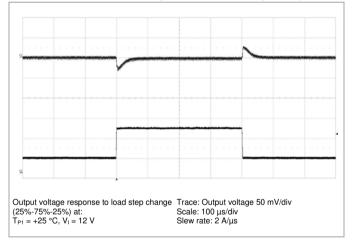

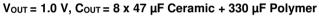

### **Transient Response**

Output voltage response to load step change (25%-75%-25%) at: T<sub>P1</sub> = +25 °C, V<sub>I</sub> = 12 V, I<sub>O</sub> = 4 A Courr = 4x47  $\mu$ F Ceramic + 330  $\mu$ F Polymer Trace: output voltage 50 mV/div Scale: 100 µs/div Slew rate: 2A/µs 20 MHz bandwidth

### Shut down by EN pin

Bottom trace: V<sub>OUT</sub> 500 mV/div Scale: 200 µs/div

### 7

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

### 3.3V, 4A / 13.2W Electrical Specification

### PMU8218

$\begin{array}{l} T_{P1}=-40 \ to \ +105 \ ^{o}C, \ V_{I}=4.5 \ to \ 17 \ V, \ unless \ otherwise \ specified \ under \ Conditions. \\ Typical \ values \ given \ at: \ T_{P1}=+25 \ ^{o}C, \ V_{I}=12 \ V, \ max \ I_{O}, \ unless \ otherwise \ specified \ under \ Conditions. \\ Additional \ C_{IN}=100 \ \mu F \ Electrolytic \ + \ 2x10 \ \mu F \ Ceramic \ capacitors \ and \ C_{OUT}=4x47 \ \mu F \ Ceramic \ capacitors. \end{array}$

| Charao           | cteristics                                            |                                 | Conditions                                                                | min                     | typ  | max  | Unit  |

|------------------|-------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------|-------------------------|------|------|-------|

| Vi               | Input voltage rar                                     | ige                             |                                                                           | 4.5                     | 12   | 17   | V     |

| Vloff            | Turn-off input vo                                     | Itage                           | Decreasing input voltage                                                  | 3.7                     | 3.9  |      | V     |

| Vlon             | Turn-on input vo                                      | Itage                           | Increasing input voltage                                                  |                         | 4.1  | 4.3  | V     |

| Cı               | Internal input ca                                     | pacitance                       |                                                                           |                         | 2    |      | μF    |

| Po               | Output power                                          |                                 |                                                                           | 0                       |      | 13.2 | W     |

|                  | Efficiency                                            |                                 | $V_{I} = 12 \text{ V}, 50 \% \text{ of max } I_{O}$                       |                         | 91.4 |      | 0(    |

| η                |                                                       |                                 | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                |                         | 93.1 |      | %     |

| _                |                                                       |                                 | $V_{I} = 12 \text{ V}, 50 \% \text{ of max } I_{O}$                       |                         | 0.62 |      | W     |

| о <sub>d</sub>   | Power Dissipation                                     | on                              | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                |                         | 1.0  |      | W     |

| D <sub>li</sub>  | Input idling powe                                     | er                              | V <sub>1</sub> = 12 V                                                     |                         | 0.4  |      | W     |

| • <sub>RC</sub>  | Input standby po                                      | ower                            | V <sub>1</sub> = 12 V                                                     |                         | 20   |      | mW    |

| s                | Switching freque                                      | ency                            | 0-100 % of max I <sub>0</sub>                                             |                         | 1.0  |      | MHz   |

| V <sub>Oi</sub>  | Output voltage ir accuracy                            | nitial setting and              | V <sub>1</sub> = 12 V, max I <sub>0</sub>                                 |                         | 3.31 |      | V     |

|                  | Output voltage to                                     | olerance band                   | 10-100 % of max I <sub>0</sub>                                            |                         | ±1.5 |      | %     |

| Vo               | Idling voltage                                        |                                 | $V_{I} = 12 V, I_{O} = min I_{O}$                                         |                         | 3.31 |      | V     |

|                  | Line regulation                                       |                                 | $I_0 = \max I_0$                                                          |                         | ±0.4 |      | mV    |

|                  | Load regulation                                       |                                 | $V_{I} = 12 V, 0-100 \% \text{ of max } I_{O}$                            |                         | ±1.6 |      | mV    |

| / <sub>tr</sub>  | Load transient voltage deviation                      |                                 | $V_1$ = 12 V, Load step 25-75-25 % of max I <sub>o</sub> , di/dt = 2 A/µs |                         | ±40  |      | mV    |

| tr               | Load transient re                                     | ecovery time                    | With Loop Optimization<br>C <sub>OUT</sub> = 518 μF; RLo = 11 k           |                         | 80   |      | μS    |

| t <sub>r</sub>   | Ramp-up time<br>(from 10-90 % of                      | V <sub>o</sub> )                | V <sub>1</sub> = 12 V, 100 % of max I <sub>0</sub>                        |                         | 1.1  |      | ms    |

| ts               | Start-up time<br>(from V <sub>1</sub> connectio       | in to 90 % of $V_{\rm O}$ )     |                                                                           |                         | 1.7  |      | ms    |

|                  | V <sub>I</sub> shut-down                              |                                 | I <sub>o</sub> = max lo                                                   |                         | 8.2  |      | ms    |

| t <sub>f</sub>   | fall time.<br>(from $V_I$ off to<br>10 % of $V_O$ )   | V <sub>1</sub> = 12 V           | I <sub>o</sub> = min Io                                                   |                         | 0.13 |      | S     |

|                  | RC start-up time                                      |                                 | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                |                         | 1.4  |      | ms    |

| RC <b>t</b> Inh  | RC shut-down                                          | e $V_1 = 12 V$ $I_0 = \min I_0$ | I <sub>o</sub> = max lo                                                   |                         | 0.36 |      | ms    |

| LRC Linh         | fall time (from RC off to $10 \%$ of V <sub>O</sub> ) |                                 | n RC off to $V_1 = 12 V$ $I_0 = \min I_0$                                 | I <sub>o</sub> = min lo |      | 1.3  |       |

| D                | Output current                                        |                                 |                                                                           | 0                       |      | 4    | Α     |

| im               | Current limit threshold                               |                                 |                                                                           |                         | 11.7 |      | Α     |

| sc               | Short circuit curr                                    | ent                             | RMS, 12 mΩ short                                                          |                         | 2.35 |      | Α     |

| Cin              | External input ca                                     | apacitance                      | Ceramic type                                                              | 20                      |      |      | μF    |

|                  |                                                       |                                 | Non-ceramic type, Note 2                                                  | 47                      | 100  | 4500 | _     |

| C <sub>out</sub> | External output of                                    | •                               | Note 3                                                                    | 47                      |      | 1500 | μF    |

| / <sub>Oac</sub> | Output ripple & r                                     | noise V <sub>I</sub> = 12 V     | $I_0 = \max I_0$                                                          |                         | 3.9  |      | mVp-p |

Note 2. For Non-ceramic type of external input capacitor, a 100  $\mu$ F bulk capacitor is recommended for application with transient load requirement. An OS-CON capacitor is recommended when adding the bulk capacitor in low temperature.

Note 3. A minimum external output ceramic capacitance is required. In low output voltage, more capacitance might to be added considering capacitance derating. The maximum external output capacitor could only be ceramic type or combination of ceramic and a single non-ceramic type.

8

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

### 3.3V, 4A / 13.2W Typical Characteristics

### Efficiency

### **Output Ripple & Noise**

Output voltage ripple at:  $T_{P1} = +25 \text{ °C}, V_1 = 12 \text{ V}, I_0 = 4 \text{ A}$  $C_{OUT} = 4X47 \mu F \text{ Ceramic}$

Trace: output voltage 2 mV/div Scale: 1 µs/div 20MHz bandwidth

### Start up by EN pin

Dissipated power vs. load current and input voltage at  $T_{\text{P1}}$  = +25  $^{\circ}\text{C}$

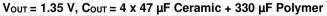

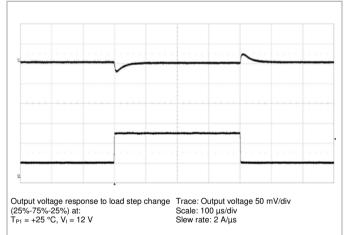

### **Transient Response**

Output voltage response to load step change (25%-75%-25%) at: T\_P1 = +25 °C, V\_I = 12 V, I\_0 = 4 A C\_{OUT} = 4x47 \,\mu\text{F} Ceramic + 330  $\mu\text{F}$  Polymer

Trace: output voltage 50 mV/div Scale: 100  $\mu s/div,$  Slew rate: 2 A/ $\mu s$  20MHz bandwidth

### Shut down by EN pin

9

# flex

### **Technical Specification** 10

| PMU 8000 Series PoL Regulators          |  |

|-----------------------------------------|--|

| Input 4.5-17 V, Output up to 8 A / 44 W |  |

1/28701 - BMR668 Rev. D September 2020 © Flex

**PMU 8218**

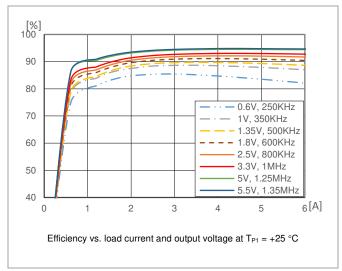

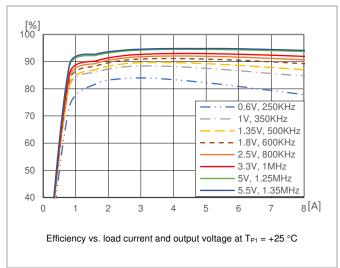

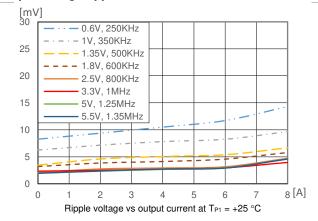

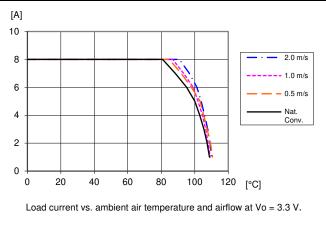

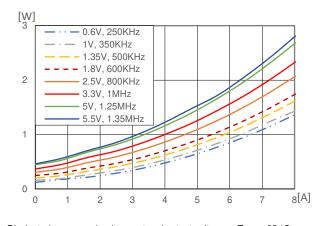

## Typical Characteristics (V<sub>IN</sub> = 12V)

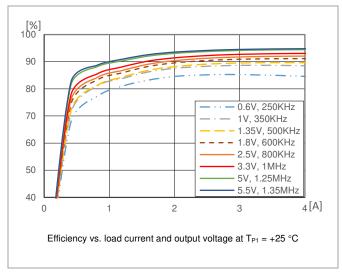

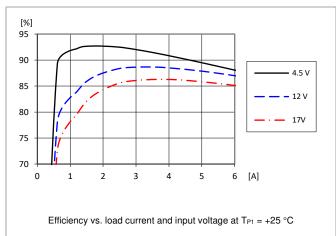

### Efficiency

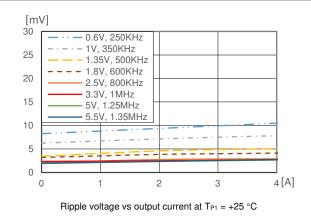

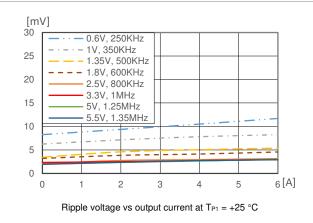

### **Output voltage ripple**

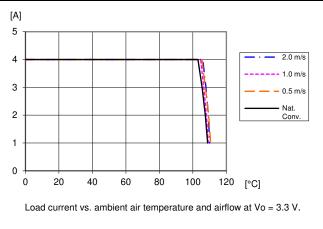

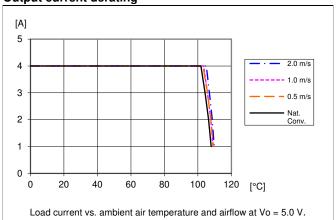

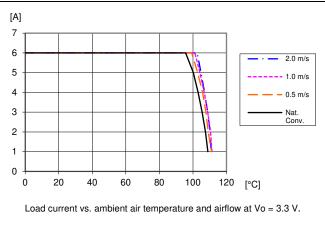

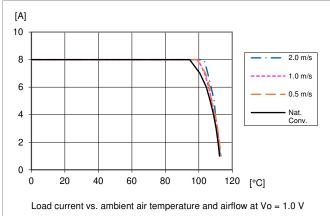

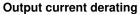

### **Output current derating**

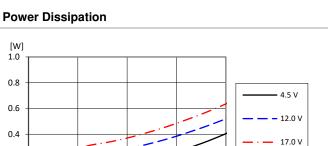

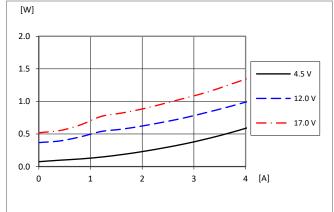

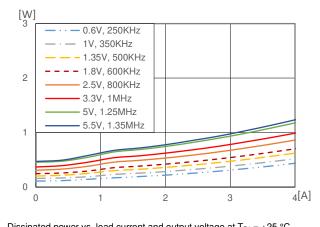

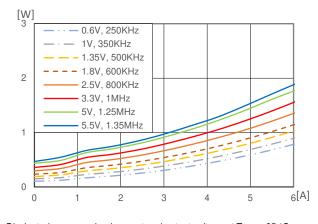

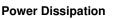

### **Power Dissipation**

Dissipated power vs. load current and output voltage at  $T_{P1}$  = +25 °C

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

### 1.0V, 6A / 6W Electrical Specification

$T_{P1} = -40$  to +105 °C,  $V_1 = 4.5$  to 17 V, unless otherwise specified under Conditions. Typical values given at:  $T_{P1} = +25$  °C,  $V_1 = 12$  V, max  $I_0$  unless otherwise specified under Conditions. Additional  $C_{W2} = 100$  UE Electrolytic + 2x10 UE Ceramic capacitors and  $C_{W2} = 4x47$  UE Ceramic capacit

| Charac                           | teristics                                          |                            | Conditions                                                                         | min   | typ  | max  | Unit  |

|----------------------------------|----------------------------------------------------|----------------------------|------------------------------------------------------------------------------------|-------|------|------|-------|

| Vi                               | Input voltage range                                |                            |                                                                                    | 4.5   | 12   | 17   | V     |

| Vloff                            | Turn-off input volta                               | age                        | Decreasing input voltage                                                           | 3.7   | 3.9  |      | V     |

| V <sub>Ion</sub>                 | Turn-on input volta                                | age                        | Increasing input voltage                                                           |       | 4.1  | 4.3  | V     |

| Cı                               | Internal input capa                                | acitance                   |                                                                                    |       | 2    |      | μF    |

| <b>&gt;</b> 0                    | Output power                                       |                            |                                                                                    | 0     |      | 6.0  | W     |

| 2                                | Efficiency                                         |                            | $V_{I} = 12 \text{ V}, 50 \% \text{ of max } I_{O}$                                |       | 88.6 |      | 0/    |

| η                                |                                                    |                            | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                         |       | 87.0 |      | ~ %   |

| ⊃ <sub>d</sub>                   | Power Dissipation                                  |                            | $V_{\rm I}$ = 12 V, 50 % of max $I_{\rm O}$                                        |       | 0.40 |      | W     |

| d                                | Power Dissipation                                  |                            | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                         |       | 0.90 |      | W     |

| ⊃ <sub>li</sub>                  | Input idling power                                 |                            | V <sub>1</sub> = 12 V                                                              |       | 0.17 |      | W     |

| ⊃ <sub>RC</sub>                  | Input standby pow                                  | ver                        | V <sub>1</sub> = 12 V                                                              |       | 20   |      | mW    |

| s<br>S                           | Switching frequent                                 | су                         | 10-100 % of max I <sub>0</sub>                                                     |       | 350  |      | kHz   |

| V <sub>Oi</sub>                  | Output voltage init accuracy                       | ial setting and            | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                         |       | 1.0  |      | V     |

| Vo                               | Output voltage tole                                | erance band                | 10-100 % of max I <sub>o</sub>                                                     |       | ±1.5 |      | %     |

|                                  | Idling voltage                                     |                            | $V_1 = 12 V, I_0 = min I_0$                                                        | 1.0   |      |      | V     |

|                                  | Line regulation                                    |                            | $I_0 = \max I_0$                                                                   | ±0.14 |      |      | mV    |

|                                  | Load regulation                                    |                            | $V_1 = 12 V, 0-100 \% \text{ of max } I_0$                                         | ±1.6  |      |      | mV    |

| V <sub>tr</sub>                  | Load transient<br>voltage deviation                |                            | V <sub>1</sub> = 12 V, Load step 25-75-25 % of max I <sub>0</sub> , di/dt = 2 A/µs | ±39   |      |      | mV    |

| tr                               | Load transient rec                                 | overy time                 | With Loop Optimization<br>$C_{OUT} = 518 \ \mu\text{F}; R_{LO} = 3 \ k\Omega$      |       | 40   |      | μS    |

| ·r                               | Ramp-up time<br>(from 10-90 % of Vo                | )                          | V <sub>1</sub> = 12 V, 100 % of max I <sub>0</sub>                                 |       | 1.1  |      | ms    |

| s                                | Start-up time<br>(from V <sub>I</sub> connection t | o 90 % of V <sub>0</sub> ) | $v_1 = 12 v_1 + 100 / 6 01 max 10$                                                 |       | 1.6  |      | ms    |

| t <sub>f</sub>                   | V <sub>I</sub> shut-down fall time.                | V <sub>I</sub> = 12 V      | I <sub>O</sub> = max lo                                                            |       | 9.8  |      | ms    |

| L <sup>†</sup>                   | (from $V_l$ off to 10 % of $V_0$ )                 | V  - 12 V                  | l <sub>o</sub> = min lo                                                            |       | 1.0  |      | s     |

|                                  | RC start-up time                                   |                            | $V_{I} = 12 V$ , max $I_{O}$                                                       |       | 1.5  |      | ms    |

| t <sub>RC</sub> t <sub>Inh</sub> | RC shut-down<br>fall time                          | V <sub>I</sub> = 12 V      | I <sub>o</sub> = max lo                                                            |       | 75.3 |      | μs    |

|                                  | (from RC off to 10 % of $V_0$ )                    | .,                         | I <sub>o</sub> = min lo                                                            |       | 1.2  |      | s     |

| 0                                | Output current                                     |                            |                                                                                    | 0     |      | 6    | A     |

| lim                              | Current limit threshold                            |                            |                                                                                    |       | 11.7 |      | Α     |

| SC                               | Short circuit currer                               | nt                         | RMS, 12 mΩ short                                                                   |       | 2.3  |      | A     |

| Cin                              | External input cap                                 | acitance                   | Ceramic type                                                                       | 20    |      |      | μF    |

| - 111                            |                                                    |                            | Non-ceramic type, Note 2                                                           |       | 100  |      | ·'4   |

| Cout                             | External output ca                                 | pacitance                  | Note 3                                                                             | 188   |      | 1500 | μF    |

| V <sub>Oac</sub>                 | Output ripple & no                                 | ise V <sub>I</sub> = 12 V  | I <sub>O</sub> = max lo                                                            |       | 8.25 |      | mVp-p |

Note 2. For Non-ceramic type of external input capacitor, a 100 µF bulk capacitor is recommended for application with transient load requirement. An OS-CON capacitor is recommended when adding the bulk capacitor in low temperature. Note 3. A minimum external output ceramic capacitance is required. In low output voltage, more capacitance might to be added considering capacitance derating. The

maximum external output capacitor could only be ceramic type or combination of ceramic and a single non-ceramic type.

11

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |  |  |

|-----------------------------------------|----------------------------------------|--|--|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |  |  |

### 1.0V,6A / 6W Typical Characteristics

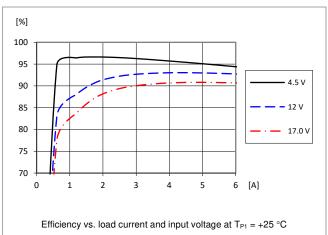

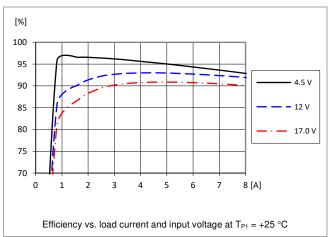

### Efficiency

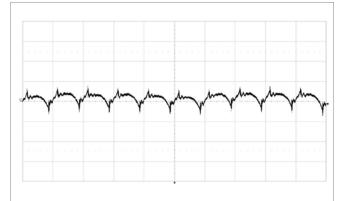

### **Output Ripple & Noise**

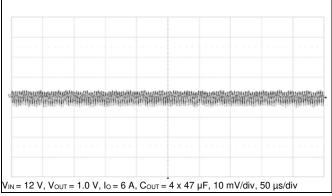

Output voltage ripple at:  $T_{P1} = +25 \text{ °C}, V_I = 12 \text{ V}, I_O = 6 \text{ A}$   $C_{OUT} = 4X47 \ \mu\text{F}$  Ceramic

Trace: output voltage 5 mV/div Scale: 2 µs/div 20 MHz bandwidth

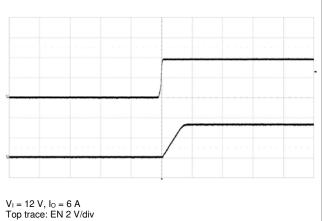

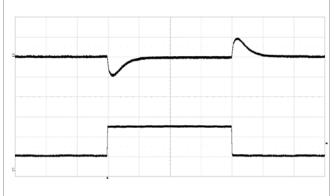

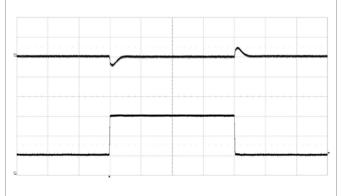

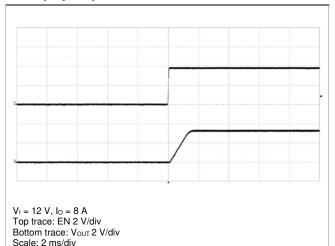

### Start up by EN pin

Top trace: EN 2 V/div Bottom trace: V<sub>OUT</sub> 500 mV/div Scale: 2 ms/div

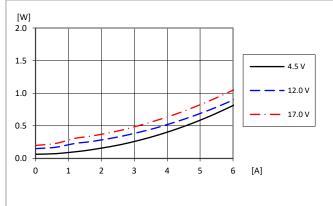

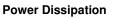

### **Power Dissipation**

Dissipated power vs. load current and input voltage at  $T_{P1}$  = +25 °C

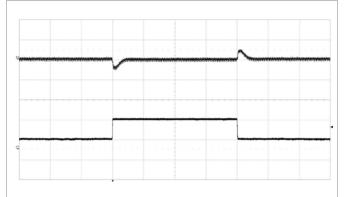

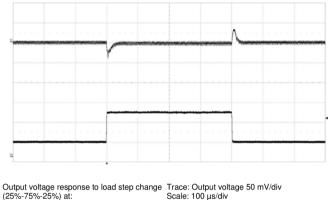

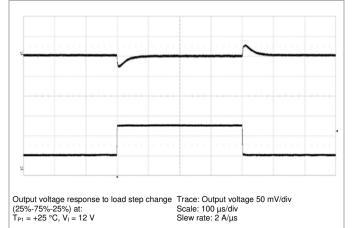

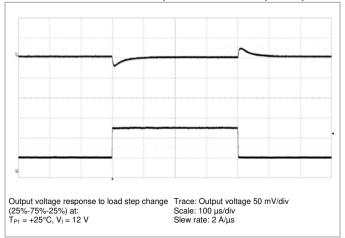

### **Transient Response**

Output voltage response to load step change (25%-75%-25%) at:  $T_{P1} = +25$  °C,  $V_1 = 12$  V,  $I_0 = 6$  A  $C_{OUT} = 4x47$  µF Ceramic + 330 µF Polymer

Trace: output voltage 50 mV/div Scale: 100 µs/div Slew rate: 2A/µs 20 MHz bandwidth

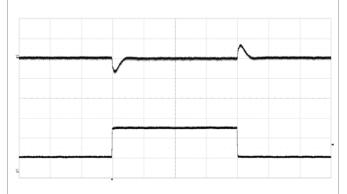

### Shut down by EN pin

### 12

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |

|-----------------------------------------|----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |

### 3.3V, 6A / 19.8W Electrical Specification

### **PMU8318**

$T_{P1}$  = -40 to +105 °C,  $V_1$  = 4.5 to 17 V, unless otherwise specified under Conditions. Typical values given at:  $T_{P1}$  = +25 °C,  $V_1$  = 12 V, max  $I_0$ , unless otherwise specified under Conditions. Additional  $C_{IN}$  = 100 µF Electrolytic + 2x10 µF Ceramic capacitors and  $C_{OUT}$  = 4x47 µF Ceramic capacitors

| Characteristics                |                                                                       |                          | Conditions                                                                  | min   | typ  | max  | Unit  |

|--------------------------------|-----------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------|-------|------|------|-------|

| Vi                             | Input voltage range                                                   |                          |                                                                             | 4.5   | 12   | 17   | V     |

| Vloff                          | Turn-off input voltag                                                 | е                        | Decreasing input voltage                                                    | 3.7   | 3.9  |      | V     |

| Vlon                           | Turn-on input voltag                                                  | е                        | Increasing input voltage                                                    |       | 4.1  | 4.3  | V     |

| Cı                             | Internal input capaci                                                 | tance                    |                                                                             |       | 2    |      | μF    |

| Po                             | Output power                                                          |                          |                                                                             | 0     |      | 19.8 | W     |

|                                | Efficiency                                                            |                          | $V_1 = 12 V$ , 50 % of max $I_0$                                            |       | 92.7 |      |       |

| η                              |                                                                       |                          | $V_1 = 12 V$ , max $I_0$                                                    |       | 92.7 |      | %     |

| _                              |                                                                       |                          | $V_1 = 12 V$ , 50 % of max $I_0$                                            |       | 0.80 |      | W     |

| P <sub>d</sub>                 | Power Dissipation                                                     |                          | $V_1 = 12 V$ , max $I_0$                                                    |       | 1.56 |      | W     |

| р <sub>li</sub>                | Input idling power                                                    |                          | V <sub>1</sub> = 12 V                                                       |       | 0.4  |      | W     |

| • <sub>RC</sub>                | Input standby power                                                   | ·                        | V <sub>1</sub> = 12 V                                                       |       | 20   |      | mW    |

| s                              | Switching frequency                                                   | ,                        | 0-100 % of max I <sub>0</sub>                                               |       | 1.0  |      | MHz   |

| V <sub>Oi</sub>                | Output voltage initial setting and accuracy                           |                          | V <sub>I</sub> = 12 V, max I <sub>O</sub>                                   |       | 3.31 |      | V     |

|                                | Output voltage tolera                                                 | ance band                | 10-100 % of max I <sub>0</sub>                                              |       | ±1.5 |      | %     |

|                                | Idling voltage                                                        |                          | $V_1 = 12 V$ , $I_0 = min I_0$                                              |       | 3.31 |      | V     |

| / <sub>0</sub>                 | Line regulation                                                       |                          | $I_0 = \max I_0$                                                            | ±0.58 |      |      | mV    |

|                                | Load regulation                                                       |                          | $V_{I}$ = 12 V, 0-100 % of max $I_{O}$                                      | ±1.26 |      |      | mV    |

| <b>V</b> <sub>tr</sub>         | Load transient voltage deviation                                      |                          | $V_1$ = 12 V, Load step 25-75-25 % of max I <sub>0</sub> , di/dt = 2 A/µs   |       | ±50  |      | mV    |

| tr                             | Load transient recov                                                  | very time                | With Loop Optimization<br>C <sub>OUT</sub> = 518 μF; R <sub>LO</sub> = 11 k |       | 100  |      | μS    |

| t <sub>r</sub>                 | Ramp-up time<br>(from 10-90 % of V <sub>O</sub> )                     |                          | V <sub>1</sub> = 12 V, 100 % of max I <sub>0</sub>                          |       | 1.1  |      | ms    |

| ts                             | Start-up time<br>(from V <sub>1</sub> connection to                   | 90 % of V <sub>0</sub> ) | v1= 12 v, 100 % of maxing                                                   |       | 1.7  |      | ms    |

|                                | V <sub>I</sub> shut-down                                              |                          | I <sub>o</sub> = max lo                                                     |       | 7.4  |      | ms    |

| t <sub>f</sub>                 | fall time.<br>(from V <sub>1</sub> off to<br>10 % of V <sub>0</sub> ) | = 12 V                   | I <sub>O</sub> = min Io                                                     |       | 0.13 |      | S     |

|                                | RC start-up time                                                      |                          | $V_1 = 12 \text{ V}, \text{ max } I_0$                                      |       | 1.4  |      | ms    |

| <sub>RC</sub> t <sub>Inh</sub> | RC shut-down                                                          |                          | I <sub>O</sub> = max lo                                                     |       | 0.36 |      | ms    |

| trc unn                        | fall time<br>(from RC off to<br>10 % of V <sub>0</sub> )              | = 12 V                   | I <sub>O</sub> = min lo                                                     |       | 1.3  |      | s     |

| 0                              | Output current                                                        |                          |                                                                             | 0     |      | 6    | Α     |

| im                             | Current limit threshold                                               |                          |                                                                             |       | 11.7 |      | А     |

| SC                             | Short circuit current                                                 |                          | RMS, 12 mΩ short                                                            |       | 2.35 |      | Α     |

| Cin                            | External input capac                                                  | citance                  | Ceramic type<br>Non-ceramic type, Note 2                                    | 20    | 100  |      | – μF  |

| Cout                           | External output capacitance                                           |                          | Note 3                                                                      | 47    |      | 1500 | μF    |

| V <sub>Oac</sub>               | Output ripple & nois                                                  |                          | $I_0 = \max I_0$                                                            |       | 2.96 |      | mVp-p |

Note 2. For Non-ceramic type of external input capacitor, a 100 µF bulk capacitor is recommended for application with transient load requirement. An OS-CON capacitor is recommended when adding the bulk capacitor in low temperature.

Note 3. A minimum external output ceramic capacitance is required. In low output voltage, more capacitance might to be added considering capacitance derating. The maximum external output capacitor could only be ceramic type or combination of ceramic and a single non-ceramic type.

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |  |  |

|-----------------------------------------|----------------------------------------|--|--|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |  |  |

### 3.3V, 6A / 19.8W Typical Characteristics

### Efficiency

### **Output Ripple & Noise**

Output voltage ripple at:  $T_{P1} = +25 \text{ °C}, V_I = 12 \text{ V}, I_O = 6 \text{ A}$   $C_{OUT} = 4X47 \ \mu\text{F}$  Ceramic

Trace: output voltage 2 mV/div Scale: 1 µs/div 20MHz bandwidth

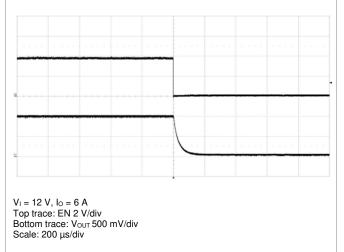

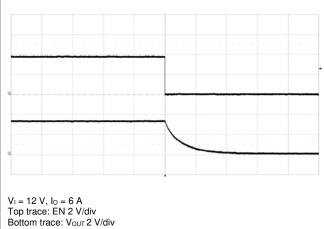

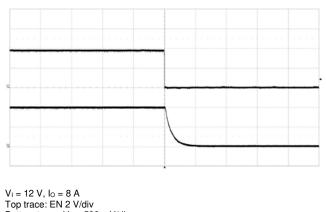

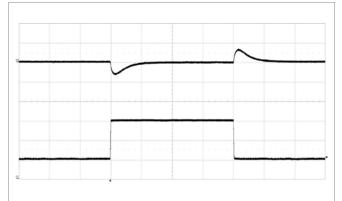

### Start up by EN pin

Bottom trace: Vout 2 V/div Scale: 2 ms/div

Dissipated power vs. load current and input voltage at  $T_{P1}$  = +25 °C

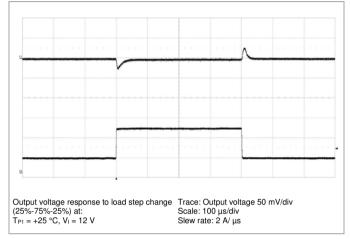

### **Transient Response**

Output voltage response to load step change (25%-75%-25%) at: T<sub>P1</sub> = +25 °C, V<sub>I</sub> = 12 V, I<sub>0</sub> = 6 A C<sub>OUT</sub> = 4x47  $\mu$ F Ceramic + 330  $\mu$ F Polymer

Trace: output voltage 50 mV/div Scale: 100  $\mu s/div,$ Slew rate: 2 A/µs 20MHz bandwidth

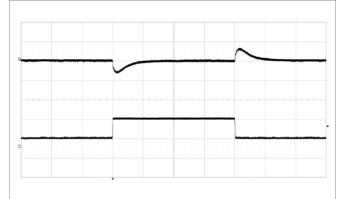

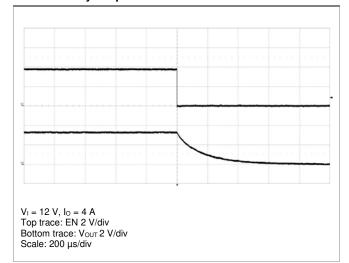

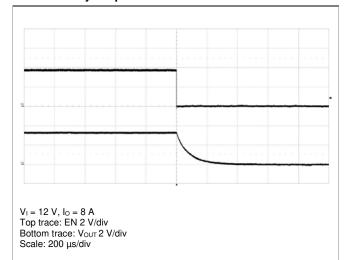

### Shut down by EN pin

Bottom trace: V<sub>OUT</sub> 2 V/div Scale: 200 µs/div

# flex

### **Technical Specification** 15

| PMU 8000 Series PoL Regulators          |

|-----------------------------------------|

| Input 4.5-17 V, Output up to 8 A / 44 W |

1/28701 - BMR668 Rev. D September 2020 © Flex

# Typical Characteristics (V<sub>IN</sub> = 12V)

### Efficiency

### **Output voltage ripple**

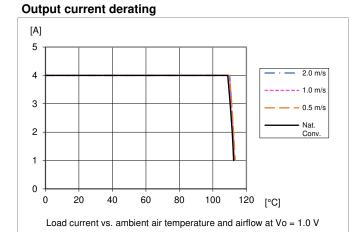

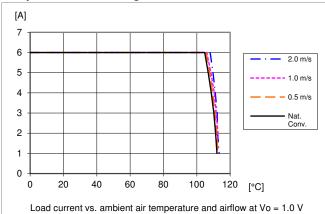

### **Output current derating**

### **Power Dissipation**

Dissipated power vs. load current and output voltage at  $T_{P1}$  = +25 °C

## **Output current derating**

| PMU 8000 Series PoL Regulators          | 1/28701 - BMR668 Rev. D September 2020 |  |  |

|-----------------------------------------|----------------------------------------|--|--|

| Input 4.5-17 V, Output up to 8 A / 44 W | © Flex                                 |  |  |

### 1.0V, 8A / 8W Electrical Specification

$T_{P1} = -40$  to +105 °C,  $V_1 = 4.5$  to 17 V, unless otherwise specified under Conditions. Typical values given at:  $T_{P1} = +25$  °C,  $V_1 = 12$  V, max  $I_0$  unless otherwise specified under Conditions. Additional  $C_{W2} = 100$  UE Electrolytic + 2x10 UE Ceramic capacitors and  $C_{W2} = 4x47$  UE Ceramic capacit

| Additional $C_{IN} = 100 \ \mu F$ Electrolytic + 2x10<br>Characteristics |                                                                      |                         | Conditions                                                                         | min     | typ  | max  | Unit  |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------|---------|------|------|-------|--|

| Vi                                                                       | Input voltage range                                                  |                         |                                                                                    | 4.5     | 12   | 17   | V     |  |

| Vloff                                                                    | Turn-off input voltage                                               |                         | Decreasing input voltage                                                           | 3.7     | 3.9  |      | V     |  |

| Vlon                                                                     | Turn-on input voltage                                                |                         | Increasing input voltage                                                           | 4.1 4.3 |      | 4.3  | V     |  |

| Cı                                                                       | Internal input capacitan                                             | се                      |                                                                                    |         | 2    |      | μF    |  |

| Po                                                                       | Output power                                                         |                         |                                                                                    | 0       |      | 8.0  | W     |  |

| n                                                                        | Efficiency                                                           |                         | $V_{I}$ = 12 V, 50 % of max $I_{O}$                                                |         | 88.2 |      | %     |  |

| η                                                                        |                                                                      |                         | $V_I = 12 V$ , max $I_O$                                                           | 84.8    |      |      | 70    |  |

| Pd                                                                       | Power Dissipation                                                    |                         | $V_{\rm I}$ = 12 V, 50 % of max $I_{\rm O}$                                        | 0.54    |      |      | W     |  |

| d                                                                        |                                                                      |                         | $V_{I} = 12 V$ , max $I_{O}$                                                       | 1.43    |      |      | W     |  |

| Pli                                                                      | Input idling power                                                   |                         | V <sub>1</sub> = 12 V                                                              | 0.17    |      |      | W     |  |

| P <sub>RC</sub>                                                          | Input standby power                                                  |                         | V <sub>1</sub> = 12 V                                                              |         | 20   |      | mW    |  |

| f <sub>s</sub>                                                           | Switching frequency                                                  |                         | 10-100 % of max I <sub>0</sub>                                                     |         | 350  |      | kHz   |  |

| V <sub>Oi</sub>                                                          | Output voltage initial se accuracy                                   | tting and               | $V_{I} = 12 \text{ V}, \text{ max } I_{O}$                                         |         | 1.0  |      | V     |  |

|                                                                          | Output voltage toleranc                                              | e band                  | 10-100 % of max I <sub>o</sub>                                                     |         | ±1.5 |      | %     |  |

|                                                                          | Idling voltage                                                       |                         | $V_1 = 12 V, I_0 = min I_0$                                                        |         | 1.0  |      | V     |  |

| V <sub>o</sub> Line regulation                                           |                                                                      |                         | $I_{0} = \max I_{0}$                                                               | ±0.18   |      |      | mV    |  |

|                                                                          | Load regulation                                                      |                         | $V_1 = 12 V, 0-100 \%$ of max $I_0$                                                | ±1.81   |      |      | mV    |  |

| V <sub>tr</sub>                                                          | Load transient<br>voltage deviation                                  |                         | V <sub>1</sub> = 12 V, Load step 25-75-25 % of max I <sub>0</sub> , di/dt = 2 A/µs | ±55     |      |      | mV    |  |

| t <sub>tr</sub>                                                          | Load transient recovery time                                         |                         | With Loop Optimization<br>$C_{OUT} = 518 \ \mu\text{F}; R_{LO} = 3 \ k\Omega$      | 40      |      |      | μS    |  |

| t <sub>r</sub>                                                           | Ramp-up time<br>(from 10-90 % of V <sub>0</sub> )                    |                         | V <sub>I</sub> = 12 V, 100 % of max I <sub>0</sub>                                 | 1.1     |      |      | ms    |  |

| ts                                                                       | Start-up time (from $V_1$ connection to 90 % of $V_0$ )              |                         | $V_1 = 12 V$ , 100 % of max 10                                                     | 1.6     |      |      | ms    |  |

| ÷                                                                        | V <sub>1</sub> shut-down                                             |                         | I <sub>O</sub> = max lo                                                            |         | 9.7  |      | ms    |  |

| t <sub>f</sub>                                                           | (from V <sub>1</sub> off to 10<br>% of V <sub>0</sub> ) $V_1 = 12 V$ | I <sub>O</sub> = min Io |                                                                                    | 1.0     |      | S    |       |  |

|                                                                          | RC start-up time                                                     |                         | $V_I = 12 V$ , max $I_O$                                                           |         | 1.4  |      | ms    |  |

| : <sub>RC</sub> t <sub>Inh</sub>                                         | RC shut-down<br>fall time<br>(from PO eff to 10) $V_1 = 12 V$        |                         | I <sub>o</sub> = max lo                                                            |         | 46.6 |      | μs    |  |

|                                                                          | (from RC off to TU<br>% of V <sub>O</sub> )                          |                         | I <sub>O</sub> = min lo                                                            |         | 1.3  |      | S     |  |

| 0                                                                        | Output current                                                       |                         |                                                                                    | 0       |      | 8    | A     |  |

| lim                                                                      | Current limit threshold                                              |                         |                                                                                    |         | 11.7 |      | Α     |  |

| sc                                                                       | Short circuit current                                                |                         | RMS, 12 mΩ short                                                                   |         | 2.3  |      | А     |  |

| C <sub>in</sub>                                                          | External input capacitar                                             | nce                     | Ceramic type                                                                       | 20      |      |      | μF    |  |

| <b>C</b> in                                                              | Enternal input capacitance                                           |                         | Non-ceramic type, Note 2                                                           |         | 100  |      |       |  |

| C <sub>out</sub>                                                         | External output capacita                                             | ance                    | Note 3                                                                             | 188     |      | 1500 | μF    |  |

| V <sub>Oac</sub>                                                         | Output ripple & noise V                                              | = 12 V                  | I <sub>O</sub> = max lo                                                            |         | 9.66 |      | mVp-p |  |

Note 2. For Non-ceramic type of external input capacitor, a 100 µF bulk capacitor is recommended for application with transient load requirement. An OS-CON capacitor is recommended when adding the bulk capacitor in low temperature. Note 3. A minimum external output ceramic capacitance is required. In low output voltage, more capacitance might to be added considering capacitance derating. The

maximum external output capacitor could only be ceramic type or combination of ceramic and a single non-ceramic type.

| PMU 8000 Series PoL Regulators          |  |  |  |

|-----------------------------------------|--|--|--|

| Input 4.5-17 V, Output up to 8 A / 44 W |  |  |  |

1/28701 - BMR668 Rev. D September 2020 © Flex

### 1.0V, 8A / 8W Typical Characteristics

### Efficiency

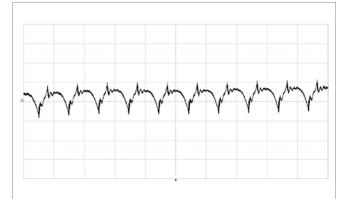

### **Output Ripple & Noise**

Output voltage ripple at:  $T_{P1} = +25 \text{ °C}, V_I = 12 \text{ V}, I_O = 8 \text{ A}$   $C_{OUT} = 4X47 \ \mu\text{F}$  Ceramic

Scale: 2 µs/div 20 MHz bandwidth

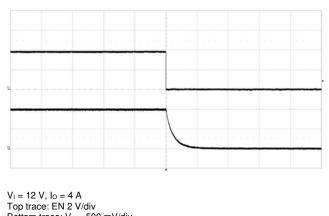

### Start up by EN pin

$V_{\rm I} = 12 \; V, \; I_{\rm O} = 8 \; A$ Top trace: EN 2 V/div Bottom trace: V<sub>OUT</sub> 500 mV/div Scale: 2 ms/div

### **Power Dissipation**

Dissipated power vs. load current and input voltage at  $T_{P1}$  = +25 °C

### **Transient Response**