# HD3SS3220 USB Type-C DRP Port Controller with SuperSpeed 2:1 MUX

#### 1 Features

- USB Type-C Port Controller with Integrated 2:1 SuperSpeed Mux

- Compatible to USB Type-C™ Specifications

- Supports USB 3.1 G1 and G2 up to 10 Gbps

- Supports up to 15 W of Power Delivery with 3-A **Current Advertisement and Detection**

- Mode Configuration

- Host Only DFP/Source

- Device Only UFP/Sink

- Dual Role Port DRP

- Channel Configuration (CC)

- Attach of USB Port Detection

- Cable Orientation Detection

- Role Detection

- Type-C Current Mode (Default, Mid, High)

- V<sub>(BUS)</sub> Detection and VCONN Support for Active Cables

- Audio and Debug Accessory Support

- Supports for Try.SRC and Try.SNK DRP Modes

- Configuration Control through GPIO and I<sup>2</sup>C

- Low Active and Standby Current Consumptions

- Industrial Temperature Range of -40 to 85°C

#### 2 Applications

- USB Host, Device, Hub

- Mobile Phones, Tablets and Notebooks

- USB Peripherals such as Thumb Drives. Portable Hard Disks, Set Top Box

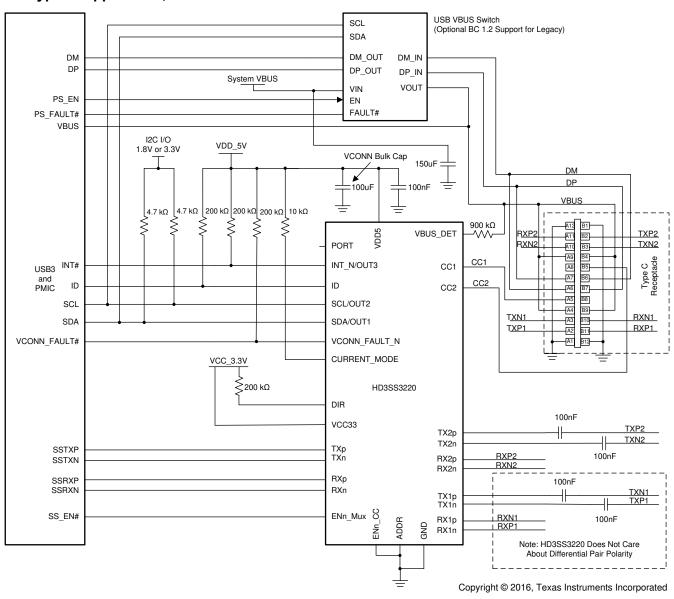

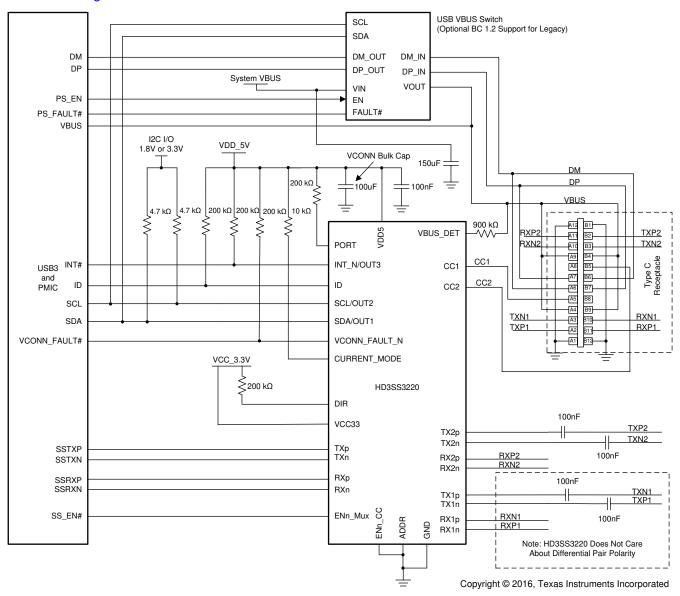

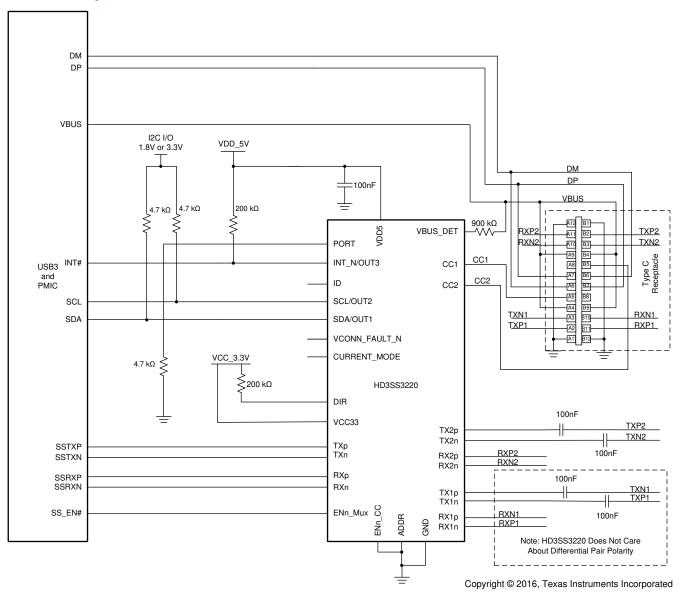

Simplified Schematic

## 3 Description

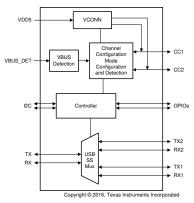

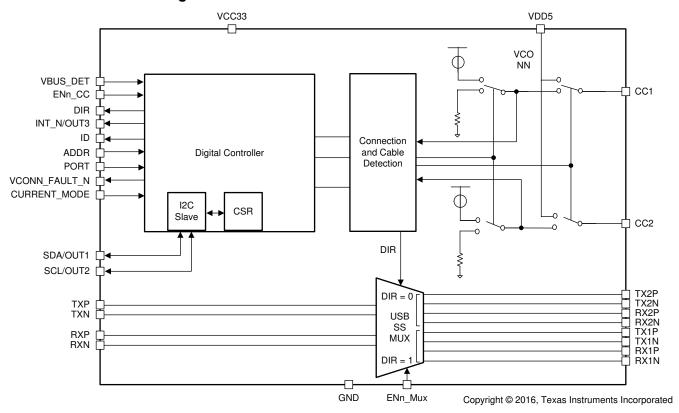

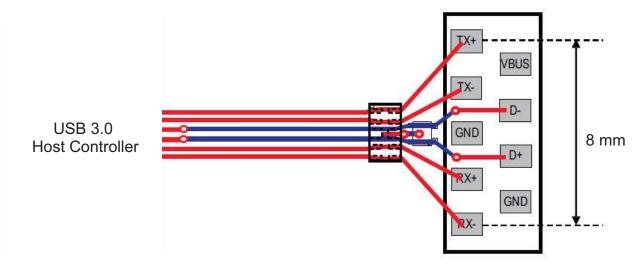

HD3SS3220 is a USB SuperSpeed (SS) 2:1 mux with DRP port controller. The device provides Channel Configuration (CC) logic and 5V VCONN sourcing for ecosystems implementing USB Type-C. HD3SS3220 can be configured as a Downstream Facing Port (DFP), Upstream Facing Port (UFP) or a Dual Role Port (DRP) making it ideal for any application.

The HD3SS3220, in DRP mode, alternates presenting itself as a DFP or UFP according to the Type-C specifications. The CC logic block monitors the CC1 and CC2 pins for pull-up or pull-down resistances to determine when a USB port has been attached and its port role. Once a USB port has been attached, the CC logic also determines the orientation of the cable and configures the USB SS mux accordingly. Finally, CC logic advertises or detects Type-C current mode -Default, Mid, or High in DFP and UFP modes respectively.

Excellent dynamic characteristics of the integrated mux allow switching with minimum attenuation to the SS signal eye diagram and very little added jitter. The device's switch paths deploy adaptive common mode voltage tracking resulting identical channel despite different common mode voltage for RX and TX channels.

#### Device Information (1)

| PART NUMBER | PACKAGE       | BODY SIZE (NOM)          |

|-------------|---------------|--------------------------|

| HD3SS3220   | VQFN RNH (30) | 2.50 mm x 4.50 mm        |

| HD3SS3220I  | VQ(141X(4))   | 2.50 11111 x 4.50 111111 |

For all available packages, see the orderable addendum at the end of the data sheet.

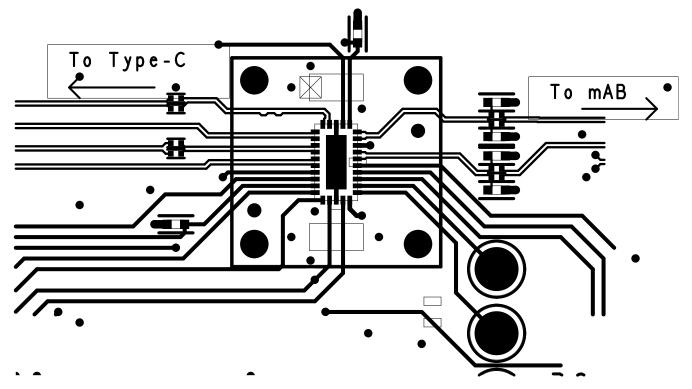

Typical Application

## **Table of Contents**

| 1 Features                                                            | 1                  | 7.4 Device Functional Modes                                                       | 18         |

|-----------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------|------------|

| 2 Applications                                                        | 1                  | 7.5 Programming                                                                   | 20         |

| 3 Description                                                         | 1                  | 7.6 Register Maps                                                                 |            |

| 4 Revision History                                                    |                    | 8 Application and Implementation                                                  | 25         |

| 5 Pin Configuration and Functions                                     |                    | 8.1 Application Information                                                       |            |

| 6 Specifications                                                      |                    | 8.2 Typical Application, DRP Port                                                 |            |

| 6.1 Absolute Maximum Ratings                                          |                    | 9 Layout                                                                          |            |

| 6.2 ESD Ratings                                                       |                    | 9.1 Layout Guidelines                                                             |            |

| 6.3 Recommended Operating Conditions                                  |                    | 9.2 Layout                                                                        |            |

| 6.4 Thermal Information                                               |                    | 10 Device and Documentation Support                                               |            |

| 6.5 Electrical Characteristics                                        |                    | 10.1 Receiving Notification of Documental                                         |            |

| 6.6 Timing Requirements                                               |                    | 10.2 Community Resources                                                          |            |

| 7 Detailed Description                                                |                    | 10.3 Trademarks  11 Mechanical, Packaging, and Orderable                          |            |

| 7.1 Overview                                                          |                    | Information                                                                       | ,          |

| 7.3 Feature Description                                               |                    | IIIIOIIIIatioii                                                                   | 39         |

| 4 Revision History                                                    |                    |                                                                                   |            |

| Changes from Revision C (May 2017) to R                               | evision D          | (September 2020)                                                                  | Page       |

|                                                                       |                    |                                                                                   | 3          |

|                                                                       | •                  |                                                                                   |            |

|                                                                       |                    |                                                                                   |            |

|                                                                       |                    |                                                                                   |            |

|                                                                       |                    |                                                                                   |            |

| for I <sup>2</sup> C, customer must ensure VDD5 is al                 | pove 3 V at        | all times                                                                         | 6          |

| · Changed the "I2C (SDA, SCL)" section of                             | the <i>Timing</i>  | Requirements table                                                                | 8          |

| • Added t <sub>ENDCC</sub> H <sub>I</sub> parameter in section of the | he <i>Timina F</i> | Requirements table                                                                | 8          |

|                                                                       |                    |                                                                                   |            |

| <ul> <li>Added note in section DFP/Source – Down</li> </ul>           | vnstream Fa        | acing Port that ID pin will remain high until                                     | VBUS is at |

| <ul> <li>From: When a voltage level within the pro</li> </ul>         | per thresho        | old is detected on CC1, the DIR pin is pulle                                      | d low. To: |

|                                                                       |                    |                                                                                   |            |

| • ,                                                                   |                    | · · · · · · · · · · · · · · · · · · ·                                             |            |

| supports audio and debug accessories in                               | UFP, DFP           | and DRP mode by default                                                           | 16         |

| Changed VDD to VDD5                                                   |                    |                                                                                   |            |

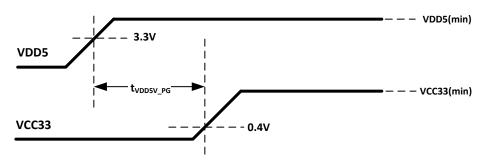

| <ul> <li>Added section on VDD5 and VCC33 pow</li> </ul>               | er-on requir       | rements                                                                           | 17         |

|                                                                       |                    |                                                                                   |            |

| VCC33 Power-On Requirements section.                                  |                    | a Datery Section as this information is in the                                    | 19         |

| Changes from Revision B (September 201                                | 6) to Revis        | sion C (May 2017)                                                                 | Page       |

| <ul> <li>Added R<sub>VBUS</sub> values: MIN = 855, TYP = 8</li> </ul> | 387, MAX =         | 920 ΚΩ                                                                            | 6          |

| Changes from Revision A (August 2016) t                               | o Revision         | B (September 2016)                                                                | Page       |

| <ul> <li>Changed pins CC1 and CC2 values From</li> </ul>              | 1: MIN = -0.       | $3 \text{ MAX} = \text{VDD5} + 0.3 \text{ To: MIN} - 0.3 \overline{\text{MAX}} =$ | 6 in the   |

Absolute Maximum Ratings ......5

| C | hanges from Revision * (December 2016) to Revision A (August 2016)                                         | Page |

|---|------------------------------------------------------------------------------------------------------------|------|

| • | Absolute Maximum Ratings, Deleted "ENn_MUX" from the Control Pins                                          | 5    |

| • | ESD Ratings, Deleted text "Pins listed as ±XXX V may actually have higher performance." from Note 1        | 5    |

| • | Recommended Operating Conditions, Added "VDD5 supply ramp time"                                            | 5    |

| • | Recommended Operating Conditions, Changed "External resistor on VBUS_DET pin" MIN value From KΩ To: 880 KΩ |      |

| • | Switch the position of CC1 and CC2 in Figure 8-1                                                           | 26   |

| • | Switch the position of CC1 and CC2 in Figure 8-2                                                           | 28   |

| • | Switch the position of CC1 and CC2 in Figure 8-3                                                           | 30   |

|   |                                                                                                            |      |

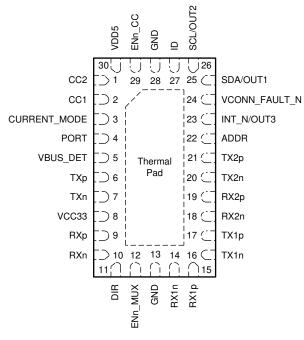

# **5 Pin Configuration and Functions**

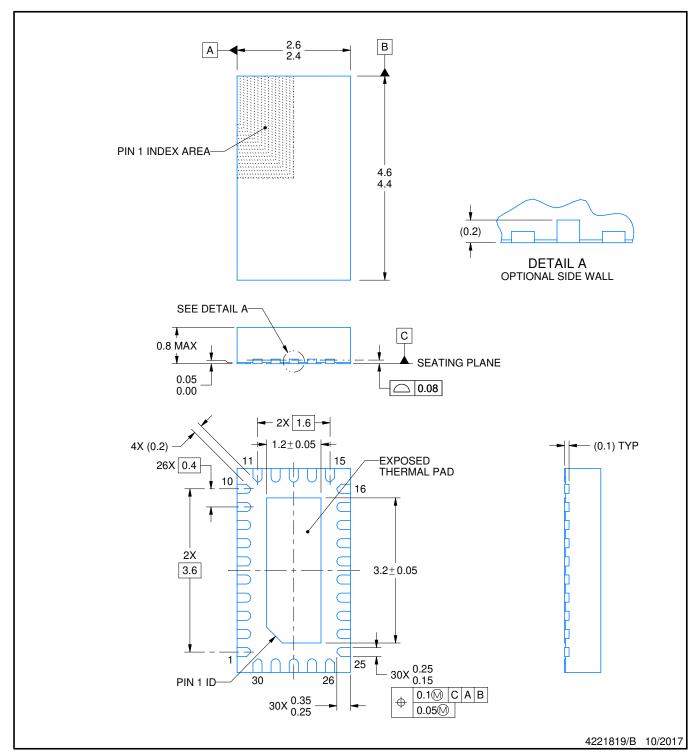

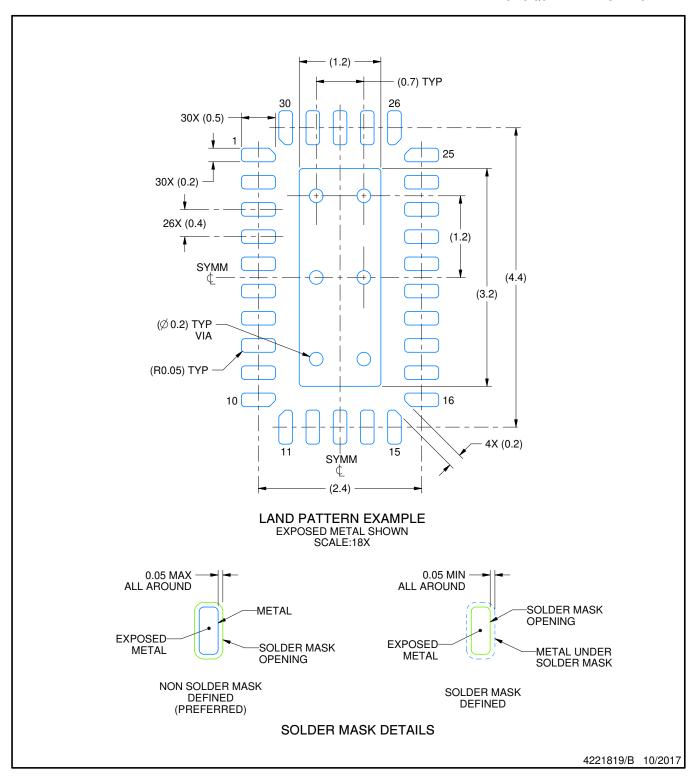

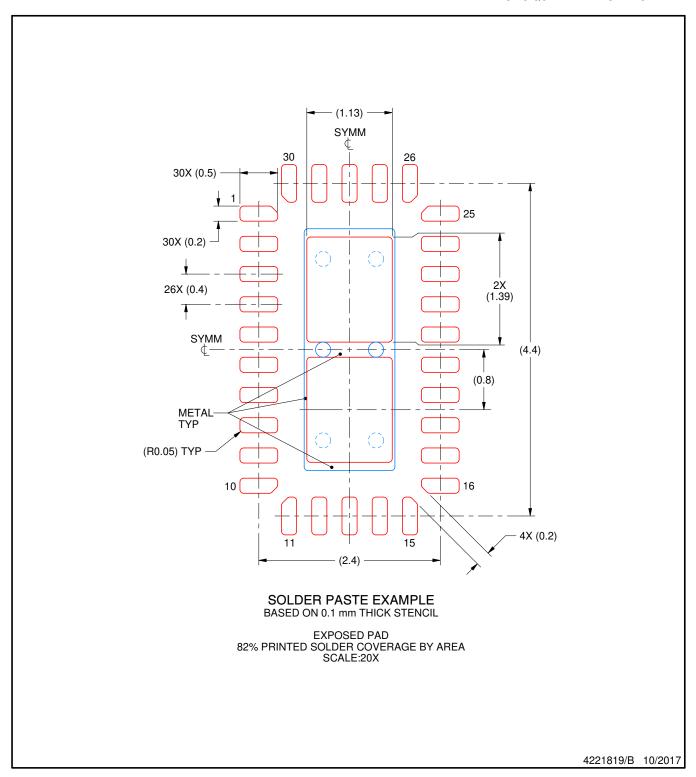

Figure 5-1. RNH Package 30 Pin (VQFN) Top View

#### **Pin Functions**

| PIN          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| CC2          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O | Type-C Configuration channel signal 2                                                                                                                                                                                                                                                                                                                                                   |  |  |

| CC1          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O | Type-C Configuration channel signal 1                                                                                                                                                                                                                                                                                                                                                   |  |  |

| CURRENT_MODE | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ı   | Tri-level input pin to indicate current advertisement in DFP (or DFP in DRP) mode while in GPIO mode. Don't care in UFP mode. Provides the flexibility to advertise higher current without I <sup>2</sup> C. The pin has 250 K internal pull-down.  L – Low - Default – 900 mA  M - Medium (Install 500 K to VDD5 on the PCB) – 1.5 A  H - High (Install 10 K to VDD5 on the PCB) – 3 A |  |  |

| PORT         | 2 I/O Type-C Configuration channel signal 1  Tri-level input pin to indicate current advertisement in DFP (or DFP in DRP) mode while in 0 mode. Don't care in UFP mode. Provides the flexibility to advertise higher current without I <sup>2</sup> (pin has 250 K internal pull-down. L – Low - Default – 900 mA M - Medium (Install 500 K to VDD5 on the PCB) – 1.5 A H - High (Install 10 K to VDD5 on the PCB) – 3 A  Tri-level input pin to indicate port mode. The state of this pin is sampled when HD3SS3220's ENn_CC is asserted low, and VDD5 is active. This pin is also sampled following a I2C_SOFT_RESET. H - DFP (Pull-up to VDD5 if DFP mode is desired) NC - DRP (Leave unconnected if DRP mode is desired) L - UFP (Pull-down or tie to GND if UFP mode is desired) |     |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I   | 5-28V VBUS input voltage. VBUS detection determines UFP attachment. One 900K external resistor required between system VBUS and VBUS_DET pin.                                                                                                                                                                                                                                           |  |  |

| TXp          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O | Host/Device USB SuperSpeed differential Signal TX positive                                                                                                                                                                                                                                                                                                                              |  |  |

| TXn          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O | Host/Device USB SuperSpeed differential Signal TX negative                                                                                                                                                                                                                                                                                                                              |  |  |

| PIN           |        |     |                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| VCC33         | 8      | Р   | 3.3-V Power supply                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RXp           | 9      | I/O | Host/Device USB SuperSpeed differential Signal RX positive                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXn           | 10     | I/O | Host/Device USB SuperSpeed differential Signal RX negative                                                                                                                                                                                                                                                                                                                                           |  |  |

| DIR           | 11     | 0   | Type-C plug orientation. Open drain output. A pull-up resistor (that is, 200 K) must be installed for proper operation of the device.                                                                                                                                                                                                                                                                |  |  |

| ENn_MUX       | 12     | I   | Active Low MUX Enable: L - Normal operation, and H - Shutdown.                                                                                                                                                                                                                                                                                                                                       |  |  |

| GND           | 13, 28 | G   | Ground                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| RX1n          | 14     | I/O | Type-C Port - USB SuperSpeed differential Signal RX1 negative                                                                                                                                                                                                                                                                                                                                        |  |  |

| RX1p          | 15     | I/O | Type-C Port - USB SuperSpeed differential Signal RX1 positive                                                                                                                                                                                                                                                                                                                                        |  |  |

| TX1n          | 16     | I/O | Type-C Port - USB SuperSpeed differential Signal TX1 negative                                                                                                                                                                                                                                                                                                                                        |  |  |

| TX1p          | 17     | I/O | Type-C Port - USB SuperSpeed differential Signal TX1 positive                                                                                                                                                                                                                                                                                                                                        |  |  |

| RX2n          | 18     | I/O | Type-C Port - USB SuperSpeed differential Signal RX2 negative                                                                                                                                                                                                                                                                                                                                        |  |  |

| RX2p          | 19     | I/O | Type-C Port - USB SuperSpeed differential Signal RX2 positive                                                                                                                                                                                                                                                                                                                                        |  |  |

| TX2n          | 20     | I/O | Type-C Port - USB SuperSpeed differential Signal TX2 negative                                                                                                                                                                                                                                                                                                                                        |  |  |

| TX2p          | 21     | I/O | Type-C Port - USB SuperSpeed differential Signal TX2 positive                                                                                                                                                                                                                                                                                                                                        |  |  |

| ADDR          | 22     | ı   | Tri-level input pin to indicate I <sup>2</sup> C address or GPIO mode: H (connect to VDD5) - I <sup>2</sup> C is enabled and I2C 7-bit address is 0x67. NC - GPIO mode (I2C is disabled) L (connect to GND) - I <sup>2</sup> C is enabled and I2C 7-bit address is 0x47. ADDR pin should be pulled up to VDD5 if high configuration is desired                                                       |  |  |

| INT_N/OUT3    | 23     | 0   | The INT_N/OUT3 is a dual-function pin.  When used as the INT_N, the pin is an open drain output in I <sup>2</sup> C control mode and is an active low interrupt signal for indicating changes in I <sup>2</sup> C registers.  When used as OUT3, the pin is in audio accessory detect in GPIO mode:  H - no detection, and L - audio accessory connection detected.                                  |  |  |

| VCONN_FAULT_N | 24     | 0   | Open drain output. Asserted low when VCONN overcurrent detected.                                                                                                                                                                                                                                                                                                                                     |  |  |

| SDA/OUT1      | 25     | I/O | The SDA/OUT1 is a dual-function pin.  When I2C is enabled (ADDR pin is high or low), this pin is the I²C communication data signal.  When in GPIO mode (ADDR pin is NC), this pin is an open drain output for communicating Type-C current mode detect when the device is in UFP mode:  H – Default (900 mA) current mode detected, and  L – Medium (1.5 A) or High (3 A) Current Mode detected.     |  |  |

| SCL/OUT2      | 26     | I/O | The SCL/OUT2 is a dual function pin.  When I <sup>2</sup> C is enabled (ADDR pin is high or low), this pin is the I <sup>2</sup> C communication clock signal.  When in GPIO mode (ADDR pin is NC), this pin is an open drain output for communicating Type-C current mode detect when the device is in UFP mode:  H – Default or Medium current mode detected, and  L – High current mode detected. |  |  |

| ID            | 27     | 0   | Open drain output. Asserted low when CC pin detected device attachment when port is a source (DFP), or dual-role (DRP) acting as source (DFP).                                                                                                                                                                                                                                                       |  |  |

| ENn_CC        | 29     | I   | Enable signal for CC controller. Enable is active low.                                                                                                                                                                                                                                                                                                                                               |  |  |

| VDD5          | 30     | Р   | 5-V Power supply                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Thermal Pad   | -      | -   | The thermal PAD must be connected to GND, see the Thermal Pad connection techniques (SLMA002).                                                                                                                                                                                                                                                                                                       |  |  |

# **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                                                        | MIN  | MAX        | UNIT |

|---------------------------------------|--------------------------------------------------------|------|------------|------|

| 5-V Supply Voltage                    | VDD5                                                   | -0.3 | 6          | V    |

| 3.3-V Supply Voltage                  | VCC33                                                  | -0.3 | 4          | V    |

|                                       | ADDR, PORT, ID, INT_N/OUT3, ENn_CC, SDA/OUT1, SCL/OUT2 | -0.3 | VDD5 +0.3  | V    |

| Control Pins                          | CC1, CC2                                               | -0.3 | 6          | V    |

|                                       | ENn_MUX, DIR                                           | -0.3 | VCC33 +0.3 | V    |

|                                       | VBUS_DET                                               | -0.3 | 4          | V    |

| Super-speed Differential Signal Pins  | [RX/TX] [p/n], [RX/TX][2/1][p/n]                       | -0.3 | 2.5        | V    |

| Storage temperature, T <sub>stg</sub> |                                                        | -65  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

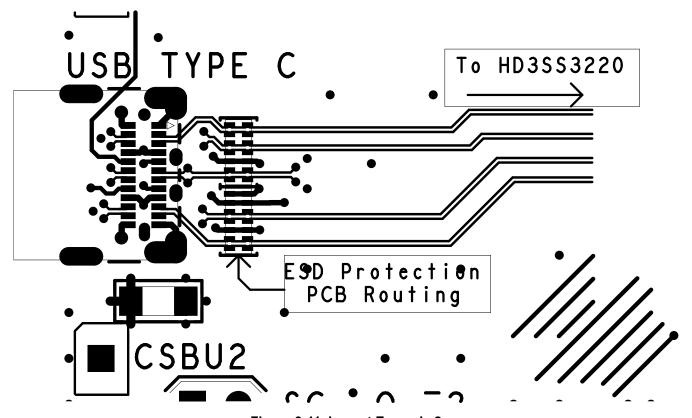

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                          |                                                                                                            | MIN                | NOM | MAX | UNIT     |

|--------------------------|------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|----------|

| V <sub>DD5</sub>         | 5-V Supply Voltage range                                                                                   | 4.5 <sup>(1)</sup> |     | 5.5 | V        |

| V <sub>CC33</sub>        | 3.3-V Supply Voltage range                                                                                 | 3                  |     | 3.6 | V        |

| $V_{DD}$                 | Supply range for I2C (SDA, SCL) pins                                                                       | 1.65               |     | 3.6 | V        |

| V <sub>DD5(ramp)</sub>   | VDD5 supply ramp time                                                                                      |                    |     | 25  | ms       |

| $V_{(diff)}$             | High speed signal pins differential voltage                                                                | 0                  |     | 1.8 | $V_{PP}$ |

| V <sub>(cm)</sub>        | High speed signal pins common mode voltage                                                                 | 0                  |     | 2   | V        |

| T <sub>A</sub>           | Operating free-air/ambient temperature (HD3SS3220)                                                         | 0                  |     | 70  | °C       |

| T <sub>A</sub>           | Operating free-air/ambient temperature (HD3SS3220I)                                                        | -40                |     | 85  | °C       |

| V <sub>(BUS)</sub>       | System V <sub>(BUS)</sub> input voltage through 900-K resistor                                             | 4                  | 5   | 28  | V        |

| C <sub>(BULK)</sub>      | Bulk capacitance on VCONN. Only when VCONN is on. Disconnected when VCONN is off. Shall be placed on VDD5. | 10                 |     | 200 | μF       |

| R <sub>(p_ODext)</sub>   | External Pull up resistor on Open Drain IOs (OUT1, OUT2, INT/OUT3, ID, VCONN_FAULT_N, and DIR pins)        |                    | 200 |     | ΚΩ       |

| R <sub>(p_TLext)</sub>   | Tri-level input external pull-up resistor (PORT and ADDR pins)                                             |                    | 4.7 |     | ΚΩ       |

| R <sub>(p_15A)</sub>     | External pull up resistor to advertise 1.5 A (CURRENT_MODE pin)                                            |                    | 500 |     | ΚΩ       |

| R <sub>(p_3A)</sub>      | External pull up resistor to advertise 3 A (CURRENT_MODE pin)                                              |                    | 10  |     | ΚΩ       |

| R <sub>(p_i2c_ext)</sub> | External Pull up resistance on I <sup>2</sup> C bus<br>(Could be 4.7 K or higher. Nominal value listed)    |                    | 2.2 |     | ΚΩ       |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process..

over operating free-air temperature range (unless otherwise noted)

|                     |                                   | MIN | NOM | MAX | UNIT |

|---------------------|-----------------------------------|-----|-----|-----|------|

| R <sub>(VBUS)</sub> | External resistor on VBUS_DET pin | 880 | 900 | 910 | ΚΩ   |

(1) With 200 mA VCONN current for VCONN ≥ 4.75 V at connector, VDD5 ≥ 5 V is recommended

## **6.4 Thermal Information**

|                       | Junction-to-board thermal resistance  Junction-to-top characterization parameter | HD3SS3220  |      |

|-----------------------|----------------------------------------------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                                                    | RNH (VQFN) | UNIT |

|                       |                                                                                  | 30 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance                                           | 60.9       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                                        | 50.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                                             | 22.8       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter                                       | 1.7        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter                                     | 22.6       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                                     | 12.1       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                                                                                          | TEST CONDITIONS         | MIN  | TYP | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|------|------|

| Power Consum               | nption                                                                                                                             |                         |      |     |      |      |

| I <sub>(ACTIVE)</sub>      | Current consumption in active mode- both CC controller and SS mux on                                                               | ENn_CC/Mux = L          |      | 0.7 | 0.9  | mA   |

| I <sub>CC</sub>            | Current consumption in active mode – CC controller on and SS mux off                                                               | ENn_CC = L, ENn_Mux = H |      | 0.2 |      | mA   |

| I <sub>(SHUTDOWN)</sub>    | Current consumption in shutdown mode                                                                                               | ENn_CC/Mux = H          |      | 5   |      | μΑ   |

| CC PINS                    |                                                                                                                                    |                         | •    |     |      |      |

| R <sub>(CC_DB)</sub>       | Pulldown resistor when in dead-battery mode.                                                                                       |                         | 4.1  | 5.1 | 6.1  | kΩ   |

| R <sub>(CC_D)</sub>        | Pulldown resistor when in UFP or DRP mode.                                                                                         |                         | 4.6  | 5.1 | 5.6  | kΩ   |

| V <sub>(UFP_CC_USB)</sub>  | Voltage level for detecting a DFP attach when configured as a UFP and DFP is advertising default current source capability.        |                         | 0.25 |     | 0.61 | V    |

| V <sub>(UFP_CC_MED)</sub>  | Voltage level for detecting a DFP attach when configured as a UFP and DFP is advertising medium (1.5 A) current source capability. |                         | 0.7  |     | 1.16 | V    |

| V <sub>(UFP_CC_HIGH)</sub> | Voltage level for detecting a DFP attach when configured as a UFP and DFP is advertising high (3 A) current source capability.     |                         | 1.31 |     | 2.04 | V    |

| V <sub>(DFP_CC_USB)</sub>  | Voltage level for detecting a UFP attach when configured as a DFP and advertising default current source capability.               |                         | 1.51 | 1.6 | 1.64 | V    |

| V <sub>(DFP_CC_MED)</sub>  | Voltage level for detecting a UFP attach when configured as a DFP and advertising 1.5-A current source capability.                 |                         | 1.51 | 1.6 | 1.64 | V    |

| V <sub>(DFP_CC_HIGH)</sub> | Voltage level for detecting a UFP attach when configured as a DFP and advertising 3-A current source capability.                   |                         | 2.46 | 2.6 | 2.74 | V    |

| V <sub>(AC_CC_USB)</sub>   | Voltage level for detecting an active cable attach when configured as a DFP and advertising default current source capability.     |                         | 0.15 | 0.2 | 0.25 | V    |

| V <sub>(AC_CC_MED)</sub>   | Voltage level for detecting an active cable attach when configured as a DFP and advertising 1.5-A current source capability.       |                         | 0.35 | 0.4 | 0.45 | V    |

| V <sub>(DFP_CC_HIGH)</sub> | Voltage level for detecting an active cable attach when configured as a DFP and advertising 3-A current source capability.         |                         | 0.75 | 0.8 | 0.84 | V    |

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

#### www.ti.com

over operating free-air temperature range (unless otherwise noted)

|                             | PARAMETER                                                                     | TEST CONDITIONS           | MIN            | TYP        | MAX            | UNIT |

|-----------------------------|-------------------------------------------------------------------------------|---------------------------|----------------|------------|----------------|------|

| CC(DEFAULT_P)               | Default mode pull-up current source when operating in DFP or DRP mode.        |                           | 64             | 80         | 96             | μA   |

| CC(MED_P)                   | Medium (1.5 A) mode pull-up current source when operating in DFP or DRP mode. |                           | 166            | 180        | 194            | μA   |

| CC(HIGH_P)                  | High (3 A) mode pull-up current source when operating in DFP or DRP mode.     |                           | 34             | 330        | 356            | μA   |

| 3-Level Input Pi            | ins: PORT, ADDR, ENn_CC and CURRENT_M                                         | ODE                       |                |            |                |      |

| V <sub>IL</sub>             | Low-level input voltage                                                       |                           |                |            | 0.4            | V    |

| V <sub>M</sub>              | Mid-Level (Floating) voltage (PORT, ADDR and CURRENT_MODE pins)               |                           | 0.28 x<br>VDD5 |            | 0.56 x<br>VDD5 | V    |

| V <sub>IH</sub>             | High-level input voltage                                                      |                           | VDD5 - 0.3     |            | VDD5           | V    |

| liн                         | High-level input current                                                      |                           | 20             |            | 20             | μΑ   |

| I <sub>IL</sub>             | Low-level input current                                                       |                           | -10            |            | 10             | μA   |

| I <sub>ID(LKG)</sub>        | Current Leakage on ID pin                                                     | VDD5 = 0 V, ID = 5 V      |                |            | 10             | μA   |

| R <sub>(pu)</sub>           | Internal pull-up resistance (PORT and ADDR pins)                              |                           |                | 588        |                | kΩ   |

| R <sub>(pd)</sub>           | Internal pull-down resistance (PORT and ADDR pins)                            |                           |                | 1.1        |                | МΩ   |

| R <sub>(pd_CURRENT)</sub>   | Internal pull-down resistance (CURRENT_MODE pin)                              |                           |                | 275        |                | kΩ   |

| R <sub>(ENn_CC)</sub>       | Internal pull-up resistance (ENn_CC pin)                                      |                           |                | 1.1        |                | МΩ   |

| Input Pins: ENn             | ı_MUX                                                                         |                           | 1              |            |                |      |

| V <sub>IL</sub>             | Low-level input voltage                                                       |                           |                |            | 0.3 x<br>VCC33 | V    |

| V <sub>IH</sub>             | High-level input voltage                                                      |                           | 0.7 x<br>VCC33 |            |                | V    |

| ІН                          | High-level input current                                                      |                           | -1             |            | 1              | μA   |

| I <sub>IL</sub>             | Low-level input current                                                       |                           | -1             |            | 1              | μA   |

| Open Drain Out              | tput Pins: OUT1, OUT2, INT_N/OUT3, ID, VCO                                    | NN_FAULT_N, DIR           | '              |            |                |      |

| V <sub>OL</sub>             | Low-level signal output voltage                                               | I <sub>OL</sub> = -1.6 mA |                |            | 0.4            | V    |

| 2C- SDA/OUT1                | , SCL/OUT2 can Operate from 1.8/3.3 V (±10%                                   | 6) <sup>(1)</sup>         | '              |            |                |      |

| V <sub>IH</sub>             | High-level input voltage                                                      |                           | 1.05           |            |                | V    |

| V <sub>IL</sub>             | Low-level input voltage                                                       |                           |                |            | 0.4            | V    |

| V <sub>OL</sub>             | Low-level output voltage (open-drain)                                         | I <sub>OL</sub> = -1.6 mA |                |            | 0.4            | V    |

| VBUS_DET IO P               | Pin (Connected to System VBUS Signal)                                         |                           |                |            |                |      |

| V <sub>(BUS_THR)</sub>      | VBUS threshold range                                                          |                           | 2.95           | 3.3        | 3.8            | V    |

| R <sub>VBUS</sub>           | External resistor between V <sub>BUS</sub> and VBUS_DET pin                   |                           | 855            | 887        | 920            | ΚΩ   |

| R <sub>(VBUS_DET_INT)</sub> | Internal pull-down resistor at VBUS_DET pin                                   |                           |                | 95         |                | kΩ   |

| VCONN                       |                                                                               | 1                         | 1              |            |                |      |

| R <sub>ON</sub>             | On resistance of the VCONN power FET                                          |                           |                |            | 1.25           | Ω    |

| V <sub>(TOL)</sub>          | Voltage tolerance on VCONN power FET                                          |                           |                |            | 5.5            | V    |

| V <sub>(pass)</sub>         | Voltage to pass through VCONN power FET                                       |                           |                |            | 5.5            | V    |

| (VCONN)                     | VCONN current limit. VCONN will be disconnected above this value              |                           | 225            | 300        | 375            | mA   |

| MUX High Spee               | d Performance Parameters                                                      |                           |                |            |                |      |

|                             |                                                                               | f = 0.3 Mhz               |                | -0.43      |                |      |

| IL                          | Differential Insertion Loss                                                   | f = 2.5 Ghz               |                | -1.07      |                | dB   |

|                             |                                                                               | f = 5 Ghz                 |                | -1.42      |                |      |

| BW                          | Bandwidth                                                                     |                           |                | 8          |                | Ghz  |

|                             |                                                                               | f = 0.3 Mhz               |                | -27        |                |      |

| $R_L$                       | Differential return loss                                                      | f = 2.5 Ghz               |                | -9         |                | dB   |

| •                           |                                                                               | f = 5 Ghz                 |                | <b>–</b> 9 |                |      |

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                     | TEST CONDITIONS | MIN | TYP         | MAX | UNIT |

|-------------------|-------------------------------|-----------------|-----|-------------|-----|------|

|                   |                               | f = 0.3 Mhz     |     | <b>–</b> 79 |     |      |

| O <sub>IRR</sub>  | RR Differential OFF isolation | f = 2.5 Ghz     |     | -23         |     | dB   |

|                   |                               | f = 5 Ghz       |     | -20         |     |      |

|                   |                               | f = 0.3 Mhz     |     | -89         |     |      |

| X <sub>TALK</sub> | Differential Cross Talk       | f = 2.5 Ghz     |     | -34         |     | dB   |

|                   |                               | f = 5 Ghz       |     | -30         |     |      |

| R <sub>ON</sub>   | On resistance                 |                 |     |             | 8   | Ω    |

<sup>(1)</sup> When using  $3.3\ V$  for  $I^2C$ , customer must ensure VDD5 is above  $3\ V$  at all times.

# **6.6 Timing Requirements**

|                         |                                                                                 | MIN | NOM MAX | UNIT |

|-------------------------|---------------------------------------------------------------------------------|-----|---------|------|

| I2C (SDA, S             | CL)                                                                             |     |         |      |

| t <sub>SU:DAT</sub>     | Data setup time                                                                 | 100 |         | ns   |

| t <sub>HD:DAT</sub>     | Data setup time                                                                 | 10  |         | ns   |

| t <sub>SU;STA</sub>     | Set-up time, SCL to start condition                                             | 0.6 |         | μs   |

| t <sub>HD,STA</sub>     | Hold time,(repeated) start condition to SCL                                     | 0.6 |         | μs   |

| t <sub>SU:STO</sub>     | Set up time for STOP condition                                                  | 0.6 |         | μs   |

| t <sub>VD;DAT</sub>     | Data valid time                                                                 |     | 0.9     | μs   |

| t <sub>VD;ACK</sub>     | Data valid acknowledge time                                                     |     | 0.9     | μs   |

| t <sub>BUF</sub>        | Bus free time between a STOP and START condition                                | 1.3 |         | μs   |

| f <sub>SCL</sub>        | SCL clock frequency; I <sup>2</sup> C mode for local I <sup>2</sup> C control   |     | 400     | ns   |

| t <sub>r</sub>          | Rise time of both SDA and SCL signals                                           |     | 300     | ns   |

| t <sub>f</sub>          | Fall time of both SDA and SCL signals                                           |     | 300     | ns   |

| C <sub>BUS_100KHZ</sub> | Total capacitive load for each bus line when operating at ≤ 100 KHz             |     | 400     | pF   |

| C <sub>BUS_400KHZ</sub> | Total capacitive load for each bus line when operating at 400 KHz.              |     | 100     | pF   |

| SS MUX                  |                                                                                 |     |         |      |

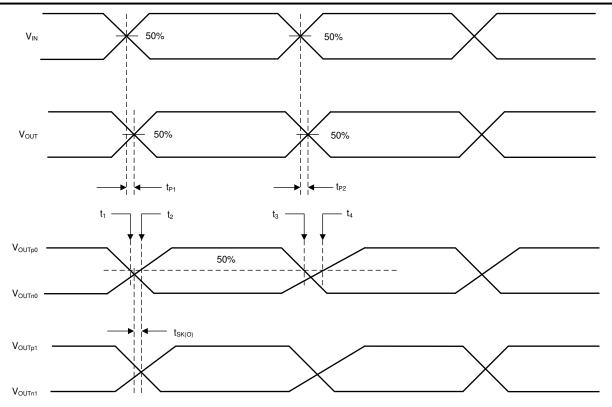

| t <sub>PD</sub>         | Switch propagation delay See Figure 6-3                                         |     | 80      | ps   |

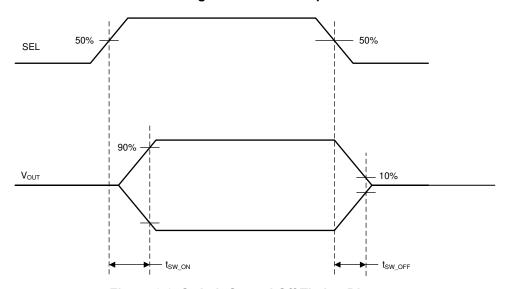

| t <sub>SW_ON</sub>      | Switching time DIR-to-Switch ON See Figure 6-2                                  |     | 0.5     | μs   |

| t <sub>SW_OFF</sub>     | Switching time DIR-to-Switch OFF See Figure 6-2                                 |     | 0.5     | μs   |

| t <sub>SK_INTRA</sub>   | Intra-pair output skew See Figure 6-3                                           |     | 5       | ps   |

| t <sub>SK_INTER</sub>   | Inter-pair output skew See Figure 6-3                                           |     | 20      | ps   |

| Power-On T              | imings                                                                          | •   |         |      |

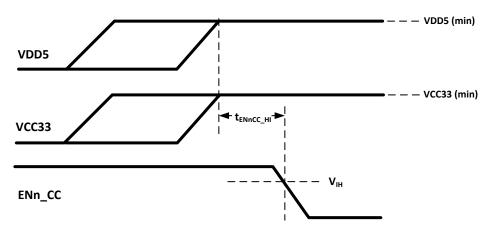

| t <sub>ENnCC_HI</sub>   | ENn_CC high after both VDD5 and VCC33 supplies are stable. Refer to Figure 7-3. | 2   |         | ms   |

| t <sub>VDD5V_PG</sub>   | VDD5 stable before VCC33. Refer to Figure 7-2.                                  | 2   |         | ms   |

Submit Document Feedback

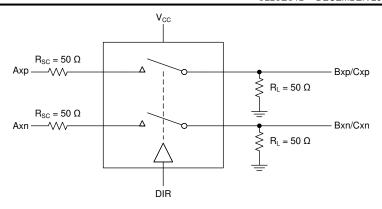

Figure 6-1. Test Setup

Figure 6-2. Switch On and Off Timing Diagram

Figure 6-3. Timing Diagrams and Test Setup

## 7 Detailed Description

#### 7.1 Overview

The USB Type-C ecosystem operates around a small form factor connector and cable that is flippable and reversible. Due to the nature of the connector, a scheme is needed to determine the connector orientation. Additional schemes are needed to determine when a USB port is attached, determine the acting role of the USB port (DFP, UFP, DRP), and communicate Type-C current capabilities. These schemes are implemented over the CC pins according to the USB Type-C specifications. The HD3SS3220 provides Configuration Channel (CC) logic for determining USB port attach/detach, role detection, cable orientation, and Type-C current mode. The HD3SS3220 also contains several features such as VCONN sourcing, audio and debug accessory modes, Try.SRC and Try.SNK DRP configurations which make this device ideal for source, sink or dual role applications with USB 2.0 or USB 3.1.

HD3SS3220 has integrated USB 3.0/3.1 SS/SS+ MUX with 2 channel 2:1 switching required to handle cable flips. The CC controller determines the orientation of the cable and controls the MUX selection. The device also provides this orientation signal as a GPIO signal DIR that can be used in the system for increased flexibility and features.

#### 7.1.1 Cables, Adapters, and Direct Connect Devices

Type-C Specification defines several cables, plugs and receptacles to be used to attach ports. The HD3SS3220 supports all cables, receptacles, and plugs. The HD3SS3220 device does not support any USB feature which requires USB Power Delivery (PD) communications over CC lines, such as e-marking or alternate mode.

## 7.1.1.1 USB Type-C receptacles and Plugs

The following is alist of Type-C receptacles and plugs supported by the HD3SS3220 device:

- USB Type-C receptacle for USB2.0 and USB3.1 and full-featured platforms and devices

- USB Full-Featured Type-C plug

- USB2.0 Type-C Plug

#### 7.1.1.2 USB Type-C Cables

The following is a list of Type-C cables supported by the HD3SS3220 device:

- USB Full-featured Type-C cable with USB3.1 full featured plug

- USB2.0 Type-C cable with USB2.0 plug

- Captive cable with either a USB Full featured plug or USB2.0 plug

#### 7.1.1.3 Legacy Cables and Adapters

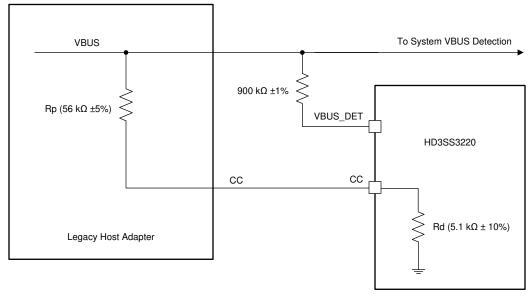

The HD3SS3220 supports legacy cable adapters as defined by the Type-C specifications. The cable adapter must correspond to the mode configuration of the HD3SS3220 device.

Copyright © 2016, Texas Instruments Incorporated

Figure 7-1. Legacy Adapter Implementation Circuit

#### 7.1.1.4 Direct Connect Device

HD3SS3220 supports the attaching and detaching of a direct connect device such as cradle dock.

#### 7.1.1.5 Audio Adapters

Additionally, HD3SS3220 supports audio adapters for audio accessory mode, including:

- · Passive Audio Adapte

- · Charge Through Audio Adapter

# 7.2 Functional Block Diagram

## 7.3 Feature Description

The HD3SS3220 can be configured as a DFP, UFP, or DRP using the 3-level PORT pin. The PORT pin should be strapped high to VDD5 using a pull-up resistance to achieve DFP mode, low to GND for UFP mode or left floating for DRP mode on the PCB. This flexibility allows the HD3SS3220 to be used in a variety of applications. The HD3SS3220 samples the PORT pin after reset and maintains the desired mode until the HD3SS3220 is reset again. It shall be static. Table 7-1 shows the supported features in each mode.

Table 7-1. Supported Features for HD3SS3220 by Mode

| PORT PIN                                      | High     | Low      | NC     |

|-----------------------------------------------|----------|----------|--------|

| Supported Features                            | DFP Only | UFP Only | DRP    |

| Port Attach/Detach                            | √        | √        | √      |

| Cable Orientation                             | √        | √        | √      |

| Current Advertisement                         | √        |          | √(DFP) |

| Current Detection                             |          | √        | √(UFP) |

| Audio Accessory                               | √        | √        | √      |

| Debug Accessory Modes                         | √        | √        | √      |

| Active Cable Detection                        | √        |          | √(DFP) |

| Try.SRC                                       |          |          | √      |

| Try.SNK                                       |          |          | √      |

| I2C/GPIO                                      | √        | √        | √      |

| Legacy Cables                                 | √        | √        | √      |

| VBUS Detection                                |          | √        | √(UFP) |

| VCONN                                         | √        |          | √(DFP) |

| USB 3.1 G1 and G2 SS mux                      | √        | √        | √      |

| Adaptive common mode tracking for SS channels | √        | √        | √      |

#### 7.3.1 DFP/Source – Downstream Facing Port

The HD3SS3220 can be configured as a DFP only by pulling the PORT pin high through a resistance to VDD5. The HD3SS3220 device can also be configured as a DFP-only device by changing the MODE\_SELECT register default setting with PORT pin left floating. In DFP mode, the HD3SS3220 constantly presents  $R_{(p)}$  on both CC lines. In this mode, the HD3SS3220 will initially advertise default USB Type-C current. The Type-C current can be adjusted through CURRENT\_MODE pin or I<sup>2</sup>C if the system wishes to increase the current advertisement. The HD3SS3220 will adjust the  $R_{(p)}$  resistors to match the desired advertisement.

A DFP monitors the voltage level on the CC pins looking for the  $R_{(d)}$  termination of a UFP. When a UFP is detected and HD3SS3220 is in the attached. SRC state, the HD3SS3220 pulls the ID pin low to indicate to the system the port is attached to a device (UFP). Additionally, when a UFP is detected, the HD3SS3220 supplies VCONN on the unconnected CC pin if  $R_{(a)}$  is also detected.

The following list describes the steps for enabling DFP through  $I^2C$ :

- 1. Write a 1'b1 to DISABLE\_TERM register (address 0x0A bit 0)

- 2. Write a 2'b10 to MODE SELECT register (address 0x0A bits 5:4)

- 3. Write a 1'b0 to DISABLE TERM register (address 0x0A bit 0)

When configured as a DFP, the HD3SS3220 can operate with older USB Type-C 1.0 devices except for a USB Type-C 1.0 DRP device. The HD3SS3220 cannot operate with a USB Type-C 1.0 DRP device. This limitation is a result of a backwards compatibility problem between USB Type-C 1.1 DFP and a USB Type-C 1.0 DRP.

#### Note

Upon detecting a UFP device, HD3SS3220 will keep ID pin high if VBUS is not at VSafe0V. Once VBUS is at VSafe0V, the HD3SS3220 will assert ID pin low. This is done to enforce Type-C requirement that VBUS must be at VSafe0V before re-enabling VBUS.

#### 7.3.2 UFP/Sink - Upstream Facing Port

The HD3SS3220 can be configured as a UFP only by pulling the PORT pin low to GND. In UFP mode, the HD3SS3220 constantly presents Rd (pull-down resistors) on both CC pins.

In UFP mode, the HD3SS3220 monitors the voltage level at the CC pins for attachment of a DFP and also to determine Type-C current advertisement by the connected DFP. The HD3SS3220 will debounce the CC pins and wait for VBUS detection before successful attachment. As a UFP, the HD3SS3220 will detect and communicate the DFP's advertised current level to the system through the OUT1 and OUT2 pins if in GPIO mode or through the I2C CURRENT MODE DETECT register once in the Attached.SNK state.

The following list describes the steps for enabling DFP through I<sup>2</sup>C:

- 1. Write a 1'b1 to DISABLE\_TERM register (address 0x0A bit 0)

- 2. Write a 2'b10 to MODE SELECT register (address 0x0A bits 5:4)

- 3. Write a 1'b0 to DISABLE TERM register (address 0x0A bit 0)

#### 7.3.3 DRP - Dual Role Port

The HD3SS3220 can be configured to operate as DRP when the PORT pin is left floating on the PCB. In DRP mode, the HD3SS3220 toggles between presenting as a DFP (Rp on both CC pins) and presenting as a UFP (Rd on both CC pins according to USB Type-C specification.

When presenting as a DFP, the HD3SS3220 monitors the voltage level on the CC pins looking for the  $R_{(d)}$  termination of a UFP. When a UFP is detected and HD3SS3220 is in the attached. SRC state, the HD3SS3220 pulls the ID pin low to indicate to the system the port is attached to a sink (UFP). Additionally, when a UFP is detected, the HD3SS3220 supplies VCONN on the unconnected CC pin if Ra is also detected. In DFP mode, the HD3SS3220 will initially advertise default USB Type-C current. The Type-C current can be adjusted through I<sup>2</sup>C if the system wishes to increase the amount advertised. HD3SS3220 will adjust the  $R_{(p)}$  resistors to match the desired Type-C current advertisement.

When presenting as a UFP, the HD3SS3220 monitors the CC pins for the voltage level corresponding to the Type-C current advertisement by the connected DFP. The HD3SS3220 will debounce the CC pins and wait for VBUS detection before successfully attaching. As a UFP, the HD3SS3220 detects and communicate the DFP advertised current level to the system through the OUT1 and OUT2 pins if in GPIO mode or through the I2C CURRENT\_MODE\_DETECT register once in the attached.SNK state.

The HD3SS3220 supports two optional Type-C DRP features called Try.SRC and Try.SNK. Products supporting dual-role functionality may have a requirement to be a source (DFP) or a sink (UFP) when connected to another dual-role capable product. For example, a dual-role capable notebook can be used as a source when connected to a tablet, or a cell phone could be a sink when connected to a notebook or tablet. When standard DRP products (products which don't support either Try.SRC or Try.SNK) are connected together, the role (UFP or DFP) outcome is not predetermined. These two optional DRP features provide a means for dual-role capable products to connect to another dual-role capable product in the role desired. Try.SRC and Try.SNK are only available when HD3SS3220 is configured in I<sup>2</sup>C mode. When operating in GPIO mode, the HD3SS3220 will always operate as a standard DRP.

The Try.SRC feature of the HD3SS3220 device provides a means for a DRP product to connect as a DFP when connected to another DRP product that doesn't implement Try.SRC. When two products which implement Try.SRC are connected together, the role outcome of either UFP or DFP is the same as a standard DRP. Try.SRC is enabled by changing I<sup>2</sup>C register SOURCE\_PREF to 2'b11. Once the register is changed to 2'b11, the HD3SS3220 will always attempt to connect as a DFP when attached to another DRP capable device.

#### 7.3.4 Cable Orientation and Mux Control

The HD3SS3220 detects the cable orientation by monitoring the voltage on the CC pins. When a voltage level within the proper threshold is detected on CC1, the DIR pin is high. When a voltage level within the proper threshold is detected on CC2, the DIR is pulled low. The DIR pin is an open drain output and a pull-up resistor must be installed. The cable orientation status is also be communicated by I<sup>2</sup>C for HD3SS3220. The device also controls the integrated SS mux to switch appropriate SS signals pairs (RX1/TX1 or RX2/TX2).

#### 7.3.5 Type-C Current Mode

Once a valid cable detection and attach have been completed, the DFP has the option to advertise the level of Type-C current a UFP can sink. The default current advertisement for HD3SS3220 can be configured using CURRENT\_MODE pin or I2C CURRENT\_MODE\_ADVERTISE register. When a different than default current is chosen, the device adjusts the R<sub>(p)</sub> resistors for the specified current level.

Table 7-2. Type-C Current Advertisement for GPIO and I<sup>2</sup>C Modes

| Type-C Current                                         | GPIO Mode (A                                 | ADDR pin NC)     | I <sup>2</sup> C Mode (ADDR pin H, L)                   |                                           |  |  |

|--------------------------------------------------------|----------------------------------------------|------------------|---------------------------------------------------------|-------------------------------------------|--|--|

|                                                        | UFP (PORT pin L)                             | DFP (PORT pin H) | UFP                                                     | DFP                                       |  |  |

| Default – 500mA for<br>(USB2.0)<br>900 mA for (USB3.1) | Detected current mode provided through OUT1/ | CURRENT_MODE=L   | Detected current mode provided through I <sup>2</sup> C | Advertisement selected                    |  |  |

| Mid – 1.5 A                                            | OUT2                                         | CURRENT_MODE=M   | register                                                | through writing I <sup>2</sup> C register |  |  |

| High – 3 A                                             |                                              | CURRENT_MODE=H   |                                                         |                                           |  |  |

## 7.3.6 Accessory Support

HD3SS3220 supports audio and debug accessories in UFP, DFP and DRP mode by default. Audio and debug accessory support is provided through reading of I2C registers. Audio accessory is also support through GPIO mode with INT N/OUT3 pin (audio accessory has been detected when INT N/OUT3 is low).

#### Note

If UFP accessory support is not needed in your application, UFP accessory support can be disabled by setting the DISABLE\_UFP\_ACCESSORY register.

## 7.3.7 Audio Accessory

Audio accessory mode is supported through two types of adapters. First, the passive audio adapter can be used to convert the Type-C connector into an audio port. In order to effectively detect the passive audio adapter, the HD3SS3220 must detect a resistance  $< R_{(a)}$  on both the CC pins.

Secondly, a charge through audio adapter can be used. The primary difference between a passive and charge through adapter is that the charge through adapter supports supplying 500 mA of current over VBUS. The charge through adapter contains a receptacle and a plug. The plug shall act as a DFP and supply VBUS when it sees it's connected.

When HD3SS3220 is configured in GPIO mode, OUT3 pin shall be used to determine if an Audio Accessory is connected. When an Audio Accessory is detected, the OUT3 pin is pulled low.

#### 7.3.8 Debug Accessory

Debug is an additional state supported by USB Type-C. The specification does not define a specific user scenario for this state, but the end user could use debug accessory mode to enter a test state for production specific to the application. Charge through debug accessory is not supported by HD3SS3220 when in DRP or UFP mode. The HD3SS3220 when configured as a DFP-only or as a DRP acting as a DFP detects a debug accessory which presents  $R_{(d)}$  on both CC1 and CC2 pins. The HD3SS3220 sets ACCESSORY\_CONNECTED register to 3'b110 to indicate a UFP debug accessory. The HD3SS3220 when configured as a UFP-only or as a DRP acting as a UFP detects a debug accessory which presents  $R_{(p)}$  on both CC1 and CC2 pins. The HD3SS3220 sets ACCESSORY\_CONNECTED register to 3b'111 to indicate a DFP debug accessory.

#### 7.3.9 VCONN support for Active Cables

The HD3SS3220 supplies VCONN to active cables when configured in DFP mode or DRP acting as a DFP. VCONN is provided only when it is determined that the unconnected CC pin is terminated to a resistance,  $R_{(a)}$ , and after a UFP is detected and the attached. SRC state is entered. VCONN is supplied from VDD5 through a low resistance power FET out to the unconnected CC pin. VCONN is removed when a detach event is detected and the active cable is removed.

HD3SS3220 provides a current limiting function which will disconnect VCONN when the current being drawn from a device is above the max allowed for VCONN. When a VCONN fault has occurred, the VCONN flag in the

I<sup>2</sup>C register is set and HD3SS3220 stops supplying VCONN (switch turns off), until the register flag has been cleared. If HD3SS3220 is in GPIO mode when a fault occurs, the VCONN switch is turned off and HD3SS3220 will not supply VCONN until a port detach and re-attach occurs.

#### 7.3.10 I<sup>2</sup>C and GPIO Control

The HD3SS3220 can be configured for I<sup>2</sup>C or GPIO using the ADDR pin. The ADDR pin is a 3-level control pin. When the ADDR pin is left floating (NC), the HD3SS3220 is in GPIO mode. When the ADDR pin is pulled High, the HD3SS3220 is in I<sup>2</sup>C mode with address bit 6 equal to 1. When the ADDR pin is pulled low, the HD3SS3220 is in I<sup>2</sup>C mode with address bit 6 equal to 0.

All outputs for HD3SS3220 are open drain configuration.

The OUT1 and OUT2 pins are used to output the Type-C current mode when in GPIO mode. Additionally, the OUT3 pin is used to communicate the Audio Accessory mode in GPIO mode. The specifics of the output pins can be found in Table 7-3.

Table 7-3. Simplified Operation for OUT1 and OUT2

| OUT1 | OUT2 | ADVERTISEMENT |

|------|------|---------------|

| Н    | Н    | Default       |

| Н    | L    | Default       |

| L    | Н    | Medium        |

| L    | L    | High          |

When operating in I<sup>2</sup>C mode, HD3SS3220 uses the SCL and SDA lines for clock and data and the INT pin. The INT pin communicates an interrupt, or a change in I<sup>2</sup>C registers, to the system. The INT pin will be pulled low when the HD3SS3220 updates the registers with new information. The INT N pin is open drain. The INTERRUPT STATUS register should be set when the INT pin is pulled low. The customer shall write to I<sup>2</sup>C to clear the INTERRUPT STATUS register.

When operating in GPIO mode, the OUT3 pin is used in place of INT pin to determine if an Audio Accessory has been detected and attached. The OUT3 pin is pulled low when an Audio Accessory is detected.

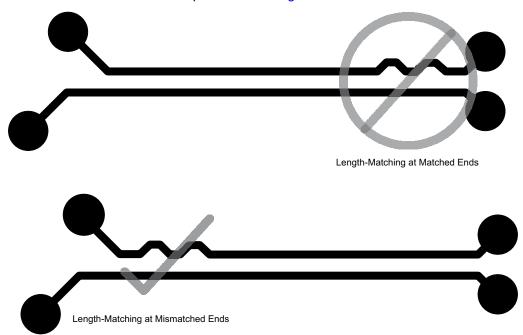

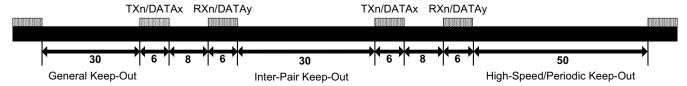

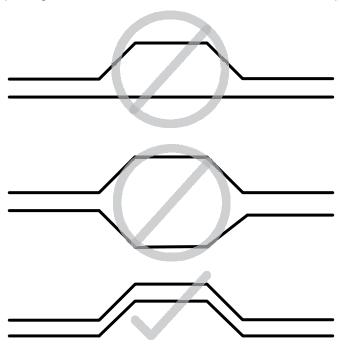

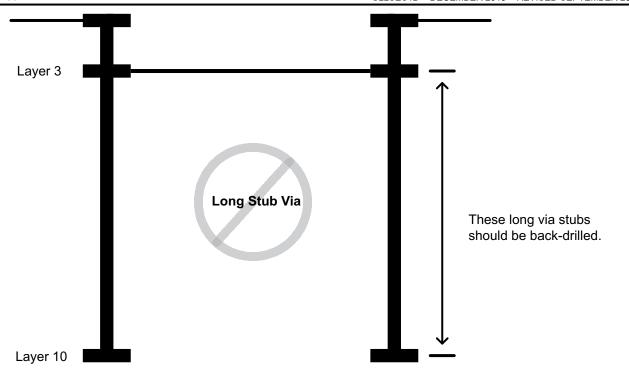

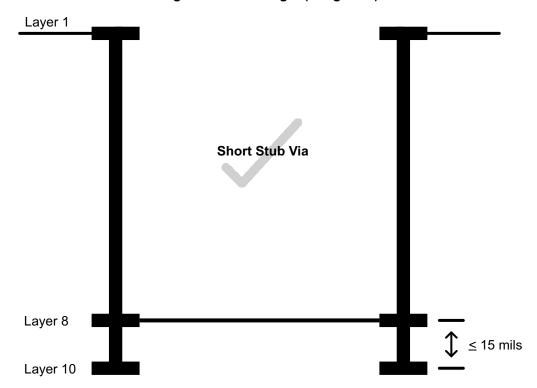

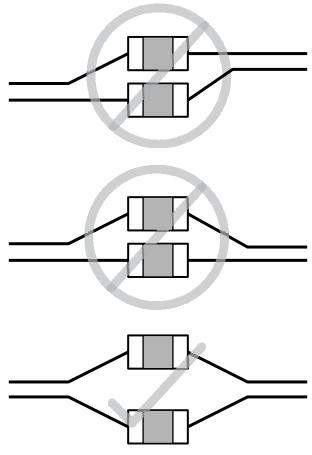

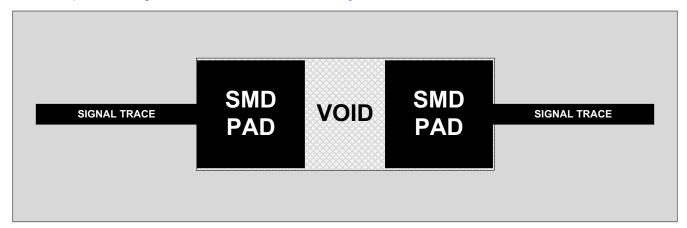

#### Note