**US** Headquarters 2950 Red Hill Ave, Costa Mesa California, USA 92626

Office: 714.913.2200 Fax: 714.913.2202

www.vikingtechnology.com

## **Datasheet for:**

# SDHC/SDXC UHS104 microSD Cards

PSFUSDxxxxCxxxxx\_W

microSD Cards

## **Legal Information**

Copyright© 2020 Sanmina Corporation. All rights reserved. The information in this document is proprietary and confidential to Sanmina Corporation. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from Sanmina. Sanmina reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of Sanmina to provide notification of such revision or change.

Sanmina provides this documentation without warranty, term or condition of any kind, either expressed or implied, including, but not limited to, expressed and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made. In no event will Sanmina be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. Sanmina may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

Sanmina, Viking Technology, Viking Modular Solutions, and the Viking logo are trademarks of Sanmina Corporation. Other company, product or service names mentioned herein may be trademarks or service marks of their respective owners.

## **Revision History**

| Dete                                | Revisio                                           | Description                                                                                 | Charled by |

|-------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------|------------|

| Date                                | n                                                 | Description                                                                                 | Checked by |

| 4/15/19 A Remove references to tos, |                                                   | Revised from PSUSDxxxxCxxxxxC_A Remove references to tos, change performance. Change to TLC |            |

|                                     |                                                   | Add new PN's per PSG 9/25/19. Add<br>VWFUSD016GCEDWW PN per agile                           |            |

| 10/14/19                            | С                                                 | Add VWFUSD016GCEDWW PN per agile                                                            |            |

| 11/1/19 D Add specs for 256GB       |                                                   | Add specs for 256GB                                                                         |            |

| 11/15/19                            | Revise VWFUSD8192CEWWW to 11/15/19 E (-25to+85°C) |                                                                                             |            |

| 1/21/20                             | F                                                 | Add VWUSD128GCEHWW3C<br>VWUSD064GCE5WW3C                                                    |            |

|                                     |                                                   |                                                                                             |            |

## Ordering Information for the SDHC/SDXC UHS104 microSD Cards

| VikingPart#      | Interface    | Temp           | GB  | Client/Ent | NAND            |

|------------------|--------------|----------------|-----|------------|-----------------|

| VWFUSD8192CEWWW  | microSD Card | (-25 to +85ºC) | 8   | Client     | TSB BiCS 3D     |

| VWFUSD016GCEDWW  | microSD Card | (-25 to +85ºC) | 16  | Client     | TSB BiCS 3D     |

| VWUSD032GCE1WW3C | microSD Card | (-25 to +85ºC) | 32  | Client     | TSB BiCS 3D TLC |

| VWUSD064GCE5WW3C | microSD Card | (-25 to +85ºC) | 64  | Client     | TSB BiCS 3D TLC |

| VWUSD128GCEHWW3C | microSD Card | (-25 to +85ºC) | 128 | Client     | TSB BiCS 3D TLC |

| VWFUSD064GCEAMWL | microSD Card | (-25 to +85°C) | 64  | Client     | SanDisk MLC     |

| VWFUSD128GCEZMWL | microSD Card | (-25 to +85ºC) | 128 | Client     | SanDisk MLC     |

| VWFUSD256GCECMWL | microSD Card | (-25 to +85°C) | 256 | Client     | SanDisk MLC     |

#### Notes:

- Contact Viking for availability date

The lowercase letters x,y and z are wildcard characters that indicate product or customer specific information

- 3. Refer to the Viking part number coversheet or PN decoder for details.

## **Table of Contents**

| 1                                                           | INTRODUCTION 8                                                                                                                                                                                                      |                                                          |  |  |  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

| 1.1                                                         | FEATURES 8                                                                                                                                                                                                          |                                                          |  |  |  |  |  |

| 2                                                           | MICROSD CARD STANDARDS COMPATIBILITY                                                                                                                                                                                | 9                                                        |  |  |  |  |  |

| 3                                                           | PHYSICAL CHARACTERISTICS                                                                                                                                                                                            | 9                                                        |  |  |  |  |  |

| 3.1                                                         | Package Characteristics                                                                                                                                                                                             | 9                                                        |  |  |  |  |  |

| 3.2                                                         | Environmental Characteristics                                                                                                                                                                                       | 9                                                        |  |  |  |  |  |

| 3.3                                                         | Physical Characteristics                                                                                                                                                                                            | 10                                                       |  |  |  |  |  |

| 4                                                           | ELECTRICAL INTERFACE                                                                                                                                                                                                | 10                                                       |  |  |  |  |  |

| 4.1                                                         | Pin Assignment                                                                                                                                                                                                      | 10                                                       |  |  |  |  |  |

| <b>4.2</b> 4.2                                              | microSD Card Bus Topology 2.1 SD Bus Mode protocol                                                                                                                                                                  | <b>11</b><br>11                                          |  |  |  |  |  |

| 4.3                                                         | Initialization                                                                                                                                                                                                      | 17                                                       |  |  |  |  |  |

| 4.4<br>4.4<br>4.4                                           | Electrical Characteristics  4.1 Absolute Maximum Conditions  4.2 DC Characteristics  4.3 AC Characteristics (Default Speed)  4.4 AC Characteristics (High Speed)  4.5 AC Characteristics (Ultra High Speed; UHS104) | <b>21</b><br>21<br>22<br>25<br>27<br>28                  |  |  |  |  |  |

| 5                                                           | CARD INTERNAL INFORMATION                                                                                                                                                                                           | 33                                                       |  |  |  |  |  |

| 5.1                                                         | Security Information                                                                                                                                                                                                | 33                                                       |  |  |  |  |  |

| 5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2 | 2.2 CID Register 2.3 CSD Register 2.4 RCA Register 2.5 DSR Register 2.6 SCR Register 2.7 Card Status 2.8 SD Status                                                                                                  | 33<br>34<br>35<br>35<br>37<br>37<br>37<br>38<br>40<br>41 |  |  |  |  |  |

| <b>5.3</b>                                                  | Logical Format  3.1 microSD card Capacities                                                                                                                                                                         | <b>42</b><br>43                                          |  |  |  |  |  |

| 6 | SD SPECIFICATION COMPLIANCE        | 43 |

|---|------------------------------------|----|

| 7 | RELIABILITY GUIDANCE               | 43 |

| 8 | MICROSD CARD MECHANICAL DIMENSIONS | 45 |

## **Table of Tables**

| Table 1-1: Features                                                            | 8        |

|--------------------------------------------------------------------------------|----------|

| Table 4-1: microSD Card Pin Assignment                                         | 10       |

| Table 4-2: SD Mode Command Set ( + = Implemented, - = Not Implemented)         | 12       |

| Table 4-3: SPI Mode Command Set ( + = Implemented, - = Not Implemented)        | 15       |

| Table 4-4:S18R and S18A Combinations                                           | 19       |

| Table 4-5: Absolute Maximum Conditions                                         | 21       |

| Table 4-6: DC Characteristics                                                  | 22       |

| Table 4-7: Bus Operating Conditions - Signal Line's Load                       | 24       |

| Table 4-8: Threshold Level 1.8V Signaling                                      | 24       |

| Table 4-9: Threshold Level 1.8V Signaling                                      |          |

| Table 4-10: Bus Timing - Parameters Values (Default Speed)                     |          |

| Table 4-11: Bus Timing - Parameters Values (High Speed)                        |          |

| Table 4-12: Clock Signal Timing of SDR104, SDR50, SDR25, SDR12                 | 29       |

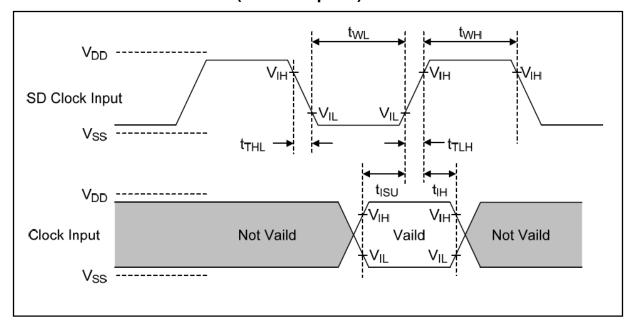

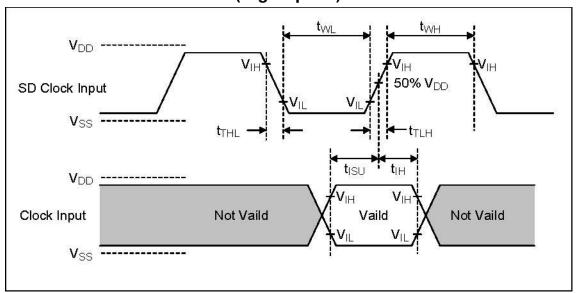

| Table 4-13: Clock input Timing of SDR104, SDR50, SDR25, SDR12                  | 29       |

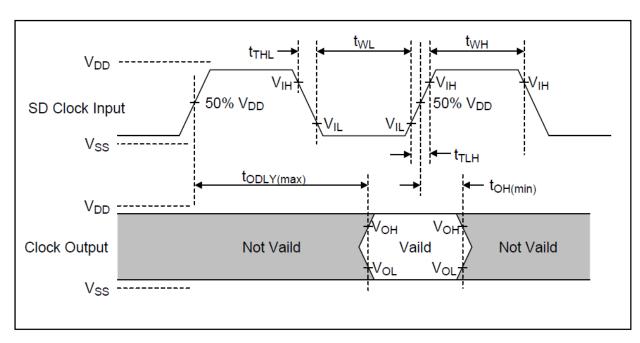

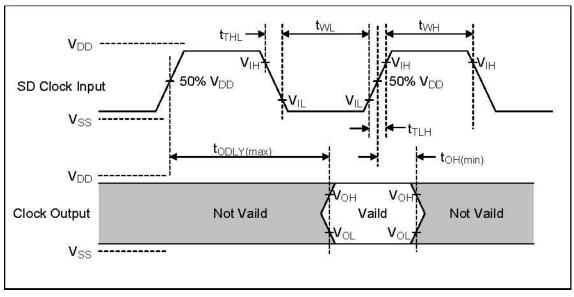

| Table 4-14: Output Timing of Fixed Data Window (SDR50, SDR25, SDR12)           |          |

| Table 4-15: Output Timing of Variable Data Window (SDR104)                     | 31       |

| Table 4-16: Clock Signal Timing of DDR50                                       | 21       |

| Table 4-17: BUS Timings – Parameters Values (DDR50 mode)                       |          |

| Table 5-1: microSD Card Registers                                              | 32       |

| Table 5-2: OCR register definition                                             | 34       |

| Table 5-3: CID register                                                        |          |

| Table 5-4: CSD register                                                        | 35       |

| Table 5-5: The SCR Fields                                                      | 37       |

| Table 5-6: Card Status                                                         |          |

| Table 5-7: SD Status                                                           |          |

| Table 5-8: Switch Function Status                                              | 40<br>41 |

|                                                                                |          |

| Table of Figures                                                               |          |

| Table of Figures                                                               |          |

| Figure 1-1: Top View                                                           | 9        |

| Figure 4-1: microSD Card Pin Assignment (Back view of the Card)                |          |

| Figure 4-2: Bus Connection Diagram (SD Mode)                                   | 12       |

| Figure 4-3: Bus Connection Diagram (SPI Mode)                                  | 15       |

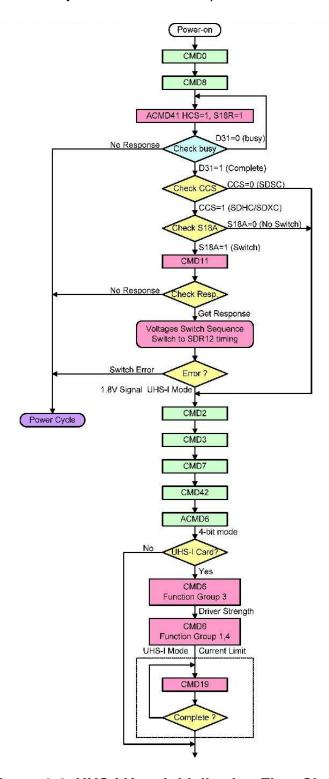

| Figure 4-4: UHS-I Host Initialization Flow Chart                               | 17       |

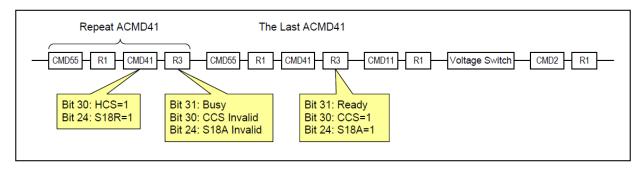

| Figure 4-5. ACMD41 Timing Followed by Signal Voltage Switch Sequence           | 18       |

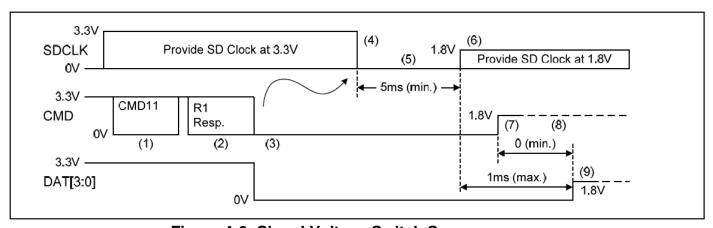

| Figure 4-6: Signal Voltage Switch Sequence                                     | 20       |

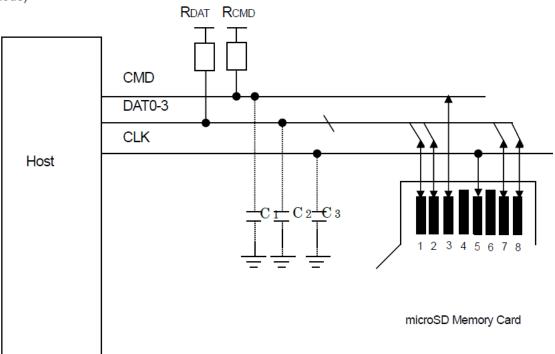

| Figure 4-7: microSD Card Connection Diagram                                    |          |

| Figure 4-8: Card Input Timing (Default Speed Mode)                             | 25       |

| Figure 4-9: Card Output Timing (Default Speed Mode)                            |          |

| Figure 4-10: Card Input Timing (High Speed Card)                               | 27       |

| Figure 4-11: Card Output Timing (High Speed Card)                              | 27       |

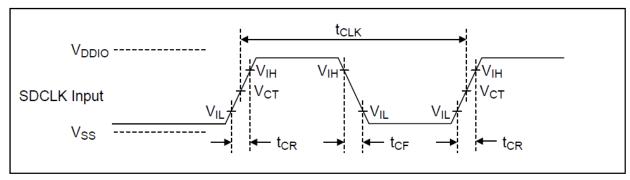

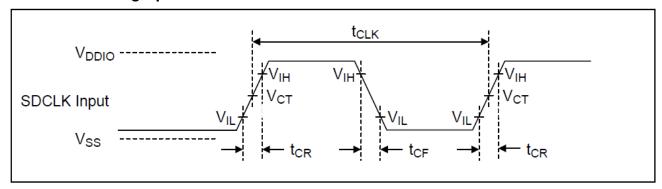

| Figure 4-12: Clock Signal Timing                                               | 28       |

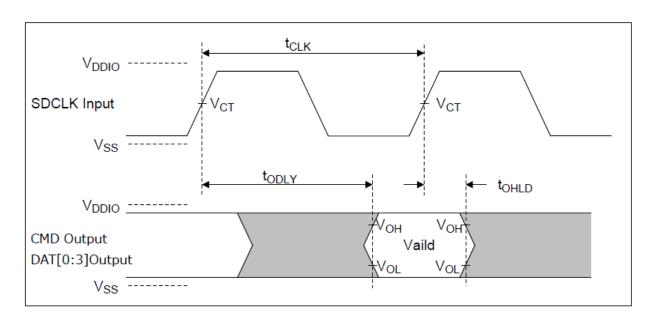

| Figure 4-13: Clock Input Timing                                                | 29       |

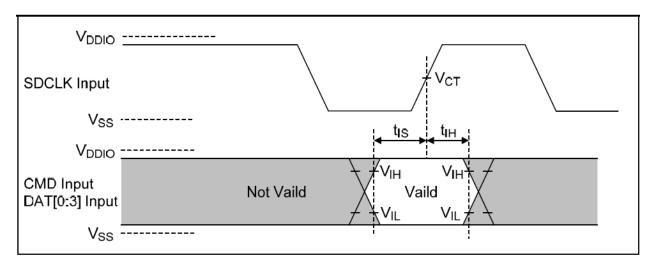

| Figure 4-14: Output Timing of Fixed Window                                     | 30       |

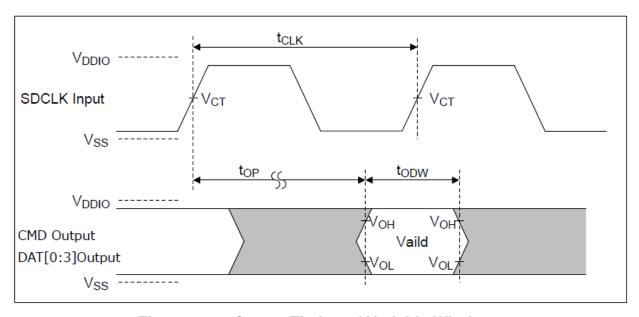

| Figure 4-15: Output Timing of Variable Window                                  |          |

| Figure 4-16: Clock Signal Timing                                               | 31       |

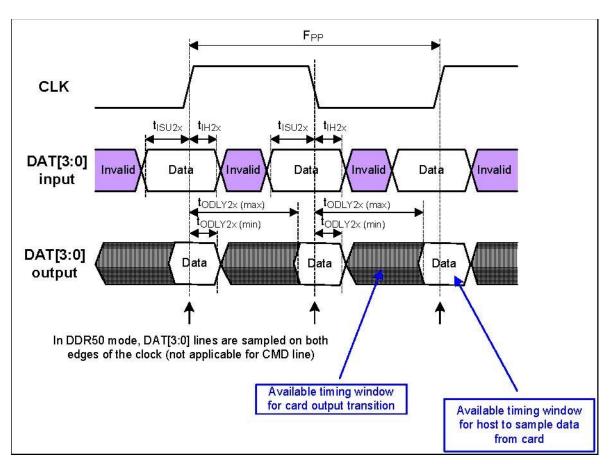

| Figure 4-17: Timing Diagram DAT Inputs/Outputs Referenced to CLK in DDR50 Mode | 32       |

| · · · · · · · · · · · · · · · · · ·                                            |          |

#### 1 Introduction

This data sheet describes the specifications of the SDHC/SDXC Standard microSD Card with UHS104 SD Bus mode. The SDHC/SDXC microSD Cards are a Memory Card of Small and Thin with SDMI compliant Security method. (SDMI: Secure Digital Music Initiative) Contents in the Card can be protected by CPRM based security. This contents security can be accomplished by SDHC/SDXC Card, host, and security application software combinations.

#### 1.1 FEATURES

Table 1-1: Features

| Media Format                    |                                                                                                                                                                                                                     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 |                                                                                                                                                                                                                     |

| microSD Memory Card<br>Standard | Compliant with the SD Memory Card Standard Ver. 4.20, UHS104                                                                                                                                                        |

| Staridard                       |                                                                                                                                                                                                                     |

| Security Functions              | SD Security Specification Ver.2.00 Compliant (CPRM Based) *CPRM: Contents Protection for Recording Media Specification                                                                                              |

| Logical Format                  | SD File System Specification Ver.2.00 Compliant SDHC Card = FAT32, SDXC Card = exFAT                                                                                                                                |

| Electrical Features             |                                                                                                                                                                                                                     |

| Operating Voltage               | VDD = 2.7V(min), 3.3V(Typ), 3.6V(max)                                                                                                                                                                               |

| Operating Current               | SDR104 Write: 140mA(max) SDR104 Read: 150mA(max)                                                                                                                                                                    |

| SD Interface                    | DS : Signaling Voltage = 3.3V(Typ), SDCLK = 25MHz HS : Signaling Voltage = 3.3V(Typ), SDCLK = 50MHz                                                                                                                 |

| UHS-I Interface                 | Ultra High Speed: UHS104: Signaling Voltage = 1.8V(Typ), SDCLK = 208MHz UHS50: Signaling Voltage = 1.8V(Typ), SDCLK = 100MHz@SDR100 / 50MHz@DDR50 Supported UHS-I bus modes are SDR104, SDR50, DDR50, SDR25, SDR12. |

| Physical Features               |                                                                                                                                                                                                                     |

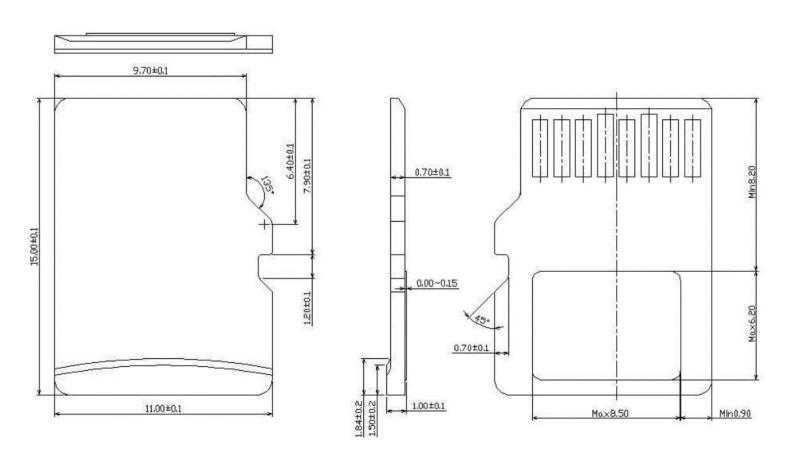

| Physical Package size /Mass     | L: 15, W: 11, T: 1 (mm), Weight: 0.3g (typ.) SD Physical Layer Specification Ver.3.01 Compliant                                                                                                                     |

| Durability                      | Compliant with SD Physical Layer Specification Ver.3.01 and microSD Memory Card specification 2.01 Compliant                                                                                                        |

| RoHS                            | Compliant with RoHS regulations (DIRECTIVE 2011/65/EU)                                                                                                                                                              |

| Performance Features            |                                                                                                                                                                                                                     |

| Maximum access speed            | Bus mode Sequential Write = 50 MB/s Sequential Read = 80 MB/s                                                                                                                                                       |

| Speed Class                     | UHS Speed Class = U3 SD Speed Class = C10, Class 4                                                                                                                                                                  |

Figure 1-1: Top View

## 2 microSD Card Standards Compatibility

This microSD Memory Card Specification is compliant with:

- PHYSICAL LAYER SPECIFICATION Ver.3.01 (Part1) (Except for Mechanical Specification)

- FILE SYSTEM SPECIFICATION Ver.2.00. (Part2)

- SECURITY SPECIFICATION Ver.2.00. (Part3)

- microSD Card Memory Card Specification Version 2.01

## 3 Physical Characteristics

#### 3.1 Package Characteristics

- 1. Mold Material: Epoxy Resin+Silicon Dioxide

- 2. Flameproof Grade: V-0(UL94)

- 3. Heatproof Temperature: approx.400 degrees

#### 3.2 Environmental Characteristics

The standard Operation Conditions are:

- Absolute Maximum Temperature Range

- Humidity less than RH = 95 %, Non condensed

The standard Storage Conditions are:

- Maximum Temperature Range:

- Humidity less than RH = 93%, Non condensed

$Ta = -25 \text{ to } +85^{\circ}C$

$Ta = 25^{\circ}C$

Tstg = -40 to +85°C

$Ta = 40^{\circ}C$

#### 3.3 Physical Characteristics

#### 1) Hot Insertion or Removal

The microSD Card can be removed or inserted without power off from the host system as described in the SD Physical Layer Specification 6.1

The connector will recognize the Hot Insertion or Removal is defined in the 6.2 of the PHYSICAL LAYER SPECIFICATION.

#### 2) Mechanical Write Protect Switch

The microSD memory Card has no mechanical write protect switch.

#### 4 Electrical Interface

#### 4.1 Pin Assignment

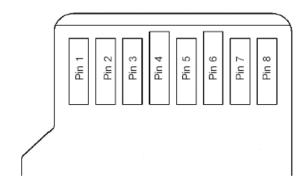

The table below describes the pin assignment of the microSD card. The following figure describes the pin assignment of the microSD card. Please refer to the detail descriptions by SD Card Physical Layer Specification.

Figure 4-1: microSD Card Pin Assignment (Back view of the Card)

**Table 4-1: microSD Card Pin Assignment**

|     | SD Mode         |         |                              |                 | SPI     | Mode                           |

|-----|-----------------|---------|------------------------------|-----------------|---------|--------------------------------|

| Pin | Name            | Ю Туре  | Description                  | Name            | ІО Туре | Description                    |

| 1   | DAT2            | I/O/PP  | Data Line[Bit2]              | RSV             |         |                                |

| 2   | CD/<br>DAT3     | I/O/ PP | Card Detect/ Data Line[Bit3] | CS              | I       | Chip Select<br>(Negative True) |

| 3   | CMD             | PP      | Command/Response             | DI              | I       | Data In                        |

| 4   | V <sub>DD</sub> | S       | Supply Voltage               | V <sub>DD</sub> | S       | Supply Voltage                 |

| 5   | CLK             | I       | Clock                        | SCLK            | I       | Clock                          |

| 6   | Vss             | S       | Ground                       | Vss             | S       | Ground                         |

| 7   | DAT0            | I/O/PP  | Data Line[Bit0]              | DO              | O/PP    | Data Out                       |

| 8   | DAT1            | I/O/PP  | Data Line[Bit1]              | RSV             | -       | Reserved(*)                    |

#### Notes:

S: Power Supply

I: Input

O: Output using push-pull drivers

PP: I/O using push-pull drivers

(\*) These signals should be pulled up by host side with 10-100k ohm resistance in the SPI Mode.

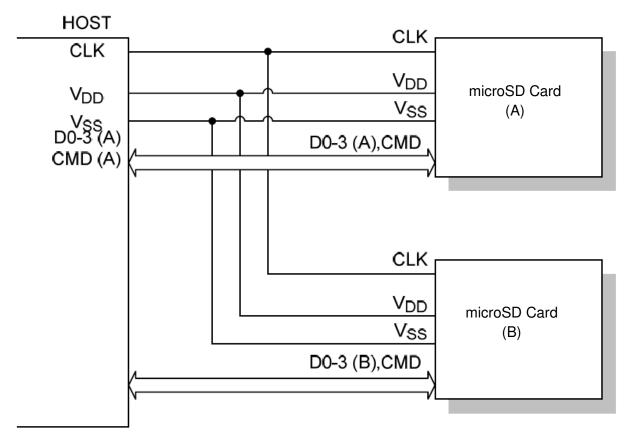

#### 4.2 microSD Card Bus Topology

The device supports two alternative communication protocols: SD and SPI Bus Mode. It is as same as standard microSD memory cards. Host System can choose either one of modes. Same Data of the device can read and write by both modes. SD Mode allows the 4-bit high performance data transfer. SPI Mode allows easy and common interface for SPI channel. The disadvantage of this mode is loss of performance, relatively to the SD mode.

#### 4.2.1 SD Bus Mode protocol

The SD bus allows the dynamic configuration of the number of data line from 1 to 4 Bidirectional data signal. After power up by default, the Device will use only DATO. After initialization, host can change the bus width. Multiplied microSD cards connections are available to the host. Common VDD, VSS and CLK signal connections are available in the multiple connections. However, Command, Respond and Data lined (DATO-DAT3) shall be divided for each card from host. This feature allows easy tradeoff between hardware cost and system performance. Communication over the SD bus is based on command and data bit stream initiated by a start bit and terminated by stop bit.

#### Command:

Commands are transferred serially on the CMD line. A command is a token to starts an operation from host to the card. Commands are sent to an addressed single card (addressed Command) or to all connected cards (Broad cast command).

#### Response:

Responses are transferred serially on the CMD line. A response is a token to answer to a previous received command. Responses are sent from an addressed single card or from all connected cards.

#### Data:

Data can be transfer from the card to the host or vice versa. Data is transferred via the data lines.

Figure 4-2: Bus Connection Diagram (SD Mode)

CLK Host card Clock signal

CMD Bi-directional Command/ Response Signal

DAT0 - DAT3 4 Bi-directional data signal

VDD Power supply

VSS GND

Table 4-2: SD Mode Command Set ( + = Implemented, - = Not Implemented)

| CMD<br>Index | Abbreviation         | Implementation | Note                             |

|--------------|----------------------|----------------|----------------------------------|

| CMD0         | GO_IDLE_STATE        | +              |                                  |

| CMD2         | ALL_SEND_CID         | +              |                                  |

| CMD3         | SEND_RELATIVE_ADDR   | +              |                                  |

| CMD4         | SET_DSR              | -              | DSR Register is not implemented. |

| CMD6         | SWITCH_FUNC          | +              |                                  |

| CMD7         | SELECT/DESELECT_CARD | +              |                                  |

| CMD8         | SEND_IF_COND         | +              |                                  |

| CMD9         | SEND_CSD             | +              |                                  |

| CMD10        | SEND_CID             | +              |                                  |

| CMD11        | VOLTAGE_SWITCH       | +              | UHS-I mode                       |

| CMD<br>Index | Abbreviation              | Implementation | Note                                                |

|--------------|---------------------------|----------------|-----------------------------------------------------|

| CMD12        | STOP_TRANSMISSION         | +              |                                                     |

| CMD13        | SEND_STATUS               | +              |                                                     |

| CMD15        | GO_INACTIVE_STATE         | +              |                                                     |

| CMD16        | SET_BLOCKLEN              | +              |                                                     |

| CMD17        | READ_SINGLE_BLOCK         | +              |                                                     |

| CMD18        | READ_MULTIPLE_BLOCK       | +              |                                                     |

| CMD19        | SEND_TUNING_PATTERN       | +              | UHS-I mode                                          |

| CMD20        | SPEED_CLASS_CONTROL       | +              | For SDHC/SDXC                                       |

| CMD23        | SET_BLOCK_COUNT           | +              |                                                     |

| CMD24        | WRITE_BLOCK               | +              |                                                     |

| CMD25        | WRITE_MULTIPLE_BLOCK      | +              |                                                     |

| CMD26        | Reserved for Manufacturer | +              |                                                     |

| CMD27        | PROGRAM_CSD               | +              |                                                     |

| CMD28        | SET_WRITE_PROT            | -              |                                                     |

| CMD29        | CLR_WRITE_PROT            | -              | Internal Write Protection is not implemented.       |

| CMD30        | SEND_WRITE_PROT           | -              |                                                     |

| CMD32        | ERASE_WR_BLK_START        | +              |                                                     |

| CMD33        | ERASE_WR_BLK_END          | +              |                                                     |

| CMD38        | ERASE                     | +              |                                                     |

| CMD42        | LOCK_UNLOCK               | +              |                                                     |

| CMD55        | APP_CMD                   | +              |                                                     |

| CMD56        | GEN_CMD                   | +              | This command is not specified.                      |

| CMD60        | Reserved for Manufacturer | +              |                                                     |

| CMD61        | Reserved for Manufacturer | +              |                                                     |

| CMD62        | Reserved for Manufacturer | +              |                                                     |

| ACMD6        | SET_BUS_WIDTH             | +              |                                                     |

| ACMD13       | SD_STATUS                 | +              |                                                     |

| ACMD22       | SEND_NUM_WR_BLOCKS        | +              |                                                     |

| ACMD23       | SET_WR_BLK_ERASE_COUNT    | +              |                                                     |

| ACMD41       | SD_SEND_OP_COND           | +              | 1.8V Signaling and XPC (SDXC Power Control) support |

| ACMD42       | SET_CLR_CARD_DETECT       | +              |                                                     |

| ACMD51       | SEND_SCR                  | +              |                                                     |

| ACMD18       | SECURE_READ_MULTI_BLOCK   | +              |                                                     |

| ACMD25       | SECURE_WRITE_MULTI_BLOCK  | +              |                                                     |

| ACMD26       | SECURE_WRITE_MKB          | +              |                                                     |

| ACMD38       | SECURE_ERASE              | +              |                                                     |

| ACMD43       | GET_MKB                   | +              |                                                     |

| ACMD44       | GET_MID                   | +              |                                                     |

| ACMD45       | SET_CER_RN1               | +              |                                                     |

| ACMD46       | GET_CER_RN2               | +              |                                                     |

| ACMD47       | SET_CER_RES2              | +              |                                                     |

| ACMD48       | GET_CER_RES1              | +              |                                                     |

| ACMD49       | CHANGE_SECURE_AREA        | -              |                                                     |

Notes:

- CMD28, 29 and CMD30 are optional commands.

- CMD4 is not implemented because DSR register (Optional Register) is not implemented.

- CMD56 is a vender specific command which is not defined in the standard card.

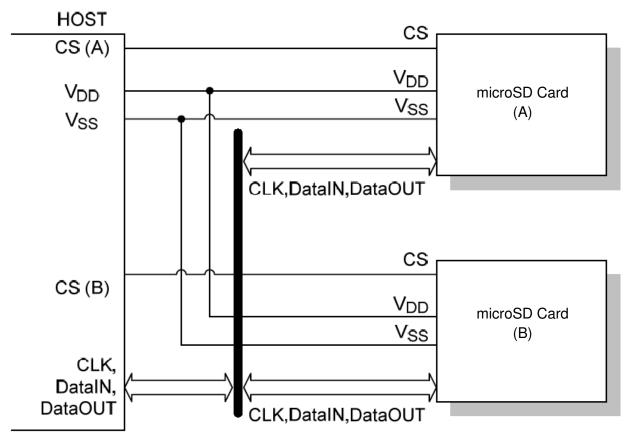

#### 6.2.2 SPI Bus mode Protocol

The SPI bus allows 1 bit Data line by 2-chanel (Data In and Out). The SPI compatible mode allows the MMC Host systems to use microSD card with little change. The SPI bus mode protocol is byte transfers. All the data token are multiples of the bytes (8-bit) and always byte aligned to the CS signal.

The advantage of the SPI mode is reducing the host design effort. Especially, the MMC host can be modified with little change. The disadvantage of the SPI mode is the loss of performance versus SD mode.

**Caution:** Please use SD Card Specification. DO NOT use MMC Specification. (For example, initialization is achieved by ACMD41, and be careful to Register. Register definition is different, especially CSD Register.)

Figure 4-3: Bus Connection Diagram (SPI Mode)

CS Card Select Signal

CLK Host card Clock signal

CMD Bi-directional Command/ Response Signal

DataIN Host to card data line

DataOUT Host to card data line

VDD Power supply

VSS GND

Table 4-3: SPI Mode Command Set ( + = Implemented, - = Not Implemented)

| CMD<br>Index | Abbreviation      | Implementation | Note               |

|--------------|-------------------|----------------|--------------------|

| CMD0         | GO_IDLE_STATE     | +              |                    |

| CMD1         | SEND_OP_COND      | +              | NOTICE: DO NOT USE |

| CMD6         | SWITCH_FUNC       | +              |                    |

| CMD8         | SEND_IF_COND      | +              |                    |

| CMD9         | SEND_CSD          | +              |                    |

| CMD10        | SEND_CID          | +              |                    |

| CMD12        | STOP_TRANSMISSION | +              |                    |

| CMD13        | SEND_STATUS       | +              |                    |

| CMD16        | SET_BLOCKLEN      | +              |                    |

| CMD<br>Index | Abbreviation              | Implementation | Note                                          |

|--------------|---------------------------|----------------|-----------------------------------------------|

| CMD17        | READ_SINGLE_BLOCK         | +              |                                               |

| CMD18        | READ_MULTIPLE_BLOCK       | +              |                                               |

| CMD24        | WRITE_BLOCK               | +              |                                               |

| CMD25        | WRITE_MULTIPLE_BLOCK      | +              |                                               |

| CMD26        | Reserved for Manufacturer | +              |                                               |

| CMD27        | PROGRAM_CSD               | +              |                                               |

| CMD28        | SET_WRITE_PROT            | -              |                                               |

| CMD29        | CLR_WRITE_PROT            | -              | Internal Write Protection is not implemented. |

| CMD30        | SEND_WRITE_PROT           | -              |                                               |

| CMD32        | ERASE_WR_BLK_START        | +              |                                               |

| CMD33        | ERASE_WR_BLK_END          | +              |                                               |

| CMD38        | ERASE                     | +              |                                               |

| CMD42        | LOCK_UNLOCK               | +              |                                               |

| CMD55        | APP_CMD                   | +              |                                               |

| CMD56        | GEN_CMD                   | +              | This command is not specified.                |

| CMD58        | READ_OCR                  | +              |                                               |

| CMD59        | CRC_ON_OFF                | +              |                                               |

| CMD60        | Reserved for Manufacturer | +              |                                               |

| ACMD13       | SD_STATUS                 | +              |                                               |

| ACMD22       | SEND_NUM_WR_BLOCKS        | +              |                                               |

| ACMD23       | SET_WR_BLK_ERASE_COUNT    | +              |                                               |

| ACMD41       | SD_SEND_OP_COND           | +              |                                               |

| ACMD42       | SET_CLR_CARD_DETECT       | +              |                                               |

| ACMD51       | SEND_SCR                  | +              |                                               |

| ACMD18       | SECURE_READ_MULTI_BLOCK   | +              |                                               |

| ACMD25       | SECURE_WRITE_MULTI_BLOCK  | +              |                                               |

| ACMD26       | SECURE_WRITE_MKB          | +              |                                               |

| ACMD38       | SECURE_ERASE              | +              |                                               |

| ACMD43       | GET_MKB                   | +              |                                               |

| ACMD44       | GET_MID                   | +              |                                               |

|              | SET_CER_RN1               | +              |                                               |

| ACMD46       | GET_CER_RN2               | +              |                                               |

| ACMD47       | SET_CER_RES2              | +              |                                               |

| ACMD48       | GET_CER_RES1              | +              |                                               |

#### Notes:

- CMD28, 29 and CMD30 are optional commands.

- CMD56 is a vender specific command which is not defined in the standard card.

#### 4.3 Initialization

The flow chart for UHS-I hosts and the sequence of commands to perform a signal voltage switch is shown below. Red and yellow boxes are new procedures to initialize the UHS-I card.

Figure 4-4: UHS-I Host Initialization Flow Chart

Figure 4-5: ACMD41 Timing Followed by Signal Voltage Switch Sequence

#### 1) POWER ON: Supply Voltage for initialization.

Host System applies the perating Voltage to the card. Apply more than 74 cycles of Dummy-clock to the microSD card.

#### 2) Select operation mode (SD mode or SPI mode)

In the case of SPI mode operation, the host should drive pin 1 (CD/DAT3) of the microSD Card I/F to a "Low" level. Then, issue CMD0. In the case of SD mode operation, the host should drive or detect pin 1 of the microSD Card I/F (Pull up register of pin 1 is pull up to "High" normally). The card maintains selected operation mode except re-issue of CMD0 or power on below is SD mode initialization procedure.

#### 3) Send Interface condition command (CMD8).

When the card is in the Idle state, the host shall issue CMD8 before ACMD41. In the argument, 'voltage supplied' is set to the host supply voltage and 'check pattern' is set to any 8-bit pattern. The card that accepted the supplied voltage returns R7 response. In the response, the card echoes back both the voltage range and check pattern set in the argument. If the card does not support the host supply voltage, it shall not return response and stays in the Idle state.

#### 4) Send initialization command (ACMD41).

When the signaling level is 3.3V, the host repeats an issue ACMD41 with HCS=1 and S18R=1 until the response indicates ready. The argument (HCS and S18R) of the first ACMD41 is effective but the all the following ACMD41 should be issued with the same argument. If Bit 31 indicates ready, the host needs to check CCS and S18A. The card indicates S18A=0, which means that the voltage switch is not allowed and the host needs to use the current signaling level.

Table 4-4:S18R and S18A Combinations

| Current Signaling<br>Level | 18R | S18A | Comment                                  |  |

|----------------------------|-----|------|------------------------------------------|--|

|                            | 0   | 0    | 1.8V signaling is not requested          |  |

| 3.3V                       | 1   | 0    | The card does not support 1.8V signaling |  |

|                            | 1   | 1    | Start signal voltage switch sequence     |  |

| 1.8V                       | Χ   | 0    | Already switched to 1.8V                 |  |

#### 5) Send voltage switch command (CMD11)

S18A=1 means that the voltage switch is allowed and host issues CMD11 to invoke voltage switch sequence. By receiving CMD11, the card returns R1 response and start voltage switch sequence. No response of CMD11 means that S18A was 0 and therefore the host should not have sent CMD11. Completion of voltage switch sequence is checked by high level of DAT[3:0]. Any bit of DAT[3:0] can be checked depends on ability of the host. The card enters UHS-I mode and card input and output timings are changed (SDR12 in default) when the voltage switch sequence is completed successfully.

#### 6) Send ALL SEND CID command (CMD2) and get the Card ID (CID)

## 7) Send SEND RELATIVE ADDR (CMD3) and get the RCA. RCA value is randomly changed by access, not equal zero.

8) Send SELECT / DESELECT CARD command (CMD7) and move to the transfer state. When entering tran state, CARD\_IS\_LOCKED status in the R1 response should be checked (it is indicated in the response of CMD7). If the CARD\_IS\_LOCKED status is set to 1 in the response of CMD7, CMD42 is required before ACMD6 tounlock the card. (If the card is locked, CMD42 is required to unlock the card.) If the card is unlocked, CMD42 can be skipped.

#### 9) Send SET BUS WIDTH command (ACMD6).

UHS-I supports only 4-bit mode. Host shall select 4-bit mode by ACMD6. If the card is locked, host needs to unlock the card by CMD42 in 1-bit mode and then needs to issue ACMD6 to change 4-bit bus mode. Operating in 1-bit mode is not assured.

#### 10) Set driver strength.

CMD6 mode 0 is used to query which functions the card supports, and to identify the maximum current consumption of the card under the selected functions. In case of UHS-I card, appropriate driver strength (default is Type-B buffer) is selected by CMD6 Function Group 3.

#### 11) Set UHS-I mode current limit.

UHS-I modes (Bus Speed Mode) is selected by CMD6 Function Group

1. Current limit is selected by CMD6 Function Group 4.

#### Maximum access settings:

SDR104 = (CMD6 Function Group 1 = 3-h, CMD6 Function Group 4 = 0-h(\*)) SDR50 = (CMD6 Function Group 1 = 2-h, CMD6 Function Group 4 = 0-h(\*)) DDR50 = (CMD6 Function Group 1 = 4-h, CMD6 Function Group 4 = 0-h(\*)) (\*) The Current Limit is default value (200mA).

#### Note:

Function Group 4 is defined as Current Limit switch for SDR50, SDR104. The Current Limit does not act on the card in SDR12 and SDR25. The default value of the Current Limit is 200mA (minimum setting). Then after selecting one of SDR50, SDR104 mode by Function Group 1, host needs to change the Current Limit to enable the card to operate in higher performance. This value is determined by a host power supply capability to the card, heat release method taken by a host and the maximum current of a connector.

#### 12) Tuning of sampling point

CMD19 sends a tuning block to the host to determine sampling point. In SDR50 and SDR104 modes, if tuning of sampling point is required, CMD19 is repeatedly issued until tuning is completed. Then the Host can access the Data between the microSD card as a storage device.

#### **Application Notes:**

- 1.The host shall set ACMD41 timeout to more than 1 second to abort repeat of issuing ACMD41 when the card does not indicate ready. The timeout count starts from the first ACMD41 which is set voltage window in the argument.

- 2.Once the signal voltage is switched to 1.8V, the card continues 1.8V signaling regardless of CMD0. Power cycle resets the signal voltage to 3.3V. After switching 1.8V singling, the card cannot be changed to SPI mode.

- 3. Timing to Switch Signal Voltage To change signaling level at the same time between host and card, signal voltage switch sequence is invoked by CMD11 as shown in the figure below. CMD11 is issued only when S18A=1 in the response of ACMD41.

Figure 4-6: Signal Voltage Switch Sequence

#### Steps that the host takes to start a voltage switch sequence.

- 1. The host issues CMD11 to start voltage switch sequence.

- 2. The card returns R1 response.

- 3. The card drives CMD and DAT[3:0] to "low" immediately after the response.

- 4. The host stops supplying SDCLK. The card shall start switching voltage after host stops SDCLK. The

- time to stop SDCLK is not specified. The host can detect whether the sequence starts by checking signal level of either one of CMD, DAT[3:0]. What signal should be checked will depend on the ability of the host. If low level is not detected, the host should abort the sequence and execute power cycle.

- 5. 1.8V output of voltage regulator in card shall be stable within 5ms. The Host keeps SDCLK low at least 5ms. This means that 5ms is the maximum for the card and the minimum for the host.

- 6. After 5ms from (step 4) and host voltage regulator is stable, the host starts providing SDCLK at 1.8V. The card can check whether SDCLK voltage is 1.8V.

- 7. By detecting SDCLK, the card drives CMD to high at 1.8V for at least one clock and then stops driving (tri-state). CMD is triggered by rising edge of SDCLK (SDR timing).

- 8. The card can check whether host drives CMD to 1.8V through the host pull-up resister.

- 9. If switching to 1.8V signaling is completed successfully, the card drives DAT[3:0] to high at 1.8V at least one clock and then stop driving (tri-state). DAT[3:0] is triggered by rising edge of SDCLK (SDR timing). DAT[3:0] shall be high within 1ms from start of providing SDCLK. Host check whether DAT[3:0] is high after 1ms from supplying SDCLK. This means that 1ms is the maximum for the card and the minimum for the host.

#### 4.4 Electrical Characteristics

(SD Bus Mode)

Figure 4-7: microSD Card Connection Diagram

#### 4.4.1 Absolute Maximum Conditions

**Table 4-5: Absolute Maximum Conditions**

| Item           | Symbol          | Value                               | Unit |

|----------------|-----------------|-------------------------------------|------|

| Supply Voltage | V <sub>DD</sub> | -0.3 to 3.9                         | V    |

| Input Voltage  | Vin             | -0.3 to V <sub>DD</sub> +0.3 (≤3.9) | V    |

## 4.4.2 DC Characteristics

**Table 4-6: DC Characteristics**

| High   Level   ViH   -   1.27   2   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Unit | MAX.                   | Тур.   | MIN.                   | Condition                                                     | Symbol          |               |                   | Item                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|--------|------------------------|---------------------------------------------------------------|-----------------|---------------|-------------------|---------------------|

| High   Level   VIH   Voltage   VIH   Voltage   VIH   Voltage   VIH   Low   VIH   Voltage   VIH   VIH | V    | 3.6                    | -      | 2.7                    | -                                                             | V <sub>DD</sub> |               | tage              | Supply Vol          |

| Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    | -                      | -      | V <sub>DD</sub> *0.625 |                                                               |                 |               |                   |                     |

| Level   Voh   2mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V    | V <sub>DD</sub> *0.25  | -      | -                      |                                                               | VıL             |               |                   |                     |

| Signaling   Voltage   Level   Vol.   IoL = 2mA   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V    | -                      | -      | V <sub>DD</sub> *0.75  |                                                               | Vон             |               |                   |                     |

| High   Level   VIH   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V    | V <sub>DD</sub> *0.125 | -      | -                      | loL = 2mA                                                     | <b>V</b> ol     |               |                   |                     |

| Voltage   Level   VIL     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V    |                        |        | 1.27                   |                                                               |                 |               |                   |                     |

| 1.8V   Output   Low   Low   Level   Vol   Iol = 2mA   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V    | 0.58                   | -      | -                      |                                                               | Vıl             |               |                   |                     |

| Signaling   Voltage   Level   Vol   IoL = 2mA   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V    | -                      | -      | 1.4                    |                                                               |                 | High          |                   |                     |

| Standby Current   G4GB   Iccs   VDD = 3.6V     450     128GB   256GB   Stop     500     SDR104   Current   Limit = 200mA, 400mA   VDD = 3.6V     170     Operation Read   G4GB   G4GB   Current   Limit = 200mA, 400mA   VDD =   Current   Limit = 200mA, 400mA   VDD =   Current                      | V    | 0.45                   | _      | -                      | lot = 2mA                                                     | <b>V</b> ol     |               |                   |                     |

| 256GB Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - uA | 450                    | -<br>- |                        | 3.6V                                                          | Iccs            | 64GB          | Current           |                     |

| Current Limit = 200mA, 400mA VDD= 3.6V  170  SDR50 Current Limit = 200mA, 400mA VDD= 3.6V  170  SDR50 Current Limit = 200mA, 400mA VDD =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 650                    | -      | -                      | Stop                                                          |                 |               |                   |                     |

| SDR50 Current Limit = 200mA, 400mA Current (peak) 128GB Iccop1 1 VDD =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 170                    | -      | -                      | Current<br>Limit =<br>200mA,<br>400mA                         |                 |               |                   |                     |